NEWS

2020.04.13

2020年4月8日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のハード設計向け要求管理ツール「Spec-TRACER」がIBMの要求管理ツール「DOORS Next」と連携に向け機能を強化したことを発表した。

発表によると機能強化によりAldecの「Spec-TRACER」はIBMの「DOORS Next」とのデータ交換が可能となった。

「Spec-TRACER」は、発売当時の2013年から業界デファクトツールと言われているIBMの要求管理ツール「DOORS」とのデータ交換をサポートしているが、今回「DOORS」の進化版である「DOORS Next」のサポートに至った。「DOORS Next」は2019年にリリースされた製品でISO26262などの安全規格の要求管理も可能だという。

Aldecの「Spec-TRACER」はハードウェア設計における設計要求のトレーサビリティ管理を実現するツールで、要求仕様をインポートし 、デザインおよびテストに対して各要求がどのように実装されているかをキャプチャできるほか、要求仕様の変更の影響分析や要求カバレッジ分析なども可能で、トレーサビリティレポートを自動生成する事もできる。

「Spec-TRACER」は、「DOORS Next」の成果物とトレーサビリティ・データをキャプチャするだけでなく、要求とハードウェア設計データ間の関係を「DOORS Next」にエクスポートして戻すことができるため、システムエンジニアは要求カバレッジ・ステータスをハードウェアも含めて監視することが可能。Aldecは、システムとハードウェアのライフサイクル・データ間の完全なトレーサビリティを実現できるとしている。

※アルデック・ジャパン株式会社

2020.04.10

2020年4月9日、IC Insightsの記事

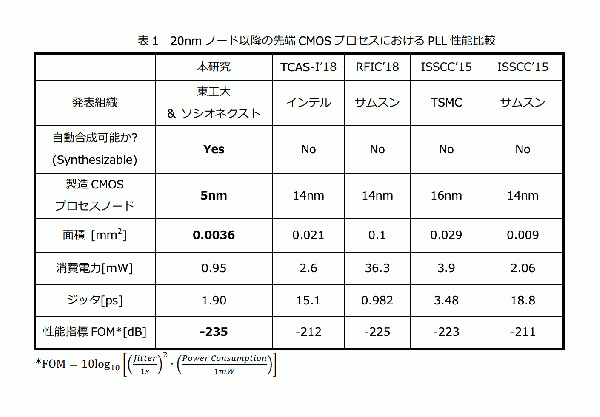

半導体関連を専門とする市場調査会社IC Insightsは、今年の世界半導体市場の予測を更新した。

同社は年初の1月時点で2020年はプラス8%成長と予測していたが、その後中国で発生した新型コロナウイルスの影響を踏まえ3月時点で予測をプラス3%成長に下方修正。そして新型コロナウイルスが世界各地に拡がったこと受け、今年は4%のマイナス成長になる見通しと再び予測を下方修正した。

IC Insightsによる集計値とは異なるが、SIAの報告によると2019年の世界半導体市場は前年比約12%減の4120億ドルだった。IC Insightsの予測通りに4%のマイナス成長となった場合、今年の世界半導体市場は4000億ドルを割り込むことになるが、果たしてその程度の落ち込みで済むのだろうか。

2020.04.07

2020年4月3日、国立大学法人筑波大学、国立大学法人東京工業大学、アヴネット株式会社、ザイリンクス株式会社、株式会社SUSUBOX、特殊電子回路株式会社、株式会社フィックスターズ、わさらぼ合同会社の計8団体は、アダプティブコンピューティング研究推進体「ACRi(アクリ)」の設立を発表した。

発表によるとACRiは、FPGAの活用方法の模索・研究を目的とした産学連携の研究団体で、東京工業大学の大岡山キャンパス内に拠点を設置。創設メンバーを含む下記計15の団体(2大学、13社)が活動を協賛している。

(大学)

国立大学法人筑波大学

国立大学法人東京工業大学

(創設企業)

アヴネット株式会社

ザイリンクス株式会社

株式会社SUSUBOX

特殊電子回路株式会社

株式会社フィックスターズ

わさらぼ合同会社

(参加企業)

アイベックステクノロジー株式会社

株式会社アクセル

株式会社インターネットイニシアティブ

株式会社インテリジェント ウェイブ

KDDI株式会社

株式会社サイバーエージェント

Mipsology SAS

ACRiは具体的な研究テーマとして下記の3テーマを掲げており、FPGA検証環境や学習機会の無償提供、エンジニアの交流の場の提供なども行っていくとしている。

・AI等の処理を高速化するFPGAアクセラレータの開発

・IoTのためのFPGAアクセラレータおよびFPGAシステムの開発

・設計を効率化するためのFPGA活用基盤の開発

FPGA関連の国内コミュニティとしては、FPGAコンソーシアムというNPO法人がFPGA創成期から活動しており、最近ではFPGAエクストリーム・コンピューティングというエンジニア・コミュニティも注目を集めている。今回立ち上げられたACRiは、産学連携の研究団体として国内に新たな形のFPGAコミュニティを創り出してくれそうだ。

2020.04.07

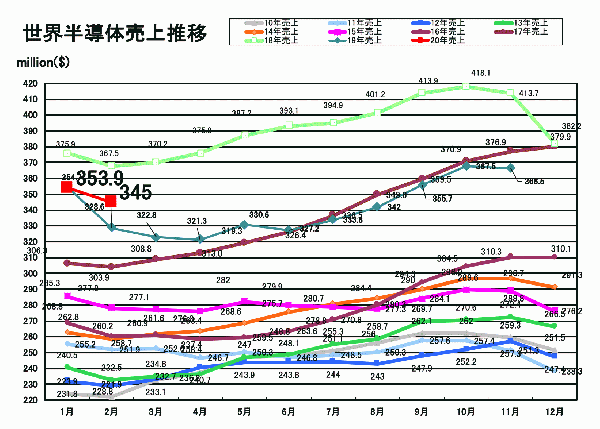

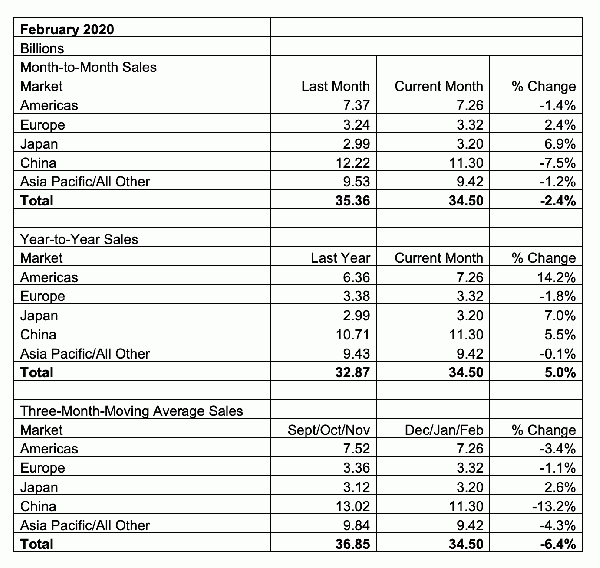

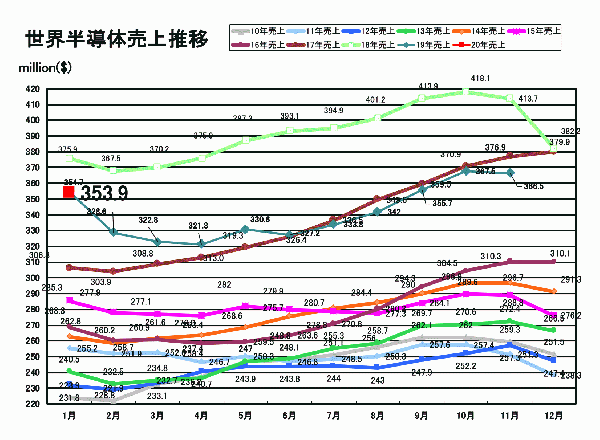

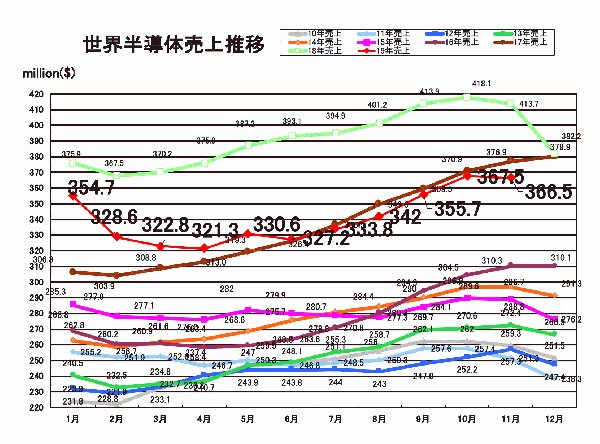

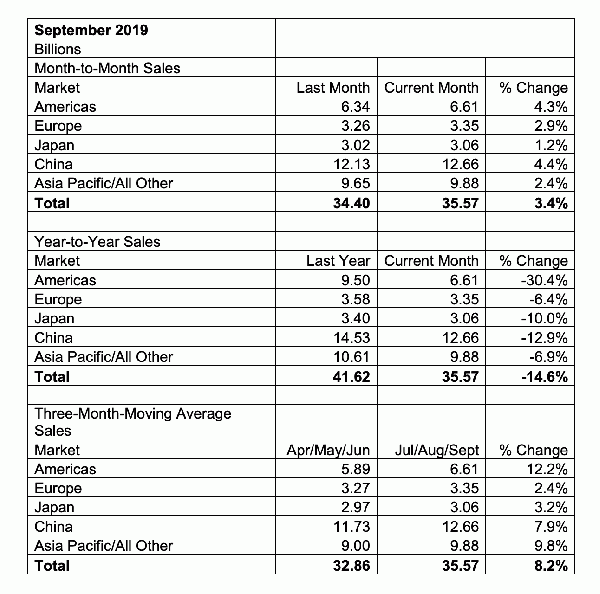

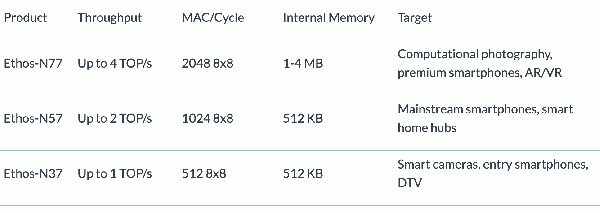

2020年4月3日、米SIA(Semiconductor Industry Association)は、2020年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年2月の世界半導体売上は、前年同月比5%増、前月比2.4%減の345億ドルという結果だった。SIAによるとこの2月の売上にはコロナウイルスの影響はまだ現れていないとの事。1月まで売上実績の前年割れが15ヶ月連続で続いていたが、2月は1年3ヶ月ぶりに前年実績を上回った。しかし、月次売上の減少は昨年11月から4ヶ月連続で、来月以降はコロナウイルスの影響が現れ更に売上が減少する可能性が高い。

2020年2月の売上を地域別で見ると、北米、中国、日本が前年比プラス成長を達成、中でも北米は前年比14.2%増と大きく回復した。前月比では日本市場が6.9%増と成長率トップだった。

日本市場の2月の売上は32億ドルで、売上を円ベースで換算すると前月比約7.3%増、前年比約6.6%増の約3,519億円となる。

2020.04.01

2020年3月31日、RISC-VベースのCPU IPを手掛ける台湾Andes Technologyによると、同社のIPを用いたSoCの出荷数は2019年に15億個に到達した。(

プレスリリース)この実績は前年比で50%増で同社のIPを用いたSoCの累計出荷数は50億個を超えた。同社のIPは以下のようなアプリケーションに組み込まれているという。

オーディオ、Bluetooth、ゲーム、GPS、機械学習、MCU、センサーフュージョン、SSDコントローラー、タッチスクリーンとTDDIコントローラー、USB 3.0ストレージ、音声認識、Wi-Fi、ワイヤレス充電器など。

Andes Technologyは創業15年と歴史は浅いが、オープンソースのISAであるRISC-Vにいち早く目をつけ、独自の命令セットアーキテクチャ「AndeStar」をRISC-Vベースに刷新し、32ビット/64ビットの「Andes Core」を数品種ラインナップしている。同社によると、2019年に既存ISAベースの製品とRISC-Vベース製品の収益率が初めて逆転したという話だ。累計のSoC出荷数50億個の半分は直近2年の実績で、RISC-Vベースの「Andes Core」をリリースした2016年以降、実績を伸ばし続けている。

2020.04.01

2020年3月26日、IC Insightsのレポート

半導体分野の調査会社IC Insightsによると、2009年以降の10年間で転用または閉鎖された半導体ウエハ工場の数は世界で計100か所。うち70%が北米および日本国内の工場で、地域別では日本国内が計36と最も多かった。

転用・閉鎖されたウエハ工場の多くは200mm以下のウエハを製造する工場で、2020年から2021年にかけて更に4つの工場が閉鎖される見通し。ウエハ工場の新設コストが高騰しており、多くのIC企業がファブライトまたはファブレスのビジネスモデルに移行していることから、IC Insightsは今後数年間でファブ閉鎖が増えると予測している。

転用・閉鎖の件数が多かった2009年、2010年は、2007年から2008年の大不況の直後という時期であり、今回のコロナウイルスの影響で来年以降、再びファブ閉鎖の波が訪れる可能性がある。

2020.03.26

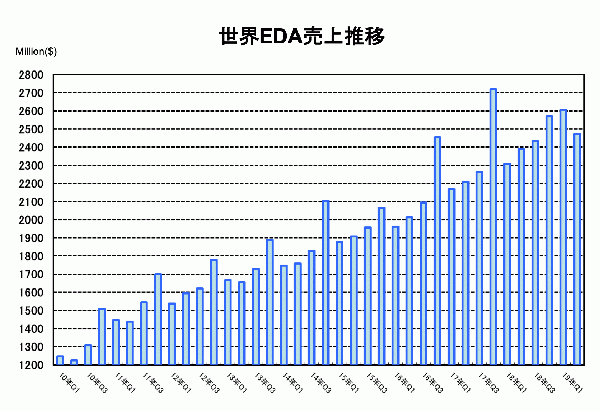

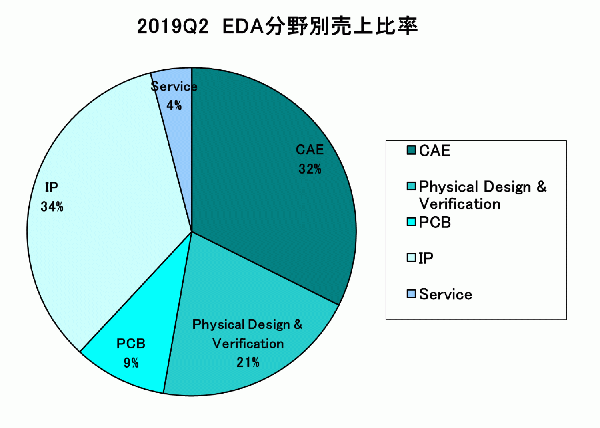

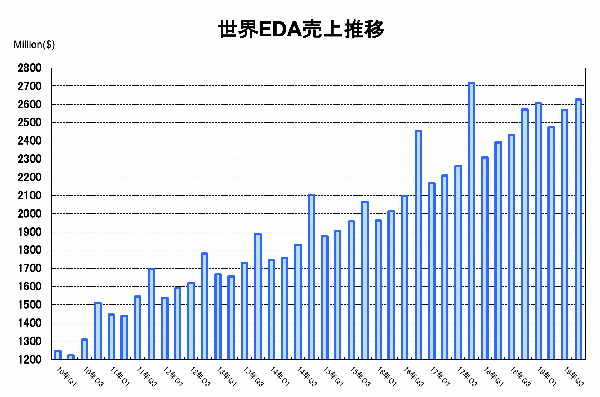

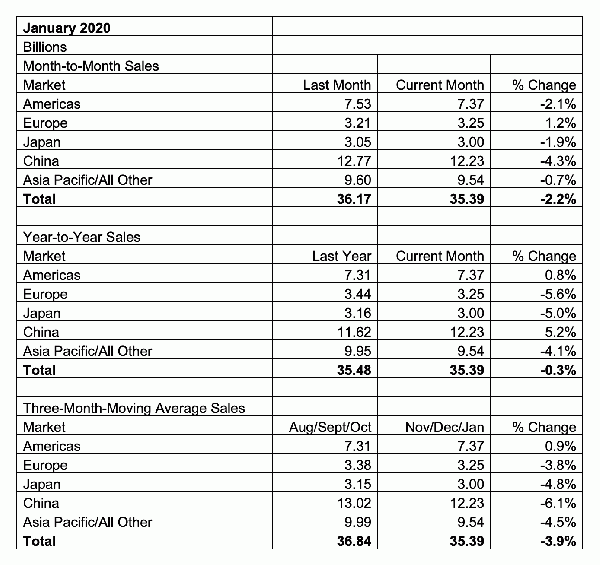

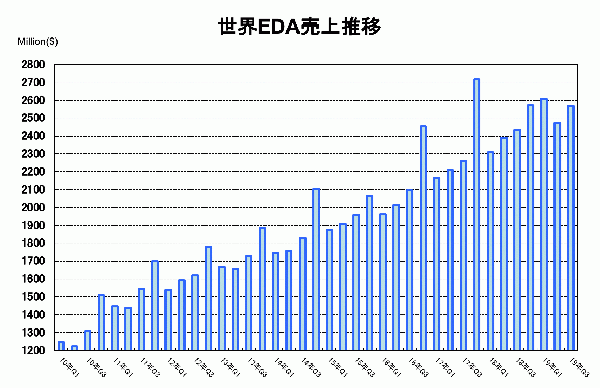

2020年3月25日、米ESD Allianceは、2019年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2019年Q4(10-12月)の世界のEDA売上総額は前年比約2.2%増の26億2630万ドルで、4四半期連続で四半期売上が前年実績を上回った。

2019年の売上合計は前年比8.3%増の102億ドルとなり、初めて100億ドルの大台を突破した。ちなみに20年前の世界EDA市場はおよそ50億ドル程度だった。

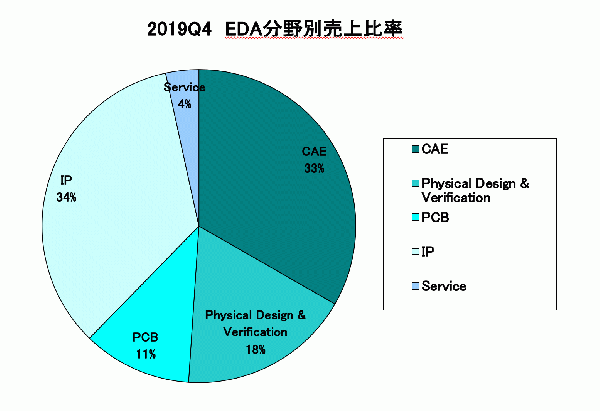

2019年Q4のEDA売上をカテゴリ別に見ると、CAE,IP分野の他にPCB/MCM分野が大きく伸びた。

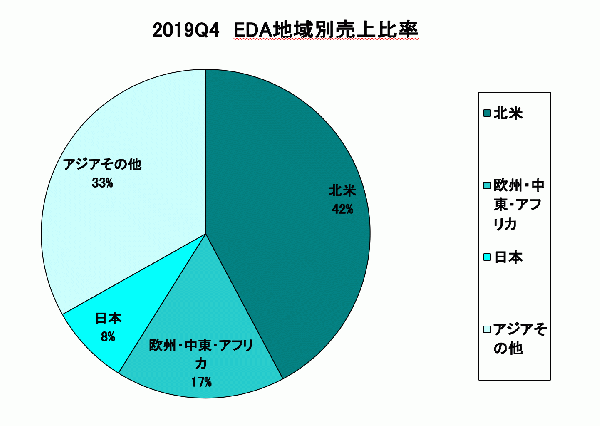

2019年Q4のEDA売上を地域別に見ると、欧州・中東・アフリカが前年比31%増と大幅増。ここのところアフリカでの売上が順調に推移している。Q4のEDA市場の伸びは、欧州・中東・アフリカが押し上げている状況だ。日本市場は依然落ちる一方の状況となっている。

2019年Q4時点でのEDA業界の従業員数は前年比6.1%増の45,416人でQ3よりも増加した。

2019年Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 8億7440万ドル 1%Up

■IC Physical Design & Verification分野 4億6640万ドル 3.9%Down

■IP分野 9億60万ドル 4%Up

■サービス分野 8960万ドル 15%Down

■PCB/MCM分野 2億9530万ドル 19.4%Up

2019年Q4の地域別の売上と昨年同時期との比較は以下の通り。

■北米 11億2560万ドル 2.9%Down

■欧州・中東・アフリカ 4億4510万ドル 31%Up

■日本 2億1140万ドル 6%Down

■アジアその他地域 8億8420万ドル 0.2%Down

※ESDA(Electronic System Design Alliance)

2020.03.26

2020年3月25日、eenewsanalogの記事:

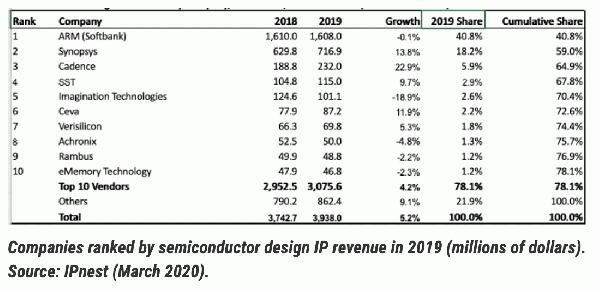

市場アナリストのIPnestによると2019年のIPライセンス売上額においてSynopsysの実績が業界首位のArmを上回った。

2019年のIPライセンス売上におけるSynopsysのシェアは29.3%で首位。2位Armは25.2%、3位Cadenceは7.8%。

ロイヤリティも含めた市場シェアではArmが40.8%で首位。2位Synopsysは18.2%, 3位Cadenceは5.9%。

ARMはかつてIP市場の50%を占めていたが、2018年44.7%, 2019年40.8%と徐々にシェアを減らしている。これは、RISC-Vなど競合製品の登場ではなく、プロセッサ以外のIPの需要が高まっているためとIPnestは指摘する。

Synopsysの2019年のIP売上は前年比13.8%増、CadenceのIP売上は前年比22.9%増となっている。

2020.03.26

2020年3月25日、Synopsysは、同社の設計・検証ツールがSiFiveのクラウド設計環境に採用された事を発表した。

SiFiveは、オープンソースの命令セット・アーキテクチャ「RISC-V」ベースのプロセッサ・コアを手掛けるIPベンダとしてこの数年で業界最大手に上り詰めたベンチャー。IPを提供するだけでなく自社IPを用いたカスタムSoCをワンストップで設計・製造するというソリューションを打ち出しており、業界に新風を巻き起こしている。

SiFiveはテンプレートを用いてチップ設計を行う事が可能なクラウド上の設計環境をユーザーに用意しているが、今回その環境にSynopsysの設計環境「Synopsys Fusion Design Platform」と検証環境「Verification Continuum Platform」が組み込まれる事になった。但し、これらツールはあくまでもSiFiveが顧客のカスタムSoCを設計するために用いられるようで、SiFiveのユーザーに開放されるものでは無さそうだ。

SiFiveのクラウド環境はチップ構成を検討するためのもので、論理回路の設計・実装・検証を行うものではなくそこはSiFiveに委ねるか、SiFiveからプロセッサ・コアのRTLを受け取り自ら行う必要がある。

SiFiveは元々自社のIPやSoCテンプレートの設計にSynopsysのツールを利用していたという事だ。

2020.03.24

2020年3月17日、台湾TrendForceが2019年のファブレス半導体ベンダ売上ランキングを発表した。

ランキングの詳細は下記の図を参照。

※画像はTrendForece発表のデータ

注目されるのはTop3が軒並み前年実績を割り込んでいる点で、Broadcomは米国輸出規制の影響で業績が悪化。Qualcommはも米国輸出規制に端を発した中国ブランドの米国技術離れの影響でHuawei、MediaTek、Unisocらにシェアを奪われた。NVIDIAはゲーム向けのグラフィックカードの過剰在庫が原因で売上を落とした。

米企業として売上を伸ばしたのはAMDとXilinxの2社。AMDはIntelの供給不足が功を奏し売上上昇。Xilinxは5G、FA、Automotiveの分野でそれぞれ業績が伸びた。

TrendForceは、長引いている米国輸出規制の問題と新たなCOVID-19のパンデミック問題により、ファブレス半導体業界全体の売上が2020年に回復する見込みは低いとしている。

2020.03.19

2020年3月18日、Cadenceはデジタル設計フローの新バージョンのリリースを発表した。

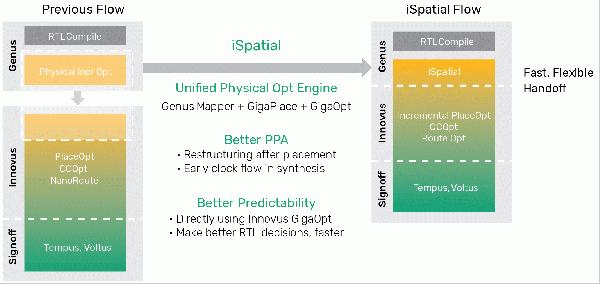

今回発表された新しいCadenceのデジタル設計フローは、PPAを最大20%向上、設計スループットを最大3倍高速化という大胆なもので大幅な機能強化が図られている。その中心となるのが「iSpatial」テクノロジと呼ばれる新たなフィジカル最適化エンジンで、同機能によりフィジカル合成「Genus」と 配置配線「Innovus」の緊密な統合が実現し、よりシームレスな形でインプリメント工程を処理できるようになる。

Cadenceの説明によると「iSpatial」は、フィジカル合成「Genus」のマッピング機能と 配置配線「Innovus」の配置エンジンおよび最適化機能を統合したもので、最適な配線レイヤー割り当て、クロックスキュー、ビアピラーなどのテクノロジをサポート。そして同最適化エンジンの目玉と言えるマシンラーニング機能が搭載されている。

「iSpatial」のマシンラーニング機能は最適化機能を高めるためのもので、既存のデザインを元にトレーニングを行う事によって設計マージンの最小化を実現する。発表に寄せられたユーザーのコメントによると、マシンラーニング機能の活用によって最大動作周波数の向上、マイナスのスラック値の低減、リーク電流の低減といった成果が得られているということだ。

※画像はCadenceの発表データ

Cadenceの新しいデジタル設計フローは、「iSpatial」テクノロジを用いてより早く賢くデザインの最適化を行うことでPPA品質を向上すると同時にインプリ工程におけるイタレーションを削減。緊密なツール連携も加わり、TAT短縮に対する効果も大きいようだ。

2020.03.17

2020年3月16日、Synopsysは新製品「RTL Architect」を発表した。

Synopsysによると「RTL Architect」は、フィジカル設計のイタレーションを削減することで設計の早期収束を狙うツールで、フィジカル設計を考慮してRTLをチューニングするというこれまでに無いタイプの製品となる。

「RTL Architect」には、Synopsysのインプリメンテーション・ツールならびにサインオフ・ツールのアルゴリズムを活用した高速動作の多目的・予測エンジンが装備されており、同エンジンを用いてRTLを解析することで「Fusion Design Platform」で実行するインプリメンテーション結果を高精度に予測することが可能。その予測結果からRTLコードに潜むボトルネックをピンポイントで特定し、RTLの品質向上を図るチューニングが可能となる。

「RTL Architect」によるインプリ結果の予測は性能/消費電力/面積/配線混雑に対して可能で、SynopsysはRTL段階で高精度な消費電力予測ならびに最適化が可能と強調。同ツールを利用することで開発期間を半減し優れた設計品質を実現できるとしている。

2020.03.05

2020年2月27日、SynopsysはRTL検証ツールの新製品「VC SpyGlass」のリリースを発表した。

Synopsysによると「VC SpyGlass」は、業界標準のRTL静的検証ツール「SpyGlass」の技術をベースに開発した新製品で、従来比半分のメモリー使用量で3倍のパフォーマンス向上を実現。検証キャパシティも3倍に拡大され数十億ゲートのRTLコードを検証できるようになった。またSynopsysは「VC SpyGlass」にマシンラーニング技術を取り入れており、その結果、検証品質を犠牲にすることなくノイズを1/10に削減できるとしている。

マシンラーニングの応用に関する詳細は明らかにされていないが、「VC SpyGlass」の主機能の一つであるCDC/RDC解析機能において利用されているようで、ユーザーであるルネサスの担当者は、「疑似CDC違反のデバッグに追われるケースを大幅に削減し、根本原因をより短期間に特定できることが期待できる。」とコメントしている。

2020.03.04

2020年2月25日、AIチップベンチャーGraphcoreは、資金調達D2ラウンドで1億5000万ドルを調達した事を発表した。

発表によると今回の投資ラウンドには投資ファンドなど複数の投資家が参加。今回の追加調達により同社の累計調達額は4億5000万ドルとなった。

Graphcoreの開発する「IPU-Processor」は、マシンラーニングの学習/推論両方に適用可能で、いずれにおいても既存のソリューションの10-100倍の性能を発揮するとしている。「IPU-Processor」は、既にMicrosoftのクラウドプラットフォーム「Azure」上で稼働しているほか、Dellのサーバーに組み込まれるなど、実ビジネスに展開されはじめている。

時同じくして資金調達を発表したSambaNovaも累計調達額はGraphcoreとほぼ同じ4億5600万ドルだが、まだ製品を市場投入するに至っていない。

2020.03.03

020年3月2日、米SIA(Semiconductor Industry Association)は、2020年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年1月の世界半導体売上は、前年同月比0.3%減、前月比2.2%減の353.9億ドルという結果だった。売上実績の前年割れは2018年11月以降15ヶ月連続。昨年11月から3ヶ月連続で売上減少が続いており、今後は新型肺炎の影響などにより更に売上減少が続く可能性が高い。

米調査会社のGartnerは、既に2020年の世界半導体売上を前年比9.9%増の4599億ドルと下方修正している。同社の2019年12月時点の予測は前年比12.5%増の4707億ドルだった。

2020年1月の売上を地域別で見ると、北米および中国市場だけかろうじて前年比プラス成長、その他の地域は前年実績を割りこんだ。

日本市場の1月の売上は前月比1.3%減、前年比5%減の30億ドルで、売上を円ベースで換算すると前月比約1.2%減、前年比約4.7%減の約3,278億円となる。

2020.02.28

2020年2月25日、シリコンバレーのAIチップ・スタートアップSambaNova Systemsは、資金調達Cラウンドで2億5000万ドルを調達したことを発表した。

発表によると今回の投資ラウンドを主導したのは世界的な資産運用会社BlackRockで、既存投資家のGoogle Ventures, Intel Capital, Walden Internationalらがこれに続いた。ちなみにWalden InternationalのチェアマンはCadenceのCEO Lip-Bu Tan氏である。

今回SambaNovaが集めた投資額は2億5000万ドルで、Aラウンドの5600万ドル、Bラウンドの1億5000万ドルを合わせると、同社の累計調達額は4億5600万ドルとなる。

SambaNova SystemsのAIチップは、独自の機械学習アルゴリズムとソフトウェア定義型の再構成可能なハードウェアを組み合わせたコンピューティング・プラットフォームで、アプリケーションに最適化されたハードウェア構成でAI処理を実行できるとされている。

2020.02.28

2020年2月27日、Cadenceは検証IPの新製品「PHY VIP」のリリースを発表した。

発表によるとCadenceの新製品「PHY VIP」は、複雑なプロトコルの物理レイヤーを網羅的かつ高速に検証することが可能な業界初のPHY専用検証IPで、PIPE 5.2 for PCI Express® (PCIe®) 5.0、USB3/USB4、DFI for LPDDR4、DDR5、HBM2E、MIPI® D-PHYsm/C-PHYsm for CSI-2sm 2.0、DSIsm 2.0など複数のプロトコルをサポートするという。

「PHY VIP」の主な機能は以下の通り。

・PHYレベルのタイミングチェック

・プロトコル依存およびプロトコルに依存しないトラフィックのドライブ機能により

詳細なテストを実行

・受信パス、送信パス、ループバックを解析するためのスコアボード表示機能

・ジッター、スペクトラム拡散クロック、ビット誤り率を制御

2020.02.21

2020年2月19日、Synopsysは、2020会計年度第1四半期(19年11-20年1月)の四半期決算を報告した。

発表によるとSynopsysの2020会計年度Q1の売上は、前年同時期比約1.7%増、前Q4比約2%減の8億3440万ドル、営業利益は前年比約37%減の1億410万ドルだった。(※GAAP基準による会計結果)。Synopsysは2019年Q4で8四半期ぶりに四半期売上が減少していたが、これで2四半期連続で売上が減少したことになる。しかし売上の減少はごく僅かなもので、2020年度は2019年度の実績を上回るという見通しを崩していない。

SynopsysはこのQ1において、下記4件の買収を完了している。

・eSilicon社の資産買収

・DINI Groupの買収

・INVECAS社のIP資産の一部買収

・Tinfoil Security社の買収

Synopsysは時期Q2の売上を8億2000-5000万ドル、2020年度売上を36億-36億5000万ドルと予測している。

2020.02.21

2020年2月18日、ハードウェア設計言語・技術の標準化団体米Accellera Systems Inisiativeは、機能安全に関する新たなワーキング・グループの始動を発表した。

Accelleraによると、「Functional Safety Working Group」は、機能安全ライフサイクルにおけるデータの相互運用性やトレーサビリティの改善を目的に、新たな言語/フォーマットを開発し標準化する計画。機能安全の実現に向けて、機能安全を意識したシステムおよび電子回路の設計/検証フローの確率を目指す。

Accelleraは昨年10月時点で機能安全関連のPWG(Proposed Working Group)を立ち上げており、その活動を経て今回のWG発足という流れ。既に業界の主要19社が同WGへの参加を表明しているという。この標準化活動によってFMEDAツールなど機能安全関連の各種解析ツールの相互運用性が高まる事が期待される。

2020.02.14

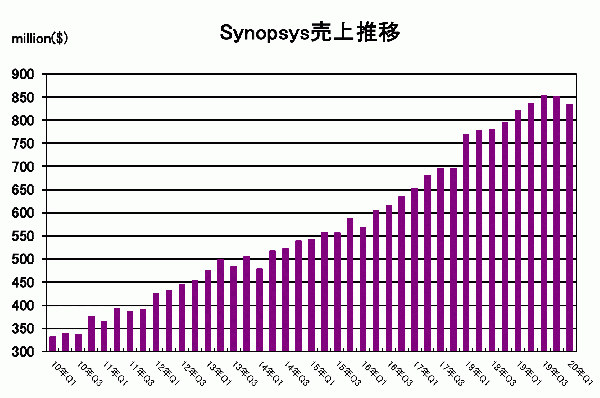

2020年2月10日、ソシオネクストと東京工業大学 岡田健一教授らの研究グループは、5nm FinFET CMOSプロセスで世界初となる世界最小の高性能分数分周型クロック回路の開発に成功したことを発表した。

発表によると今回開発されたクロック回路はデジタル回路として構成されるもので、通常のデジタル回路と同様にデジタル回路の設計ツールで自動配置配線が可能。実際に5nm FinFET CMOSプロセスで作られた回路は世界最小の0.0036mm2 という回路面積で、優れたジッタ特性と電力性能を実現。(※下記画像参照)また、同クロック回路は細かい周波数調整が可能な分数分周型PLLで構成されており、スペクトル拡散クロックの生成により低電磁妨害特性を実現しているという。

※画像はプレスリリースのデータ

従来のPLLではアナログ回路構成で実現されていたデジタル制御発振器(DCO)と時間差デジタル変換器(TDC)を、デジタル回路構成によって実現できたことが今回のクロック回路開発の成果で、デジタル時間変換器(DTC)とTDCを組み合わせデジタル補正を用いることでそれを実現した。

PLL全体をデジタル回路として実現できるということは、プロセス技術の微細化に合わせて回路面積を縮小でき、低消費電力化も可能となるだけでなく設計も容易になる。今回の成果をうけてソシオネクストは、クロック回路のデジタル化により将来のSoCの全自動設計への道が拓かれたとしている。

なお、今回の研究は、株式会社テラピクセル・テクノロジーズの協力により実現したとのこと。

2020.02.14

2020年2月14日、Cadenceは、米Integrand Softwareの買収を発表した。

米Integrand Software社は、2003年に米ベル研究所の技術者によって設立された会社で、同社の主力製品「EMX」は、RF IC用電磁界シミュレータのデファクト・スタンダードとして知られており、TSMC、UMC、GLOBALFOUNDRIESなどファンドリ大手でも認証および採用されている。また、「EMX」は、Cadenceのカスタム設計環境「Virtuoso」フローとシームレスに統合されている。

Cadenceは今回の買収を5G RF通信市場に向けたイノベーションの加速に向けたものとしており、Integrandの「EMX」を同社の「Sigrity™」、「Clarity™」、「AWR製品」と統合し完全なEM(electromagnetic)サインオフソリューションを提供するとしている。

Cadenceは先頃AWRの買収を完了したばかり。5G/RF分野に対する積極的な投資を進めている。

2020.02.14

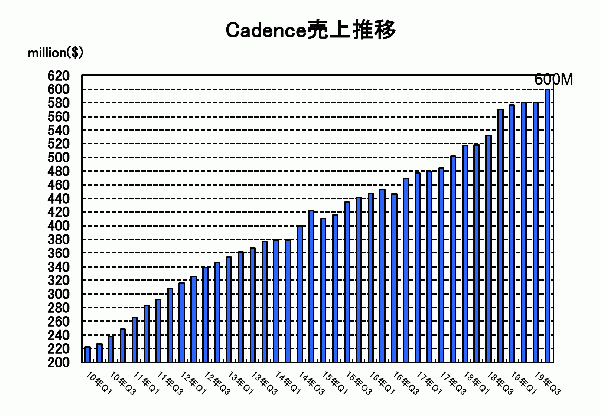

2020年2月12日、Cadenceは、2019会計年度第4四半期(2019年10-12月)の売上を報告した。

Cadenceの2019年Q4売上は、前年比約5.2%増、前期Q3比約3.4%増の6億ドルだった。営業利益は子会社への知的財産の移転に伴う特別計上が5億6600万ドルあり、計6億6000万ドルを計上した。(※GAAP基準による会計結果)

Cadenceの2019年度の売上額の合計は前年比約9.2%の23億3600万ドルで過去最高を記録。営業利益は前年の3倍近い約9億9000万ドルだった。

CadenceはこのQ4以下のような製品及びニュースを発表している。

・HPC向けの「NVMe 1.4検証IP」を発表

・サインオフタイミングを考慮したIRドロップ解析ツール「Tempus Power Integrity Solution」を発表

・ダイ間通信に向けたIP新製品「Cadence UltraLink D2D PHY IP」をリリース

・National Instrumentsの傘下AWR Corporationの買収を発表

Cadenceは2020年Q1の売上を6億1000万-2000万ドル、2020年の総売上を25億4500万-8500万ドルと予測している。

2020.02.05

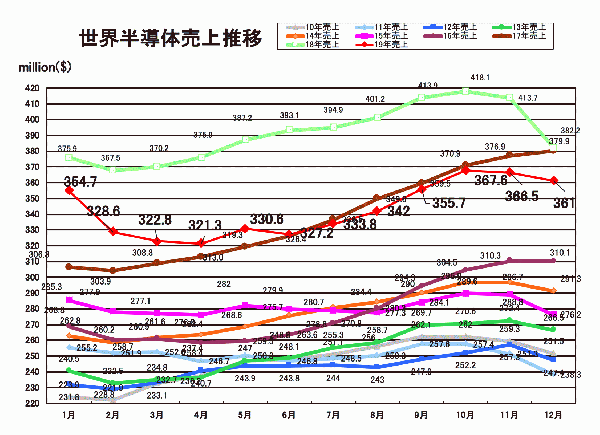

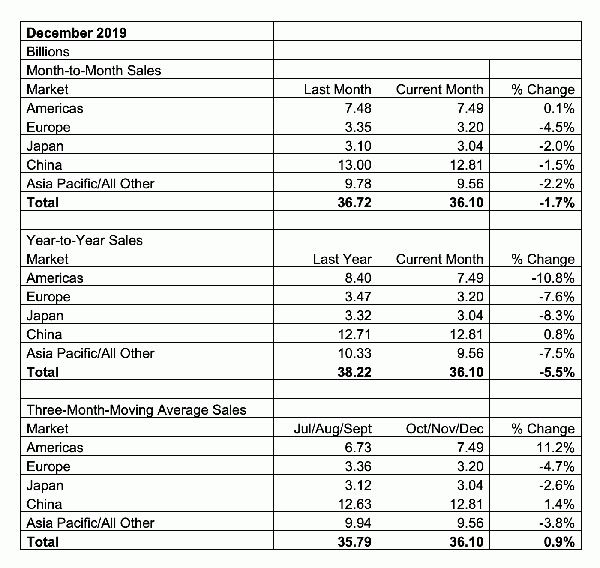

2020年2月3日、米SIA(Semiconductor Industry Association)は、2019年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年12月の世界半導体売上は、前年同月比5.5%減、前月比1.7%減の361億ドルという結果だった。売上実績の前年割れは2018年11月以降14ヶ月連続。8-10月と3ヶ月連続でわずかながら売上が伸びていたが、11月、12月と再び売上が減少した。

2019年通年の売上累計額は合計4120億ドルで前年比12.1%のマイナス成長。2019年3月時点で各統計機関や調査会社が既に2019年のマイナス成長を予測していたが(

関連ニュース)、結果的には当時の予想を大きく上回るマイナス成長となった。ちなみに2019年12月時点のWSTSの2020年市場予測は5.9%のプラス成長となっている。

2019年12月の売上を地域別で見ると中国市場だけは0.8%のプラス成長、その他の地域は全て前年実績を割りこんだ。

日本市場の12月の売上は前月比2%減、前年比8.3%減の30.4億ドルで、売上を円ベースで換算すると前月比約1%減、前年比約11.3%減の約3,318億円となる。

2020.01.17

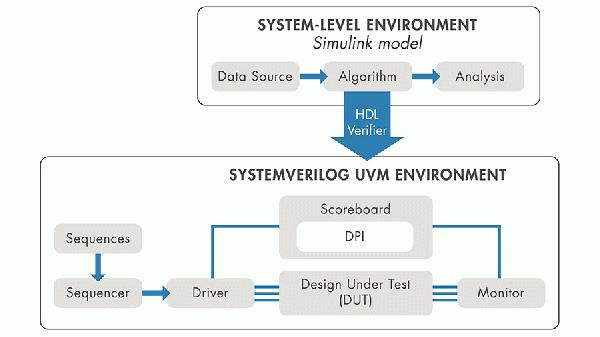

2020年1月15日、MathWorksは、同社のRTL検証ツール「HDL Verifier」による検証メソドロジ「UVM」のサポートを発表した。

MathWorksによると「HDL Verifier」によるUVMのサポートは、既に利用可能なRelease 2019b以降からで、Matlab/Simulinkで開発したアルゴリズムモデルからシーケンスやスコアボードなどのUVMコンポーネントを自動生成可能に。生成されるUVMコンポーネントはUVMをサポートする市販のHDLシミュレータで利用可能で、これらを用いる事で手書きでテストベンチ

を作成する工数を大幅に減らす事ができる。

※画像はMathWorks社Web上のデータ

「HDL Verifier」はUVMコンポーネントだけではなく、SystemVerilogアサーション、SystemVerilog DPIコンポーネントなども生成することが可能。これらを利用してMATLAB/Simulinkとの協調検証や、FPGAボード/開発ボードを使用したハードウェア・ベース検証を行うことができる。

2020.01.17

2020年1月15日、Cadenceは、RF/高周波回路設計ツールを手がけるAWR Corporationの買収完了を発表した。

CadenceがAWRの買収を発表したのは昨年12月で買収額は約1.6億ドル。(

プレスリリース)

AWR Corporationは、2011年にNational Instruments社に約5800万ドルで買収され同社の傘下で事業を継続していた。

CadenceはAWRの買収により、5GなどRF通信システムの開発ソリューションを拡充する。

また業界首位のSynopsysは、2020年1月7日にINVECAS社のIP資産の一部を買収することを発表した。

INVECASは、スタンダード・セル、メモリ、GPIOライブラリなどのFoundation IP、PLL、サーマル・センサー、ビデオ/オーディオADCなどのAnalog IP、DDR、MIPI、USB、HDMIなどのInterface IPを手掛けており、HDMIを除く各種IP資産をSynopsysに売却。買収条件などは不明。INVECASは、HDMI IPの開発とASICデザインサービスは今後も継続するという。

また、Synopsysは昨年11月にファブレス半導体ベンダeSiliconのIP資産の買収を発表していたが、2020年1月13日に同買収手続きの完了を発表した。

2020.01.10

2020年1月6日、ESL合成ツールを手掛ける米Bluespecは、同社の提供している「BSVツール」のオープンソース化を発表した。

Bluespecは元々MITのスピンアウトとして生まれたEDAツールベンダで、高抽象度の独自のハードウェア記述言語「Bluespec SystemVerilog」を用いたRTLの自動生成ツール「BSVツール」を提供している。「BSVツール」は、一般的な高位合成ツールが行う「スケジューリング」とは異なるアプローチでRTLを合成するのが特徴で、スケジューリングにあたる作業は設計者に委ねられるが、抽象度の高い言語でコーディング可能なため、複雑な制御回路なども効率的に設計できるとされている。

「BSVツール」は一時期、高位合成ツールの新たな潮流としてもてはやされた時期もあり、国内外でも大手が採用という動きがあったが、ツールとしては大成に至らず、近年BluespecはオープンソースのISA「RISC-V」に商機を見出し、独自のRISC-Vベースコアの提供に注力。その開発環境として「BSVツール」を活用していた。

Bluespecによると、「BSVツール」のソースコードは、標準のオープンソース・ライセンスの下でライセンスされ、別の非営利組織によってホストされる予定。Bluespecは、オープンソースのツールとして「BSVツール」を引き続き提供し、公開リポジトリのアップストリームの修正や機能強化も継続するとしている。

なお、既に製品として提供しており、同社のビジネスの中心となっている、RISC-Vプロセッサ向けの開発環境「RISC-V Factory」は今後も販売される。同環境には「BSVツール」も組み込まれており、RISC-Vプロセッサの評価/検証およびカスタマイズ環境として機能する。

2020.01.10

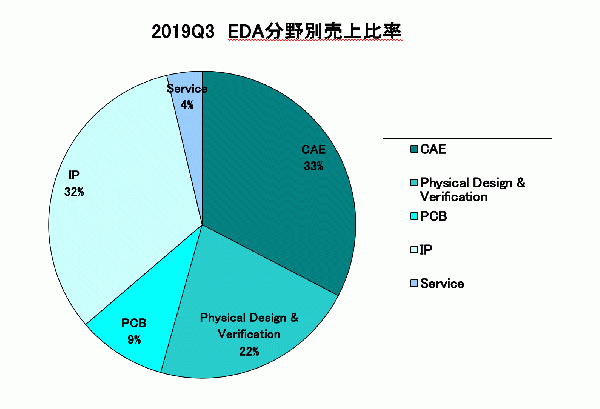

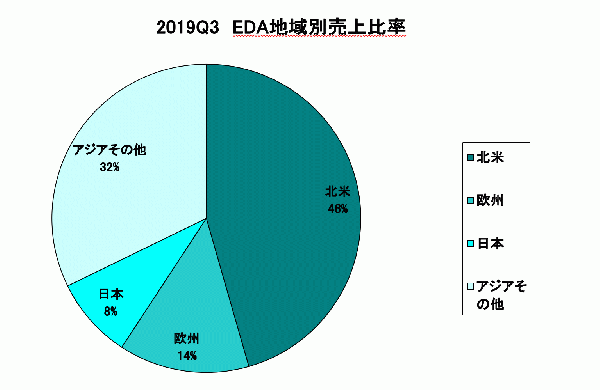

2020年1月7日、米ESD Allianceは、2019年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると2019年Q3(7-9月)の世界のEDA売上総額は、前年比約8.9%増、前19年Q2比約3.8%増の25億6770万ドルだった。四半期売上が前年実績を上回るのはこれで3四半期連続。

2019年Q3のEDA売上をカテゴリ別に見ると、Q2で2ケタ成長を見せたIP分野は微増、それ以外はサービス分野を除いて全て前年比2ケタ増の力強い成長を示した。

2019年Q3のEDA売上を地域別に見ると、北米が前年比10.4%増と力強さを取り戻した。

日本市場は前年比9.4%減で一人負けの状態。円ベースで換算すると前年比12.8%程度のマイナスとなる。

2019年Q3時点でのEDA業界の従業員数は前年比6.6%増の42,162人でQ2よりも約5%減少した。

2019年Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 8億3830万ドル 10.8%Up

■IC Physical Design & Verification分野 5億5760万ドル 17.2%Up

■IP分野 8億3590万ドル 3.7%Up

■サービス分野 9540万ドル 19.9%Down

■PCB/MCM分野 2億4050万ドル 19.8%Up

2019年Q3の地域別の売上と昨年同時期との比較は以下の通り。

■北米 11億6990万ドル 10.4%Up

■欧州 3億5110万ドル 0.1%Up

■日本 2億1930万ドル 9.4%Down

■アジアその他地域 8億2750万ドル 5.7%Up

※ESDA(Electronic System Design Alliance)

2020.01.07

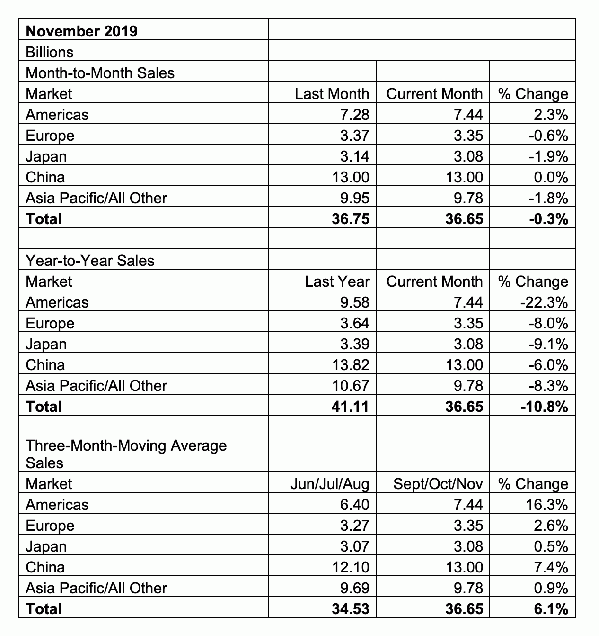

2019年12月31日、米SIA(Semiconductor Industry Association)は、2019年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年11月の世界半導体売上は、前年同月比10.8%減、前月比0.3%減の366.5億ドルという結果だった。売上実績の前年割れは2018年11月以降13ヶ月連続。8-10月と3ヶ月連続でわずかながら売上が伸びていたが、11月は10月実績を超えられなかった。とはいえ市場の減退は底を抜けた感があり、今後は市場が緩やかに回復していくと見られる。

2019年11月の売上を地域別で見ると全ての地域で前年実績割れとなったが、北米だけは10月売上を上回った。

日本市場の11月の売上は前月比1.9%減、前年比9.1%減の30.8億ドルで、売上を円ベースで換算すると前月比約0.3%減、前年比約12.9%減の約3,350億円となる。

2019.12.13

2019年12月10日から12日の3日間、サンノゼで世界最大のRISC-Vコミュニティのイベント「RISC-V Summit 2019」が開催された。

昨年始まったばかりで今年で2回目の開催となるRISC-V Summitだが、昨今のRISC-Vブームとも呼べる世界的なムーブメントの勢いはとどまることを知らず、3日間で80以上のセッション、2,000人以上の来場者、50社以上のスポンサーが集まるイベントに急成長している。

イベント会期中にはRISC-Vエコシステムを形成する様々な企業・団体から、様々なアナウンスがあったが、ここではEDA-EXが注目した幾つかの話題について紹介したい。

■Western Digitalが世界初となるデュアルスレッドの商用組込みRISC-Vコアを発表

RISC-V Foundationの中心メンバーであり、今回のRISC-V Summitの最上位スポンサーであるWestern Digitalが新たなRISC-Vコア「SweRV Core EH2」、および「SweRV Core EL2」を発表した。

「SweRV Core EH2」は、世界初となるデュアルスレッドの商用組込みRISC-Vコアで、双方向スーパースカラー・アーキテクチャ上で2つの同時スレッドの実行をサポート。既にリリースされている「SweRV Core EH1」と同じく32ビットの9ステージ・パイプラインのRISC-Vコアで、組込みAI、ストレージ・コントローラ、IoTアプリケーションなどに適している。

「SweRV Core EL2」は、16nmプロセスで.023mmという4ステージ・パイプラインの超小型コアで、コントローラーSoCのシーケンシャル・ロジックやステートマシンの置き換えなどに適している。

また、Western Digitalは、同社の開発するRISC-V向けのネットワーク・プロトコル「OmniXtend」の新たなリファレンスデザインも発表。「OmniXtend」は、イーサネット・ファブリック上でキャッシュコヒーレント・メモリを提供するオープンなプロトコルで「SweRV」ファミリのRISC-Vコアとともに、Linux FoundationがホストするCHIPS Allianceプロジェクトに管理が委ねられている。

■「OpenHW Group」が「CORE-V Chassis SoC」プロジェクトを発表

RISC-Vベースのオープンソースコア「CORE-V」を提供する非営利組織「OpenHW Group」は、「CORE-V Chassis SoC」プロジェクトと呼ぶヘテロジニアス・マルチコアSoCの開発プロジェクトを発表した。

発表によると「CORE-V Chassis SoC」は、NXPのSoC「i.MXプラットフォーム」をベースに、Linux対応の64ビットRISC-Vコアと32ビットRISC-Vコアが組み合わされる構成で、2020年後半のテープアウトを目指しているという。

■WindRiverがVxWorksによるRISC-Vアーキテクチャのサポートを発表

WindRiverはRISC-V Foundationのメンバーとして参画し、既にMicrochipの「PolarFire SoC FPGA」、SiFiveのRISC-V IPコア製品などでVxWorksの実装を実現している。

■LatticeとSiFiveがコラボレーションを発表

LatticeとSiFiveのコラボレーションにより、28nm FD-SOIプロセスで製造されるLatticeの最新FPGA「CrossLink-NX」を含むLatticeのFPGAファミリ製品から、SiFiveの提供する「SiFive E2 Core」などのRISC-Vコアに簡単にアクセスできるようになるという。

■デンソー子会社のIPベンダNSITEXEがSmartDVのTileLink向け検証IPを採用

自動運転向けのデータフロー・プロセッサ(DFP)を手掛けるNSITEXEは、RISC-Vプロセッサで利用されるネットワーク・プロトコル「TileLink」の検証用IPをSmartDV社から導入した。その狙いは当然RISC-V製品の開発にあり、NSITEXEのDFPではRISC-Vコアが利用されているようだ。

■RISC-Vベースの新製品をアナウンスする各社

その他にも下記に挙げた企業など、RISC-Vエコシステム内の多くのプレーヤーが新製品のアナウンスを行なっている。

・Andes Technology:AndesCore 27-series CPU core

・Cobham Gaisler:NOEL-V processor

・GreenWaves Technologies:GAP9 IoT Application Processor

・Think Silicon:NEOX|V GPU

なお、RISC-V Summitの開催に先立ち、SiFiveが教育プログラムと教育用の開発パッケージを発表。

プレスリリース iFive FE310プロセッサを搭載するボードは、6,000円弱で予約受付中とのこと。

また、Imagination Technologiesは、10世代目のPowerVRにおいてGPUコアの制御にRISC-VベースのCPUコアを採用したことを発表している。

プレスリリース ■驚異の成長率で利用者が増えるRISC-V

調査会社Semico Reserchのレポートによると、RISC-VべースのCPUコアの利用数は2025年には累計624億個に到達する見通し。利用個数の平均成長率は2018-2025年で146.2%と、毎年倍以上の速さで利用数の増加が進む。RISC-Vベースコアを消費する最大セグメントはインダストリアル関連だという。

プレスリリース既にハードウェアの世界で大きな潮流となったRISC-V、今後の進化、そしてエコシステムの拡大からしばらく目が離せない。

2019.12.06

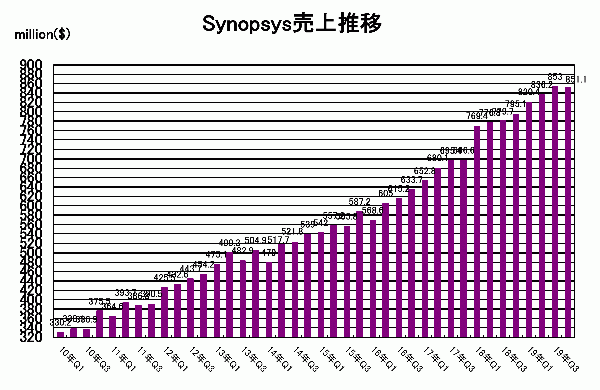

2019年12月4日、Synopsysは、2019会計年度第4四半期(19年8-10月)の四半期決算を報告した。

発表によるとSynopsysの2019会計年度Q4の売上は、前年同時期比約7%増、前Q3比約0.2%減の8億5110万ドル、営業利益は前年比約37%減の1億6070万ドルだった。(※GAAP基準による会計結果)。Synopsysは2019年Q3まで7四半期連続で四半期売上記録を更新し続けていたが、ついに記録更新が止まった。

Synopsysの2019会計年度の売上額は前年比約7.7%増の33.6億ドルで過去最高を記録。営業利益は前年比23%増の5億3240万ドルだった。(※GAAP基準による会計結果)

SynopsysはこのQ4において、車載ソフトウェア開発向けのシミュレーション環境を手掛ける独QTronic社の買収、クラウドベースの機能検証に関するGoogle Cloudとの協業、自動車向けAIに関するInfineonとの提携、TSMCおよびSamsungファウンドリとの5nmプロセスに関する協業などを発表している。

2019.12.05

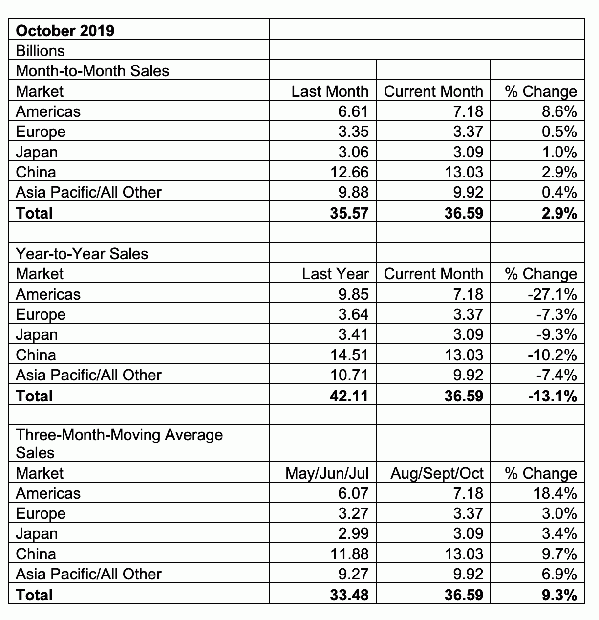

2019年12月3日、米SIA(Semiconductor Industry Association)は、2019年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年10月の世界半導体売上は、前年同月比13.1%減、前月比2.9%増の365.9億ドルという結果だった。この売上高は今年1月以降で最高額。売上実績の前年割れは2018年11月以降12ヶ月連続となっているが、7月以降は3ヶ月連続でわずかながら前の月の実績を上回っており、市場が緩やかに回復している傾向が見られる。

なお、先日12月3日に発表された

WSTS秋季半導体市場予測によると、2019年の世界半導体市場は前年比マイナス12.8%の約4090億ドルとなる見通し。二桁のマイナス成長はITバブル崩壊後の2001年以来になるという。来年2020年については、現時点で5.9%のプラス成長を予測している。2019年の日本の半導体市場は、円ベースで前年比-12.7%の約3兆8,521億円。2020年は+1.7%の約3兆9,162億円と予測している。

2019年10月の売上を地域別で見ると全ての地域で前年実績は割り込んだが、9月実績は上回った。落ち込みの激しかった北米市場もここのところ堅調に売上を回復しつつある。

日本市場の10月の売上は前月比1%増、前年比9.3%減の30.9億ドルで、売上を円ベースで換算すると前月比2.2%増、前年比約12.6%減の約3,361億円となる。

2019.11.22

2019年11月20日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、新製品「S10 10M Prodigy Logic System」のリリースを発表した。

「S10 10M Prodigy Logic System」は、発表間もないIntelの14nm FPGA「Stratix® 10 GX 10M」を搭載するプロトタイピング・ボードで、S2Cは「S10 10M Prodigy Logic System」ファミリとして、シングル、デュアル、クアッド構成の3種類のシステムを用意。シングル構成の「S10 10M Prodigy Logic System」は即日出荷可能としている。

「Stratix® 10 GX 10M」のロジック・エレメント数は1,080万で、同FPGAシングル構成の「S10 10M Prodigy Logic System」は、最大8,000万ASICゲートのデザインに対応可能。同FPGAを4個用いるクアッド構成のシステムだと最大3億2,000万ゲートのデザイン容量となる計算だ。

※写真は開催中のET2019で展示されていたS10 10M Prodigy Logic System」の実物

シングル構成の「S10 10M Prodigy Logic System」の汎用I/O数は1,184で最大1.4Gbps、高速トランシーバーは40個搭載で最大16Gbpsのパフォーマンスを実現。カタログスペック上の最大動作周波数は350MHzとなっている。また同プロトタイピング・システムは、USBまたはEthernetを用いたリモート管理機能を備えており、FPGAコンフィギュレーション、システム監視、リモートテストなどのほかに電源のオン/オフなども制御できるという。

「S10 10M Prodigy Logic System」を利用するための周辺環境としては、6世代目となるデザインの実装・検証環境「Prodigy Player Pro」やデバッグモジュール、各種IP、80種以上のドーターカードなどが用意されている。

「Stratix® 10 GX 10M」を搭載するプロトタイピング・ボードは、時同じくして独ProDesignも発売を発表しているが、日本国内での供給については不明。一方でS2Cは日本での発売を明言しており、聞くところによると既に日本には同社のStratix 10搭載システムを導入している大口顧客がいるという。

※S2Cジャパン株式会社

2019.11.20

2019年11月19日、ハードウェア設計言語・技術の標準化団体米Accellera Systems Inisiativeは、UVM-AMSワーキング・グループの発足を発表した。

UVM-AMSワーキング・グループは、デジタル設計で標準化されている検証メソドロジUVM(Universal Verification Methodology)をアナログ/ミックスドシグナル設計向けに拡張するために立ち上げられたグループで、UVMに基づく統一されたアナログ/ミックスドシグナル検証方法の標準化を目指す。

具体的な活動としては、まずUVM-AMSの業界要件の取りまとめを行い、標準化の取り組みの範囲に関するホワイトペーパーを作成。その後に、UVM-AMS標準を定義する言語リファレンスマニュアル、リファレンス・インプリメンテーションの作成を行う。

2019.11.19

2019年11月18日、FPGAベースのプロトタイピング・システムを手掛ける独ProDesignは、新製品「proFPGA quad Stratix® 10 GX 10M system」の発売を発表した。

「proFPGA quad Stratix® 10 GX 10M system」は、先日発表されたばかりのIntelの14nm FPGA「Stratix® 10 GX 10M」を4個搭載するプロトタイピング・ボードで、最大240M ASICゲートのデザイン容量を誇る。これは同社既存の最上位製品の2倍にあたる容量で、同ボードを9枚接続することで最大20億ASICゲートの容量に拡張できる。I/O数は8,304で192個の高速シリアルトランシーバーを備え、単一FPGAの最大システム速度は最大500MHzを保証。システムのポイント・ツー・ポイント・パフォーマンスは、標準のI/Oを介して最大1.4Gbps、高速シリアルトランシーバーを介して最大17.4Gbpsを実現する。

※画像はProDesign提供のデータ

ProDesignによると「proFPGA quad Stratix® 10 GX 10M system」は、前世代のproFPGA製品と完全に互換性があり、ほぼ全てのproFPGAマザーボード、FPGAモジュール、ドーターカード、およびアクセサリを組み合わせて使用することが可能。さらに、新しいIntel®Stratix®10 GX 10Mデバイスと既存のIntelStratix®10 GX 2800およびArria®10 FPGAを同じシステム上で組み合わせて使用することもできる。

新製品は、2019年11月から早期顧客に提供を開始。一般リリースは2020年1月を予定している。ProDesign社の製品は、日本国内ではプロトタイピング・ジャパンが代理店として販売している。

2019.11.19

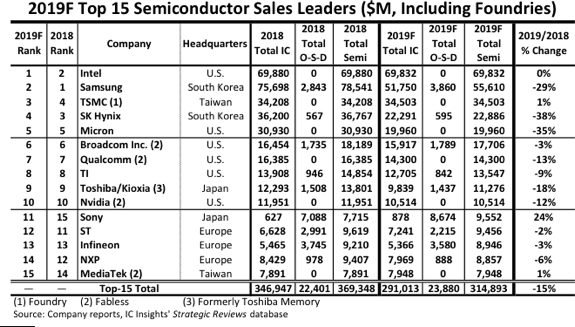

2019年11月18日、市場調査会社IC Insightsは、今年の半導体売上ランキング予測を発表した。

発表によるとTop10の顔ぶれは変わらず、変わったのは昨年首位のSamsungと昨年2位のIntelが位入れ替わったのみ。Intelの売上は前年と同水準だが、メモリ主体のSamsungが前年比マイナス29%と大きく売上を落としているため首位に返り咲いた。

※画像はIC Insights Web上のデータ

日本勢では9位の東芝のほかにイメージセンサーが絶好調のSonyが躍進する見通し。Sonyは売上前年比プラス24%で昨年の15位から11位までランキングを上げる。大きく冷え込んだ今年の半導体市場の中、前年比の売上成長率ではただ一社Sonyだけが大きな成長を見せている。

2019.11.18

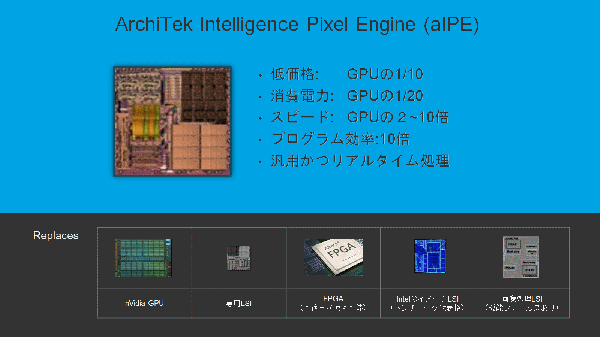

2019年11月18日、RISC-VベースのIPコアを手がけるSiFiVeは、同社の日本代理店DTSインサイトと共同で日本のAI向けIPベンチャーArchiTekとのパートナーシップを発表した。

ArchiTekは2011年設立の大阪に本拠を構える日本のIPベンチャーで、「aIPE(ArchiTek Intelligence Pixel Engine)」と呼ぶエッジAI向けのプログラマブルな画像処理エンジンを開発している。「aIPE」は独自の仮想エンジン技術と独自のアクセラレーター/GPUを用いた画像処理エンジンで、汎用性の高さ、プログラミングの容易性、高性能、低消費電力、低コストと仕様上は非の打ちどころのない製品となっている。

※画像はArchiTek Webページ上のデータ

発表によるとArchiTekは、次世代の「aIPE」を用いたSoCの開発でRISC-Vベースのプロセッサ「SiFive Core IP」と同開発環境「SiFive Core Designer」を導入。同SoCには最近SiFiveが発表したセキュリティ・プラットフォーム「SiFive Shield」の実装も検討しているという。なお、SiFive社の代理店DTSインサイトがローカルサポートとして、SiFiveのIPと環境を活用したArchiTekのSoC開発を支援していく。

Architek CEO兼CTO 高田周一氏のコメント。「SiFive Core IPが提供する優れたパフォーマンス、省電力、省スペースにより、次世代aIPE SoCが容易に市場に受け入れられることが期待できます。」

ArchiTekは今週20日からパシフィコ横浜で開催されるET2019に出展し、同社のエッジAI向け画像処理エンジン「aIPE」を展示する予定。DTSインサイトも同じくET2019にて展示ブースを構える。

2019.11.18

2019年11月14日、Wave Computingは、MIPS Open Initiativeの即時閉鎖を発表した。公なアナウンスではなく、MIPS Open Initiativeに登録しているユーザーへメールで案内を行った。

MIPS Open Initiative閉鎖の理由は明らかにされていないが、MIPSコアなどMIPS Open Componentsの無料ダウンロードは既に中止されており、Wave Computingは今後これらを用いた開発は制限することを推奨しているとのこと。既にダウンロードされたMIPS Open Componentsと現在アクティブなライセンスは引き続き利用を認定されるという。

MIPS Open Initiativeは、MIPS命令セット・アーキテクチャのオープンソース化を目的に立ち上げられた活動で、昨年12月にその計画が発表され、今年3月からMIPS Open Componentsの無償公開が開始されていた。

MIPS Open Initiativeが立ち上がった背景には、ご存知の通りオープンソースのISA「RISC-V」の隆興/流行があるが、実際に行われたMIPSのオープン化は真にオープンなRISC-Vなどとは異なり、"オープンユース"と呼ぶライセンスの下でISAが提供される形であり、商用利用するには開発者として登録し「MIPS Open CERTIFIED Independent Core」として認定される必要があった。

また、MIPS Openパーツの開発者に対して、MIPSの特許を妨害するサードパーティーの支援を行わないという、永久かつ取り消し不能な同意を必要とするなど、オープンソースとしながらもユーザーに疑問を持たれる部分があった。活動閉鎖の理由は不明だが、少なくともRISC-Vのように多くのユーザーに支持され受け入れられる活動にはならなかったという事だ。

2019.11.18

2019年11月11日、Synopsysは、ファブレス半導体ベンダeSiliconの資産買収を発表した。

Synopsysによると買収するのは、TCAM(Ternary Content Addressable Memory)、マルチポート・メモリー・コンパイラなど組み込みメモリ関連のIP資産と、高帯域幅メモリー・インターフェイスなどのインタフェースIP資産。合わせてR&DのエンジニアもSynopsysに移籍するという。eSilicon社の本体はInphi Corporationが買収することを発表している。

Synoposysの買収案件もう一つは、DINI Groupの買収。Synopsysは11月15日にDINI Groupの買収完了を発表した。

DINI GroupはFPGAベース・プロトタイピングボードの老舗で同分野の草分け的な存在。Xilinxベース、Alteraベース、両タイプのFPGAボードを提供しており、日本国内にも長年複数のユーザーを抱えていた。

2019.11.05

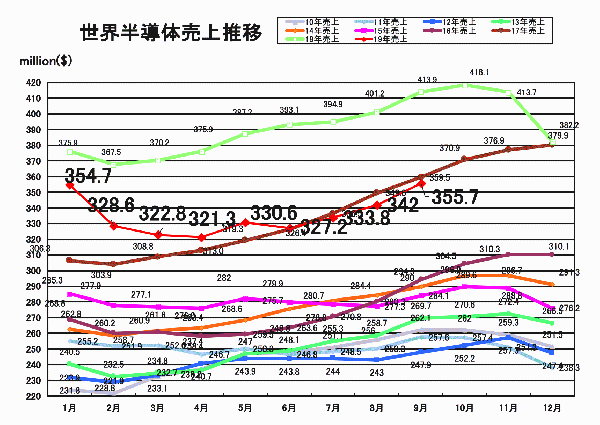

2019年11月1日、米SIA(Semiconductor Industry Association)は、2019年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年9月の世界半導体売上は、前年同月比14.6%減、前月比3.4%増の355.7億ドルという結果だった。この売上高は8月実績を抜いて今年1月以降で最高額。一方で売上実績の前年割れは2018年11月以降11ヶ月連続。7月、8月、9月と3ヶ月連続で2017年の売上水準を下回っている。

2019年9月の売上を地域別で見ると全ての地域で前年実績は割り込んだが、8月実績は上回った。四半期売り上げを見てもQ3実績(7-9月)はQ2実績(4-6月)を8.2%上回り計1,067億ドルに達した。

日本市場の9月の売上は前月比1.2%増、前年比10%減の30.6億ドルで、売上を円ベースで換算すると前月比0.8%減、前年比約13.6%減の約3,289億円となる。

2019.10.31

2019年10月29日、Synopsysは、同社のFPGAベース・プロトタイピング・システム「HAPS-80」の出荷台数が3000台を超えたと発表した。

「HAPS-80」は、Xilinx社の20nm FPGA「Virtex UltraScale VU440」を搭載するプロトタイピング・システムで、最大16億ASICゲートのデザインを実装する事が可能。一般リリースされたのは2015年9月。Synopsysによると半導体上位10社中の9社を含め世界100社以上の企業で採用されているとの事。日本国内にも多数のユーザーがおり、NECや理研がスパコン開発でHAPSを導入といった事例もある。

HAPSの歴史を遡ると、HAPSを世に送り出したのはスウェーデンHARDI社で、その後2007年に同社をSynplicity社が買収。更に2008年にSynplicity社をSynopsysが買収した事によってSynopsysの製品ラインナップに加わった。Synopsys製品となって以降、HAPSは様々なエンハンスが行われそのアーキテクチャも刷新。インプリ環境、周辺のデバッグ環境なども含め最新のHAPSは名実ともにSynopsysオリジナルの製品となっている。

2019.10.25

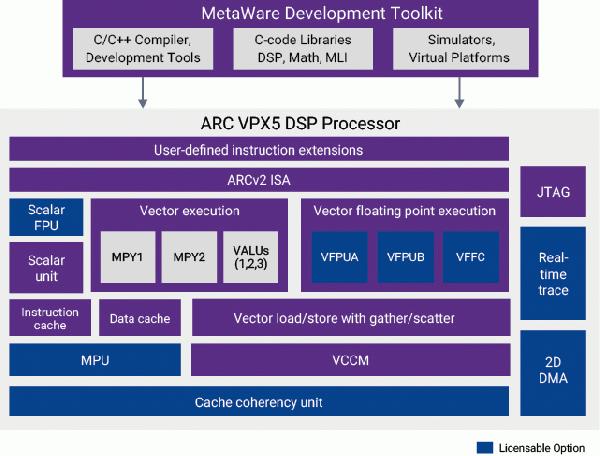

2019年10月22日、SynopsysはARCプロセッサファミリの新製品「ARC VPX DSP」を発表した。

今回発表されたのは、「ARC VPX5 DSP」と「ARC VPX5FS DSP」の2品種。共に高度な信号処理性能が要求されるRADAR/LiDAR、センサー・フュージョン、ベースバンド通信などをターゲットとしていて、命令セットが最適化されている。

特長は以下の通り。

・高性能32ビットスカラー実行ユニット、512ビット複数ベクター演算ユニット、およびオプションのベクター浮動小数点ユニットを統合。

・VLIW/SIMDアーキテクチャをシングル/デュアル/クアッド・コアにコンフィギュラブルに実装可能。

・各コアで最大3つのベクター浮動小数点パイプラインを活用することが可能。半/単/倍精度の浮動小数点データ・タイプに対応。

・線形代数演算と行列演算専用のハードウェア・アクセラレータを搭載。

・ARC VPX5FS DSPには、セーフティー・モニター、ロックステップ機構、その他のハードウェア・セーフティー機能を搭載。

→ISO 26262 ASIL BならびにD基準に対応

※画像はSynopsys Web上のデータ

Synopsysが高性能DSPアルゴリズムに特化したDSP製品をリリースするのは今回が初めて。競合のCadenceは「ConnX B10/B20」という製品を提供している。

「ARC VPX5」は主要顧客向けに2020年Q1に、「ARC VPX5FS」は2020年Q2に提供が開始される予定。

2019.10.25

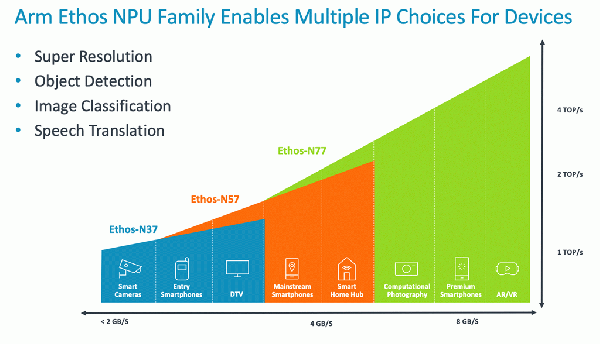

2019年10月23日、Armは新製品となるマシンラーニング推論向けの専用プロセッサ「Ethos-N57」および「Ethos-N37」を発表した。

Armは今回発表したマシンラーニング推論向けの専用プロセッサを「NPU」と呼び、「Ethos NPU」という新たな製品ファミリのラインナップとした。今回発表された二つのコア「Ethos-N57」および「Ethos-N37」は、ローエンドからミッドレンジのエッジ端末に向けられたもので、性能的には最初に発表されたArmの「MLプロセッサ」の下位製品となる。パフォーマンスと必要なメモリ帯域のイメージは以下の通り。「Ethos-N57」はマシンラーニングの性能と電力効率のバランスを重視したコア、「Ethos-N37」は小型化を意識した少面積のコアという位置づけとなる。なお、既存の「MLプロセッサ」は、今回の新ファミリ化に伴い「EthosーN77」と呼ばれるようになっている。

「Ethos NPU」ファミリがサポートするデータ型はInt8およびInt16。データの移動に伴う電力消費を抑えるために、独自のデータ管理技術を使用している。畳み込みアルゴリズムWinogradの利用などにより、他のNPUと比較して2倍以上の性能を実現できるという。

※画像はArm Web上のデータ

2019.10.23

2019年10月21日、Cadenceは、2019会計年度第3四半期(2019年7-9月)の売上を報告した。

Cadenceの2019年Q3売上は、前年比約9%増、前期Q2と同額の5億8000万ドルで営業利益は前年比約3%増の1億200万ドルだった。(※GAAP基準による会計結果)この実績は前Q2実績の報告時の予測通り。Cadenceは前の2019年Q2まで11四半期連続で四半期売上記録を更新し続けていたが、このQ3は記録を更新する事ができなかった。

CadenceはこのQ3以下のような製品及びニュースを発表している。

・タイミング制約およびCDCのサインオフ検証ツール「Conformal® Litmus」を発表

・業界初の電気・熱の協調シミュレーションソリューション「Celsius™ Thermal Solver」を発表

・デジタル設計フローとカスタム/アナログ設計ツールがTSMCのN6/N5/N5Pプロセスで認証

Cadenceは2019年Q4の売上を5億9000万-6億ドル、2019年の総売上を23億2700万-3700万ドルと予測。総売上については予測を上方修正した格好だ。

2019.10.02

2019年9月30日、米SIA(Semiconductor Industry Association)は、2019年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年8月の世界半導体売上は、前年同月比15.9%減、前月比2.5%増の342億ドルという結果だった。この売上高は今年1月以降で最高額となるが、売上実績の前年割れは2018年11月以降10ヶ月連続。7月に続いて8月も2017年の売上水準を下回った。

2019年8月の売上を地域別で見ると全ての地域で前年実績を下回ったが、7月実績と比較すると欧州市場以外は全ての地域で僅かながらプラスに転じた。3ヶ月ごとの売上推移を見ても、3-5月売上に対して6-8月売上は3.5%増と伸びている。

日本市場の8月の売上は前月比1.1%増、前年比11.5%減の30.1億ドルで、売上を円ベースで換算すると前月比0.8%減、前年比約3.3%減の約3,198億円となる。

2019.09.25

2019年9月25日、各種組込みソフト開発ソリューションを手がけるDTSインサイト(旧横河デジタルコンピュータ)は、RISC-VベースのIPを手がける米SiFive社とのパートナーシップ契約を発表した。

発表によるとDTSインサイトはSiFiveとのパートナーシップ契約により、日本国内における唯一の販売代理店として、SiFiveのRISC-VベースIP及び専用開発ツールの販売を行う。

SiFiveは既に世界7ヶ国に12の拠点を持ち自社IPの拡販を進めており、そのチップ化実績は300を超える。基本的にはクラウドベースの環境を通じて顧客のニーズに応じたカスタムコアを提供するビジネス形態をとっているが、各拠点ではCPUコアの提供と合わせてチップ開発全体の顧客サポートを行っている。

DTSインサイトは既に新規事業としてLSI設計サービスの開始を表明しており、代理店としてSiFive製品を販売するだけでなく、SiFiveのIPを用いたチップ開発を包括的にサポートしていく予定。

※DTSインサイトのSiFiveビジネスについては、後日別途レポート記事を掲載します。

2019.09.20

2019年9月18日、中国のファブレスFPGAベンダGowin Semiconductorは、自社FPGAを用いたAIアクセラレーション・ソリューション「GoAI」を発表した。

発表によるとGOWINの「GoAI」は、エッジのAI推論処理のアクセラレーションをターゲットにしたソリューションで、標準的なMCUによる処理と比較して78倍のパフォーマンスを提供可能とうたっている。

パフォーマンスと合わせてGOWINが強調するのはその容易な開発フローで、CaffeおよびARM CMSIS-NNフレームワークとGOWINの独自のインプリツールを接続することで、トレーニング済みの推論モデルを簡単にGOWIN FPGA内のマイクロコントローラー(Arm Cortex-M3)でテストし、FPGAファブリックを用いて高速化することが可能。「GoAI」のアクセラレータには、アクセラレータ制御用のAHBインターフェイス、MIPI CSI-2カメラやI2Sマイクなどを接続するための各種インターフェイスが備えられているという。

GOWINは発表した「GoAI」のデモを10/8からサンノゼで開催されるARM Techcon 2019で披露する予定。

2019.09.20

2019年9月18日、ASICデザインサービスを手掛ける台湾のファブレス半導体ベンダFaraday Technologyは、SoC設計サービスのプロジェクト件数が3年連続で倍増したと発表した。

Faradayによると、好調なSoCのプロジェクトの中心は28nmおよび40nmプロセス製品で、顧客にとっては先進プロセスよりも参入障壁が低く、生産コストにおけるFaradayの競争力がビジネスの強みとなっているとのこと。

FaradayはプラットフォームベースのSoCデザインサービスの開発や独自の内製IPの開発に力を注いでおり、AI FPGA-to-ASICソリューション、IoT向けSoCプラットフォーム、RISC-VベースASICプラットフォームなどを提供している。

2019.09.19

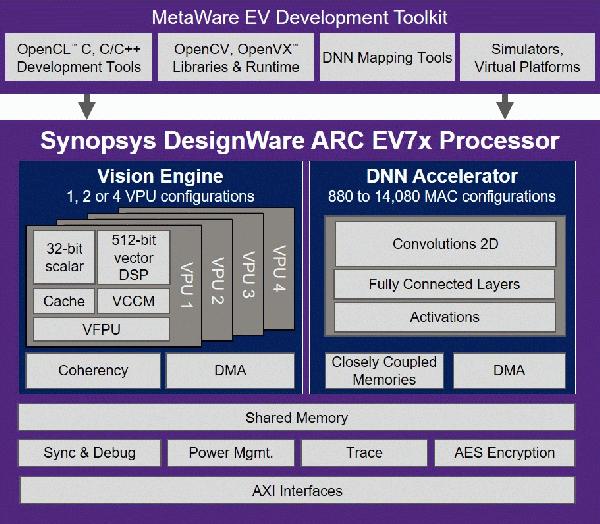

2019年9月16日、Synopsysは組み込みプロセッサIPの新製品「DesignWare ARC EV7x Vision Processor」を発表した。

新製品「ARC EV7x Vision Processor」は、DNNエンジンを搭載したエッジAIアプリケーション向けの組み込みプロセッサIPで、約2年前にリリースされた既存製品「EX6x」のパフォーマンスを刷新したもの。32ビットのスカラユニットと512ビットのベクターDSPを組み合わせたVPUコアを最大4個利用できるビジョン・エンジン部とオプションのDNNエンジン部からなるヘテロジニアスなアーキテクチャーは、基本的に「EX6x」と同じだがDNNエンジンとして搭載できるMAC数が最大14,040個と4倍に拡張された。ユーザーは用途に応じてビジョン・プロセッサのコア数(1-4個)とDNNエンジンのMAC数(880-14,040)を選ぶことができる。

Synopsysの説明によると「EV7x」はDNNエンジンのMAC数が増えただけではなく、MACの使用率やバンド幅の改善などによりエンジンの処理性能が向上されており、最大構成で業界最高水準の35TOPSの演算性能を実現(16nm FinFETプロセスで標準実装した場合)。パワーゲーティングによるローパワー化も施されており電力効率も向上しているという。

また、「EV7x」のDNNエンジンは、MobileNet、GoogLeNet、ResNet、Yolo、Faster R-DNN、ICNetなどの一般的なCNNのサポートに加えて、時間ベースの結果を必要とするLSTMをサポート。データ精度は8ビットおよび12ビットをサポートする。Synopsysは、ビジョン・エンジンとDNNエンジンで各種タスクを並列処理できる「EV7x」は、複数のカメラやビジョン・アルゴリズムが並列動作する自動運転システムやADASアプリケーションに最適だとしている。

「EV7x」には、オンチップ・メモリーからのデータ転送を保護するためのオプションとして「AES-XTS暗号エンジン」も用意されている。更に、機能安全規格ISO 26262 ASIL B/Dに準拠した製品「EV7xFS」も用意されている。開発環境としては「MetaWare EV Development Toolkit」を利用することでDNNの容易なマッピングが可能。処理タスクを利用可能なハードウェアリソースに自動的にディスパッチして、実行を高速化できる。

発表された「EV7x」のフル機能は主要顧客向けに2020年Q1より提供開始予定。3,520 MAC対応のDNNアクセラレータ・オプションは既に提供を開始している。

2019.09.18

2019年9月17日、図研は国内のAIベンチャーギリアとの資本業務提携を発表。ギリアは図研を引受先とする第三者割当増資を実施した。

ギリア株式会社は、株式会社UEI、株式会社ソニーコンピュータサイエンス研究所、WiL, LLCの三社によって2017年6月に設立されたAIベンチャーで、「ヒトとAIの共生環境の実現」を目指して、最先端の深層学習技術をあらゆる人が自在に使いこなせるOS及びハードウェアを含む統合プラットフォームの開発を行っている。

図研とギリアは、図研の子会社図研プリサイトの製品開発を通じて関係があり、図研プリサイトはギリアの深層学習を利用した自然言語解析技術を用いたフルオート型ナレッジ共有ソリューション『Knowledge Explorer Ver.1.0』をリリースしている。

今回の両社の提携は、図研の回路設計および基板設計を中心とした製造業向けソフトウェア製品へのAI技術の搭載を狙うもので、実際に中長期的なロードマップのもとで製品開発を進めていくようだ。

2019.09.18

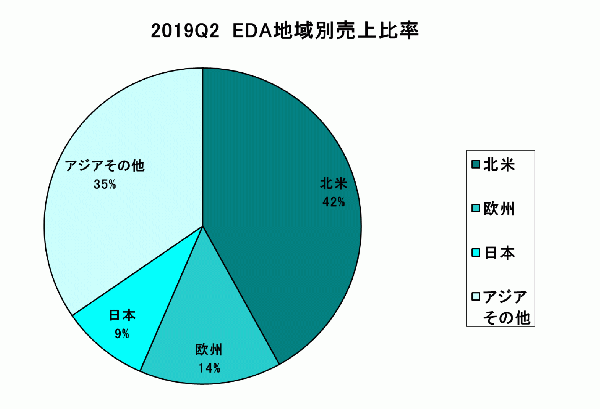

2019年9月17日、米ESD Allianceは、2019年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると2019年Q2(4-6月)の世界のEDA売上総額は、前年比約6.6%増、前19年Q1比約7.2%減の24億7210万ドルだった。

例年Q2実績はQ1実績を上回る傾向にあるが、前Q1は前年Q4実績を上回る好調な実績を残したためそれには及ばなかった。四半期売上が前年実績を上回るのはこれで2四半期連続。

2019年Q2のEDA売上をカテゴリ別に見ると、IP分野が大きく成長、C Physical Design & Verification分野、PCB分野も前年比プラス成長だった。

2019年Q2のEDA売上を地域別に見ると、アジアその他地域が前年比23.7%増と大きく成長。北米はQ1では前年比10%以上の成長だったが、Q2は一転前年比マイナス5.5%と落ち込んだ。

日本市場はマイナス10.1%で対前年比で売上の落ち込みが最も大きかった。円ベースで換算しても前年比8.5%程度のマイナスとなる。

2019年Q2時点でのEDA業界の従業員数は前年比6.3%増の44,342人で過去最高記録を更新した。

2019年Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 7億9380万ドル 3.2%Down

■IC Physical Design & Verification分野 5億10万ドル 7.1%Up

■IP分野 8億3500万ドル 19.7%Up

■サービス分野 9890万ドル 4.0%Down

■PCB/MCM分野 2億2430万ドル 5.6%Up

2019年Q2の地域別の売上と昨年同時期との比較は以下の通り。

■北米 10億3740万ドル 5.5%Down

■欧州 3億5890万ドル 0.9%Up

■日本 2億2070万ドル 10.1%Down

■アジアその他地域 8億5510万ドル 23.7%Up

※ESDA(Electronic System Design Alliance)

-thumb-600x420-5450.jpg)