NEWS

2021.03.04

2021年3月3日、ソシオネクストは、米Leopard Imaging社による画像処理プロセッサの採用実績を発表した。

米Leopard Imaging社は、組み込みカメラモジュールを幅広く展開するグローバル企業。

今回同社のエッジAIビデオ解析用のカメラモジュール「EdgeTuring」において、ソシオネクストの画像処理プロセッサ「SC2000」が採用された。

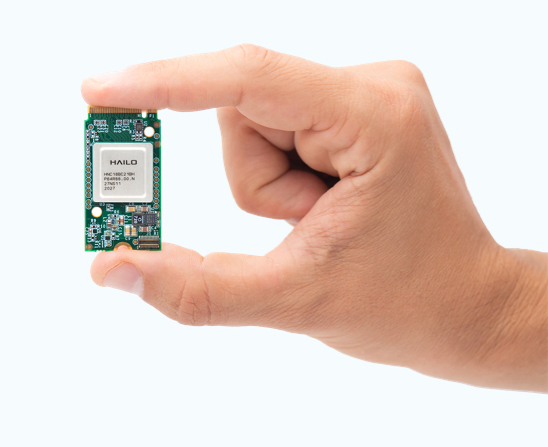

「EdgeTuring」はソシオネクストの「SC2000」とイスラエルHailo社のAIアクセラレータ「Hailo-8 M.2」を組み合わせて利用することで、高性能かつ低消費電力なAIビデオ解析を実現。AWSの提供するIoT向けクラウドサービス「Amazon Kinesis Video Streams」、「Amazon Kinesis Data Streams」を用いて、エッジでのビデオ解析結果を様々な用途に簡単に展開できる。主に産業用オートメーション、スマートデバイス、スマートリテールなどの分野がターゲットのようだ。

ソシオネクストは「EdgeTuring」以外にもLeopard Imagingの組み込みカメラモジュールに画像処理プロセッサを提供している。また、HailoとはFoxconnのエッジ・コンピューティング・ソリューション「BOXiedge」の開発においても協業した実績がある。

2021.03.03

2021年3月2日、SoCのテストケース自動生成ツールを手掛けるBreker Verification Systemsは、新製品「Synthesizable VerificationOS」を発表した。

Brekerの新製品「Synthesizable VerificationOS」は、オペレーティング・システムのようなサービスをテストコンテンツに自動的に組み込み、複雑なSoC検証のテストを実行・管理するもの。ソフトウェアとハードウェアの両方を同時実行させる複雑なコーナーケースの機能テストにおいて効力を発揮するという。

「Synthesizable VerificationOS」は、シミュレーション、エミュレーション、プロトタイピング・プラットフォームで利用可能。テストコンテンツとSoCモデルの間で動作するOSライクなメカニズムを提供してくれるため、プロセッサを駆動する必要があるSoC検証を簡素化しファームウェアの検証などにも活かせるという。

2021.03.03

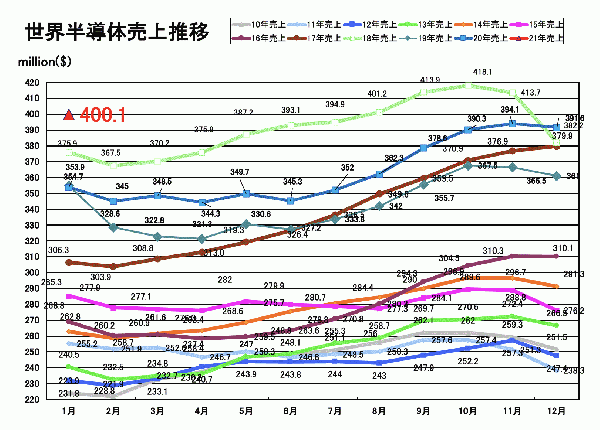

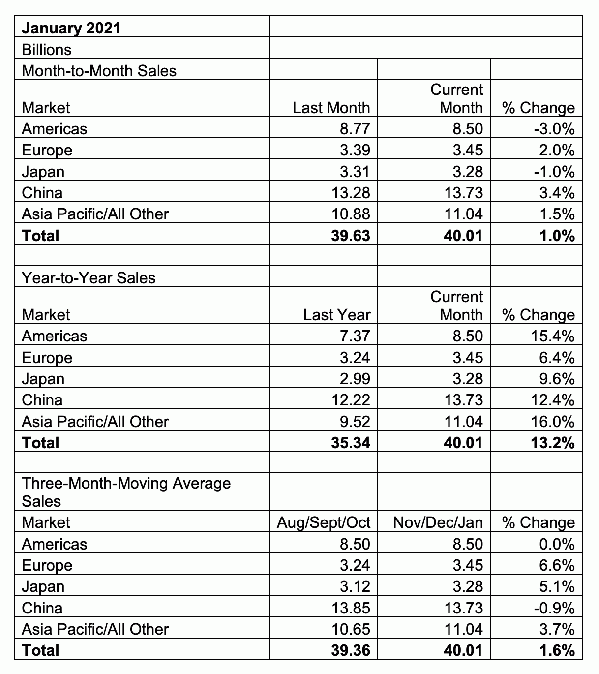

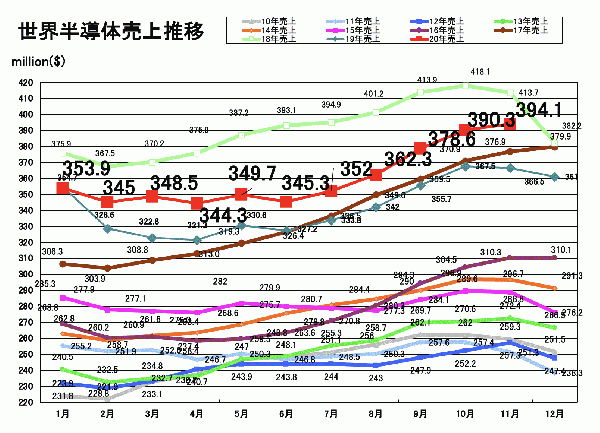

2021年3月1日、米SIA(Semiconductor Industry Association)は、2021年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年1月の世界半導体売上は、前年同月比約13.2%増、前月比約1%増の400.1億ドルだった。この実績は1月の売上としては過去最高。単月売上が前年同時期を超えるのは12ヶ月連続となる。

2021年1月の世界半導体売上を地域別にみると、全ての地域で売上前年比増を達成。成長率では北米、中国、アジアその他地域がいずれも前年比2ケタ増と好調だった。

日本市場は12月を上回る成長率で前年比9.6%増と好調を維持した。売上を円ベースで換算すると前月比約0.8%減、前年比約4%増の約3,400億円となる。日本市場の売上が前年同月比プラス成長となるのは3か月連続となる。

2021.03.03

2021年3月1日、Wave Computingは破産手続きが完了し、MIPSとして事業を再スタートすることを発表した。

破産手続きを進めていたWave Computingは、カリフォルニア北部地区連邦破産裁判所により連邦破産法第11章の再編計画が承認された。

破産オークションにより、トールウッドベンチャーキャピタルが6100万ドル相当の入札で再編された会社の過半数の所有権を取得。Wave Computingは、MIPSとして再編され事業を再スタートすることになった。

MIPSは、RISC-Vベースの新たな第8世代アーキテクチャを開発しているという。

2021.03.03

2021年3月2日、LinuxFoundationとRISC-V InternationalはRISC-V ISAの無料オンライン・トレーニングのリリースを発表した。

リリースされたオンライン学習コースは下記2種類で、オンライン学習プラットフォーム「edX.org」で利用可能。

いずれのコースも7週間の無料コースで149ドルを支払うと履修の証明書が発行され、1年間コースへのアクセスと追加のコンテンツが提供される。

2021.03.02

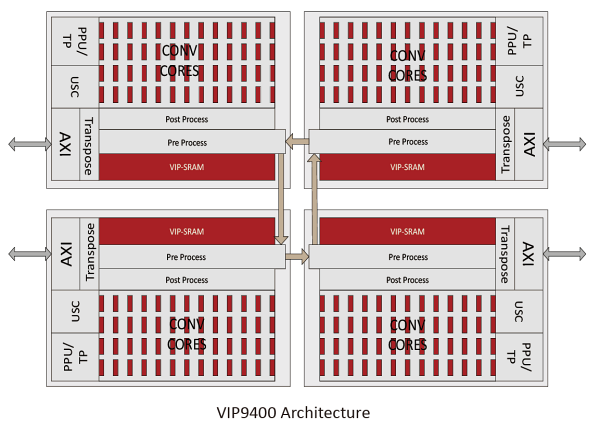

2021年3月1日、チップ設計とIPを手掛ける中国VeriSiliconは、新たなビデオ処理ソリューションを発表した。

新たなビデオ処理ソリューションは、データセンターをターゲットとしたもので、同社の主力IPの一つであるビデオ・コーデックIPの最上位品「Hantro VC9000」の最新バージョンと新型のニューラル・ネットワーク・プロセッサ「VIP9400」を組み合わせたもの。

VeriSiliconのVIPシリーズは、ニューラル・ネットワーク・エンジンとテンソル・プロセッシング・ファブリックで構成されているが、既存製品「VIP9000」の後継上位モデルとなる「VIP9400」には、プログラマブルな並列処理ユニット(PPU)も用意されている。PPUおよびMAC数はスケーラブルに選択可能で、同社のビデオIPやISP IPなどと組み合わせて利用できる。「VIP9400」のターゲットはデータセンターと車載用途で最大200TOPSの演算能力(INT8,1GHz)を提供。OpenCL 3.0とOpenVX 1.2に準拠している。

なお、VeriSiliconの説明によると、同社のビデオ・コーデックIP「Hantro」シリーズは、クラウドプラットフォーム・ソリューションプロバイダーの上位20社のうち12社、インターネットプロバイダーの上位5社のうち3社が採用しているという。

ちなみにVeriSiliconは、Arm, Synopsys, Cadence, Imagination Technologies, CEVAに次ぐ業界第6位のIPベンダでもある。

2021.03.01

2021年2月3日、設計/検証IPを手掛けるインドのSmartDVは、2020年の営業実績について発表した。

SmartDVによると、同社は業績好調で2020年の売上は前年比51%増を達成、新たに獲得した顧客は前年の倍以上の26社となった。

SmartDVの主力製品は数百種類にもおよぶ検証IPだが、最近は設計IPへの関心も高く2020年は需要が300%増加したとのこと。設計IPでは2020年にMIPIやUSBインターフェース用のIPもリリースし、既にシリコン実績を残している。

なお、SmartDVの日本代理店株式会社ネクストリームによると、SmartDVは子会社を設立してRISC-V、5G、8K向けプロトコルの設計IP開発に注力しているとの話。また、SmartDVは各種オートモーティブ向けの設計/検証IPも展開しているが、それら全てのIPに対してISO26262の認証を取得する計画だという。

2021.03.01

2021年2月17日、インターコネクトIPを手掛けるArteris IPは、2020年の営業実績について発表した。

Arterisによると、2020年に獲得した同社IPの新規ライセンシーは計28社。これは同社過去最高の契約件数で累計ライセンシーは159社に到達。

ArterisのIPは、自動車、機械学習、5Gおよびデータセンター向けSoCなどで需要が伸びている様子。ArterisのIPを用いたSoC設計のプロジェクトは、これまでの累計で500チップを超えているという話だ。

なお、Arterisのライセンシーを地域別で見ると中国企業が最も多く40社を超えている。

日本国内では東芝、京セラ、メガチップス、ソシオネクスト、ルネサスの他に、カメラOEMなどもArterisのインターコネクトIPを利用している。

2021.02.26

2021年2月24日、IC Insightsのレポート:

ウエハサイズ別にまとめられたランキングによると、300mmウエハのキャパシティではSamsungがトップで2位TSMCの順。TSMC以外、Top5にはメモリベンダの名が並ぶ。

200mmウエハでは、TSMC、UMC 、SMICというファウンドリ勢とアナログ/ミックスドシグナルIC、マイクロコントローラーを製造する老舗の半導体ベンダが僅差で名を連ねる。

150mm以下のウエハでは、アナログ/ミックスドシグナルIC、パワーデバイス、ディスクリート半導体などを製造する中国の半導体ベンダ2社が1位、2位となっている。

IC Insightsの統計によると、300mmウエハの製造設備を保有する企業は世界で28社、うち上位5社が300mmウエハの製造キャパシティの75%を占めているという。

2021.02.26

2021年2月25日、PCB設計ツールを手掛けるAltiumは、Amazon Web Services(AWS)を利用した新たなクラウドベース・ソリューションについて発表した。

Altiumは自社のクラウドベースのPCB設計プラットフォーム「Altium 365」をAWS上で利用できる形にした。

これまでは「Altium 365」により、独自のクラウド環境を用いてユーザー向けにデータ保存やバージョン管理、ワークスペースの提供などを行っていたが、AWS上に「Altium 365」をホストすることでその有用性を更に高めた。

Altiumによると「Altium 365」は、AWSがホストする最初のクラウドベースのPCB設計プラットフォームだという。

COVID-19の影響により、リモート環境で作業を行うケースも増えているため、このようなクラウドベースの設計環境は今後も普及していくことだろう。

2021.02.26

2021年2月25日、EETimesの記事:

2018年創業のカナダのAIチップ・ベンチャーUntetherAIは、今年Q3から同社のAI推論チップを搭載した商用アクセラレータ・カードを販売するという。

UntetherAIは、「AT-MEMORY COMPUTING」すなわちメモリ配列内にPE(プロセッシング・エレメント)を配置することで演算時のデータ移動に伴う消費電力を削減するアーキテクチャに加え、「ゼロ検出回路」を用いることで何かにゼロを掛けることでMACユニットが電力を浪費しないようにする手法により、大幅な電力削減を実現する。

16nmプロセスで製造される同社の推論チップ「RunAI200」を用いた推論パフォーマンスについては記事参照。先端プロセスを用いたチップではないが、パフォーマンス、電力性能において優れたベンチマーク結果を叩き出している。「RunAI200」は既にFinTech分野で実績があるようだ。

なお、2018年に3名で創業したUntetherAIは、現在従業員数60人、累計資金調達額は2700万ドルとなっている。

2021.02.26

2012年2月24日、Synopsysが新製品「ZeBu Empower」を発表した。

「ZeBu Empower」は、Synopsysのエミュレーション・システム「ZeBu」にパワー検証機能を追加した新製品で、発表にあるAMDのコメントをそのまま引用すると、「プレシリコン環境で実際のワークロード全体の電力消費を効率的にプロファイリングできるソリューション」ということだ。

現実的なソフトウェア・ワークロードを使って、プレシリコンの段階で電力消費を分析できるというのが「ZeBu Empower」を利用する最大のモチベーションで、設計サイクルの早い段階で電力バグのリスクやSoC電力目標のリスクを大幅に削減できる。

なおSynopsysの説明によると「ZeBu Empower」は、パワー・クリティカルなブロックとタイム・ウィンドウをSynopsysの「PrimePower」にフィードすることも可能。これにより、RTLパワー分析とゲートレベルのパワーサインオフを加速できるという。

2021.02.26

2012年2月22日、SynopsysがSamsungファウンドリによるツール認定を発表。

Samsungファウンドリは、Synopsysの物理検証ツール「IC Validator」を自社の先端プロセス4nm/5nm向けの物理検証ツールをとして認定した。

「IC Validator」は、高速DRCチェック、プログラマブルな電気ルールチェック、ダミーメタルフィルなどの機能を提供する。

「IC Validator」はSynopsysの設計環境「Fusion Design Platform™」および「Custom Design Platform」の一部として機能するため、サードパーティーの物理検証ツールよりも利用メリットが大きい。

2021.02.24

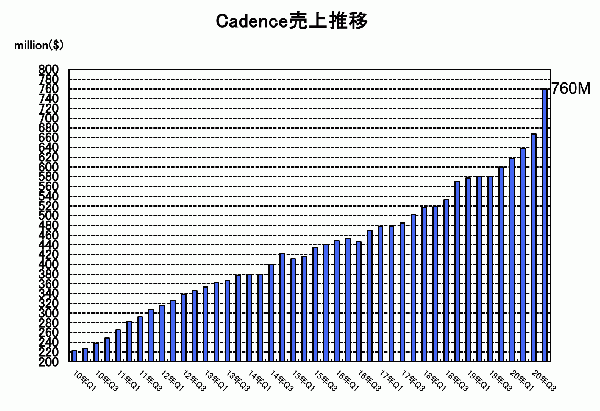

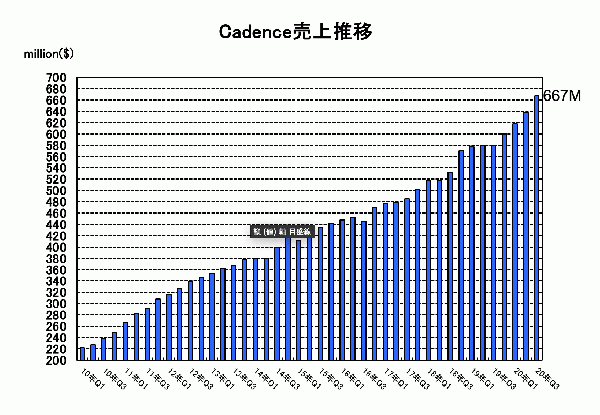

2021年2月22日、Cadenceは、2020会計年度第4四半期(2020年10-12月)の売上を報告した。

Cadenceの2020年Q4売上は、前年比約26.6%増、前期Q3比約14%増の7億6000万ドル、営業利益は1億7400万ドルだった。(※GAAP基準による会計結果)

このQ4実績は同社の四半期売上記録として過去最高を更新するもので四半期売上7億ドル超えは初。Q3売上に対して約1億ドルも積み増した形だ。ちなみに四半期売上記録の更新は2019年Q4以来5四半期連続となる。

Cadenceの2020会計年度(2020年1-12月)の総売上は前年比約24%像の26億8300万ドルで過去最高を更新。営業利益は5億9100万ドルだった。

2020年のCadenceの動きで目立ったのはシステム解析分野への投資で、企業買収や新製品の投入を積極的に進めていた。その動きは2021年に入っても継続されており、システム分野のソリューションは今後も拡張されていく見通しだ。

CadenceはこのQ4に以下のような新製品を発表している。

・検証IPの新たな製品群「Cadence® System-Level Verification IP (System VIP)」 を発表

・新製品「Cadence® Clarity™ 3D Transient Solver」の提供を開始

Cadenceは2021年Q1の売上を7億1000万-3000万ドル、2021年の年間売上を28億6000-29億2000万ドル程度と予測している。

2021.02.22

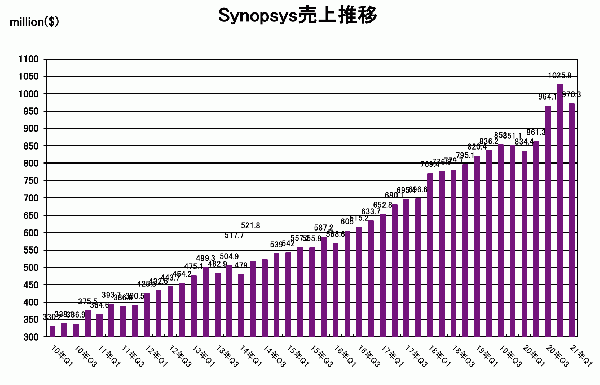

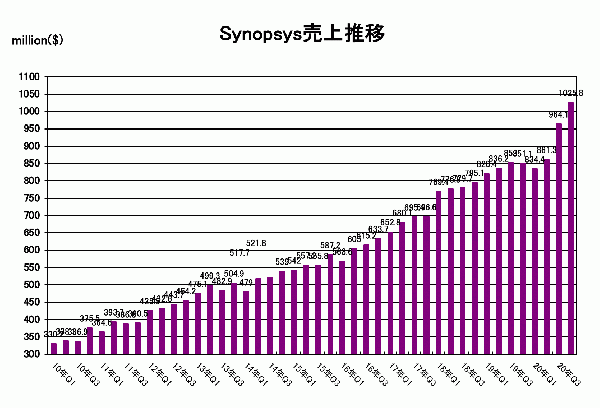

2021年2月19日、Synopsysは、2021会計年度第1四半期(20年11-21年1月)の四半期決算を報告した。

発表によるとSynopsysの2021会計年度Q1の売上は、前年同時期比約16.2%増、前Q4比約5.4%減の9億7030万ドルで、営業利益は前年比約56%増の1億6230万ドルだった。(※GAAP基準による会計結果)

SynopsysはこのQ1において、以下のような発表を行なっている。

・インチップ・モニタリング・ソリューションのMoortec社の買収

・AWSによるVCSの採用

・PCI Express 5.0およびCXL 2.0向けの暗号化セキュリティIPのリリース

Synopsysは、来期Q2(2-4月)の売上を9億7000万-10億ドル、2021会計年度の売上を40億-40.5億ドルと予測している。

2021.02.19

2021年2月16日、Design Automation Conferenceの実行委員会は、今年7月に予定していた第58回DACの開催を12月に延期することを発表した。

DACは昨年COVID-19の影響で初の完全バーチャル・イベントとしてカンファレンスを開催。今年はサンフランシスコのMoscone West Centerにて、ライブイベントとしての復活を計画していた。今回のDAC実行委員会の延期判断は、COVID-19の影響による旅行制限と大規模な集会に対する州および地方の制限の継続を見越したもので、会場変更は行わずサンフランシスコで12月5日から9日までカンファレンスを開催する計画。なお次回の第58回DACでは、ライブイベントと合わせて昨年同様イベントのデジタル配信も実施する予定としている。

第58回DACの参加登録開始は9月7日の予定。現時点で第59回DACは2022年7月の開催を計画しているということだ。

2021.02.02

韓国紙コリアタイムスのレポートによると、SamsungはNXP、Infineon、TI、ルネサスのいずれかを買収して、自動車セクターでの地位を強化しようとする可能性がある。また、専業ファウンドリのGlobalfoundriesを買収する可能性がある。

SamsungのCEOは、1月28日の投資家との電話会議でM&Aの準備が進んでいる一方で、大規模な設備投資も行われると語った。

自動車用半導体は、Samsungの存在感が薄い高成長セクターで、Samsungが同市場の地位強化を狙うモチベーションとそのための資金は十分にある。

2021.02.02

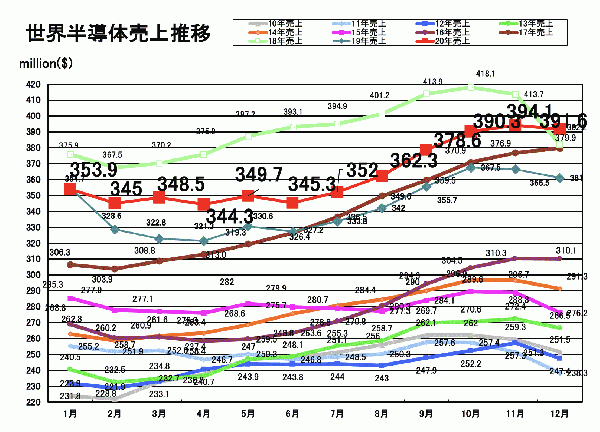

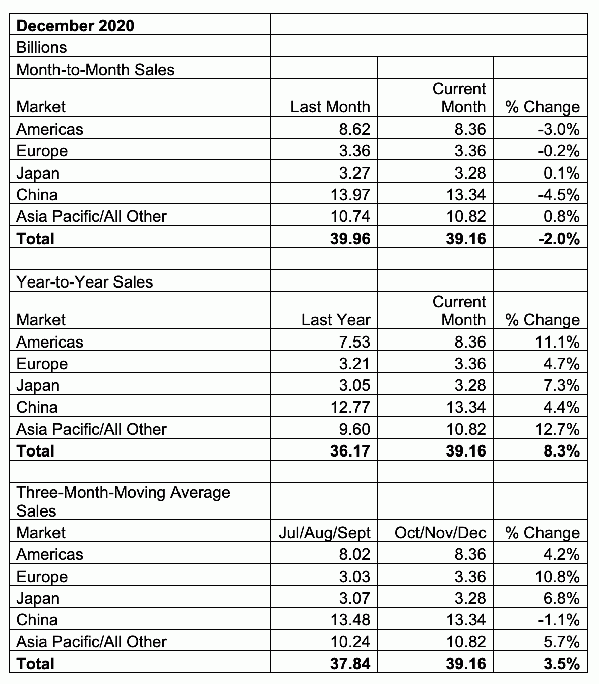

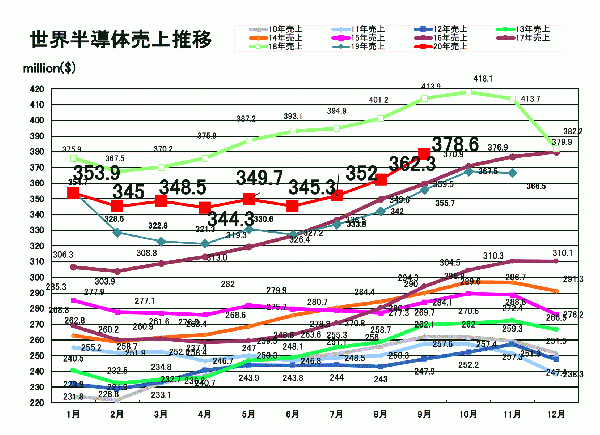

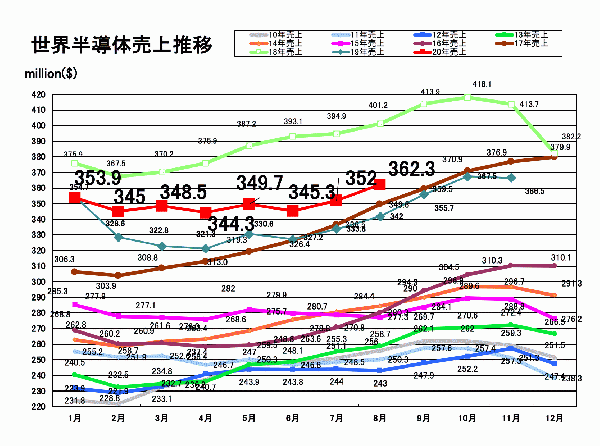

2021年2月1日、米SIA(Semiconductor Industry Association)は、2020年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年12月の世界半導体売上は、前年同月比約8.3%増、前月比約2%減の391.6億ドルだった。2020年の単月売上の記録を更新とはならなかったが、単月売上が前年同時期を超えるのは11ヶ月連続となる。

2020年の年間総売上は前年比6.5%増の4,390億ドルで、史上二番目の実績となった。

今年の半導体市場は、当初はパンデミックの影響で市場が落ち込むと見られていたが、PC/サーバー需要が伸びるなど市場には追い風が吹き、終わってみれば11月時点のWSTSの秋季予測を上回る結果となった。WSTSは春季予測で3.3%増、秋季予測では5.1%増と予測していた。ちなみに民間のGartnerは4月の時点で0.9%減のマイナス成長と予測を下方修正していた。

2020年の半導体売上の内訳を見ると、その半分以上、約54%はロジックとメモリの売上で、それぞれの売上額は、1,175億ドル(ロジック)、1,173億ドル(メモリ)だった。ロジック製品の年間売上は2019年と比較して10.3%増、メモリ製品の売上は10.2%増だった。メモリカテゴリ内では、NANDフラッシュの売上が際立っており、2020年は23.1%増の495億ドルだった。MCUを含むマイクロICの売上は、4.8%増の696億ドルだった。結果的にメモリ以外の製品カテゴリの売上合計は、前年比5.2%増を達成し、全てのカテゴリーは過去最高売上を更新した。

2020年12月の世界半導体売上を地域別にみると、全ての地域で売上前年比増を達成。成長率ではアジアその他地域が前年比12.7%増と好調を維持していた北米市場を上回った。北米市場の売上は前年比11.1%増で、売上が前年同月比で2桁のプラス成長となるのはこれで12ヶ月連続。

日本市場は11月に続いて前年比7.3%増と好調だった。売上を円ベースで換算すると前月比約0.5%減、前年比約2.3%増の約3,425億円となる。日本市場の売上が前年同月比プラス成長となるのは、11月に続いて2か月連続となる。

2021.01.28

Design Solution Forum 2020(DSF2020)は、2月12日(金)パシフィコ横浜アネックスホールで開催します。

幅広い分野に跨がる計50のセッションは全てオンラインで聴講できます。

様々な技術と人に出会えるDSF2020。

是非この機会にご登録頂き、エンジニア・コミュニティの拡大にご協力下さい。

今回のDSF2020では、2/12 パシフィコ横浜でのライブ講演のほかに、オンラインでご覧頂ける様々な特別企画を実施しています。

現役エンジニアのDSF2020実行委員による手作りコンテンツも是非お楽しみ下さい。

2020年にDSF実行委員に新たに加わった7人のメンバーの自己紹介です。

DSFは会社の枠を超えたエンジニア繋がりによって企画・運営されています。

一緒にDSFを盛り上げて頂ける有志のエンジニアを募集していますので、ご興味ある方は是非ご連絡下さい。

DSF2020に関連する講演者様やスポンサー企業など、様々な方にインタビューさせて頂きました。皆さん基本エンジニアで、ご自身や自社の技術について語って頂いています。

・EDGEMATRIX様

・ブルックマンテクノロジ様

・モルフォ様

・デンソー 渡辺様

・AIQ様

・リコー 登坂様

■DSF2020ネット配信の舞台裏

今回DSFがチャレンジする初の講演ライブ配信の舞台裏について、特集記事を公開しています。

実行委員の考えた講演配信システムにご興味お持ちの方は是非御覧ください。

DSF2020では、今後も特別企画として様々なコンテンツをイベントホームページに掲載していく予定です。

新規実行委員の自己紹介です。

個性豊かな実行委員のコメントをご覧ください。個性豊かな実行委員のコメントをご覧ください

2021.01.25

2021年1月21日、各種EDAソリューション及び設計IPを手掛けるSilvacoは、ウクライナのEDAベンダPOLYTEDA CLOUDの買収を発表した。

POLYTEDA CLOUDは2015年にウクライナで設立されたEDAベンダで、クラウドベースでスケーラブルな物理検証を実現するDRC/LVSソリューションを提供している。同社の起源は元Cadenceのエンジニアが立ち上げたカナダのEDAベンダPOLYTEDAで、当時からウクライナを拠点に高速DRCツールを開発していた。

SilvacoによるとPOLYTEDA CLOUDの買収は既に手続きを完了済。取引条件などの詳細は明らかにされていない。

Silvacoは積極的な買収戦略でEDAソリューションの拡充を続けており、昨年9月にもフランスのEDAベンダCoupling Wave Solutions(CWS)の技術資産の買収をし、アナログ・カスタムIC設計ソリューションを強化している。

2021.01.22

2021年1月20日、Cadenceは、CFD(数値流体力学)シミュレーションの大手ベルギーNUMECA International社の買収を発表した。

今回の買収に関して具体的な取引条件などは明らかにされていないが、買収手続きは2021年第1四半期に完了する予定で、NUMECAの製品、技術、人員はCadenceに移管される。

Cadenceは近年、システム解析領域のソリューション開発に力を注いでおり、3D電磁界解析ソルバー「Clarity™ 3D Solver」、3D FDTD電磁界解析ソルバー「Clarity 3D Transient Solver」、電気・熱の協調シミュレーション環境「Celsius™ Thermal Solver」など、次々と新製品を投入している。

Cadenceは今回のNUMECAの買収によってシステム解析ソリューションの更なる拡充を狙う。

2021.01.21

2021年1月19日、IC Insightsのレポート

米調査会社IC Insightsによると、2020年の世界半導体業界の研究開発費は、前年比5%増の684億ドルと過去最高を記録。2021年には前年比4%増の714億ドルになると予測されている。2021年から2025年の平均成長率は5.8%で、2025年には893億ドルに増加する見通しだという。

研究開発費ランキングでは、Intelが推定129億ドルでトップをキープしているが金額としては前年比約4%の減少、業界全体の研究開発費に占める同社のシェアは2019年の22%から2020年は19%に減少した。2020年のIntelの研究開発費の減少は、1990年代半ば以来最大の減少。2位のSamsungの研究開発費は前年比19%増の推定56億ドルで、研究開発費の増加は5nm以下の先端プロセスの開発強化が一因。ファウンドリビジネスでSamsungの先を行くTSMCの研究開発費は前年比24%増の推定37億ドル。

研究開発費トップ10は、Intel、Samsung、Broadcom、Qualcomm、Nvidia、TSMC、MediaTek、Micron、SK Hynix、AMDの順で、合計すると前年比11%増の435億ドルで業界全体の64%を占めている。 Nvidiaは昨年の6位から5位、MediaTekは9位から7位、Advanced Micro Devicesは11位から10位にランキングを上げた。

トップ10のR&D/セールスのR&D投資比率は、2019年の15.0%に対し、2020年は14.5%だった。

2021.01.20

2021年1月12日、ソシオネクストとSynopsysの両社は、SynopsysのDesignWare® IPの活用に関する協業の拡大を発表した。

発表によるとソシオネクストは、5nmプロセスをターゲットとした高性能なAIエンジンならびにアクセラレータの開発に向けて、SynopsysのesignWare HBM2E IPを採用。メモリ処理能力の大幅な向上を目指す。

SynopsysのDesignWare HBM2/HBM2E IPは、シリコン実証済みのHBMおよびDDR4 IPに基づいており、既に25件以上の量産SoCに利用された実績を持つ。HBM2E IPを利用することで、DDR4 IPの12倍の帯域幅、10倍の電力効率が実現できるという。

なおソシオネクストは、DesignWare® IPの活用に関するSynopsysとの協業の一環として、HBM3メモリの活用においても協業していることを明らかにしている。

2021.01.19

2月12日 Design Solution Forum 2020 開催のご案内です。

Design Solution Forum(以下、DSF)は、組込みシステム開発に携わるエンジニアの方々に向けた技術イベントとして、2014年より開催しています。

人と技術の交流を目的に、エンジニアによるエンジニアのためのイベントとして開催してきたDSFは、お陰さまでDSF2019にて参加申込者数1000名を突破。DSF2020では更なる飛躍を目指していました。

ところが2020年COVID-19の影響により、DSFの状況も大きく変わりました。

DSF実行委員会は、例年10月に開催していたイベントを翌年2月開催に延期することを決定。それと同時にセミナー・イベントをオンラインでも配信するというネット併催にチャレンジする事にしました。イベント運営としてはオンラインのみに割り切る方が容易ですが、エンジニア交流をコンセプトに掲げるDSFとして、ライブでの講演とイベントを通じた様々な出会いに拘った結果、ネット併催という形を選択しました。

2021年2月12日の開催に向けてネット併催の準備を開始したのは2020年6月、以降、実行委員一同、試行錯誤を重ねながら、パシフィコ横浜で行われる全ての講演をZoomとTeamsの両サービスでリアルタイム配信する、という目標に向けて取り組んで参りました。

お陰様で今回のDSF2020も基調講演のALE社岡島様をはじめ、多彩な顔ぶれの講演者様にお集まり頂き、様々な技術分野の話を聴講できる貴重なイベントに仕上がりました。

2020年10月に予定していたイベント内容をそのまま実現するという意味で、イベント名はDSF2020のまま変更せず開催させて頂く予定です。

実施予定の計50のセッションは、全て講演会場であるパシフィコ横浜アネックスホールまたはオンラインでご聴講頂けます。

DSFは、エンジニアの皆様の交流や繋がりを重視した非営利のイベントです。

コロナ禍において人との交流が難しい状況が続いておりますが、こんな時だからこそ、是非DSF2020に参加頂き、様々な技術、話題、そして人に出会って頂ければ幸いです。

DSF2020を通じ、少しでも皆様のエンジニア・ネットワークそして可能性が拡がればという想いで、実行委員一同皆様のご参加をお待ちしております。

■□■ DSF2020参加登録受付中〜今年はネット併催にチャレンジ! ■□■

DSF2020は、同イベント初のネット併催という形でセミナー会場で行われるセッションをオンラインで配信致します。

5つの講演トラックと特別会場で行われる計50全てのセッションを、セミナー会場だけでなくオンライン環境(ZoomまたはTeams)でライブでご聴講可能です。是非ご登録よろしくお願いします。

記

Design Solution Forum 2020(DSF2020)

開催:2021/2/12(金) 9:20-17:50 (会場展示は18:50まで)

会場:パシフィコ横浜アネックス・ホール

主催:DSF2020実行委員会

参加:無料、昼食付き(セミナー会場のみ)

・今年の講演トラック

-Rambus Track(ラムバス社の企画トラックです)

-FPGA Solution Track

-Internet of AtoZ Track(拡大するIoTの世界をテーマにしたトラックです)

-ハードもソフトもオープンソース Track

-HOT TECH Track:(注目の技術、話題の技術にフォーカスしたトラックです)

・基調講演:株式会社ALE 代表取締役社長 岡島 礼奈様

「夢から現実へ!人工流れ星の実現に向けて」

・DSF特別企画

「スタートアップ×エンジニアネットワークで明日の新ビジネスを創ろう!」

-AIQ、EDGEMATRIX、ブルックマンテクノロジ、モルフォが参戦

・セミナー会場展示

セミナー会場では当日、スポンサー企業25社の展示をご覧頂けます。

・バーチャル展示

イベントWebページでは、2月1日〜3月31日まで、スポンサー企業30社の展示を

ご覧頂けます。

・プレゼント抽選会

セミナー会場にご来場頂いた方を対象にプレゼント抽選会を行います。

プレイステーション5など豪華景品を用意しておりますので、是非ご参加下さい。

セミナー会場での聴講をご希望の方は、お早めにご登録下さい。

全てのセッションは、ご登録数が定員に達した時点で登録を終了させて頂きます。

2021.01.14

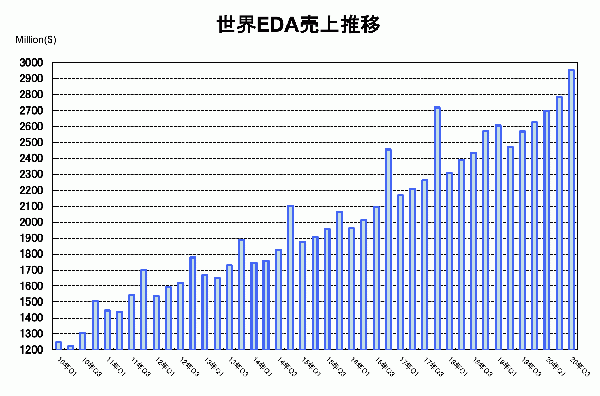

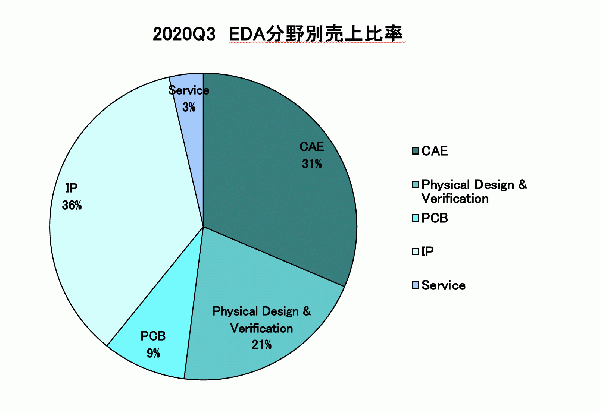

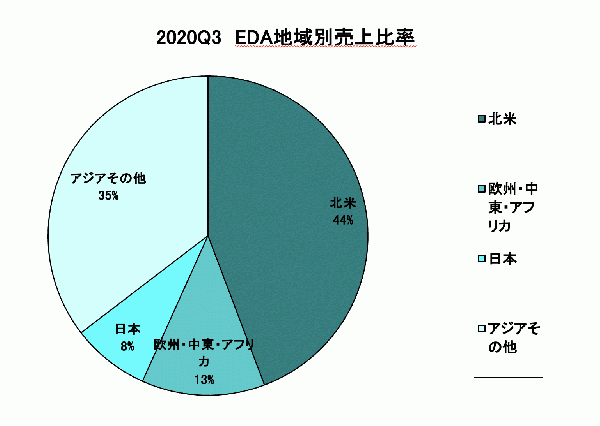

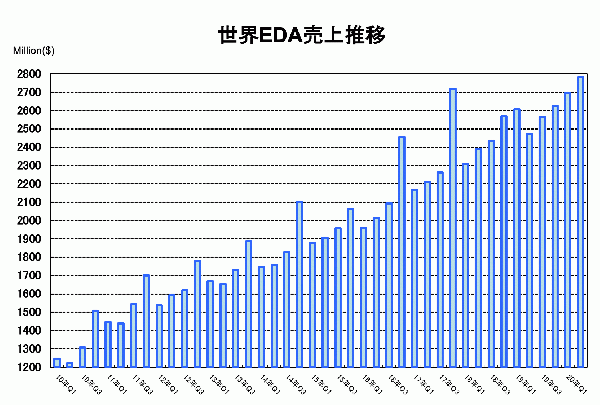

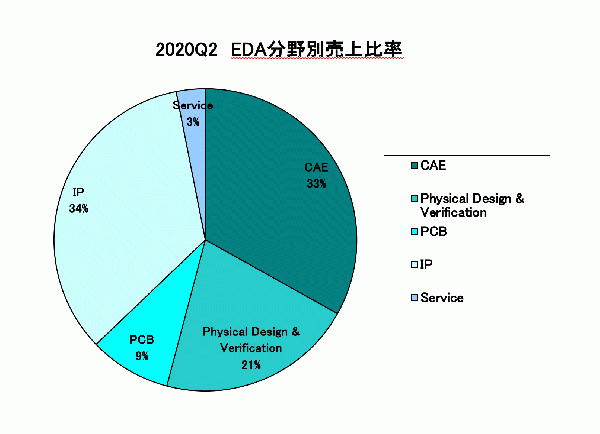

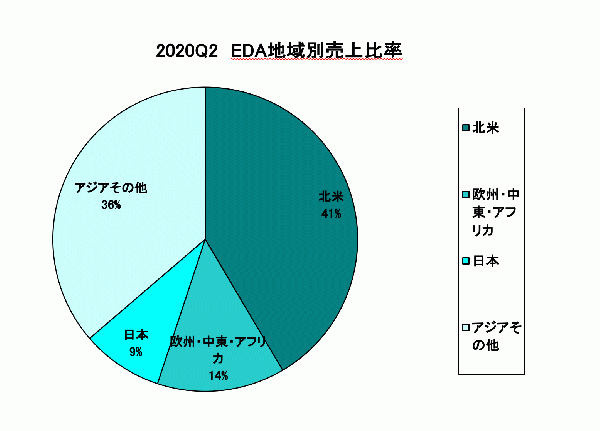

2021年1月11日、米ESD Allianceは、2020年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2020年Q3(7-9月)の世界のEDA売上総額は前年比約15増、前Q2比約6.1%増の29億5390万ドルで、四半期売上として過去最高記録を更新した。売上記録の更新は前Q2に続いて2四半期連続。半導体業界、半導体製造装置業界と同様にEDA業界にも活況の波が押し寄せているのが分かる。

ちなみに四半期売上が前年実績を上回るのは7四半期連続となる。

2020年Q3のEDA売上をカテゴリ別に見ると、IP分野が前年比25.8%増と大きく成長し初めて10億ドルの大台に乗せた。

2020年Q3のEDA売上を地域別に見ると、Q2に続いてアジア・パシフィックが前年比26.4%増と強力な伸びを示した。次いで最大市場の北米が11.7%増と好調を維持し、初めて売上13億ドルの大台に乗せた。欧州・中東・アフリカ、そして日本市場も一桁ながら前年比増を達成している。

2020年Q3時点でのEDA業界の従業員数は前年比4.8%増の47,087人でQ2よりも1.1%増加した。

2020年Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 9億2760万ドル 10.7%Up

■IC Physical Design & Verification分野 6億820万ドル 9.1%Up

■IP分野 10億5170万ドル 25.8%Up

■サービス分野 1億590万ドル 11%Up

■PCB/MCM分野 2億6040万ドル 8.3%Up

2020年Q3の地域別の売上と昨年同時期との比較は以下の通り。

■北米 13億720万ドル 11.7%Up

■欧州・中東・アフリカ 3億6830万ドル 4.9%Up

■日本 2億3240万ドル 6%Up

■アジアその他地域 10億4600万ドル 26.4%Up

2021.01.05

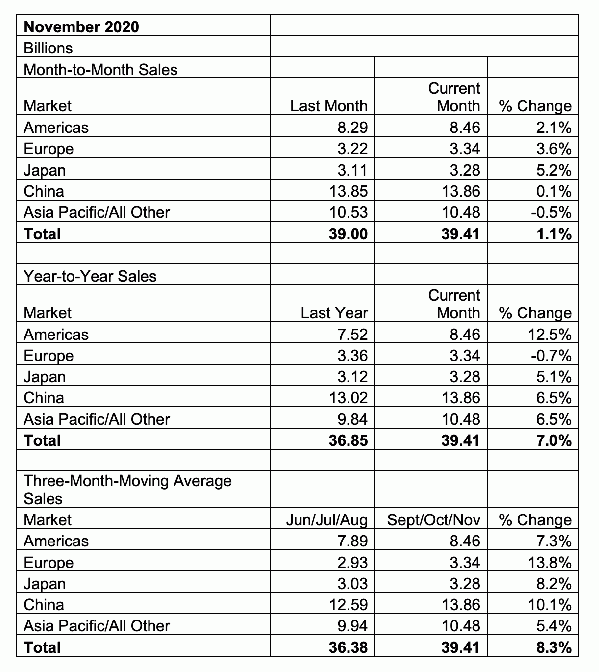

2021年1月4日、米SIA(Semiconductor Industry Association)は、2020年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年11月の世界半導体売上は、前年同月比約7%増、前月比約1.1%増の394.1億ドルで先月に続いて2020年の単月売上の記録を更新。これで単月売上が前年同時期を超えるのは10ヶ月連続となる。

2020年11月の世界半導体売上を地域別にみると、北米市場が依然好調を維持しており前年比12.5%増の売上を記録。北米市場の売上が前年同月比で2桁のプラス成長となるのは11ヶ月連続。北米市場に続いて中国、アジアその他地域がともに前年同月比6.5%増と売上を堅調に伸ばしている。

日本市場は久しぶりに前年同月比で5%のプラス成長を達成。前月比では5.2%増の32.8億ドルで、売上を円ベースで換算すると前月比約4.4%増、前年比約1%増の約3,425億円となる。日本市場の売上が前年同月比プラス成長となるのは、2020年2月以来となる。

2020.12.07

2020年12月2日、Synopsysは、2020会計年度第4四半期(20年8-10月)の四半期決算を報告した。

発表によるとSynopsysの2020会計年度Q4の売上は、前年同時期比約20%増、前Q3比約6.3%増の10億2500万ドルで四半期売上としては過去最高、営業利益は前年比約23%増の1億9750万ドルだった。(※GAAP基準による会計結果)

Synopsysの2020会計年度の売上総額は、36億8500万ドルで過去最高を更新。前年比9.6%のプラス成長を達成した。

SynopsysはこのQ4において、3nmプロセス・チップの実現に関するTSMCとの協業を発表したほか、業界初の機能安全ASIL D完全準拠プロセッサIP(※

関連ニュース)、ライフサイクル全般に渡ってチップを管理し最適化する「Silicon Lifecycle Managementプラットフォーム」(※

関連ニュース)などの新たなソリューションを発表している。

2020.12.07

2020年12月3日、米SIA(Semiconductor Industry Association)は、2020年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年10月の世界半導体売上は、前年同月6%増、前月比3.1%増の390.3億ドルで先月に続いて2020年の単月売上の記録を更新。これで単月売上の前年比増は9ヶ月連続となる。

10月の半導体売上額に先行して発表されたWSTS2020秋季半導体市場予測によると、2020年の半導体市場は前年比5.1%増の成長となる見込み。パンデミックによるマイナス要因がある反面、5Gスマートフォンの増加やライフスタイルの変化が半導体需要を押し上げている結果という見立てだという。今年6月に発表された春季予測の3.3%のプラス成長を上方修正した格好となる。なお、2021年については現時点で8.4%のプラス成長と予測している。

日本市場については、2019年の前年比-11.2%に対し2020年は-2.1%のマイナス成長を予測。2年連続のマイナス成長となるが、2021年については4.8%のプラス成長と予測している。(全て円ベース)

2020年10月の世界半導体売上を地域別にみると、北米市場の力強さが目立ち前年比14.2%増の売上を記録。北米市場は3月以降、9ヶ月連続で前年比2ケタ成長を続けている。北米市場に続いて中国、アジアその他地域も売上を堅調に伸ばしているが、日本市場と欧州市場は先月同様に前年実績を割り込んだ。

日本市場の10月の売上は前年比1%減、前月比1.6%増の31.2億ドルで、売上を円ベースで換算すると前月比約1.2%増、前年比約3.6%減の約3,282億円となる。

2020.11.04

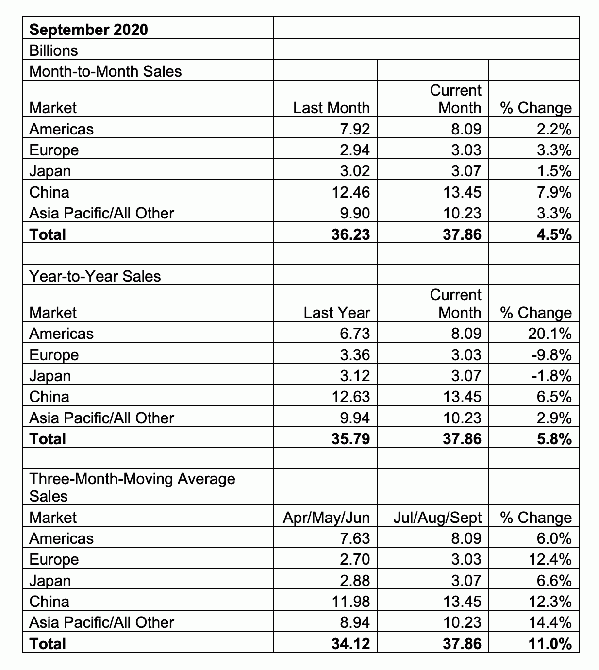

2020年10月30日、米SIA(Semiconductor Industry Association)は、2020年9月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年9月の世界半導体売上は、前年同月比5.8%増、前月比4.5%増の378.6億ドルで2020年の単月売上としては最高額を記録。これで単月売上の前年比増は8ヶ月連続となる。

半導体市場はコロナ禍において安定した成長を継続しており、このまま売上が順調に推移すると過去最高を記録した2018年に次ぐ年間売上となる。

2020年9月の世界半導体売上を地域別にみると、3月以降、力強い売上増を続けている北米市場は9月も前年比20.1%増の売上を記録。前年比20%を超える売上増は8ヶ月連続となる。

その他の地域では、中国、アジアその他地域も売上が堅調に推移。日本市場と欧州市場は前年実績を割り込んだ。

日本市場の9月の売上は前年比1.8%減、前月比1.5%増の30.7億ドルで、売上を円ベースで換算すると前月比約1.3%増、前年比約3.2%減の約3,244億円となる。

2020.11.02

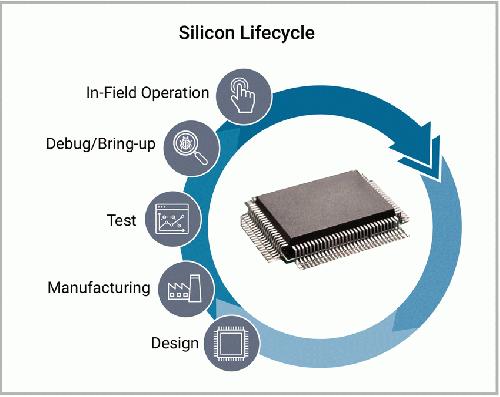

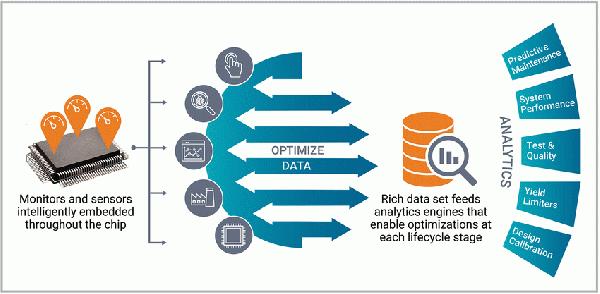

2020年10月12日、Synopsysは業界初のソリューションとして、「Silicon Lifecycle Management(SLM)プラットフォーム」を発表した。

発表によると「Silicon Lifecycle Management(SLM)プラットフォーム」は、その名の通りシリコンの製造後も含めそのライフサイクル全般に渡ってチップを管理し最適化するためのデータ分析ソリューションで、データセンターやネットワーク機器、自動車などのキー・アプリケーション分野の高性能SoCが一つのターゲットになっているようだ。

考え方としてはSoCの設計フェーズだけではなく、そのSoCが実際に製造されシステム内で運用されるフェーズも含めてデータ解析を行い、各フェーズでの最適化を目指すというもので、チップに埋め込んだモニターおよびセンサーを通じてデバイスおよびシステムの様々なデータを取得し、SoCのライフサイクル全体に渡って性能、信頼性、セキュリティの問題を可視化。その上で独自の解析手法を用いてSoCライフサイクルの各フェーズにおける問題に最適な形で対処していく。

※画像はSynopsys Web上のデータ

Synopsysの説明によると「Silicon Lifecycle Management(SLM)プラットフォーム」は、同社のインプリメント環境「Fusion Design Platform」と緊密に連携しているということで、SoCから収集したデータの解析やその後の最適化は「Fusion Design Platform」の技術がベースになっているようだ。

SoCのライフサイクル全体を可視化するというSynopsysの打ち出した新たなアプローチは、チップベンダ、チップユーザーにこれまで無かった知見を提供するだけでなく、収益の向上やコスト削減など実際のビジネスにおける利益をもたらすものになる。

2020.10.30

2020年10月28日、フォーマル検証技術をベースとしたEDAソリューションを手掛ける米Real Intentは、同社のCDCサインオフツール「MeridianCDC」がSamsung Foundryによって採用された事を発表した。

発表によるとSamsung Foundryは、自社開発IPを承認するための社内のリファレンスフローの一部としてReal Intentの「MeridianCDC」を採用。同ツールを用いてSoCの階層型CDCのサインオフを判断するという。

またReal Intentは、ツールの採用と合わせてSamsung Foundryのパートナーに選ばれた。同じくSamsungに開発・設計サービスを提供するSamsungのパートナー企業は、Samsungのクラウド環境上で「Meridian CDC」を使うことが可能となる。

「Meridian CDC」は、ASICやFPGAの非同期クロックドメインを横断する信号を確実に受信するために包括的な構造解析と機能解析を実行。メタスタビリティ、相関性の損失、グリッチ伝播に関連する問題の特定など、CDCサインオフのあらゆる側面に対応で、Real Intentは「Meridian CDC」を市場で最も速く、最大の容量で、最も正確なCDCサインオフ・ソリューションだとアピールしている。

なおReal IntentはマルチモードCDC解析用に特別に開発した「Verix Multimode CDC」というツールも提供しており、同ツールを使うと不可能なクロックの組み合わせを自動識別し、1回の実行で考えられる全てのクロッキング・シナリオをカバーすることができるという。

ちなみに久しぶりにReal IntenのWebサイトを覗いたところ、ユーザーの企業ロゴとしてSamsung, NVIDAらと共にAIチップベンチャーのMYTHICやHailoのロゴも並んでいた。

2020.10.29

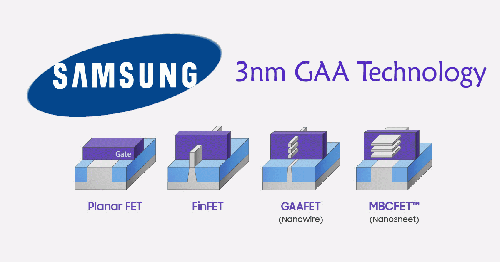

2020年10月28日、CadenceとSynopsysは、Samsung Foundryの3nm Gate-All-Around(GAA)プロセスにおけるツール認証を同時に発表した。

Samsungの3nm GAAプロセスはMBCFETと呼ばれる独自のFET構造を持ち、TSMCに先駆けての量産を目指す野心的なGAAプロセスで、今年からリスク生産の開始が予定されていた。(TSMCは2nmプロセスからGAAを採用するとされている)

今回CadenceとSynopsysの両社は、それぞれ自社ツールで構成するSamsung 3nm GAAプロセス向けのAMSデザイン・リファレンスフローをリリースし、これをSamsungが認証した。

Cadenceのフローは「Vituoso」を、Synopsysのフローは「Custom Compiler」を中心としたもので、Samsungの顧客は両社のツールを用いてSamsung 3nm GAAプロセスをターゲットとしたアナログおよびミックスド・シグナル設計が可能となる。

2020.10.27

2020年10月22日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、プロトタイピング・システムの新製品「Prodigy S7-19P」の発売を発表した。

新製品「Prodigy S7-19P」は、Xilinxの12nm FPGAで最大容量を誇るUltraScale+ VU19Pを搭載するプロトタイピング・システムで、UltraScale+ VU19Pをシングル、デュアル、クアッドの3種類の構成で利用することができる。

FPGAを4個搭載する「ProdigyS7-19PQ」の場合、ASICゲート数に換算すると最大196Mゲートのデザインに対応、I/0数は5,288個、176個の高速トランシーバ、最大2,400Mbpsで使用可能なオンボードメモリ計128GBを備える。この「Prodigy S7-19P」シリーズの製品は、同社の既存製品同様、複数のボードを接続してデザイン容量をスケーリングできるほか、リモートアクセスによる遠隔地からの利用も可能となっている。

S2Cによると、「Prodigy S7-19P」のリリースと合わせてデザインの実装環境「Player Pro Compileソフトウェア」もバージョンアップ。デザインを複数のFPGAに分割するためのパーテーション・エンジンなどが強化され複数の新機能が追加された。これにより10億ゲート規模のデザインの高速なパーティショニングが可能となったほか、システムパフォーマンスが最大50%向上(強化されたピン多重化マクロの効果)、最大70%の時間節約が可能になるなど、より速くより効率的なプロトタイピング・システムに進化した。

S2Cのプロトタイピング・システムは、包括的なソフトウェア・ツールの充実もうりの一つで以下のようなツールを揃えている。

・Player Proランタイム・ソフトウェア(FPGAボードに付属)

高度なクロック・マネジメント、統合セルフテスト、自動ボード検出、I/O電圧プログラミング、複数のFPGAダウンロード、リモートシステムの監視と管理、など

・Multi-Debug Module

複数のFPGAに対して同時に行えるディープトレースのデバッグ、クロストリガー機能を提供

※再コンパイル不要または限定的な再コンパイルで、新たな信号を選択可能

・ProtoBridge

システムレベルのコモデリングを実現

ホストコンピューターとプロトタイプ化されているSoCデザインをPCIeベースでリンク接続

2020.10.21

2020年10月19日、Cadenceは、2020会計年度第3四半期(2020年7-9月)の売上を報告した。

Cadenceの2020年Q3売上は、前年比約15%増、前期Q2比約4.5%増の6億6700万ドル、営業利益は前年比約59%増の1億6200万ドルだった。(※GAAP基準による会計結果)

このQ3実績は同社の四半期売上記録として過去最高を更新するもの。四半期売上記録の更新は2019年Q4以来4四半期連続で同社の安定した売上の伸びを示している。

同社CFO兼上級副社長のJohn Wall氏のコメントによると、下半期に入り中国でのハードウェア及びIP販売が好調だという。ハードウェアというのは、エミュレーターやFPGAベースのプロトタイピング・システムなど、ハードウェアベースのソリューションを指していると思われる。また、システム設計および解析関連のソリューションも継続的に伸びているようだ。

CadenceはこのQ3に以下のような製品及びニュースを発表している。

・マシンラーニングを用いた論理シミュレータ「Xcelium」を発表(

関連ニュース)

・TSMC N7/N6/N5プロセス向けUltraLink D2D PHY IPを発表

・デジタル設計およびカスタム設計フローがTSMCのN3プロセスで認証

Cadenceは2020年Q4の売上を7億2000万-4000万ドル、2020年の年間売上を26億4000-6000万ドル程度と予測している。

2020.10.15

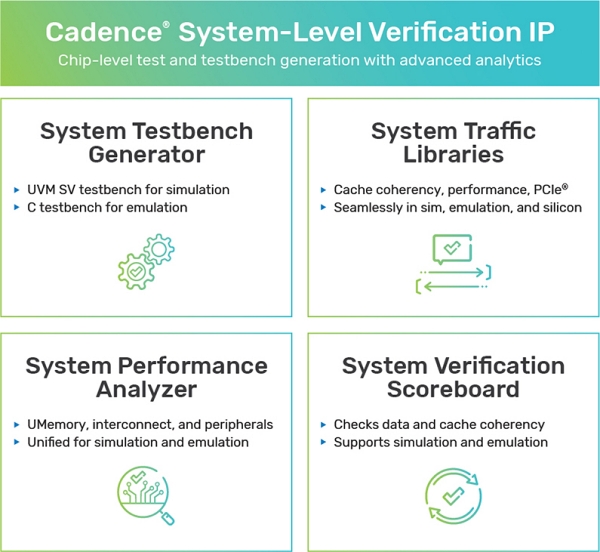

2020年10月13日、Cadenceは検証IPの新たな製品群「Cadence® System-Level Verification IP (System VIP)」 を発表した。

Cadenceによると新製品「System VIP」は、テストベンチアセンブリ、バスおよびCPUのトラフィック生成、キャッシュコヒーレンシーの検証、システムパフォーマンスのボトルネック解析など、システムレベルのチップ検証を狙うもので、同検証IPで生成したテスト環境はCadenceのシミュレーション、エミュレーション、プロトタイピングの各エンジンで使用することが可能。シリコン開発後の立ち上げ検証にも拡張して使用できるという。

「System VIP」には以下のツール、ライブラリが含まれており、Cadenceはこれらを利用することで大規模チップのチップレベルの検証効率を最大10倍向上できると説明している。

・System Testbench Generator:

複雑なメモリ、キャッシュ、インタフェース、バスのコンフィグレーションに応じてSoCのテストベンチを自動的に生成

・System Traffic Libraries:

コヒーレンシー、パフォーマンス、PCIe、NVMeサブシステムなど、System VIPのテストベンチに組み込む各種ライブラリ

・System Performance Analyzer:

メモリーサブシステム、インターコネクト、ペリフェラルの包括的なパフォーマンス解析、レポート、可視化環境

・System Verification Scoreboard:

コヒーレント・インターコネクト、メモリ、ペリフェラルに対応するスコアボード

包括的なデータ、キャッシュコヒーレンシー・チェッカーを提供

※画像はCadence Web上のデータ

既に「System VIP」を導入しているルネサスエレクトロニクスの浅野氏(共通EDA技術開発統括部 デザインメソドロジ部 部長)は、CadenceのXceliumおよびPalladiumをベースとした既存の検証環境に「System VIP」を追加したことで、自動化やスティミュラス再利用が向上。SoCの検証効率が10倍向上したとコメントしている。

2020.10.13

2020年10月12日、SynopsysはAIチップベンチャーGraphcoreによる同社の配置配線ツール「IC Compiler II」の成功事例を発表した。

発表によるとGraphcoreは、Synopsysの配置配線ツール「IC Compiler II」を用いて同社の二世代目となる新型のIPU「Colossus MK2 GC200」を設計しチップの一発完動に成功。7nmプロセスで製造される同AIアクセラレータ・プロセッサは、トランジスタ数594億、1,472個の独立したプロセッサコアと900MB超のオンチップ・メモリを統合しているという。

※IPU:Intelligence Processing Unit

Graphcoreは初代製品の設計からSynopsysのツールを包括的に採用しており、大量のプロセッサコアの複雑な配置配線に対処している。ちなみに初代の「Colossus」は235億トランジスタ。

新型のIPU「Colossus MK2 GC200」は、初代製品同様サーバー向けのAIアクセラレータとしてディープラーニングの学習および推論での利用が想定されており、同プロセッサを4基内蔵するIPUラックは、1PFLOPSの演算性能を発揮するとされている。Graphcoreの説明によると理論上最大64,000のIPUを相互に接続可能で、最大16exaflopsという驚異的な演算能力を実現できるという。

なお、GraphcoreのIPUは単体で販売されることはなく、下記画像のようなサーバー向けのIPUラックという形で提供される。既にMicrosoftと契約しておりAzure上でIPUを利用することが可能だが、新型IPU「Colossus MK2 GC200」のサポート時期については未定。同社は既に投資家から累計4億5000万ドルを集めている。

2020.10.08

2020年10月7日、CadenceはTSMCの先端プロセス向けのDDR5/LPDDR5およびGDDR6 メモリIPを発表した。

DDR5/LPDDR5 メモリIPはTSMCの5nm 最先端プロセスのN5向けに、GDDR6 メモリIPはN6/N7プロセス向けに用意された。

いずれの製品もPHY, コントローラ, 検証IPで構成され、既にシリコン実績がある。GDDR6 メモリIPは今後N5プロセスにも対応する予定だ。

2020.10.07

2020年10月6日、各種設計/検証IPを手掛けるインドのSmartDVは、新製品のテストベンチ・ジェネレータ「SmartConf」を発表した。

発表によると「SmartConf」は、Verilog、SystemVerilog、SystemC、UVMに対応するテストベンチ・ジェネレータで、GUIベースでテストベンチの構成を入力することで所望のテストベンチを各種言語、形式で自動生成することができる。当然ながらSmartDVの提供する各種検証IPをサポートしており、シミュレーション、エミュレーターを用いたSoCテストやFPGAプロトタイピングなど、様々な用途に利用できる。

「SmartConf」にはテストベンチ生成の設定・構成入力用ウィンドウの他に、スコアボードやテスト実行リストの追跡用ウィンドウも用意されており、各種テストデータの保存や復元も可能。GUIを用いずにテキスト入力によりテストベンチの構成を入力できるオプションもある。また「SmartConf」は、SmartDVのビジュアル・プロトコル・デバッガー「ViPDebug™」に直接リンクすることも可能。「ViPDebug™」はプロトコルの解析・デバッグ用のツールであらゆるプロトコルに対応、様々な検証環境で利用できる。

SmartDVは設計・検証IPのラインナップを拡大する一方で、それらを活用する周辺環境の整備にも力を注いでいる。

2020.10.07

2020年9月30日、Synopsysは車載SoCをターゲットとする新たなプロセッサIP「ARC Functional Safety Processor」のリリースを発表した。

今回SynopsysがリリースしたプロセッサIP「DesignWare ARC EM22FS Functional Safety Processor」は、製品名の通り機能安全規格ISO 26262に対応する車載SoC向けのプロセッサで、安全性の要求レベルとして最も厳しい「ASIL D」に完全に準拠した製品として認証機関SGS-TÜV Saarの認証を取得している。Synopsysによると、ASIL Dが既定するランダム故障ならびにシステマティック故障検出基準に完全に準拠したプロセッサIPは「ARC EM22FS」が業界初の製品になるという。

「ARC EM22FS」には機能安全向けに以下のようなハードウェア安全機能が統合されており、ASIL D完全準拠の同IPを利用する事で、機能安全規格を満たす車載SoCの開発工数および規格認証時間を大きく短縮することができる。

・デュアルコア・ロックステップ機構

・メモリーやインターフェイスの誤り訂正コード

・内部レジスタに対する過渡故障保護機能

・診断エラー注入

・組込みセルフ・チェッキング・セーフティー・モニター

「ARC EM22FS」ならびに同プロセッサ向けのソフトウェア開発環境「ARC MetaWare Toolkit for Safety」は既に提供が開始されている。

2020.10.06

2020年10月5日、米ESD Allianceは、2020年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2020年Q2(4-6月)の世界のEDA売上総額は前年比約12,6%増、前Q1比約3.1%増の27億8390万ドルで、四半期売上として過去最高記録を更新した。

これまでの四半期売上記録は2017年Q4に記録した27億1860万ドルだったので、記録の更新は2年半ぶり。当時の記録を約2.4%上回った。ちなみに四半期売上が前年実績を上回るのは6四半期連続となる。

2020年Q2のEDA売上をカテゴリ別に見ると、PCB/MCM分野を除く全ての分野で一様に前年比2桁増を記録。中でもQ1は不調だったIC Physical Design & Verification分野が前年比16.8%増と大きく伸びた。

2020年Q2のEDA売上を地域別に見ると、最も成長率が高かったのはアジア・パシフィックで前年比16.8%増、次いで最大市場の北米が11.4%と好調を維持した。欧州・中東・アフリカ、そして日本市場も一桁ながら前年比増を達成した。

2020年Q2時点でのEDA業界の従業員数は前年比5%増の46,579人でQ1よりも1.4%増加した。

2020年Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 9億2200万ドル 16.1%Up

■IC Physical Design & Verification分野 5億8410万ドル 16.8%Up

■IP分野 9億4820万ドル 13.6%Up

■サービス分野 8620万ドル 12.8%Up

■PCB/MCM分野 2億4350万ドル 0.3%Down

2020年Q2の地域別の売上と昨年同時期との比較は以下の通り。

■北米 11億5560万ドル 11.4%Up

■欧州・中東・アフリカ 3億7750万ドル 5.2%Up

■日本 2億4040万ドル 9%Up

■アジアその他地域 10億1030万ドル 18.1%Up

2020.10.06

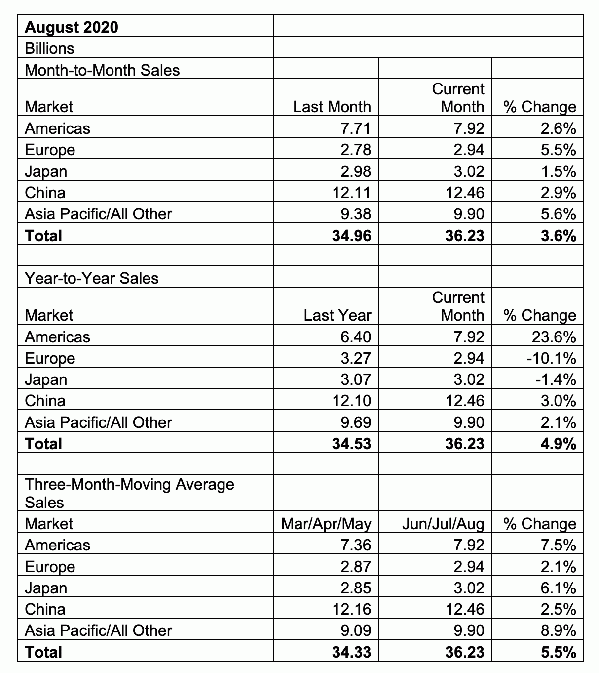

2020年10月5日、米SIA(Semiconductor Industry Association)は、2020年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2020年8月の世界半導体売上は、前年同月比4.9%増、前月比3.6%増の362.3億ドルで、7ヶ月連続で単月売上の前年比増を達成した。

半導体市場は昨年を上回る順調な成長を継続しており、現在のところ新型コロナウイルスによる経済の影響を受けず売上を伸ばし続けている。

好調な半導体市場の原動力となっているのは北米市場で、8月も前年比26.3%増の売上を記録。北米市場は3月以降、6ヶ月連続で前年比20%を超える売上増を続けている。

その他の地域を見ると7月に続いて欧州市場が売上減が目立っているがこれは為替の影響が大きい。

日本市場の8月の売上は前年比1.4%減、前月比1%増の30.2億ドルで、売上を円ベースで換算すると前月比約3.7%増、前年比約1.9%減の約3,202億円となる。

2020.10.02

2020年10月1日、ルネサスエレクトロニクスは、ASSP製品に台湾のIPベンダAndes TechnologyのRISC-V CPUコアを採用したことを発表した。

発表によるとルネサスは新しいASSP製品にAndesの32ビットRISC-V CPUコア「AndesCore™」を採用。同コアを搭載したASSPは2021年の下半期にサンプル提供を開始する予定。

同ASSPにはアプリケーションプログラムのパラメータ設定用ツールが用意されており、ルネサスはユーザーに対してRISC-Vの初期開発とソフトウェア投資の敷居を下げることができるとしている。

AndesはArm対抗の独自CPUコアで実績を積み重ねてきたIPベンダで台湾の大手半導体ベンダMediaTekの資本も入っている。2016年以降、RISC-VベースのCPUコアに力を注いでおり、2019年には同社のRISC-Vベースコアを用いたSoCの出荷数は15億個に達している。

2020.10.02

2020年10月1日、インターコネクトIPを手掛ける米Arteris IPは、ESLツール手掛ける仏Magillemの資産買収を発表した。

発表によるとArteris IPは、Magillemの技術資産と合わせてMagillemの全てのメンバーを取得するようで、実質的に企業買収に近い形のようだ。

Arteris IPは現在本社を米国に置いているが、元々フランスの企業で同じくフランス企業のMagillemとは協業関係にあり、両社ツールのインテグレーションなどを行っていた。

MagillemはIP-XACTベースのSoCアーキテクチャ設計環境やIPのアセンブリ環境を提供しており、これらツールは今後も単体製品としてArtteris IPから供給され、ツールの開発ロードマップは継続されるという。

2020.10.01

2020年9月30日、RTL静的解析ツールを手掛けるBlue Pearl Softwareは、東芝情報システムによる採用事例を発表した。

発表によると東芝情報システムは、FPGAおよびASIC開発の生産性と品質向上に向けてBlue Pearlの「Visual Verification™ Suite」を採用。同検証スイートは、Blue Pearlの提供する以下のツールで構成される包括的な環境で、クロッキングの整合性と共にRTLコードとSDCの品質を保証することにより、RTLシミュレーションを補完する。

【Visual Verification™ Suiteの構成ツール】

・HDLCreator™ スマート・エディター

・Analyze RTL™ 静的RTL解析ツール

・Clock Domain Crossing analysis CDC解析ツール

・SDC生成ツール

・管理ダッシュボード

Blue Pearlによると「Visual Verification™ Suite」は、代替えツールよりも高速に実行することが可能。QoRの向上、リスクの低減と同時に開発時間の短縮に貢献するとしている。

今回「Visual Verification™ Suite」を採用した東芝情報システムは、日本とベトナムの両拠点で検証スイートを活用し開発プロセスの合理化を目指すという。

2020.10.01

2020年9月30日、イスラエルのAIチップ・ベンチャーHailo Technologiesは、AIアクセラレーション・モジュール「Hailo-8 M.2およびMiniPCIe AI module」を発表した。

「Hailo-8 M.2およびMiniPCIe AI module」はHailoのAIプロセッサ「Hailo-8」を搭載するAIアプリケーション用のアクセラレータ・モジュールで、PCIe Gen-3.0 4-laneのインタフェースを備えており、M.2ソケットを備えたエッジ・デバイスに挿して利用することが可能。

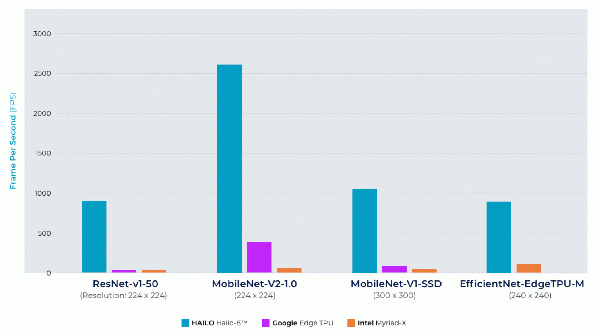

Hailoによると「Hailo-8」の演算性能は26TOPS、電力効率は3TOPS/Wで、一般的なニューラルネットワークを用いたベンチマークでは、Intel「Myriad-X」の約26倍、Google「Edge TPU」の約13倍のパフォーマンスを叩き出しているという。

「Hailo-8 M.2 module」は、既にパートナーであるFoxconnのエッジAIサーバー「BOXiedge」に組み込まれているほか、複数の顧客によって利用されているという。

なおHailoは、先日日本法人の設立をアナウンスしたばかり。

2020.09.29

2020年9月24日、GLOBALFOUNDRIESはGlobal Technology Conferences (GTC) 2020を開催した。今年は新型コロナウイルスの影響によりオンラインでの開催となった。

今年のGTCで発表された目玉のニュースは、新たなプラットフォーム「22FDX+」の発表。

「22FDX+」は22nm FD-SOIプロセスをベースとした既存の「22FDX」プラットフォームの機能拡張版で、IoT、5G、自動車、衛星通信アプリケーションなどをターゲットに既存プラットフォームよりも高性能、ローパワーを実現するほか、RF向けの「22FDXRF+」など特殊機能も用意されている。

GLOBALFOUNDRIESの22nm「22FDX」プラットフォームは、2017年から量産稼働しておりこれまで3億5000万以上のチップを出荷。45億ドル以上の収益を生み出しているという。当初GLOBALFOUNDRIESは2019年をめどに12nm FD-SOIプロセスの「12FDX」を稼働する計画を発表していたが、同プラットフォームは2023-2024年にリリースされる予定のようだ。

なお、「22FDX+」の発表に伴い、Cadenceは22nm FDXプラットフォームをサポートするミックスドシグナルOpenAccessプロセスデザインキット(PDK)の提供を発表。同PDKによりCadenceのツールと22FDXプラットフォームの連携が可能となる。(

プレスリリース)

またCadenceは、GLOBALFOUNDRIESとのIP供給に関するコラボレーションも発表。(プレスリリース)GLOBALFOUNDRIESの先端プロセス12LPおよび12LP+プラットフォームにおいて、Cadenceの各種デザインIPが利用できるようになる。IP供給に関するコラボレーションはSynopsysも同時に発表しており、Synopsysの各種DesignWare IPも12LP+プラットフォームで利用可能となる。(

プレスリリース)

更にGLOBALFOUNDRIESは、「GF12LP+」向けの新たなDFMキットについても発表。(プレスリリース)同DFMキットはMentor Graphics(Siemens)と共同開発したもので、Mentorの「Calibre nmDRCプラットフォーム」上に構築され、高度な機械学習機能を用いたDFM検証を実現する。同キットは「12LP+」のPDKのアップデートとして今年の第4四半期にリリースされる予定。

2020.09.29

2020年9月24日、バーチャル・プロトタイピング・ソリューションを手掛ける英Imperasは、日本のIPベンダNSITEXEによる採用事例を発表した。

発表によるとNSITEXEは、自社で開発している次世代のRISC-Vベース・プロセッサの検証用にImperasのRISC-Vリファレンスモデルを採用。ImperasのリファレンスモデルはRISC-Vのベクトル拡張をサポートしており、検証スイートにはベクトル拡張のコンプライアンス・テスト用のテストケースが含まれている。これらの条件・精度がNSITEXEのニーズにマッチしたようだ。

Imperasのプロセッサ・モデルは仮想プラットフォームでの検証に利用するもので、ImperasはRISC-Vモデルの供給に力を注ぐと同時に、Chips Alliance, OpenHW Groupなど各種オープンソース推進団体に積極的に参画している。

なお、Imperasの製品はイーソルトリニティが代理店として販売している。

2020.09.25

2020年9月22日、IC Insightsのレポート:

IC Insightsによると、自社製品を作らないTSMCをはじめとする半導体製造の専業ファウンドリの今年の売上額は、前年比19%増と大きく成長。この躍進は2014年の前年比18%増を超えるもので、5Gスマートフォンへのアプリケーション・プロセッサやその他通信機器の需要が原動力となっているという。IC Insightsは、2020年に2億個の5Gスマートフォン・ハンドセットが出荷されると予測している。

なおIC Insightsは、2020年の総ファウンドリ売上の81.4%を半導体専業ファウンドリが占めると予測している。その割合は2014年の89.3%から減少しているが、これはIntelやSamsungといったIDMによるファウンドリ・サービスが伸びているためと思われる。

更にIC Insightsによると、この先2019年から2024年までの半導体専業ファウンドリの売上は、平均成長率9.8%で伸びていく見通し。その成長率は、2014年から2019年の6.0%を3.8ポイント上回っている。ちなみに、2019年から2024年までの半導体市場の平均成長率は7.3%と予測されている。(※予測値は全てIC Insightsによるもの)

2020.09.18

2020年9月17日、RISC-VベースのIPコアを手がけるSiFiVeは、同社の新社長就任について発表した。

発表によると新たにSiFiveの社長兼CEOに就任したのはPatrick Little氏。同氏は元QualcommのエグゼクティブでQualcommの自動車業界への進出を指揮。その他にもeASICのCEO、CSRの上級副社長、Xilinxの上級副社長など、半導体企業の要職を歴任してきた実績を持つ。これまでSiFiveの社長兼CEOを務めていたNaveed Sherwani氏は同社取締役会長として経営陣に残る。

SiFiveは今年8月に資金調達Eラウンドで6100万ドルを調達。これにより同社の累計調達額は1億9000万ドルに達した。同社への出資にはIntelやQualcommも参加している。

またSiFiveは、同じく8月に新事業「OpenFive」を発表。ドメイン・スペシフィックなSoC開発に特化した設計サービスをより強化し、更なる顧客獲得を目指す戦略を示したほか、9月にはBarcelona Supercomputing CenterとのコラボレーションによるGCCおよびLLVM向けの新たなオープンソースAPIの開発を発表。同APIにより現在開発中のRISC-V Vector Extensionが利用可能となるという事で、ハイパフォーマンス・コンピューティング、人工知能、コンピュータービジョンといったアプリケーションにおいてもRISC-Vプロセッサの利用が拡がる可能性が開けた。なおSiFiveは既にRISC-V Vector Extensionを実装した新型プロセッサーを開発しており、来月開催されるLinley Fall Virtual Processor Conferenceにて発表する予定だという。

2020.09.17

2020年9月16日、FPGAベースのプロトタイピング・システムを手掛ける独ProDesignは、新製品「proFPGA XCVU19P System」の発売を発表した。

新製品「proFPGA XCVU19P System」は、16nmプロセスで製造されるXilinxの最上位FPGA「Virtex UltraScale+ VU19P FPGA」をベースとしたプロトタイピング・システムで、同チップの搭載数でUNO/DUO/QUADの3種類のバリエーションが用意されている。

ProDesignによると、「Virtex UltraScale+ VU19P FPGA」1個で約4800万ASICゲートのデザイン容量があり、同FPGAを4個搭載する「proFPGA quad XCVU19P System」では最大1億9200万ゲート。「proFPGA quad XCVU19P System」は最大9台の連結が可能で、最大17億2800万ゲートまでデザイン容量を拡張可能。性能面では高速PCBデザインにより、前世代の「proFPGA XCVU440」よりも最大30%高速に実行できるという。

※画像はFPGA4個搭載の「proFPGA quad XCVU19P System」

なお「proFPGA XCVU19P System」ファミリは、前世代のproFPGAファミリ製品と完全な互換性を持っており、既存のproFPGAマザーボード、FPGAモジュール、ドーターカード、およびアクセサリは、全て新しい「proFPGA VU19P FPGAモジュール」と組み合わせて利用することができる。

ProDesignがプロトタイピング・システム「proFPGA」製品を発売したのは2012年末で、以降既に同製品のユーザーを200社獲得しているという。

ちなみに正式なアナウンスは出ていないが、競合に当たるSynopsysも「Virtex UltraScale+ VU19P FPGA」を搭載したプロトタイピング・システム「HAPS SX-VU19P」という製品を用意しているようだ。