NEWS

2023.07.04

2023年5月4日、Synopsysは、パワー半導体設計の解析ツール、SoCの電力ネットワーク解析ツール、フルチップESD解析ツールなどを手掛ける米Silicon Frontline Technology社の買収を同社のブログで発表した。

Silicon Frontline Technologyは、パワーデバイス、ミックスドシグナルおよびアナログ設計向けの独自の電気レイアウト検証ソリューションを提供しており、大規模パワー半導体デバイスや静電気放電 (ESD) 保護ネットワークの設計における「盲点」を設計サイクルの早い段階で検出し最適化することが可能。同分野ではデファクト・ツールとして利用されている。

Silicon Frontline Technologyのソリューションは、Synopsysの「IC Validator™ PERC」物理検証ソリューションの静的ESDテクノロジーを補完するほか、Synopsysのパワーデバイス設計ソリューションや熱解析ソリューションの強化に活かされていく予定。具体的には、高速3D抽出、ポイントツーポイント抵抗計算、静的EMIR解析、パワーデバイスDCシミュレーション、パワーデバイス・ゲートネットワーク抽出とシミュレーション、動的デバイスモデル生成、電熱シミュレーションのためのソリューションなどがSynopsysから提供されることになるという。

2023.06.30

2023年6月29日、SiemensはOKIアイディエスによる同社製品「Catapult」の導入事例を発表した。

発表によるとOKIアイディエスは、同社の設計/検証サービスにおける高位合成および高位検証の実現にSiemensの「Catapult™」を採用。同社では既存の高位合成フローにおいて、合成用モデルと元のアルゴリズム・モデル、合成用モデルと合成後のRTLの等価性検証の効率化が課題となっていた。

OKIアイディエスは「Catapult」を用いた高位合成および高位検証フローを自社の設計/検証サービスに組み込むことで、課題となっていた効率的な等価性検証を実現。合成用モデルとアルゴリズム・モデルの検証に使うテストベンチをRTL機能検証用のテストベンチに自動変換することで、RTLの機能検証用のテストベンチをわざわざ作ることなくRTLの機能検証が可能となった。実行仕様として使用したC/C++の高レベルのコードをRTLの機能検証に利用できるため、設計品質の向上も可能になるという。

OKIアイディエスは、「Catapult」の導入によりRTL機能検証の大幅な効率化は可能となり、納期が20%以上短縮できると見ている。

Siemensの高位合成ツール「Catapult」には、高位合成機能と合わせてテストベンチ変換などを行う検証用の環境「SCVerify」やデザイン・チェッカー機能など、高度かつ高レベルな検証機能が統合されている。

2023.06.30

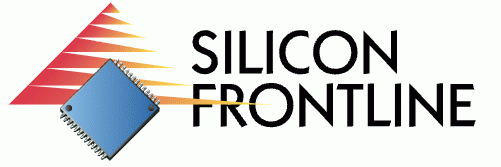

2023年6月27日、調査会社IDCは2022年半導体ファウンドリ市場の統計と今年の市場予測を発表した。

発表によると2022年の半導体ファウンドリ市場は前年比27.9%のプラス成長を達成。下記の上位10社全てが前年比2桁成長となった。

1. TSMC

2. Samsung Foundry

3. UMC

4. GlobalFoundries

5. SMIC

6. HHGrace

7. PSMC

8. VIS

9. Tower

10. Nexchip

首位TSMCは3/4/5nmの先端プロセスの受注が好調で市場シェアは2021年の53.1%から2022年には55.5%に拡大。

中国のファウンドリベンダーSMIC, HHGrace, Nexchipは、成熟したプロセスを中心にそれぞれ売上が30%以上増加。中国勢の市場シェアは2021年は7.4%だったが、2022年には8.2%に拡大した。

IDCは今年の半導体ファウンドリ市場は前年比6.5%減のマイナス成長と予測。市場状況の変化に伴う在庫調整などにより若干需要が減少するが2024年には業界全体が成長軌道に戻ると予測している。

※IDC

2023.06.29

2023年6月27日、AMDは新製品「AMD Versal Premium VP1902」アダプティブ SoCを発表した。

「VP1902」は7nm FPGAをベースとしたエミュレーション向けのSoCでLE数1,850万と大規模なデザイン容量を誇る。

AMDによると、「VP1902」は前世代の「Virtex™ UltraScale+™ VU19P FPGA」と比較して、2倍の容量(1,850万LE)、2倍のロジック密度、2倍のバンド幅(チップ間インタフェース)を提供。同デバイスを用いることでエミュレーションおよびプロトタイピングの性能を最大2倍(システムレベル)、デバッグ性能を最大8倍に向上できるとしている。また「VP1902」を複数利用することで最大600億ゲート(世界最大)のデザインに対応できるという。

AMDのFPGAを用いたエミュレーションおよびプロトタイピング・ソリューションは、Cadence、ProDesign、Siemens、Synopsys、S2CなどのEDAベンダが提供中。AMDは2024年前半に「VP1902」の量産を開始する計画なので、早ければ来年中にはEDA各社から新たな製品がリリースされるかもしれない。

2023.06.28

2023年5月22日、Cadenceは同社のブログにてアナログ/カスタムIC向けのレイアウト自動化ソリューションを手掛ける英Pulsic社の買収を公表した。

Pulsicは2000年1月に設立された英ブリストルに本社を置くEDAベンダで、アナログ/カスタムIC向けのEDAツールを提供している。

同社のソリューションは「Unity」と「Animate」の大きく2種類。

「Unity」はシェイプ・ベースのIC設計プラットフォームでフロアプランニング、配置、配線、実装機能を提供。

「Animate」はアナログ回路の自動レイアウト・システムで国内ではかつてリコーによる採用事例が報告されている。

今回、Pulsicの買収に関する取引条件などは明らかにされていないが、PulsicのチームはCadenceに移る予定。Cadenceは同社の強みであるAIベースのアナログ/カスタム設計環境「Cadence Virtuoso Studio」にPulsicの技術も取り込みアナログ/カスタム設計の更なる自動化に取り組む計画。

2023.06.23

2023年5月22日、オランダのAIスタートアップAxelera AIは、同社の資金調達額の累計が5000万ドルに達したことを発表した。

同社は昨年10月に資金調達Aラウンドで2700万ドルを調達し、調達額が累計3700万ドルに達したことを発表していたが、そのAラウンドに追加で複数の投資家が加わり調達額は累計5000万ドルとなった。同社にはIMECも投資しており、オランダの経済・気候政策省が補助金を出している。

Axelera AIは高性能かつ安価なエッジAIソリューションの提供を目指すAIスタートアップで、独自のインメモリ・コンピューティング・テクノロジーとRISC-Vデータフロー・アーキテクチャを使用して構築した「Metis AIプラットフォーム」の量産を目指している。同製品には既に100社近くがテスト用のサンプルを要求し、50社以上が早期アクセス・プログラムに申し込んでいるという。

「Metis AIプラットフォーム」はビジョン処理と自然言語処理にフォーカスしたソリューションで、既存の市販ソリューションの数分の1のコストとエネルギー消費で業界をリードするパフォーマンスと使いやすさを実現するとしている。

Axelera AIは、欧州のブロックチェーン技術開発大手Bitfury AI、IMEC、IBMチューリッヒ研究所、ETHチューリッヒ、Google、およびQualcommの研究者グループからなる18人のコアチームが2021年7月に設立。現在はオランダ本社の他にベルギー、スイス、イタリア、イギリスに研究開発オフィスを置き、世界14か国に120名を超える従業員を抱えている。

エッジAIチップを開発する半導体スタートアップが数ある中で、Axelera AIは欧州勢の本命企業の一つと目されている。

2023.06.22

2023年6月22日、RISC-Vプロセッサを手がけるCodasipは設計/検証IPを手がけるSmartDVとの提携を発表した。

Codasipはプロセッサ設計自動化ツール「CodasipStudio」、RISC-VベースのプロセッサIPといったソリューションをもとに、用途に特化した競争力の高いカスタムRISC-Vプロセッサの実現をビジネスの一つの柱に据えているが、今回発表したSmartDVとの提携は、同社の顧客によるカスタムRISC-Vプロセッサの設計をより容易化するための施策の一つ。

今回のSmartDVとの提携により、Codasipの顧客はカスタムRISC-Vプロセッサの設計にあたり、Codasipとのライセンス契約のもとでSmartDVの設計IPを利用できるようになる。これまではCodasipとSmartDVの両社と個別にライセンス契約を結ぶ必要があったが、Codasipを窓口にワンストップでRISC-V IPと周辺IPを調達できる。

SmartDVの設計IPは、豊富なラインナップと優れた品質とコストで多様なチップに利用されているが、CodasipのRISC-Vプロセッサに対しては互換性と統合の容易性があらかじめ検証されており、設計プロジェクトを加速・簡素化することができるという。

大手ベンダによる寡占が進むIP市場において、元気ある両ベンダの提携は両社および両社の顧客にとってWin-Winなものとなるが、RISC-Vエコシステムの拡張という面でも意味がありそうだ。

2023.06.20

2023年6月14日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の論理シミュレータ「Riviera-PRO」がAMDのSoC「Versal ACAP」デザインのシステム・シミュレーションをサポートしたことを発表した。

発表によると「Riviera-PRO」の最新リリースは、「Versal ACAP」のAIエンジン、プロセッシング・システム、プログラマブル・ロジック間の相互作用をテストするための「Vitis」ハードウェア・エミュレーション・フローでRTLシミュレータとして利用可能となった。

Aldecの説明によると、「Versal ACAP」デザインのハードウェア・エミュレーションのセットアップとシステム統合は全て「Vitis」環境内で行われ、「Vitis」は、グラフ・アプリケーション用にAIエンジン・シミュレータ、プログラマブル・ロジック・カーネル用にRiviera-PROシミュレータ、プロセッシング・システムのホスト・アプリケーション用にQEMUを実行する。AIエンジンとネットワーク・オン・チップにはSystemCモデルも用意されており、これらもRiviera-PROでシミュレーションすることができるという。

「Vitis」ハードウェア・エミュレーション・フローのRTLシミュレータとして「Riviera-PRO」を使用する方法に関して、Aldecはいくつかの「Versal ACAP」チュートリアル・デザインおよび手順を

Githubに掲載している。

2023.06.14

2023年6月13日、Cadenceは設計IPの提供に関するSamsung Foundryとの契約締結を発表した。

発表によるとCadenceとSamsung Foundryは、Samsungの先端プロセスSF3(3nm)およびSF5A(5nm)に対応するCadenceの設計IPポートフォリオの拡張に向け複数年契約を締結した。

この契約により、CadenceはSamsung FoundryのSF3/SF5Aプロセスを利用する両社の顧客に以下のような設計IPソリューションを提供する。

<SF5Aプロセス向け>

・112/56/25/10G PHY/MAC

・PCI Express® (PCIe®) 6.0/5.0/4.0/3.1 PHY/Controller

・Universal Chiplet Interconnect Express™ (UCIe™) PHY/Controller

・USB3.x PHY/Controller

・GDDR6およびDDR5/4向けPHY/Controller

<SF3プロセス向け>

・DDR5 8400+およびGDDR7

2023.06.14

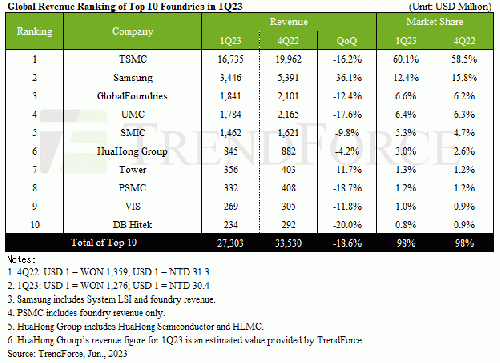

2023年6月12日、市場調査会社TrendForceは半導体ファウンドりの2023年Q1売上ランキングを発表した。

発表によると世界トップ10ファウンドリの2023年第1四半期の売上は、前四半期比18.6%減という大幅な減少となった。減少額は約273億ドルに達しており、これはエンド市場の需要の持続的な低迷と、不況の複合効果によるものとTrendForceは分析している。

Top10ランキングとしては、GlobalFoundries がUMCを上回って3 位に浮上。Tower SemiconductorがPSMCとVISを上回って7位となった。

画像はTrendForceの公開データ

これは、需要の低迷と閑散期の複合的な影響によるものだ。

また、ランキングも変化し、GlobalFoundriesがUMCを抜いて3位、Tower SemiconductorがPSMCとVISを抜いて7位となった。

TrendForceは第2四半期も引き続き売上減少が続くと予測している。

2023.06.13

2023年5月19日、DigiTimes ASIAのレポート:

Empyreanは2023年5月19日に2023年第1四半期の財務報告を発表した。

今年1月から3月にかけての売上は1億6000万元(約2,300万ドル)で前年比64.7%のプラス成長を達成した。

Empyreanの2022年のEDAソフトウェア販売の売上は、6億7800万元(約9,750万ドル)で前年比39.4%のプラス成長だった。

EDAソフトウェア販売事業では、フルプロセスEDAツールシステム、デジタル回路設計EDAツール、ウェハ製造EDAツールの売上はそれぞれ4億8800万元、1億1900万元、7100万元で、前年比38.74%、36.18%、50.07%の増加となった。

2023年Q1では、売上と利益がさらに増加し粗利益率が97.02%となったとのこと。

Empyreanは、第1四半期の成長を中国のEDA業界の継続的な成長と会社の市場シェアの拡大によるものとしている。

中国のEDA業界は、国際的な競合他社と比較して製品ラインナップが不完全であり、ツールの提供に多くのギャップがあるという課題に直面している。中国のEDA最大手であるEmpyreanは、今後の開発計画としてこれらのギャップを埋め包括的な製品ラインナップを構築することに加え、中国の先端チップ製造プロセス開発を継続的に支援することを目指している。

Empyreanによると、アナログツールはすでに5nmプロセスを部分的にサポートしており、デジタルツールは7nmプロセスを完全にサポートしているという。

2023.06.13

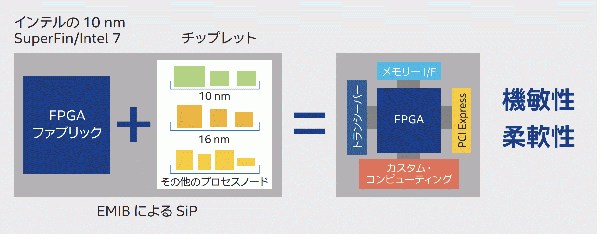

2023年5月23日、IntelはFPGAの新製品「Agilex 7」の量産開始を発表した。

Intel 10nm SuperFin テクノロジーとIntel 7 テクノロジーで実現される新製品「Agilex 7」は、「R-Tile」と呼ばれるチップレット・アーキテクチャを採用したFPGAで、トランシーバー、プロセッサー・インターフェイス、最適化されたI/O、 カスタム・コンピューティング、eASIC™ デバイスなど、 数多くの機能を専用チップレットとして FPGA ファブリックに接続し、各アプリケーションに対して独自に最適化されたソリューションを構築できる。

特筆すべきはPCIe 5.0とCXLインタフェースをハードIPとしてサポートしている点でFPGAとしては業界初。これらIPは「Embedded Multi-die Interconnect Bridge(EMIB)」と呼ぶIntel独自のチップ間接続技術を使用してFPGAファブリックに接続される。EMIBはシリコンレベルの相互接続で、チップレット間で低レイテンシ、高速、広帯域な接続を実現する。

画像はIntelのHP上のデータ

CXLのサポートによってFPGAがプロセッサー、GPU、その他のCXL対応アクセラレータ(機械学習アクセラレータやメモリ拡張など)など全てのコンピューティング要素と共通のメモリ環境を共有できるようになる。これはコンピューティング要素とストレージ要素の分散を可能にするもので、大規模なクラウドサーバー環境を簡単に分割および管理できるスケーラビリティとモジュール性を実現できる。

IntelによるとR-Tileを採用した「Agilex 7」は、競合のFPGA製品と比べて2倍高速なPCIe 5.0帯域幅と、ポート当たり4倍のCXL帯域幅を提供可能。Metaとミシガン大学が公開しているホワイトペーパーによると、CXLメモリー対応のFPGA を第4世代 Xeonプロセッサー搭載サーバーに追加することで、Linuxのパフォーマンスを最大18%向上できたという。

「Agilex 7」は、最大4Mのロジック・エレメントと最大485Mbのメモリを提供。32GBのHBM2eオプションもある。また、データ転送速度最大116Gbpsのトランシーバー、Cortex-A53を含むデュアルコアおよびクアッドコアCortex-Aプロセッサーのオプションをサポートしている。

2023.06.09

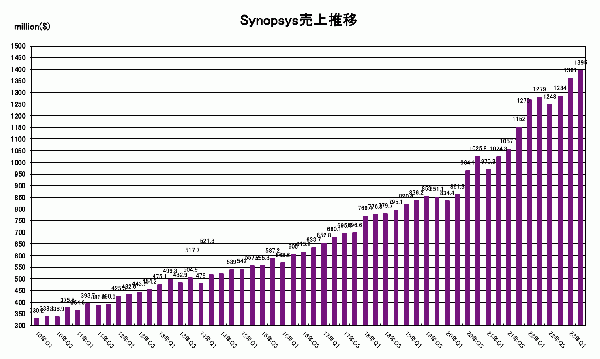

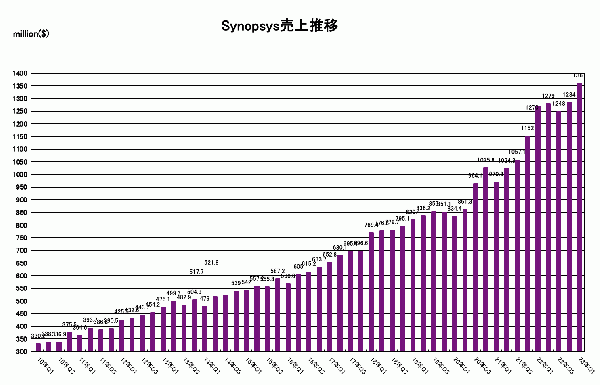

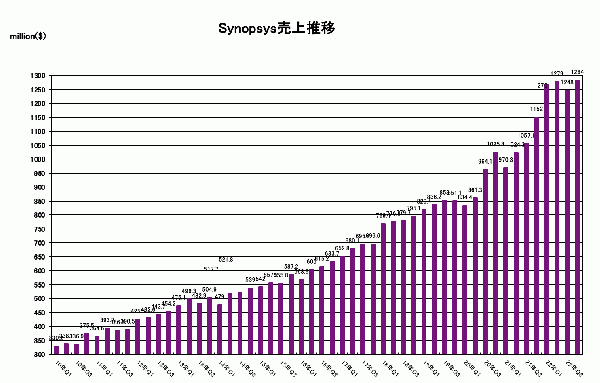

2023年5月17日、Synopsysは、2023会計年度第2四半期(23年2月-4月)の四半期決算を報告した。

発表によるとSynopsysの2023会計年度Q2の売上は、前年同時期比約9%増、前Q1比約2.5%増の13億9500万ドル、営業利益は前年比約7.5%減の2億7290万ドルだった。(※GAAP基準による会計結果)

このQ2売上結果はQ1売上報告時の予測を上回るもので同社の四半期売上記録を更新した。好調を維持するSynopsysは3四半期連続で四半期売上記録を更新している。

SynopsysはQ2(23年2月-4月)において以下のような発表を行なっている。

Synopsysは、2023年度Q3(5月-7月)の売上を14億6500万-9500万ドルと予測。更なる成長を見込んでいる。

2023.06.07

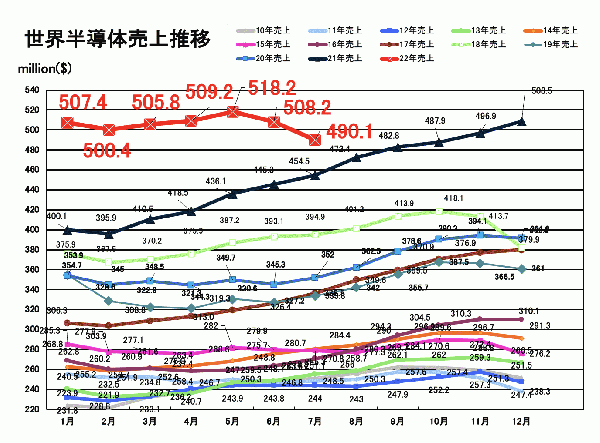

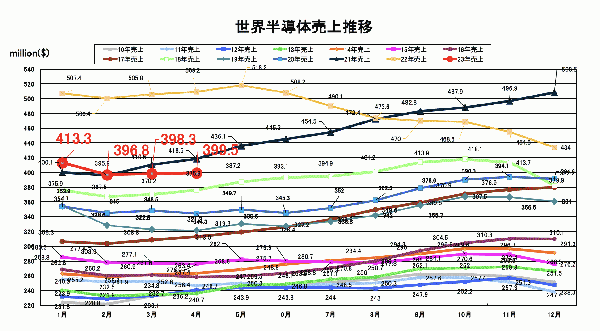

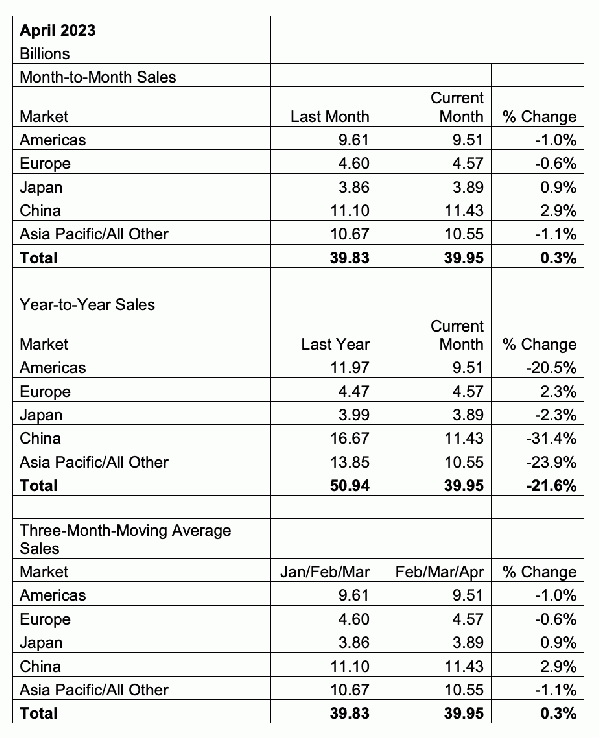

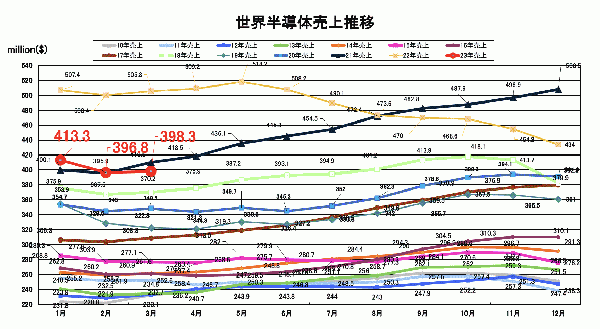

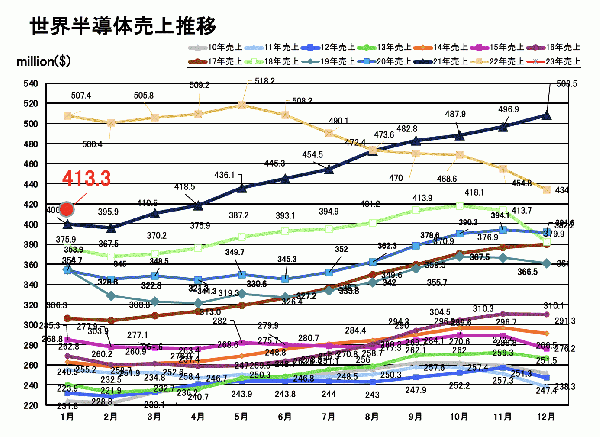

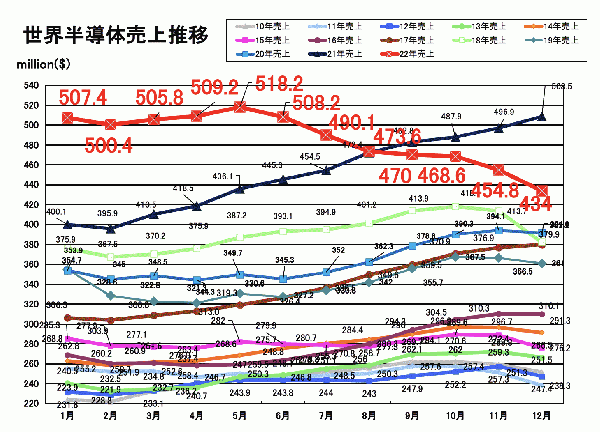

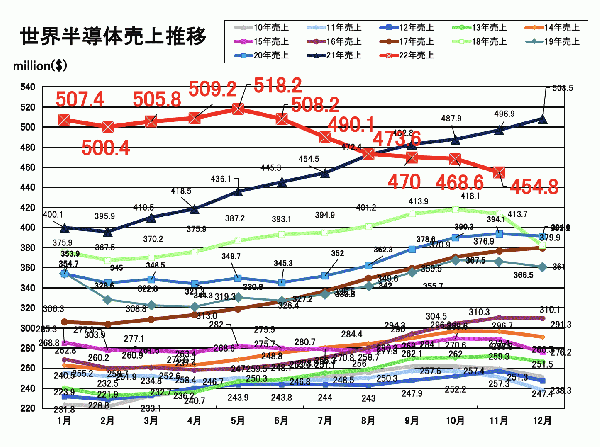

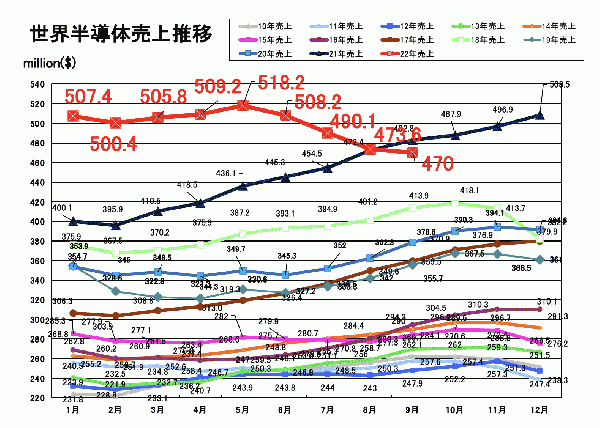

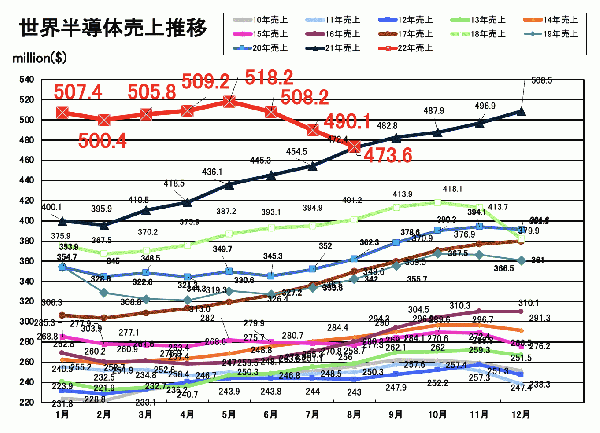

2023年6月6日、米SIA(Semiconductor Industry Association)は、2023年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2023年4月の世界半導体売上は、前年同月比約21.6%減、前月比約0.3%増の399.5億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのはこれで8ヶ月連続。

世界の半導体市場の売上鈍化は4月になっても収まる様子はなく、対前年比では3月の21.3%減を上回る減少率となった。

時同じくして発表されたWSTSの春季予測では、2023年の半導体市場は前年比10.3%のマイナス成長と予測されているが、現在のところ1月から4月にかけて平均20%のマイナス成長となっているため、下期以降の大幅な市場回復が無ければ予測を下方修正することになりそうだ。

2023年4月の世界半導体売上を地域別に見ると、欧州市場を除き全ての地域で前年比マイナス。主要市場の中国、アジア、北米は3月に続いて軒並み前年比20%以上のマイナスを記録。最大市場中国の落ち込みは若干緩んだが、それでも前年比31.4%減と深刻な状況となっている。

2023年4月の日本市場の売上を円ベースで換算すると前月比約0.3%増、前年比約3%増の約5,186億円。日本市場の売上が日本円換算で前年同月比プラス成長となるのはこれで29か月連続。円安の影響で売上増が続いているがドルベースでは前年比2.3減となっている。

2023.06.07

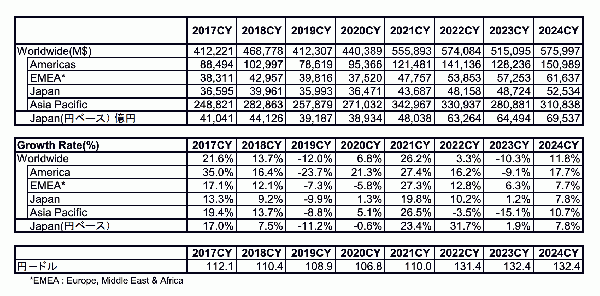

2023年6月6日、WSTS(WORLD SEMICONDUCTOR TRADE STATISTICS:世界半導体市場統計)は2023年半導体市場予測を発表した。

WSTSの予測によると2023年の世界半導体市場は前年比10.3%減の5,150億ドル。2,022年は前年比3.3%増の5,740億ドルだったが、今年は4年ぶりのマイナス成長となる見通しだ。

昨年11月にWSTSが発表した秋季予測では、2023年は前年比4.1%のマイナス成長と予測されていたが今回予測を下方修正した形となる。

マイナス成長の理由としては、景気悪化に伴うスマートフォン、パソコン、民生機器などの需要低迷を挙げており、メモリについては前年比35%減と大幅なマイナス成長を予測した。ロジック半導体については前年比1.8%減に留まるという予測で、電動化が進む自動車、再生エネルギー関連、生成AIなどが需要を押し上げる見通しだという。

2024年については景気回復を前提に前年比11.8%増の5,760億ドルと市場が再拡大すると予測している。

日本市場に関しては前年比1.2%増の478億ドルとプラス成長を予測。クルマ向けなどが需要をした支えする見通しだという。

予測通りとなると2023年の国内半導体市場は約6兆4,494億円(WSTSの想定レートで換算)となる。

なお、2024年の日本市場は前年比7.8%増の約6兆9,537億円と予測されている。

2023.05.19

2023年5月31日に組込みソフトウェア開発ツールを手掛けるIARシステムズ社とRISC-Vプロセッサを手掛けるCodasip(コダシップ)社が、「RISC-Vを始める前に知っておくこと」と題した面白いウェビナーを共同開催する。

副題は、【RISC-VインターナショナルBlog「RISC-Vに関する誤解のトップ10」の解説ウェビナー】となっており、こRISC-Vの生みの親であるDavid Patterson教授が2023年3月21日にRISC-VインターナショナルのBlogにアップした「Top Ten Fallacies About RISC-V(RISC-Vに関する誤解のトップ10)」を、IARシステムズとCodasipの両社が日本語で解説する。

RISC-Vは、誰でも無償で利用できるオープンな命令セットアーキテクチャとして世界中で注目を集めており、既に啓発期を超え教育や研究に限らず製品開発の現場で積極的に利用され始めている。そのエコシステムは日本でRISC-Vが紹介され始めた2017年当初と比較すると大きく拡大しており、今日では数多くの個人や企業がIP、開発ツール、ランタイムソフトウェア、チップ設計サービスなど、様々なRISC-Vソリューションを提供している。

しかしユーザーが増える一方で、RISC-Vに関しては「オープンソース?」「全て無料?」など、まだまだ基本的なところに多くの疑問や誤解が溢れているのも事実であり、おそらくそれを愁いたPatterson教授が誤解を解くために「RISC-Vに関する誤解のトップ10」と題したBlogを書いたのだと想像できる。

日本のRISC-V採用率は世界と比べてかなり低いようだが、RISC-Vに関する誤解がRISC-V採用の一つの障壁になっている可能性もある。RISC-Vについて理解が不十分と感じる方、これからRISC-Vにチャレンジするという方は、このウェビナーに参加すると面白いかもしない。

ウェビナーの開催時間は、2023年5月31日(水)午前11:00-午後12:00、事前登録制で参加は無料。参加者から抽選で2023年6月20日(火)開催予定の「RISC-V Days Tokyo 2023 Summer」の招待券がプレゼントされるということだ。(※RISC-V Days Tokyoは今回から有償に戻った。)なお、IARシステムズ社、Codasip社の各RISC-Vソリューションについては、RISC-V Days Tokyo 2023 Summerで聴講できる。

2023.05.09

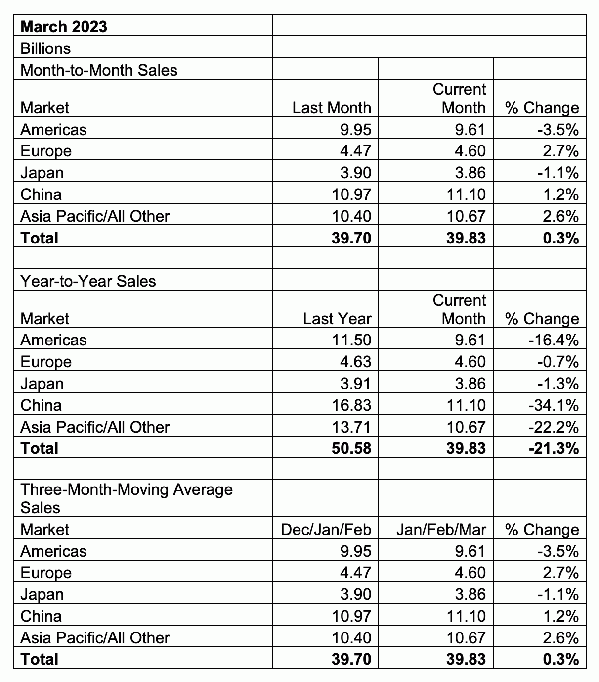

2023年5月1日、米SIA(Semiconductor Industry Association)は、2023年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2023年3月の世界半導体売上は、前年同月比約21.3%減、前月比約0.3%増の398.3億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのはこれで7ヶ月連続。

今年に入り世界の半導体市場は対前年比で1月は18.5%減、2月は20.7%減、そして3月は21.3%減と大幅な売上鈍化が続いている。2023年Q1(1-3月)の売上合計額は1195億ドルで2022年Q1と比較すると21.3%のマイナス。2023年の半導体市場は前年比で数パーセントのマイナス成長になるとWSTSほか各調査期間が予測しているが、このペースでいくと10%を超えるマイナス成長となる可能性が高まってきた。

2023年3月の世界半導体売上を地域別に見ると全ての地域で前年比マイナス。主要市場の中国、アジア、北米は1月,2月に続いて軒並み前年比2ケタ減を記録。米国規制の影響を受けている最大市場中国の落ち込みは前年比34.1%減と深刻な状況となっている。

2023年3月の日本市場の売上を円ベースで換算すると前月比約0.1%減、前年比約11.5%増の約5,167億円。日本市場の売上が前年同月比プラス成長となるのはこれで28か月連続。円安の影響で日本市場の売上増は現在も継続しているが、いよいよそれも頭打ちとなってきた感がある。

2023.04.21

2023年4月11日、新興FPGAベンダの米Rapid Siliconは、FPGA設計向けのHDLコーディング支援ツール「RapidGPT」を発表した。

発表によると「RapidGPT」はFPGA設計専用のツールで、高度な自然言語処理、コード・オートコンプリート機能そして会話機能によってHDLのコーディング作業を支援。Rapid Siliconは「RapidGPT」を利用することでFPGA設計者の生産性を2倍に向上できるとしている。

「RapidGPT」のインテリジェントなコード・オートコンプリートは、設計者のコマンドの意図を理解し関連する提案を示してくれる機能を備えており、コーディング作業を効率化することが可能。コーディング・エラーを防ぐのにも役立つ。VHDLに対応しているかどうかは定かではないが、Verilog-HDLはサポートしているようだ。

コードを自動生成してくれるツールとしては、GitHubが2021年にリリースした「Copilot」やAmazonが2022年にリリースした「CodeWhisperer」が有名だが、「RapidGPT」はそれらコード自動生成ツールのHDL版と言えるもの。「Copilot」の場合は、文章からプログラムコードを生成する「OpenAI Codex」と「GPT-3」をベースに作られており、GitHub上の膨大なオープンソース・コードによって学習されているが、Rapid Siliconの「RapidGPT」は何を使って学習したものか明らかにされていない。

Rapid Siliconは、2020年に設立されたFPGAスタートアップで「FPGAの民主化」を掲げてエッジAI向けの16nmミッドレンジFPGA「Gemini」と合わせてオープンソースのツールをベースとした独自のFPGA設計環境「Raptor」を提供している。誰でも扱えるオープンソースのEDAツールを用いて社名の通り迅速にシリコン(FPGA)を実現するというのが同社のモットーのようだ。

同社の会長兼CEO Naveed Sherwani氏は業界の大ベテランで、元Intelのゼネラル・マネージャーで、その後設計サービス会社Open Siliconを創設、同社がRISC-V IPのSiFiveに買収された後にはSiFiveのCEOも勤めていた。また同氏はオープンソースのFPGA設計ツールとIPブロックの普及推進を目指す

「Open-Source FPGA Foundation」の創設者でもあり、オープンソースとFPGA、そしてAIを組み合わせて半導体業界の中で新たなムーブメントを起こそうとしている。

今回発表された「RapidGPT」は商用ツールとして発売されるようだが、その提供開始時期や価格、ツールの機能詳細については今のところ明らかにされていない。確認したところ、Rapid Siliconは7月にサンフランシスコで開催されるDAC2023には出展するようなので、DACに合わせて詳細な製品発表が行われるかもしれない。

2023.04.20

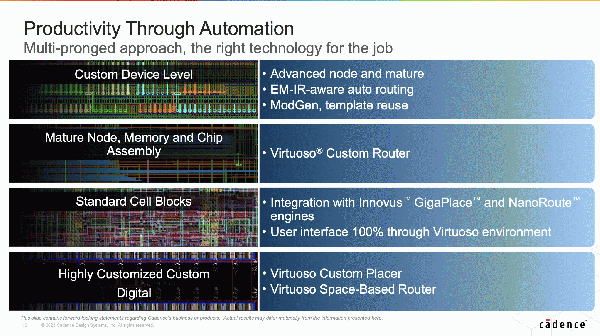

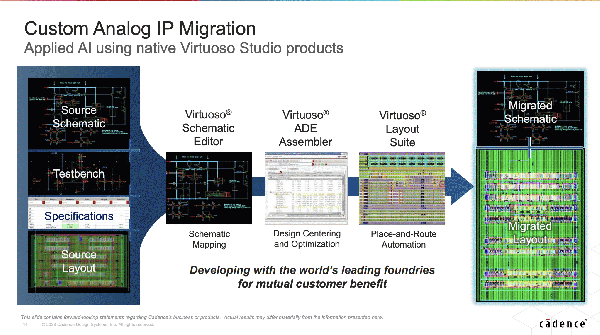

2023年4月20日、Cadenceはアナログ/カスタム設計の新製品「Virtuoso Studio」を発表した。

新製品「Virtuoso Studio」は、Cadenceの主力製品「Virtuoso」をメジャー・バージョンアップした製品でAI技術の実装をはじめ数多くの機能強化が図られている。

「Virtuoso」は約3年ぶりのバージョンアップとなるが、製品名が「Virtuoso Studio」と命名され、アナログ/カスタム/RF設計のより中心的なツールとしてコックピットのような役割を担うようになった。具体的には、以下に挙げたようなアナログ/カスタム/RF設計を取り巻く同社の各ツールが「Virtuoso Studio」とシームレスに統合され、これらツールの機能を「Virtuoso Studio」からアクセスすることが可能となった。

・回路シミュレータ「Spectre」

・PCB設計環境「Allegro」

・物理検証ツール「Pegasus」

・RF/マイクロ波設計ツール「AWR Microwave Office」

また周辺ツールとの連携としては、「Virtuoso Studio」からデジタル・インプリメント環境「Innovus」を呼び出しロジック・ブロックの配線が可能となったほか、PCB設計環境「Allegro」との連携により3D-IC設計、フォトニクス・システムも「Virtuoso Studio」の守備範囲となった。

新しい「Virtuoso Studio」は、あらゆるプロセス技術において設計生産性を3倍向上できるということだが、Cadenceは下記のようなエンハンス項目によってそれが実現されていると説明している。

・最先端3nmプロセスへの対応

・クラウド対応の強化(分散処理性能の強化)

・アナログ自動配置配線機能の強化

・インデザイン検証(物理検証)の性能改善

・AIを活用したデザイン・マイグレーション

・複数PDKの読み込み対応

※Virtuoso Studioのレイアウト機能の強化

クラウド対応については、新機能である「Simulation Manager」によりシミュレーション・ジョブの分散処理性能が強化され、省メモリ化など負荷の低減により数千のジョブにも高速に対応できるようになったという話。

AIを活用したデザイン・マイグレーションは今回のバージョンアップの目玉機能で、アナログ回路の実装プロセスを移行する際に既存のレイアウトデータを元にAI技術でバーチャル・プロトタイピング(仮のレイアウト)を作成。それを元に寄生予測と寄生を含めたパラメータの最適化を行い、回路図のマッピングを含めほぼ自動処理でプロセス・マイグレーションを完了できるという。

※Virtuoso Studioのプロセス・マイグレーション

Cadenceは既にデジタル回路のインプリメンテーション、ベリフィケーション、システム設計といった分野でAI機能のツール実装を実現しているが、アナログ/カスタム設計関連のツールでのAI機能の実装は今回が初めて。「Virotuoso」はCadenceの主力製品なだけに、AI機能を含め今回のバージョンアップが現場の設計をどれだけ変えるのか? 顧客事例の発表が楽しみだ。

2023.04.19

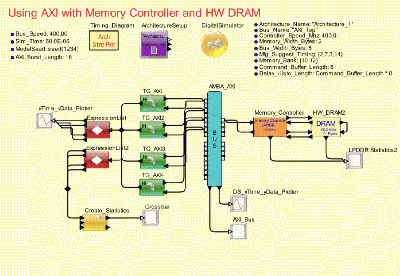

2023年4月12日、ESLツールを提供するEDAベンダ米Mirabilis Designは、同社のシステム・シミュレータ「VisualSim Architect」をデンソーが導入したことを発表した。

米Mirabilis Designの「VisualSim Architect」は、システム仕様の検討やアーキテクチャ探索に用いるシステム・シミュレータで、グラフィカルな環境を用いてシステム・モデルを容易に構築することが可能。構築したシステム・モデルをシミュレーションすることで、システム仕様の妥当性やシステムの機能、性能、消費電力などを評価・解析できる。システムを構成する各種コンポーネントモデルはあらかじめ用意されているものの他に自作することも可能。用途に応じてモデルのパラメータや精度を変更することで様々なシミュレーション結果を得ることができる。

※VisualSimで作成したモデル例

この「VisualSim」日本では馴染みの薄いツールだが、その歴史は古く2006年に製品化され、米国国防関連の大手企業に広く使われている実績がある。高度に複雑なシステムの仕様をシミュレーションしながら検討するという用途に重宝されているツールだ。

今回デンソーは、車載ネットワーク開発の効率的に向けて「VisualSim Architect」を導入。複数のシミュレーターを評価した結果、システム・モデルの構築のしやすさとツールの使いやすさから「VisualSim」を選択した。

デンソーのターゲットは車載ネットワーク・アーキテクチャからGateway等のECUの通信処理までを含めたシステムの開発で、通信パケットの遅延時間やパケットロスの見積りなどを行うためのシミュレーション環境を「VisualSim」を用いることで短時間に構築できたという。

なお、このデンソーの事例については、5/24にデンソーとMirabilis Designが共同で開催するウェビナーで紹介される予定となっている。

2023.04.18

2023年3月29日、Synopsysはサンタクララで開催した同社のイベントSNUGにて、フルスタックのAIドリブンEDAスイート「Synopsys.ai」を発表した。

発表によるとAIを用いた新ソリューション「Synopsys.ai」は、デジタル設計、アナログ設計、検証、テスト容易化設計、製造容易化設計の各フローに対応するEDAスイートで、具体的には以下に挙げるような処理・作業を実現。既にNVIDIA、TSMC、IBM、MediaTek、ルネサスといった大手各社が同ソリューションを活用して成果をあげたとしてコメントを寄せている。

・デジタル・インプリメンテーションの最適化

・アナログ・デザインのプロセス・ノード間移行の自動化

・機能検証の高速化とカバレッジ向上、予測的なバグ検出

・シリコンテスト用テストパターンの最適化と自動生成

・高精度なリソグラフィー・モデル開発の加速

Synopsysは主力のデジタル設計を中心に早くからAIベースEDAツールの開発に積極的に投資しており、その核となるデジタル・インプリメンテーション向けのソリューション「DSO.ai(Design Space Optimization AI)」を用いたテープアウト実績は既に100品種を達成。先端プロセスを用いた高性能なチップを開発するSynopsysの顧客にとって、AIベースのEDAツールは既になくてはならないものになりつつある。同時にSynopsysはAI技術の横展開も進めてきており、遂にアナログ設計、テスト容易化設計、製造容易化設計も含めた形でチップ開発フローを一通り網羅できるAIベース・EDAソリューションが整った。それが今回発表した「Synopsys.ai」となる。

なおSynopsysによると同社の「Synopsys.ai」ソリューションは現在、半導体メーカー上位10社のうち9社で導入済み。「Synopsys.ai」の各EDAツールに組み込まれている各種AIエンジンは、設計プロジェクトごとに独自のデータ・セットで継続的にトレーニングを行うため、時間の経過とともに設計結果最適化の熟練度が向上。すなわち使えば使うほど賢くなるということだ。

2023.04.11

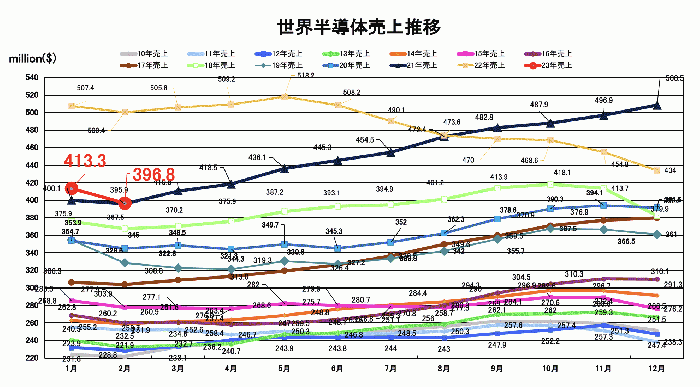

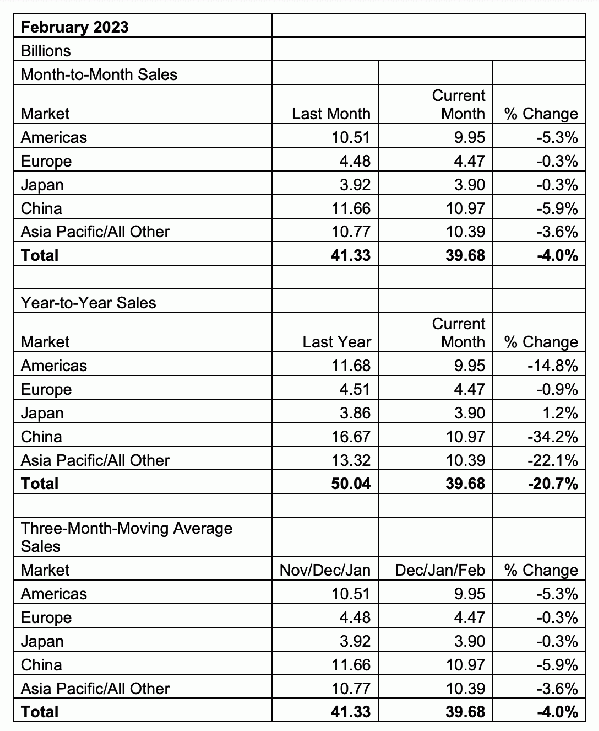

2023年4月6日、米SIA(Semiconductor Industry Association)は、2023年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2023年2月の世界半導体売上は、前年同月比約20.7%減、前月比約4.7%減の396.8億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのは6ヶ月連続。

2023年の半導体市場は前年比で数パーセントのマイナス成長になるとWSTSほか各調査期間が予測しているが、既に1月、2月と急ブレーキがかかっており、このペースでいくと10%を超えるマイナス成長となる可能性もある。

2023年2月の世界半導体売上を地域別に見ると、日本以外は全ての地域で前年比マイナス。主要市場の中国、アジア、北米は1月に続いて軒並み前年比2ケタ減を記録。米国規制の影響を受けている最大市場中国の落ち込みは深刻な状況となっている。

2023年2月の日本市場の売上を円ベースで換算すると前月比約1.2%増、前年比約16.2%増の約5,170億円。日本市場の売上が前年同月比プラス成長となるのはこれで27か月連続。円安の影響で日本市場の売上増は現在も継続している。

2023.03.15

2023年3月14日、Rambusは、ArmのセキュリティIP「CryptoCell」および「CryptoIsland」の提供開始を発表した。

発表によるとRambusは、これまでArmが提供していたセキュリティIP製品「CryptoCell」と「CryptoIsland」の2品種をArmに代わってユーザーに提供することに。製品の供給だけではなく継続的な開発もRambusが担っていくということだ。

ArmとRambusの両社は以前からセキュリティIP製品の開発や普及に向けて協力関係を築いてきた経緯があり、その一つのゴールとして今回ArmがセキュリティIPの事業をRambusに移管した格好となる。

なお、既存のArmユーザーは「CryptoCell」と「CryptoIsland」のライセンスをそのまま利用することが可能。今後、両IP製品の新規のユーザーは、Rambusからライセンスを受けることになる。

「CryptoCell」はArmのハードウェアベースのセキュリティ機能「TrustZone™」を補完するセキュリティ・サブシステムで、「Arm Cortex-M™」および「Cortex-A™」搭載のSoCに、プラットフォーム・セキュリティ・サービス(鍵管理、暗号サービス等)を提供するもの。IoTデバイスをターゲットにした「CryptoCell-300」とモバイル, DTV, STBなどをターゲットとした「CryptoCell-700」の2つのファミリーがある。

「CryptoIsland」は「CryptoCell」周りのサブシステム統合したセキュリティ・エンクレーブで、ホストプロセッサから独立して使用することが可能。同製品は以前からArmが開発を示唆していたが、これまで正式な製品リリースはアナウンスされておらず、今回の移管に伴いRambusが製品化に携わったと想像できる。

Rambusは10年ほど前からセキュリティ分野の製品拡充を積極的に進めており、Root of Trustソリューション、DPA(サイドチャネル攻撃)対策ソリューション、IoT向けソリューションなど多彩な製品をラインナップしている。今回Armから受け継いだIP資産はRoot of Trustソリューションの新たなラインナップとしてRambusのセキュリティIP製品群に加わることになる。

2023.03.06

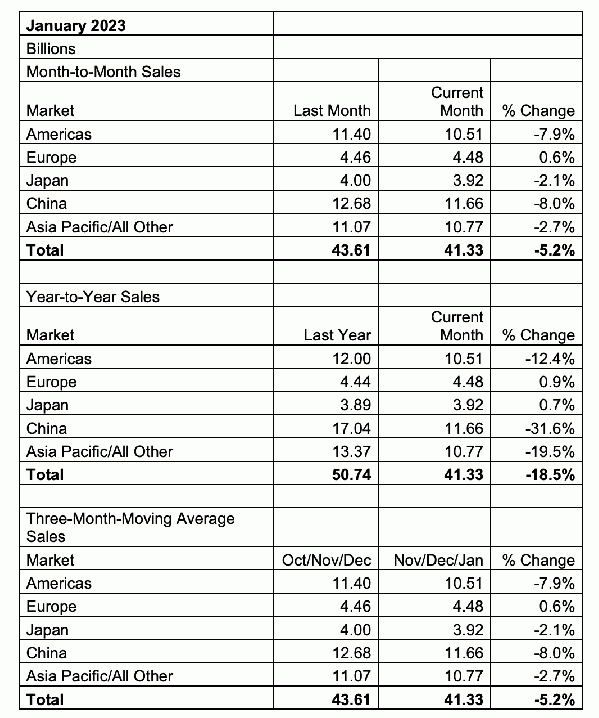

2023年3月3日、米SIA(Semiconductor Industry Association)は、2023年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2023年1月の世界半導体売上は、前年同月比約18.5%減、前月比約4.8%減の413.3億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのは5ヶ月連続。

WSTS(世界半導体市場統計)は昨年11月末に発表した秋季予測において、2023年は前年比4.1%減のマイナス成長と予測している。

日本市場に関しては円安効果により2023年は前年比6.2%増、市場規模は約6兆6,684億円になると予測している。

2023年1月の世界半導体売上を地域別に見ると、日本と欧州以外の主要市場は軒並み前年比2ケタ減を記録。中でも最大市場の中国市場は前年比31.6.%減と大きく売上が落ち込んだ。需要の減退に加え米国による対中国への半導体規制が大きく影響していると考えられる。

2023年1月の日本市場の売上を円ベースで換算すると前月比約9.7%減、前年比約14.3%増の約5,110億円。日本市場の売上が前年同月比プラス成長となるのはこれで26か月連続。昨年9月以降の急激な円安の影響でこの5ヶ月は大幅な売上増が続いているが、12月から1月にかけては大きく円高が進み円ベースの売上減少に繋がっている。

2023.02.19

2023年2月15日、Synopsysは、2023会計年度第1四半期(22年11-23年1月)の四半期決算を報告した。

発表によるとSynopsysの2023会計年度Q1の売上は、前年同時期比約7.1%増、前Q4比約6%増の13億6100万ドル、営業利益は前年比約13.5%減の2億7150万ドルだった。(※GAAP基準による会計結果)このQ1売上は前Q4売上報告時の予測の範囲内で2022年Q4に続いて再び同社の四半期売上記録を更新した。

Synopsysは、2023年度Q2(2-4月)の売上を13億6000万-9000万ドルと予測している。

2023.02.17

2023年2月7日、Synopsysは同社のAIベースのEDAツール「DSO.ai(Design Space Optimization AI)」を用いた商用チップのテープアウトが100件に達したことを発表した。

Synopsysが「DSO.ai」を発表したのが2020年の初頭なので、約3年で100件のテープアウトを達成した形となるが、Synopsysはこの成果を受けて「AIベースのチップ設計が実用段階に入った」としている。

すでにSynopsysのユーザーから「DSO.ai」を用いた様々な設計事例が発表されているが、今回の発表ではSTMicroelectronicsとSK hynixの両社が「DSO.ai」の適用効果についてコメント。

STMicroelectronicsは、クラウド・ベース・バージョンの「DSO.ai」を用いてMicrosoftのAzure環境でPPA検討の生産性を3倍以上効率化することに成功。SK hynixは、直近のプロジェクトで「DSO.ai」を用いることによりセル面積15%削減、ダイサイズ5%削減という成果を得ているという。

AI機能を活用したチップ設計は、インプリメントの最適化を中心に検証の効率化に向けても適用が進んでいる。近年、かつての論理合成ツールのように設計にブレイクスルーをもたらす新技術は久しく現れていなかったが、AI技術の進化という大きな波は既にチップ設計を変え始めている。

2023.02.16

2023年1月10日、インターコネクトIPを手がける米Arteris IPは、レジスタ設計ツールを提供する米EDAベンダSemifore社の買収を発表した。

ArterisによるSemiforeの買収はすでに完了しており、その取引条件などは明らかにされていない。

Semiforeは2006年設立のEDAベンダで「CSRCompiler」というレジスタ設計ツールを提供していた。

「CSRCompiler」は、同社の開発した専用のレジスタ仕様言語「CSRSpec」で記述されたアドレスマップから、ハードウェア開発向けの合成可能なRTL、ソフトウェア開発向けのC/Perlのヘッダ、検証用のC、Vera、Verilog、デザインチーム向けのHTMLページやドキュメントを出力するツールで、ハード/ソフト異なるチームにおけるレジスタ回りの設計を一元管理・効率化できる。ツールへの入力としてはレジスタ記述言語「SystemRDL」や「IP-XACT」もサポートしているほか、ユーザー既存のアドレスマップ(スプレッドシート)をインポートすることもできる。

今後SemiforeのメンバーはArteris IPの傘下として活動を継続するようだ。

2023.02.15

2023年2月3日、TSMCは、「TSMC ユニバーシティ FinFET プログラム」の開始を発表した。

発表によると「TSMC ユニバーシティ FinFET プログラム」は、その名の通り大学の学生や教職員など学術関係者に向けたプログラムでその骨子は大きく2つ。

1. TSMC 16nm FinFET技術のPDKの提供:

教育用の設計資料としてTSMC N16プロセスの設計事例チュートリアル、トレーニング資料、教育ビデオなども提供される。

2. マルチ・プロジェクト・ウエハー (MPW) サービスを通じたTSMC 16nm (N16) および 7nm (N7) シリコンへのアクセスの提供:

ロジック、アナログ、RFなど各種テストチップ用のN16およびN7プロセス設計資料も提供される。

TSMCは同プログラムを通じて業界で最も成功した 16nm FinFET技術を学界に提供することで、半導体分野の学術的なイノベーションに貢献するとしている。

2023.02.14

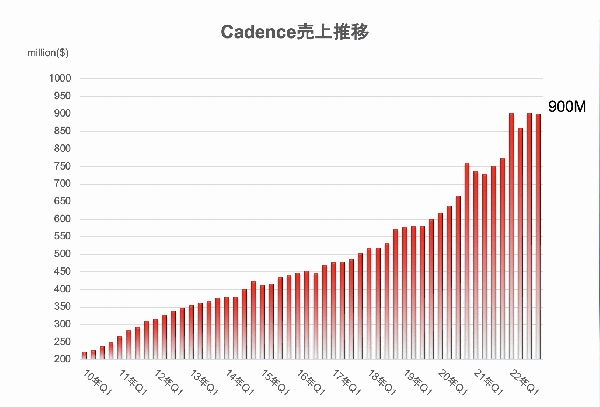

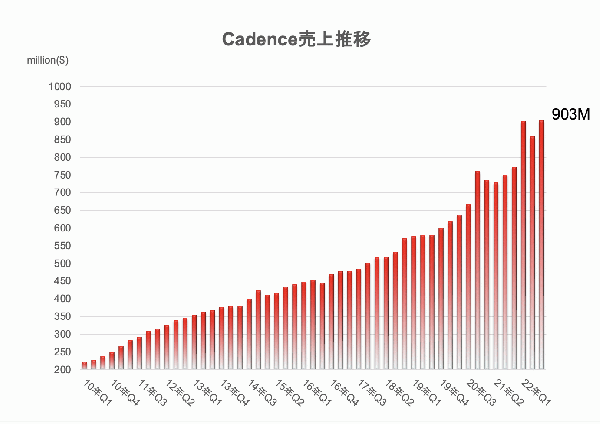

2023年2月13日、Cadenceは、2022会計年度第4四半期(2022年10-12月)の売上を報告した。

Cadenceの2022年Q4売上は、前年比約16.4%増、前期Q3とほぼ同等で微減の9億ドル、営業利益は前年比約35.6%増の2億4000万ドルだった。(※GAAP基準による会計結果)このQ4実績は同社の予測を上回るもので同社の四半期売上記録として過去3番目の実績となる。(過去最高は2022年Q3で9億300万ドル)

Cadenceの2022会計年度の売上合計額は、前年比19.2%増の35億6200万ドルで過去最高を更新。営業利益は前年比22%増の8億4900万ドルだった。(※GAAP基準による会計結果)

Cadenceは、2023年Q1の売上を10億-10億2000万ドル、2023年度の売上を40億-40億6000万ドルになると予測している。

CacdenceはこのQ4(2022年10-12月)において以下のような発表を行っている。

2023.02.14

2023年1月31日、SIemensは機械学習を用いた論理検証向けの新製品「Questa™ Verification IQ」を発表した。

発表によると「Questa Verification IQ」は、Siemensの提供する各種論理検証向けツールからカバレッジ・データを収集し、機械学習機能を用いて検証のTAT短縮を実現するというデータ駆動型の検証ソリューションで、具体的にはデザイン内のパターン抽出、カバレッジ・ホールやバグの根本原因の特定、カバレッジを向上させる可能性が高いテストの特定などを行うことが可能。下記の検証ツールをサポートしている。

・シミュレータ「Questa™ プラットフォーム」

・フォーマル検証ツール「OneSpin®」

・ アナログ/ミックスドシグナル・シミュレータ「Symphony™」

・エミュレーター「Veloce™」

「Questa Verification IQ」は、Siemensの要件管理ツール「Polarion REQUIREMENTS」とシームレスに統合しており、検証ワークフロー全体にわたって実行されるすべてのエンジンからすべてのデータを自動的に取得するプラットフォームを提供。検証の管理と加速、潜在的な問題の解決策を提示すると同時に要件のトレーサビリティの合理化も実現するとしている。

発表にコメントを寄せた先行ユーザーのArmおよびNordic Semiconductorは、「Questa Verification IQ」の活用効果として、カバレッジ収束の効率化、検証時間の大幅な短縮を挙げている。

なお「Questa Verification IQ」は、Web ベースのアプリケーション・フレームワークに実装されており、パブリック、プライベート、およびハイブリッド・クラウド構成をサポート。多拠点およびチームによるリアルタイムの共同検証作業にも活用することができるという。

2023.02.07

2023年2月3日、米SIA(Semiconductor Industry Association)は、2022年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2022年12月の世界半導体売上は、前年同月比約14.7%減、前月比約4.4%減の434億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのは4ヶ月連続。

2022年1月から12月通年の売上合計は前年比約3.2%増の5,737億ドルで過去最高を更新。上半期は順調な成長を見せていたが8月から成長が鈍化し、当初予測されていた通年売上6,000億ドル超えは実現しなかった。

WSTS(世界半導体市場統計)は今年6月時点で2022年の売上を前年比16.3%増の6,465億ドルと予測していたが、その後8月に前年比13.9%増の6,330億ドルに下方修正、11月末には前年比4.4%増の5,803億ドルと下方修正していた。

2022年の世界半導体売上を地域別に見ると、アメリカ市場が前年比16%増と地域別では最大の伸びを記録。欧州は12.7%増、日本は10%増と続いた。最大市場の中国市場は前年比6.3%減だった。

2022年の世界半導体売上を製品セグメント別に見ると、アナログ製品が成長率 7.5%と最も高く、2022年の売上は890億ドルに達した。ロジック製品の売上は1,760億ドル、メモリ製品の売上は1,300億ドル、自動車向けICの売上は前年比 29.2%増の341億ドルに達した。

2022年12月の日本市場の売上を円ベースで換算すると前月比約1%減、前年比約25.9%増の約5,655億円。日本市場の売上が前年同月比プラス成長となるのはこれで25か月連続。9月に入ってからの急激な円安の影響でこの4ヶ月は大幅な売上増となっている。

2023.01.27

2023年1月20日、Cadenceは同社の顧客である台湾GUCによる3nmチップ設計の成功事例を発表した。

発表によるとGUCはTSMC N3プロセスをターゲットとしたHPC向けコアの開発にCadenceの配置配線ツール「Innovus™ Implementation System」を使用。インスタンス数350万、最大クロック3.16GHzの先進的なデザインを実現した。この事例はGUC初の3nmチップ設計だったという。

またGUCは合わせてTSMC N5プロセスをターゲットとしたCPU設計も行い、CadenceのAI最適化ツール「Cerebrus™ Intelligent Chip Explorer」とCadenceのデジタル・インプリメント・フローを使用することでエンジニアリングの生産性を向上しながら、消費電力を8%、面積を9%削減することに成功したとしている。

Cadenceの配置配線ツール「Innovus™ Implementation System」には、「GigaPlace」や「GigaOpt」と呼ぶ強力な配置、最適化エンジンが装備されており、TSMC N3プロセスターゲットのデザインに対しても効果を発揮するという。

2023.01.25

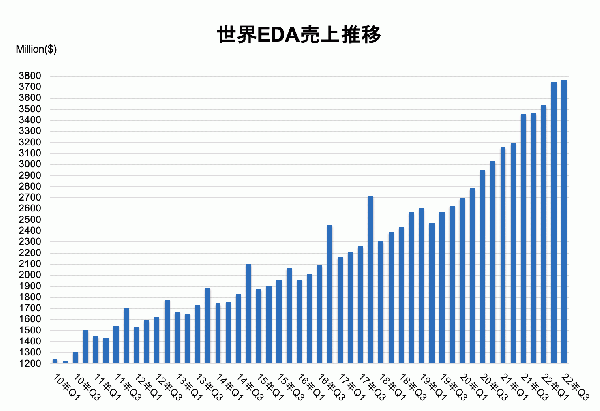

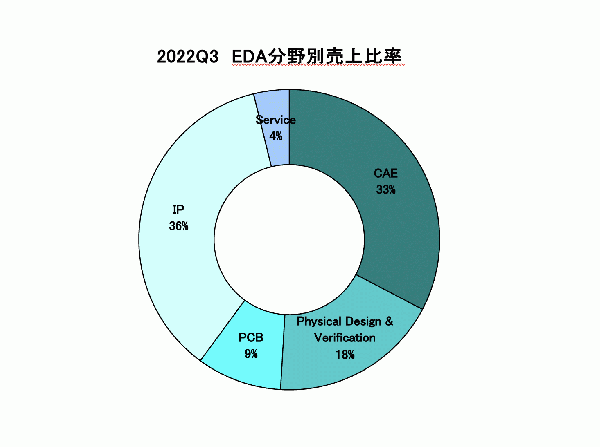

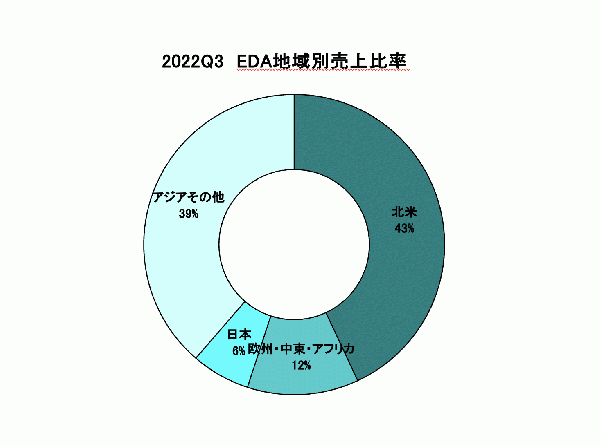

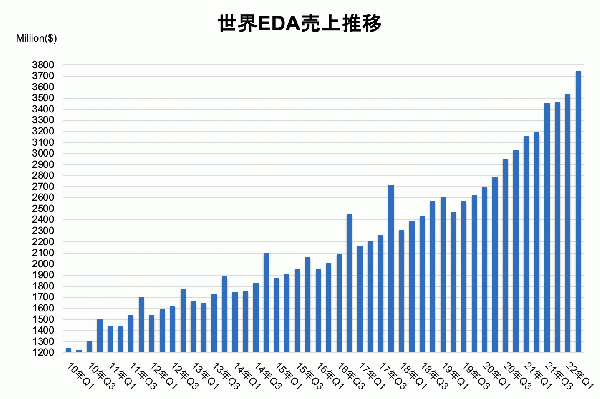

2023年1月23日、米ESD Allianceは、2022年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると2022年Q3(7-9月)の世界のEDA売上総額は、前年比約8.9%増、前Q2比約5%増の37億6740万ドルで四半期売上記録を更新した。記録の更新は10四半期連続。四半期売上が前年実績を上回るのは15四半期連続となる。

2022年Q3のEDA売上をカテゴリ別に見るとIP分野を除く全てのカテゴリで前年比2ケタ増を達成。IP分野はQ2まで四半期売上記録の更新を続けていたがQ3はQ2実績を割り込んだ。半導体市場の減速が影響しているのかもしれない。

2022年Q3のEDA売上を地域別に見ると、日本市場を除く全ての地域で前年比プラス成長を記録したが、いずれの市場も成長率はQ2の水準を割り込んでいる。

2022年Q3時点でのEDA業界の従業員数は前年比8.2%増の55,369人でQ2よりも約1.7%増加した。

2022年Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 12億3120万ドル 16.7%Up

■IC Physical Design & Verification分野 6億8740万ドル 12.2%Up

■IP分野 13億6020万ドル 1%Down

■サービス分野 1億4400万ドル 20.8%Up

■PCB/MCM分野 3億4470万ドル 15.6%Up

2022年Q3の地域別の売上と昨年同時期との比較は以下の通り。

■北米 16億2210万ドル 8.5%Up

■欧州・中東・アフリカ 4億5100万ドル 0.2%Up

■日本 2億3780万ドル 3.5%Down

■アジアその他地域 14億5640万ドル 16.3%Up

2023.01.17

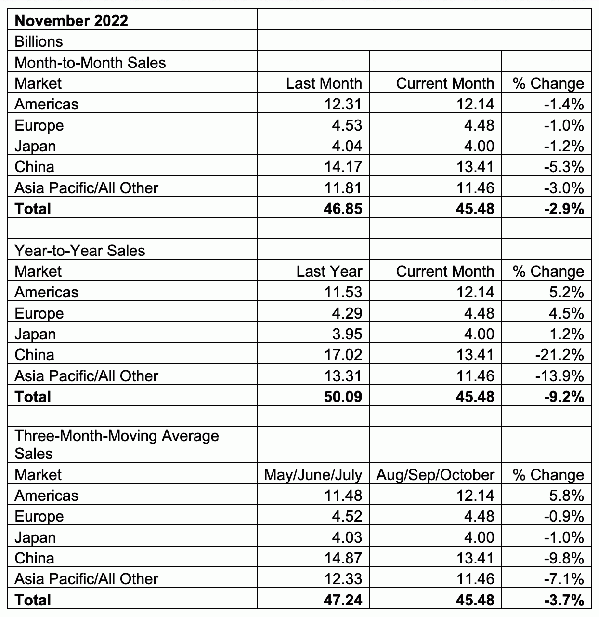

2023年1月日、米SIA(Semiconductor Industry Association)は、2022年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2022年11月の世界半導体売上は、前年同月比約9.2%減、前月比約3%減の454.8億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのは3ヶ月連続。2年半以上に渡って続いていた半導体業界の成長は9月以降マイナス成長に転じており、2022年の世界半導体市場は4.4%程度の成長に留まると予測されている。

2022年11月の世界半導体売上を地域別にみると、10月まで対前年比2桁成長を維持していた北米市場の売上が前年比5.2%増まで減少、欧州および日本市場もそれぞれ4.5%,1.2%とかろうじてプラス成長を維持した。最大市場の中国市場そしてアジア市場は急ブレーキと言えるほど売上が落ち込んでおり、それぞれ21.2%, 13.9%のマイナス成長となっている。

11月の日本市場の売上を円ベースで換算すると前月比約4.1%減、前年比約26.8%増の約5,712億円。日本市場の売上が前年同月比プラス成長となるのはこれで24か月連続。9月に入ってからの急激な円安の影響でこの3ヶ月は大幅な売上増となっている。

2022.12.09

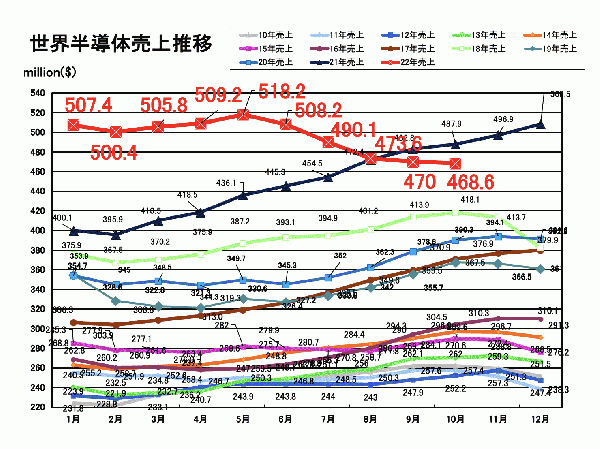

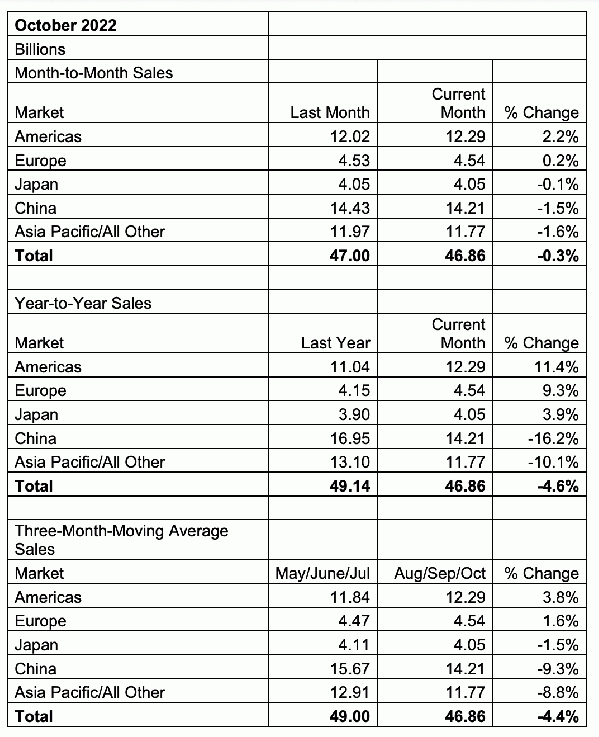

2022年12月5日、米SIA(Semiconductor Industry Association)は、2022年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2022年10月の世界半導体売上は、前年同月比約4.6%減、前月比約0.3%減の468.6億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのは2ヶ月連続。2年半以上に渡って続いていた半導体業界の成長は9月以降マイナス成長に転じた。世界の半導体市場は昨年5月をピークに売上下降基調に入っており、世界半導体貿易統計 (WSTS) は2022年11月末の時点で2022年の世界半導体市場の成長予測をプラス4.4%と下方修正している。(8月時点では13.9%のプラス成長と予測していた)

2022年10月の世界半導体売上を地域別にみると、北米市場だけが対前年比2桁成長をかろうじて維持、欧州、日本もプラス成長を維持しているが、最大市場の中国市場そしてアジア市場のマイナス成長が共に加速している。

日本市場の売上を円ベースで換算すると前月比約2.6%増、前年比約34.9%増の約5,954億円。日本市場の売上が前年同月比プラス成長となるのはこれで23か月連続。9月に入ってからの急激な円安の影響で大幅な売上増となっている。

2022.12.08

2022年11月30日、Synopsysは、2022会計年度第4四半期(22年8-10月)の四半期決算を報告した。

発表によるとSynopsysの2022会計年度Q4の売上は、前年同時期比約11%増、前Q3比約2.9%増の12億8400万ドル、営業利益は前年比約24%減の1億5350万ドルだった。(※GAAP基準による会計結果)このQ4売上はQ3売上報告時の予測通りで同社史上過去最高の四半期売上となる。

Synopsysは2022会計年度の売上合計額は、前年比20.9%増の50億8200万ドル、営業利益は前年比30%増の9億8460万ドルだった。2022会計年度の売上額はもちろん過去最高。同社は2023会計年度も継続した成長を見込んでおり、現時点で売上額を57億7500万〜58億2500万ドルと予測している。

SynopsysはQ4(22年8月-10月)において以下のような発表を行なっている。

2022.11.16

米Altair Engineering(日本法人:アルテアエンジニアリング株式会社、以下:アルテア)はミシガン州に本社を置くソフトウェア・ベンダーで、データ分析とAI、CAE、HPCの各分野にソリューションを提供している。エンジニアリング・サービスから発展した同社は製品開発向けのCAEソフトを軸に成長を遂げ、2017年にNASDAQ上場。現在はワールドワイドに3,000人以上のエンジニアを抱えグローバルなテクノロジー企業として1万社を超える顧客企業の製品開発やサービスを支えている。

半導体設計およびEDAの世界では一見馴染みの薄い同社だが、実は大手半導体ベンダー各社にHPCソリューションとして半導体設計ワークロードの管理ツールを提供しており、半導体製品の開発におけるTAT短縮やコスト削減に貢献している。ここではそのソリューションの概要と実際の顧客事例について紹介していきたい。

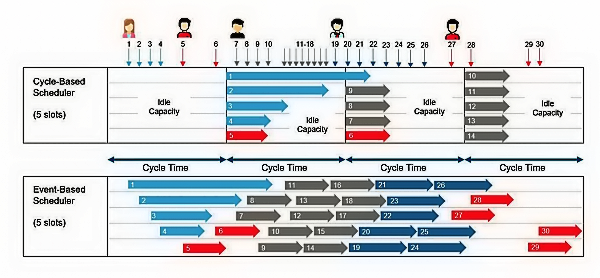

■半導体設計専用のジョブ・スケジューラ「Altair Accelerator」

アルテアの提供するHPCソリューションの中で半導体ベンダー各社に密かに重宝されているのが「Altair Accelerator」という半導体設計専用のジョブ・スケジューラで、半導体設計ワークロードの最適化に活用されている。半導体設計ワークロードとは、EDAツールを用いて各工程で行われる一連の設計・検証作業そのもので、「Altair Accelerator」は与えられた計算機リソースとEDAツールライセンスを用いて如何に速く、そして無駄なく効率的にツール処理を完了させるかという命題に答えを出してくれる。

例えばEDAツールに実行させるジョブのスケジューリングにおいては、ジョブの依存関係を管理するだけでなく、EDAライセンスの機能や数、計算リソースの状況、ジョブの優先順位などを考慮したスケジューリングが可能。優先実行やリソース予約などの機能により、緊急性の高いジョブを重要度の低い他の設計ワークロードよりも優先させて実行させたり、実行中のジョブを一時停止し、優先順位の高いジョブが完了した時点で再開するといったことも可能だという。

実際に「Altair Accelerator」を導入しているDSPコアで有名なイスラエルのファブレス半導体ベンダ「CEVA」では、「Altair Accelerator」の優先実行機能によりタイムクリティカルなジョブが待機していることを検知し、実行中のジョブに対して取り下げや再投入などの調整を即座に行うといった運用で、シミュレータを用いて365日24時間リグレッション検証を行う環境を構築できたという事例を報告している。この例は高価なEDAツールライセンスを使い倒す究極の形と言えるだろう。(※

参照URL)

また「Altair Accelerator」は、ミリ秒単位で応答するイベント・ドリブン型のスケジューラであるため、数秒単位で駆動するサイクル・ベース型のスケジューラよりも遥かに高速にジョブを投入することが可能。すなわち時間当たりのジョブ投入数を増やし計算機リソースの利用率を向上できるという訳だ。

※画像はアルテア提供のデータ

昨年Marvellに100億ドルで買収された、通信/データセンター向けアナログ/ミックスドシグナル半導体のInphiは、「Altair Accelerator」の導入により設計チームの規模を拡大することなく、より多くの作業をより短時間で行うという設計の効率化を実現。光インターフェイスで使用されるコヒーレントDSPチップやイーサネット・トランシーバーなどの主力製品の早期市場投入を達成したという事例を報告している。

同Inphiの事例によると、「Altair Accelerator」のスケジューラは評価した他のサイクル・ベースのスケジューラよりもスケジューリング速度が10倍速かったという話だ。(※

参照URL)

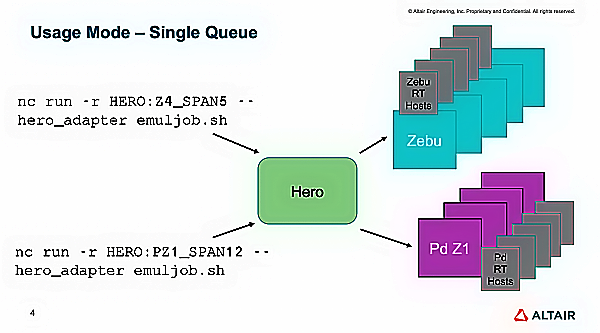

■エミュレータのワークロードも最適化

アルテアは、ハードウェア・エミュレータ向けのジョブ・スケジューラ「Altair Hero」という製品も提供している。この製品は、異なる設計チーム間でハードウェア・エミュレータを共有して運用する場合に使うフロントエンド・ツールで、ハードウェア・エミュレータのリソースの割り当てを自動化してくれるもの。

「Altair Hero」はEDAベンダの製品に依存せず、Cadenceの「Palladium」、Siemensの「Veloce」、Synopsysの「ZeBu」のジョブ・スケジューリングを管理することが可能。モデルのコンパイル、エミュレータの自動選択、リグレッションの実行など、エミュレーション・ジョブをエンドツーエンドで一元管理することができる。

「Altair Hero」を通じた1つのジョブ・キューで、同一アーキテクチャまたは異なるアーキテクチャの複数のエミュレータ・インスタンスにエミュレーション・ジョブをディスパッチすることも可能で、シミュレータよりもはるかに高価なエミュレータのリソースを最大限有効利用するのに役立つという。

※画像はアルテア提供のデータ

■11/25 Design Solution Forum 2022で講演

アルテアは、来る11/25開催のセミナー・イベント「Design Solution Forum 2022」にて「Altair Accelerator」をはじめとする同社の半導体設計向けソリューションについて講演を行う予定。

講演タイトル:「米国大手半導体メーカが採用する、高スループットなEDAジョブワークロード管理ツール」

講演者:アルテアエンジニアリング株式会社 エンタープライズ事業部 渡邊 大祐

講演時間:11/25 16:10-17:20(日本時間)

アルテアのソリューションにご興味お持ちの方は、是非セミナーにて詳しい話をお聞き頂きたい。同講演はオンラインでもライブ配信される予定。

2022.11.02

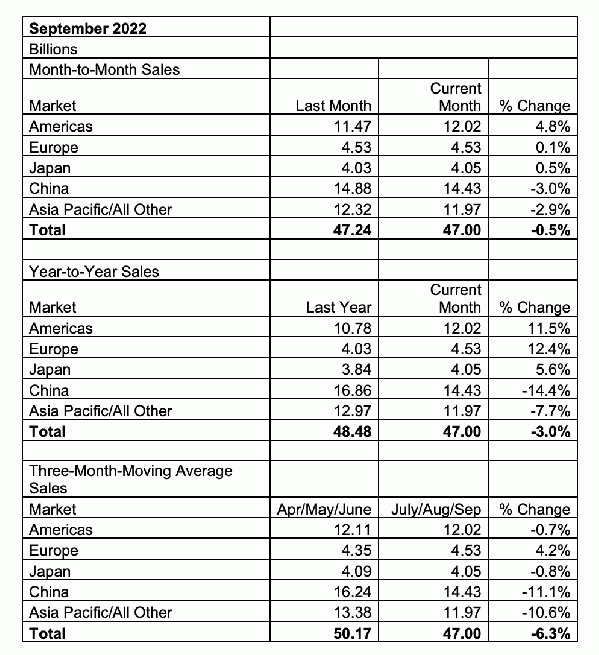

2022年10月29日、米SIA(Semiconductor Industry Association)は、2022年9月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2022年9月の世界半導体売上は、前年同月比約3%減、前月比約0.5%減の470億ドルだった。世界半導体売上の単月売上が前年同時期の実績を下回るのは32ヶ月ぶり。2年半以上に渡って続いていた半導体業界の成長はついにマイナス成長に転じた。世界の半導体市場は今年5月をピークに売上下降基調に入っており、年末にかけて更に売上の減少が加速しそうな様相となりつつある。

2022年9月の世界半導体売上を地域別にみると、北米市場と欧州市場は対前年比2桁成長を維持しているが、最大市場の中国市場そしてアジア市場がともにマイナス成長。中国市場は8月よりも売上の縮小が加速している。

日本市場の売上を円ベースで換算すると前月比約5.9%増、前年比約37.1%増の約5,803億円。日本市場の売上が前年同月比プラス成長となるのはこれで22か月連続。9月に入ってからの急激な円安の影響で大幅な売上増となっている。

2022.10.26

ここ最近、TSMCの独自イベント「TSMC OIP Forum」の開催を前に、TSMCの第二世代の3nmプロセステクノロジ「N3E」に関する話題がにわかに活発化しつつある。

TSMCは今年生産を開始した最初の3nmプロセスN3に続いて、その改良版のN3E、パフォーマンスを強化したN3P、トランジスタ密度を向上させたN3S、ハイパフォーマンス・アプリケーション向けのN3Xと複数のN3プロセスのラインナップを計画している。

そんな中、昨日10月25日にカナダのIPベンダAlphawave IPが「N3E」でのテープアウト事例を発表した。

Alphawave IPがN3Eプロセス製の最初のテストチップの一つとしてテープアウトしたのは、「ZeusCORE 100」という製品名の最先端のマルチスタンダーSerDesで、45dBを超えるエクストラロング・チャンネルと、800G Ethernet、OIF 112G-CEI、PCIe GEN6、CXL3.0など最先端の規格をサポートしている。

Alphawave IPは10月26日にカリフォルニア州サンタクララで開催されるTSMC OIP Forumで同製品を展示する予定だという。

TSMCのN3Eプロセスは、既存のN5プロセスと比較して速度18%向上、パワー34%削減、ロジック密度1.7倍と公称されており、早ければ来年半ばから量産が開始される予定となっている。

■EDAベンダの動き

TSMCのN3Eプロセスの量産立ち上げに向けてEDAベンダーも動いており、このほどCadenceとSynopsysが相次いでN3Eプロセス向けのツール認証を発表している。

両社ともにデジタルおよびカスタム設計ツール群がN3Eプロセス向けの設計で利用可能となったことを発表しているが、CadenceはN3Eと同時にN4Pプロセスにも対応したことをアピール。一方のSynopsysは豊富なIP群もN3Eをサポートしたことに加え、「IC Validator」を使用したクラウド上でのフィジカル検証がN3E向けデザインにも対応したことを強調している。

TSMCの製造プロセス別売上比率は既に7nm/5nmの売上が過半を占めており、3nmプロセスの立ち上がりによりその売上の70%近くが16nm以降の先端プロセスになる見通しだ。

2022.10.25

2022年10月24日、Cadenceは、2022会計年度第3四半期(2022年7-9月)の売上を報告した。

Cadenceの2022年Q3売上は、前年比約20%増、前期Q2比約5.2%増の9億300万ドル、営業利益は前年比約5.6%増の1億8630万ドルだった。(※GAAP基準による会計結果)このQ3実績は同社の予測を上回るもので同社の四半期売上記録として過去最高となる。

Cadenceは2022年Q4の売上を8億7000万-9000万ドルと予測。2022年の年間売上を35億3200-5300万ドル程度と予測を上方修正している。

CacdenceはこのQ3(2022年7-9月)において以下のような発表を行っている。

2022.10.19

2022年10月5日、SynopsysはECO/サインオフ向けの新製品「PrimeClosure」を発表した。

発表によると新製品「PrimeClosure」は、Synopsysの既存のECOソリューション「PrimeECO」と「Tweaker ECO」を統合した新製品で、ECOに関わる工数を大幅に削減しデザインの早期収束を実現してくれる。

具体的には「PrimeClosure」を利用することで、PPA、クロックネットワーク、電圧降下、ばらつき、経年劣化といった様々な設計指標を改善することが可能。配置配線ツール「Fusion Compiler」やSTA「PrimeTime」と連携し大規模デザインのサインオフを実現する。

Synopsysによると「PrimeClosure」は、数百のシナリオを持つ10億インスタンス以上の大規模デザインにも拡張適用可能。無駄な枝葉部分の探索を切り捨て最適化が必要な設計データを絞り込む独自機能を備えており、れにより高速かつ省リソースな設計収束を達成できる。(ECOスピードを40%以上高速化し、メモリー使用量を最大60%削減)

また「PrimeClosure」はAnsys社のパワー・インテグリティ解析ツール「RedHawk-SC」とも統合動作可能で、設計後期段階で発生する電圧降下を高精度に解析しその最大50%を修正することができるという。業界初の同機能により、タイミングに悪影響を与えることなく電力効率を最大限高めることができるという話だ。

Synopsysは新製品「PrimeClosure」を業界最速のECOソリューションと主張しており、早期適用顧客においてタイミング性能を最大45%向上、消費電力を最大10%削減、ECO作業のやり直しを最大50%削減し、設計生産性を最大10倍向上させているとアピール(いずれの数値も従来比)。

発表にコメントを寄せているソシオネクストの担当者によると、「PrimeClosure」を利用することでECO期間を1/5以上短縮、しかもコンピューティング・リソースは1/5に、メモリー使用量は1/3に削減できたとしている。

なお、ほぼ時同じくしてCadenceも同様のECO/サインオフを高速化するソリューションを発表しているが、ECOの高速化と合わせて「PrimeTime」を核としたタイミング性能の向上やAnsysとの連携による電力効率の向上を強調するSynopysに対して、Cadenceは人手処理の自動化によるTAT短縮効果を強調している。

関連ニュース:

2022.10.18

2022年10月17日、米ESD Allianceは、2022年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると2022年Q2(4-96)の世界のEDA売上総額は、前年比約17.5%増、前Q1比約6.9%増の37億4870万ドルで四半期売上記録を更新した。記録の更新は9四半期連続。四半期売上が前年実績を上回るのは14四半期連続となる。

2022年Q2のEDA売上をカテゴリ別に見ると全てのカテゴリで前年比2ケタ増を達成。PCB, IP, Serviceの3部門は前年比20%超えの成長となった。好調なIP分野は四半期売上記録の更新を続けている。

2022年Q2のEDA売上を地域別に見ると、日本市場を含む全ての地域で前年比プラス成長を記録。最大市場の北米の成長率は前年比20%増を超えた。

2022年Q2時点でのEDA業界の従業員数は前年比8.9%増の54,408人でQ1よりも約6%増加した。

2022年Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 11億3730万ドル 12.1%Up

■IC Physical Design & Verification分野 6億5700万ドル 13%Up

■IP分野 14億7670万ドル 22.6%Up

■サービス分野 1億3070万ドル 23.2%Up

■PCB/MCM分野 3億4710万ドル 22%Up

2022年Q2の地域別の売上と昨年同時期との比較は以下の通り。

■北米 16億4340万ドル 20.2%Up

■欧州・中東・アフリカ 4億7200万ドル 13.7%Up

■日本 2億5230万ドル 6.1%Up

■アジアその他地域 13億8100万ドル 17.9%Up

2022.10.17

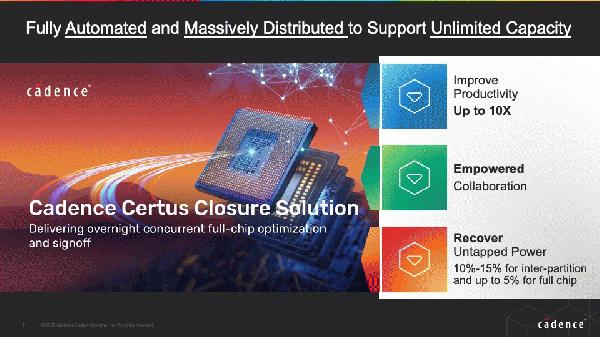

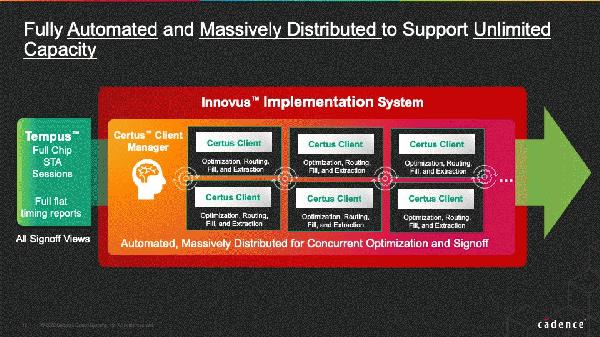

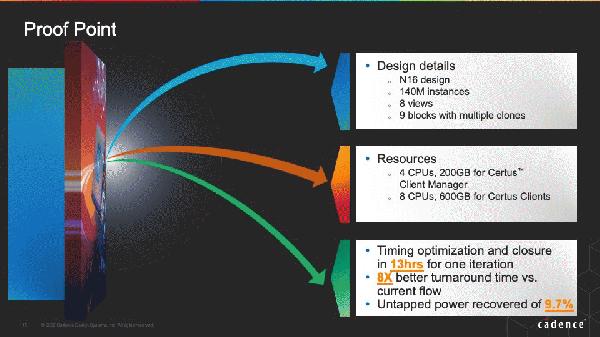

2022年10月12日、Cadenceはチップ設計の最適化とサインオフに向けた新製品「Certus Closure Solution」を発表した。

今回発表された新製品「Certus Closure Solution」は、その製品名の通りデザイン・クロージャーのためのツールで、バックエンド設計工程の中でも最も時間を要すとされているECO/最適化のフェーズを自動化してくれるもの。

タイミングや消費電力の要件を満たすために行われるECO/最適化の作業は、16nmプロセス以降その複雑度が膨れ上がり、場合によっては1回のイタレーション作業に5日から7日もの時間を費やす必要があり、デザインによってはその最適化とサインオフに数ヶ月かかるケースも珍しくない。プロセスの微細化に伴い増加したプロセス・コーナーと複雑なパワードメインによって増加したシナリオ、これらの膨大な組み合わせに対する最適化、STA、配線、メタルフィル挿入、寄生抽出という一連の作業は全て設計者の手作業で行われており、これまでその膨大な手作業を自動化できるソリューションは無かった。

「Certus Closure Solution」は、Cadenceの配置配線ツール「Innovus」とサインオフ・タイミング解析ツール「Tempus」そしてAI最適化機能「Cerebrus」を用いたデザインの最適化およびサインオフ・プロセスを言わばマネジメントするような環境で、ブロックレベルで行われる個々の最適化、それを統合したチップレベルの最適化、さらにはそのサインオフ検証を同時並列的に分散し、全て自動処理として実行させることが可能。マシンリソースさえ確保できればそのデザイン規模に制限はなく、あらゆる大規模デザインのイタレーションをたった一晩数時間で収束してくれるという。

言うまでもなく「Certus Closure Solution」による人手作業の自動化はTAT短縮に大きなインパクトを与えるが、Cadenceはデザインの同時最適化によるメリットとして消費電力の削減効果もうたっており、ブロックレベルにおいてパーティション間のリーク電流を最大15%、チップレベルでは最大5%程度の消費電力を削減できるとしている。また、「Certus Closure Solution」による分散自動処理は必ずしもハイスペックなマシン環境を必要とせず、比較的安いマシンコストで利用することが可能。設計者の人的リソースにしてもマシンリソースにしても大規模集約的な形ではなく並列分散的な形で設計の効率化/低コスト化を実現できる点も「Certus Closure Solution」を活用する大きなメリットの一つと言える。

発表にはMaxLinearとルネサスエレクトロニクスが「Certus Closure Solution」のユーザーとしコメントを寄せているが、両社ともに大幅な生産性の向上について指摘。MaxLinearは最大5%の潜在的な電力削減を実現したとコメントしている。なおCadenceが発表しているエビデンスによると、従来手法よりもTATを10倍向上、消費電力を10%近く削減といった事例もあるようだ。

※画像は全てCadence提供のデータ

Cadenceは特に先端プロセスデザイン向けで好調な配置配線ツール「Innovus」を核に、昨年7月にAI最適化ソリューション「Cerebrus™ Intelligent Chip Explorer」を発表。そして今回の「Certus Closure Solution」と立て続けにバックエンド設計向けの大型ソリューションを投入している。これらはいずれも業界初の独自ソリューションとなるが、長いチップ開発の歴史を振り返ると7nm/5nm/3nmという時代に生まれたこれらツールはチップ開発の歴史の一つの転換点となる可能性が高く、これからのチップ設計をどのように変えていくのか今後も注目していきたい。

※日本ケイデンス・デザイン・システムズ社

2022.10.14

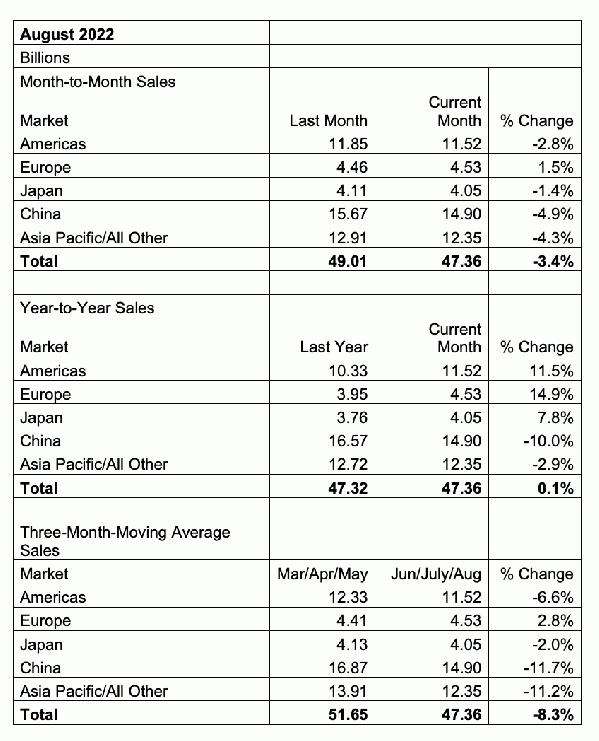

2022年10月3日、米SIA(Semiconductor Industry Association)は、2022年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2022年8月の世界半導体売上は、前年同月比0.1%増、前月比約3.4%減の473億6000万ドルだった。世界半導体売上の単月売上が前年同時期の実績を上回るのはこれで31ヶ月連続だが、9月は前年実績を割り込む見通しだ。

世界半導体市場は2022年7月に8ヶ月ぶりに売上500億ドルを割り込んだが、8月は更に売上が落ち込み470億ドル台となった。単月売上が470億ドル台になるのは2021年8月以来1年振りとなる。

2年以上好調を維持し続けてきた世界の半導体市場は今年5月をピークに売上下降基調に入っており、年末にかけて更に売上の減少が加速しそうな様相となりつつある。

2022年8月の世界半導体売上を地域別にみると、最も勢いのあった北米市場の成長率が前年比11.5%増と7月よりも更に低下。最大市場の中国市場も前年比10%減と売上の縮小が続いている。

日本市場の売上を円ベースで換算すると前月比約2.5%減、前年比約21.3%増の約5,477億円。日本市場の売上が前年同月比プラス成長となるのはこれで21か月連続。とくにここ数ヶ月は円安の影響で大幅な売上増が続いている。

2022.10.07

2022年10月7日、本日よりセミナー・イベント「Design Solution Forum 2022」の参加登録がスタートしました。

今年のDSF2022は、2年ぶりに会場にて来場者を迎えての開催。5つの会場で行われる講演は全てオンラインでライブ配信される予定で、会場での開催に伴いスポンサー企業によるブース展示(計23社)やセミナー後の交流会も行われる。

DSF2022の基調講演は、フォロワー数17万人超の人気製造業系YouTuber「ものづくり太郎」氏が登壇。日本の製造業に対する独自の提言を聞かせてくれる予定。

DSFでは毎年様々な特別企画が行われているが、今年はアダプティブコンピューティング研究推進体(ACRi) とのコラボレーション企画を含め、下記3つのDSF特別企画が予定されている。

・AIカー製作体験:ラズパイで走るAIミニ四駆「TatamiRacer」

・DSF選書:DSF参加者に今読んで欲しい一冊

・<参加型> DSF×ACRiコラボ企画:本音で語ろう!日本のものづくりとエンジニアはどうなる!?

なお今年のDSFでは2年振りの会場開催に伴い、様々な名刺交換企画を開催予定。

セミナー会場内で積極的に名刺交換を行うと、Amazonギフト券などのプレゼントがもらえるという。(

詳細はこちら)

恒例の交流会では、最優秀講演者が表彰されるほか、スポンサー各社およびDSF提供の豪華賞品が当たるプレゼント抽選会が行われる予定。

オンライン開催は、様々なコミュニケーション機能が用意されたEventHubというイベント・プラットフォームを利用して行われるので、オンラインでの参加者もイベント講演者、出展者、来場者との交流が楽しめる。

2022.09.20

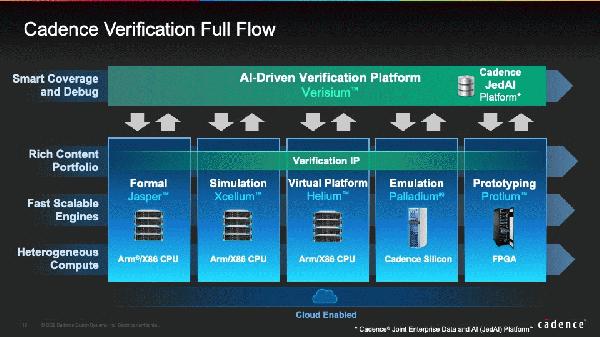

2022年9月14日、Cadenceは検証/デバッグ向けの新製品「Verisium」プラットフォームを発表した。

今回発表された「Verisium」プラットフォームは、AI技術の取り込みを積極的に進めているCacenceとして新たな一歩を踏み出す新世代のAIベース・ツールで、同日発表されたAIベース・チップ設計向けのデータベース「JedAI(ジェドエーアイ)」プラットフォームを活用する最初の論理検証関連新製品となる。

※JedAI Platform:Joint Enterprise Data and AI Platform

データベース「JedAI」は、SoC設計・検証フロー全体で利用する複数ツール・複数エンジンのデータを一元的に統合するもので、同データベースとAI技術を用いることにより最適なPPA、最高のカバレッジ、最短の製品投入を実現できることが可能。これまで行われていたツール単体での逐次実行を主体とした設計から、複数ツール・複数エンジンを複数実行しながらあらゆる設計データをもとに最適化を行う、「よりインテリジェントな設計」へと設計手法そのものを進化させることができるとCacdenceは説明する。

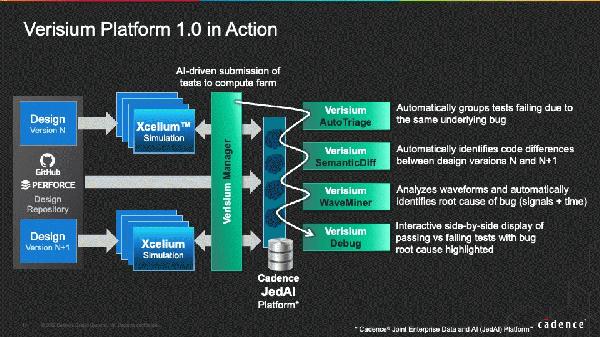

Cadenceによると新製品「Verisium」プラットフォームの役割は大きく2つある。一つは検証全体のマネジメントでこれまで「vManager」が担っていた検証作業の管理およびコックピットの機能を「Verisium Manager」が引き継ぐ。Cadenceの提供する全ての検証ツールは「Verisium Manager」を通じて実行/マネジメント可能だ。

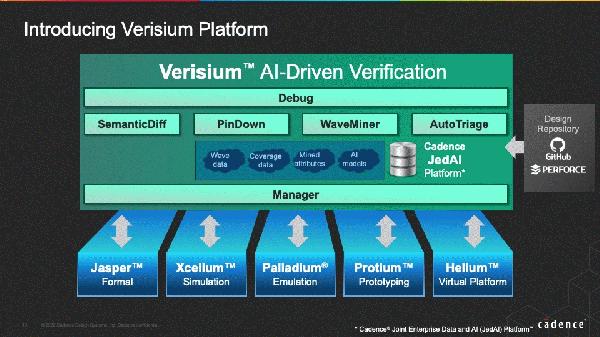

もう一つの「Verisium」プラットフォームの役割はAIベースのデバッグで、これが既存の「vManager」には無かったデータベース「JedAI」を活用した目玉機能となる。

「Verisium」プラットフォームの中には下記4つのデバッグ用アプリが用意されており、それらアプリはユーザーのデザインと検証結果、そして「JedAI」に蓄積されたデータからマシン・ラーニングを用いてフェイルを推定することが可能。ユーザーは自動または半自動でバグの根本原因を容易に特定できるようになる。

<Verisiumのデバッグ用アプリ>

Verisium AutoTriage:

フェイルしたテストを俯瞰して共通根本原因を推定しテストをグループ化する

Verisium SemanticDiff:

IPやSoCの複数コード間(バージョン間)の機能的な差分を比較し、バグを入れ込むリスクのある変更点の分類とランク付けを行う

Verisium WaveMiner:

複数テスト結果の波形からフェイルとなる根本原因に関係する可能性が高い信号とそのタイミングパターンの推定を行う

Verisium PinDown:

ソースコードの変更、テストレポート、ログファイルの情報から、バグを入れ込んだ可能性が高いソースコード更新を推定する

※Verisium PinDownは、Github, Redmine, Perforceなど業界標準のレビジョン・コントロール・システムと統合可能

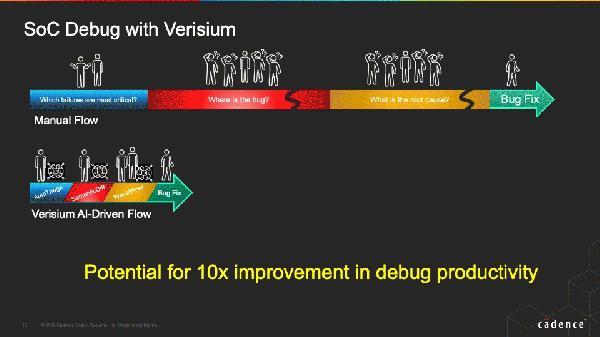

なおユーザーが検証ツールに流した結果は順次データベース「JedAI」に蓄積され活用されていくため、「Verisium」はユーザーがデザインを走らせば走らすほど賢くバグの原因を特定できるようになるとのこと。Cadenceは「Verisium」プラットフォームを使うことでデバッグ作業の工数を10分の1程度に低減できるとしている。

※画像は全てCadence提供のデータ

今回発表された「Verisium」プラットフォームはデバッグをターゲットとした「JedAI」活用検証ツールの第一弾となるが、Cadenceは今後も順次AIベースの検証ツールをリリースしていく計画だと言う。

2022.09.13

--PR--

前回、下記の記事においてシーメンスの提案する半導体製品開発におけるPLMの活用について紹介した。

同記事では半導体製品の開発に製品ライフサイクル管理 (PLM) を用いることの大きな利点として「新製品導入(NPI)サイクルタイム」を大幅に短縮できることを挙げ、その背景と理由について説明したが、シーメンスによるとPLMには大きな導入効果がほかにもある。それは「イノベーションの促進」と「製品品質の向上」だ。

PLMを取り入れることにより半導体製品開発プロセス全般に渡るデータの一元化が可能となり、必要な時に必要なデータを用いた意思決定が可能になる。その結果、製品開発が効率化され新製品導入(NPI)サイクルタイムを短縮できるようになるが、「PLMによる開発の効率化」はイノベーションの促進、そして製品品質の向上といった側面にも大きく寄与することになる。

シーメンスの引用する調査結果によると、エンジニアが製品のイノベーション、開発、エンジニアリングに直接費やしている時間は全作業時間の50パーセント未満でしかないということで、多くの半導体企業の現場において技術リソースの無駄遣いが行われている。PLMを導入し開発を効率化することで、無駄にしている技術リソースを製品のイノベーションなどもっと他のことに費やすことができれば、市場でより優位に立てるはずだというのがシーメンスの主張だ。それは至極もっともな話であり、逆に技術リソースを最大限有効に活用できなければ、今日の熾烈な半導体市場での競争に勝ち抜くことはできないと言えるだろう。

すなわちPLMを用いたデータの一元化とデジタル化、それによる開発の効率化は、製品開発におけるイノベーションの促進や市場の攻略を考える上でも重要かつ、直ちに取り組むべき課題であると言っても過言ではない。

では次にシーメンスが唱えるPLMのもう一つの導入効果「製品品質の向上」について見てみよう。

シーメンスはPLMをデータの可視化そしてトレーサビリティを高めるために必要な手段であると説明するが、その背景には「半導体企業の責任」という重要なテーマが隠されている。

半導体が一つのシステムとしてまたはシステムを構成する中核的な部品として提供されるようになった今日、半導体メーカーはその品質やトレーサビリティの向上を半導体ユーザー(顧客)から強く求められるようになってきている。自動車業界における機能安全規格ISO26262の普及などはその代表例の一つと言えるもので、万が一半導体製品の欠陥に起因するシステム故障が発生すると、半導体を開発した企業がその責任を問われるという事も起こりうる。

そいうった状況からデータの可視化/トレーサビリティの向上は、ユーザーに対する半導体企業の責任として取り組む必要があり、要件適合の確認および検証、顧客要件からテープアウトまで全開発サイクルを通じた製品関連情報の管理は避けて通れない道となっている。

データの可視化やトレーサビリティの向上を実現するツールは古くから存在しているが、それらは基本的にEDAツールを用いたチップ設計用、組み込みソフト開発用など特定のドメインに特化したもので、製品ライフサイクル全体のあらゆるデータや製造プロセス情報を連携させて可視化・トレース可能なソリューションはこれまで無かった。

シーメンスの提供するPLMツール「Teamcenter」は、製品ライフサイクル全体のあらゆるデータを包含したエンド・ツー・エンドのトレーサビリティを実現するツールで、EDA/設計管理ツールと連携し相互にデータを可視化・トレースすることが可能。全ての製品データ要素を要件からチップ提供までの重要なプロセスとタスクに取り込み関連付けることが可能なため欠陥を容易に追跡し、その根本原因をリアルタイムで解析することができる。これにより半導体設計のリスピンを回避するだけでなく、半導体製品の品質を高いレベルで最大化することが可能となる訳だ。

「新製品導入(NPI)サイクルタイムの短縮」と合わせ「イノベーションの促進」、「製品品質の向上」といった導入効果をもたらすシーメンスの提供するDX時代のPLMソリューション。ご興味ある方は、是非無料の電子ブック「半導体ライフサイクルのトレーサビリティと製品品質を向上させる方法」をご参照ください。

2022.09.13

2022年9月8日、ファブレス半導体ベンダの米QuickLogicは、米国防総省が後援する耐放射線FPGA技術の開発プロジェクトで690万ドルの基本契約を獲得したことを発表した。

このプロジェクトは、国防総省の防衛および宇宙システム要件を満たすための戦略的な耐放射線FPGA技術を開発するというもので、基本契約が成功すれば米国政府の裁量により、複数年に渡り計7200万ドルのオプションが認められる予定。QuickLogicは長年にわたり防衛・宇宙航空分野にアンチヒューズFPGAを提供する実績を持つ。

2022.09.13

2022年9月1日、高速インターコネクトIPを手がける英Alphawave IPは、SiFiveの設計子会社OpenFiveを買収したことを発表した。

発表によるとAlphawaveによるOpenFiveの買収は既に完了済。その取引内容などは明らかにされていない。

Alphawave IPは元々カナダで創業したIPベンダで、データセンターを主なターゲットにSerDes/PHY, /Fコントローラなど高速有線接続用のIPを提供している。2021年の売上は前年比173%増の2億4470万ドルで従業員数は154名、ワールドワイドで20社のTier-1 顧客に製品を提供している。

OpenFiveはドメイン・スペシフィックなSoC開発に特化した設計サービスを行うSiFiveのグループ会社で、元々米OpenSilicon社で設計サービス事業を手がけていたメンバーが中心となっていた。

2022.09.07

2022年9月6日、米SIA(Semiconductor Industry Association)は、2022年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2022年7月の世界半導体売上は、前年同月比7.3%増、前月比約2.3%減の490億1000万ドルだった。世界半導体売上の単月売上が前年同時期の実績を上回るのはこれで30ヶ月連続。2021年12月から7ヶ月連続で売上500億ドル台を維持していたが、この7月は500億ドルを割り込んだ。2年以上好調を維持し続けてきた世界の半導体市場は今年5月をピークに売上下降基調に入っている。

2022年7月の世界半導体売上を地域別にみると、最も勢いのあった北米市場の成長率が前年比20.9%増と6 月よりも低下。中国市場はついに前年比1.8%減のマイナス成長となった。

日本市場の売上を円ベースで換算すると前月比約2.4%増、前年比約40.5%増の約5,619億円。日本市場の売上が前年同月比プラス成長となるのはこれで20か月連続。とくにここ数ヶ月は円安の影響で大幅な売上増が続いている。

-thumb-600x257-6348.jpg)