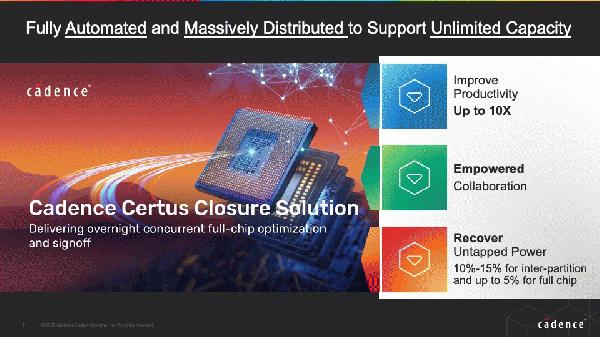

Cadenceが業界初、大規模先端チップの自動最適化を実現する新製品「Cadence Certus Closure Solution」を発表

2022年10月12日、Cadenceはチップ設計の最適化とサインオフに向けた新製品「Certus Closure Solution」を発表した。

今回発表された新製品「Certus Closure Solution」は、その製品名の通りデザイン・クロージャーのためのツールで、バックエンド設計工程の中でも最も時間を要すとされているECO/最適化のフェーズを自動化してくれるもの。

タイミングや消費電力の要件を満たすために行われるECO/最適化の作業は、16nmプロセス以降その複雑度が膨れ上がり、場合によっては1回のイタレーション作業に5日から7日もの時間を費やす必要があり、デザインによってはその最適化とサインオフに数ヶ月かかるケースも珍しくない。プロセスの微細化に伴い増加したプロセス・コーナーと複雑なパワードメインによって増加したシナリオ、これらの膨大な組み合わせに対する最適化、STA、配線、メタルフィル挿入、寄生抽出という一連の作業は全て設計者の手作業で行われており、これまでその膨大な手作業を自動化できるソリューションは無かった。

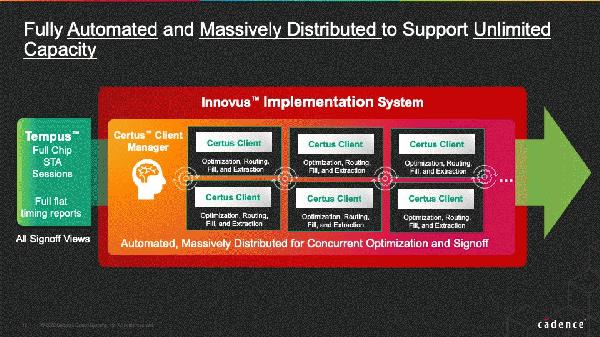

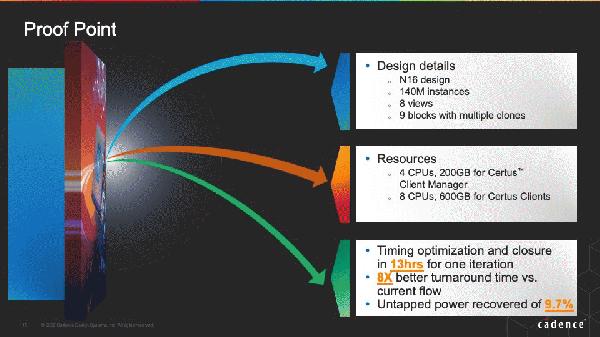

「Certus Closure Solution」は、Cadenceの配置配線ツール「Innovus」とサインオフ・タイミング解析ツール「Tempus」そしてAI最適化機能「Cerebrus」を用いたデザインの最適化およびサインオフ・プロセスを言わばマネジメントするような環境で、ブロックレベルで行われる個々の最適化、それを統合したチップレベルの最適化、さらにはそのサインオフ検証を同時並列的に分散し、全て自動処理として実行させることが可能。マシンリソースさえ確保できればそのデザイン規模に制限はなく、あらゆる大規模デザインのイタレーションをたった一晩数時間で収束してくれるという。

言うまでもなく「Certus Closure Solution」による人手作業の自動化はTAT短縮に大きなインパクトを与えるが、Cadenceはデザインの同時最適化によるメリットとして消費電力の削減効果もうたっており、ブロックレベルにおいてパーティション間のリーク電流を最大15%、チップレベルでは最大5%程度の消費電力を削減できるとしている。また、「Certus Closure Solution」による分散自動処理は必ずしもハイスペックなマシン環境を必要とせず、比較的安いマシンコストで利用することが可能。設計者の人的リソースにしてもマシンリソースにしても大規模集約的な形ではなく並列分散的な形で設計の効率化/低コスト化を実現できる点も「Certus Closure Solution」を活用する大きなメリットの一つと言える。

発表にはMaxLinearとルネサスエレクトロニクスが「Certus Closure Solution」のユーザーとしコメントを寄せているが、両社ともに大幅な生産性の向上について指摘。MaxLinearは最大5%の潜在的な電力削減を実現したとコメントしている。なおCadenceが発表しているエビデンスによると、従来手法よりもTATを10倍向上、消費電力を10%近く削減といった事例もあるようだ。

※画像は全てCadence提供のデータ

Cadenceは特に先端プロセスデザイン向けで好調な配置配線ツール「Innovus」を核に、昨年7月にAI最適化ソリューション「Cerebrus™ Intelligent Chip Explorer」を発表。そして今回の「Certus Closure Solution」と立て続けにバックエンド設計向けの大型ソリューションを投入している。これらはいずれも業界初の独自ソリューションとなるが、長いチップ開発の歴史を振り返ると7nm/5nm/3nmという時代に生まれたこれらツールはチップ開発の歴史の一つの転換点となる可能性が高く、これからのチップ設計をどのように変えていくのか今後も注目していきたい。

※日本ケイデンス・デザイン・システムズ社

= EDA EXPRESS 菰田 浩 =

(2022.10.17

)