NEWS

2019.09.17

2019年9月16日、Armは、新たなライセンス・プログラム「Arm Flexible Access for Research」を発表した。

「Arm Flexible Access for Research」は、Armが今年7月に発表した事前のライセンス契約無しにIPへのアクセスを可能とするプログラム「Arm Flexible Access」の拡張版で、その門戸を学術研究者に向けて開くもの。「Arm Flexible Access for Research」では、シンプルなエンドユーザーライセンス契約(EULA)を使用して、学術研究コミュニティに幅広い最先端Arm IPへのアクセスを無料で提供する。無料で提供されるIPとしては、Arm Cortex-A、-R、-Mファミリ内のプロセッサの大部分が含まれるほか、あらゆるRTLサブシステムおよびツールへも無料でアクセス可能となる。

上記Arm Flexible Access for Research申し込みページに記載されている同プログラムのポイントは以下の通り。

・最大1,000個のチップを製造およびテスト可能

・デザインの評価およびソフトウェア・アプリケーションの開発において、FPGA開発ボードでIPを使用可能

・IPの変更は不可(ライセンスに記載されている場合を除く)

・資料をダウンロードして使用することは、使用者が学術機関を代表して学術的な目的の下でArmとの契約条件に同意することを表明することになる

・EULAの契約期間は3年

・ICの製造、パッケージング、およびテストは、Armが承認したサードパーティのみを使用可能

なお、Arm Flexible Access for Researchは現在申し込み受付中で、2020年初頭に利用可能となる予定。

2019.09.13

2019年9月9日、Synopsysは、クラウド・ベースのシミュレーション環境の構築でGoogle Cloudと協業したことを発表した。

発表によると今回の協業で実現されるのはGoogleのクラウド環境を用いたシミュレーションの実現で、ユーザーは必要な時に必要なマシンリソースを使ってVCSによるシミュレーションを実行できるようになる。

シミュレーションの負荷をクラウド上で分散処理するには、ハードウェア・インスタンスの選定、ファイル・システムのコンフィギュレーション、ジョブ実行の最適化といった課題があるが、SynopsysはGoogle CloudおよびNetApp社と連携してこれらに対応可能なソリューションを提供する。

※NetApp社はGoogle Cloud向けにアプリとワークロードの管理を行うソリューションを提供している。

Synopsysは、昨年10月にAmazonの「AWS」とMicrosoftの「Azure」をサポートする独自のクラウド・サービス「Synopsys Cloud Solution」を発表しており、同サービスの対応ツールにはシミュレータ「VCS」も含まれている。(※

関連ニュース)

2019.09.11

2019年9月5日、Imagination Technologiesは、「IMG Edge」と呼ぶ設計・検証向けのサービス・プラットフォームを発表した。

Imagination Technologiesによると「IMG Edge」は、SoCの開発コストを費用的にも時間的にも削減することを目的に用意された設計・検証サービス向けのプラットフォームで、Imagination Technologiesのデータセンターやツール、メソドロジ、仮想プラットフォーム、ハードウェア・アクセラレーターへのアクセスと合わせてSoC開発に関するImagination Technologiesの専門知識を提供。Imagination Technologiesは「IMG Edge」を自ら「game-changing」ソリューションと語っており、同サービス・プラットフォームを活用することでSoCを開発する顧客は、場合により開発コストを1,000万ドル以上、プロジェクト期間を月単位で削減できるとしている。

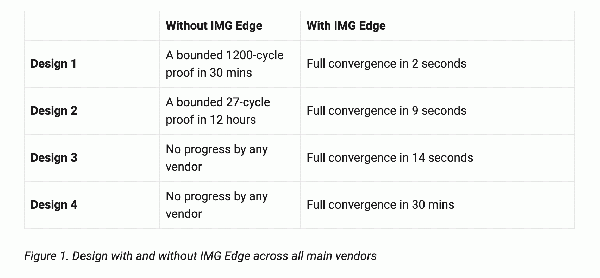

「IMG Edge」は様々な分野のSoC開発に対応できるジェネリックなソリューションで、その中身は自動車、コンスーマー、インダストリアル、モバイル、セキュリティなど、主要市場の個々の要件を満たすように完全にパーソナライズされているとのこと。Imagination Technologiesの用意するプラットフォーム、ノウハウ(コンサルティング)、独自に培われたメソドロジが「IMG Edge」を構成する柱となるが、Imagination Technologiesは主要なメソドロジの一例として、データパスヘビーなデザインで複雑な制御ロジックと演算を迅速に検証する方法を紹介。同メソドロジを用いることで完全なデータ一貫性を証明しながら複雑な64ビットALUを処理することが可能で、他の手法では収束できない検証もわずかな時間で収束できるという。(下図参照)

Imagination Technologiesは今後「IMG Edge」を利用した検証サービスを新たなビジネスとして展開していく予定。

2019.09.05

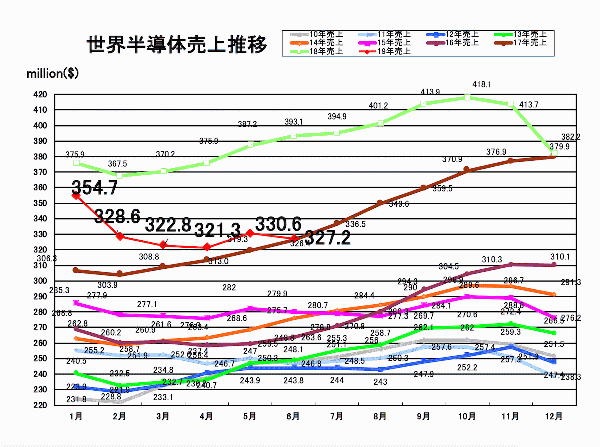

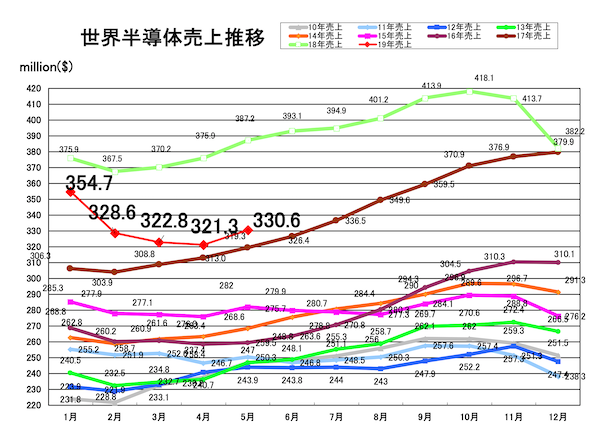

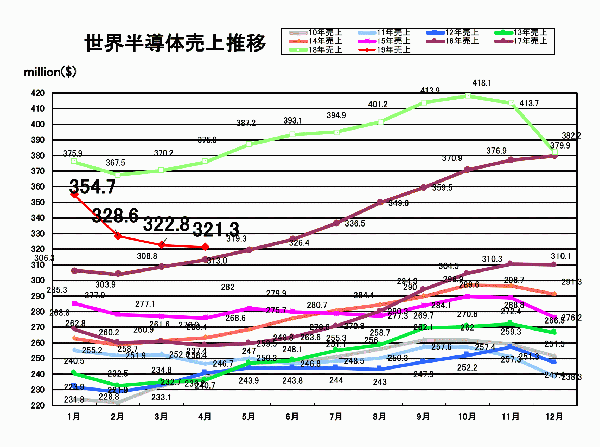

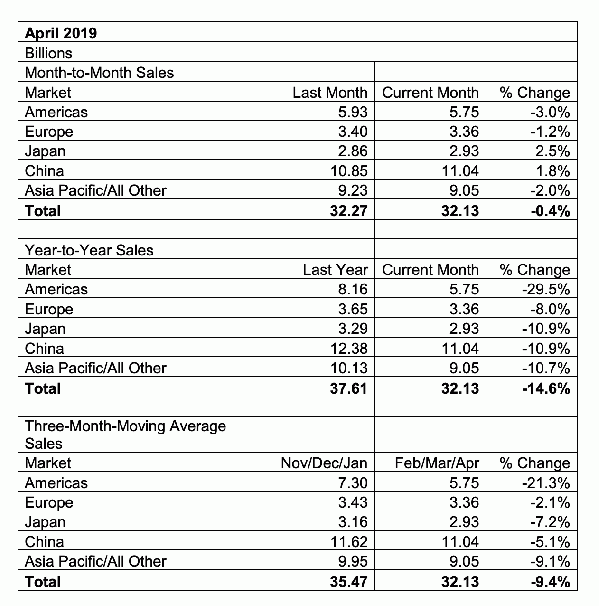

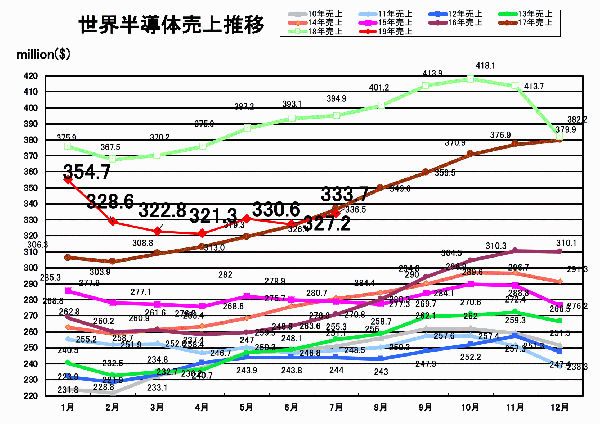

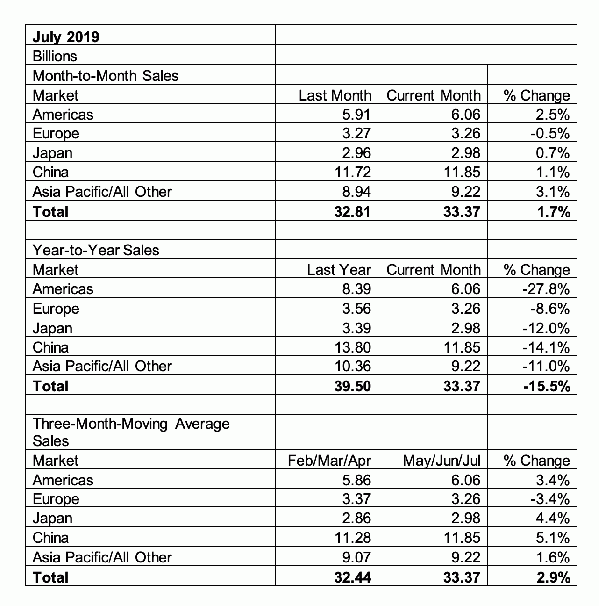

2019年9月3日、米SIA(Semiconductor Industry Association)は、2019年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年7月の世界半導体売上は、前年同月比15.5%減、前月比1.7%増の327.2億ドルという結果だった。この売上高は今年1月以降で最高額となるものだが、売上実績の前年割れは2018年11月以降9ヶ月連続で、7月の売上は2017年の水準を下回った。

2019年7月の売上を地域別で見ると全ての地域で前年実績を下回ったが、6月実績と比較すると欧州市場以外は全ての地域で僅かながらプラスに転じた。3ヶ月ごとの売上推移を見ても、2-4月売上に対して5-7月売上は2.9%増と伸びている。

日本市場の7月の売上は前月比0.7%増、前年比12%減の29.8億ドルで、売上を円ベースで換算すると前月比0.8%増、前年比約14.6%減の約3,225億円となる。

2019.09.04

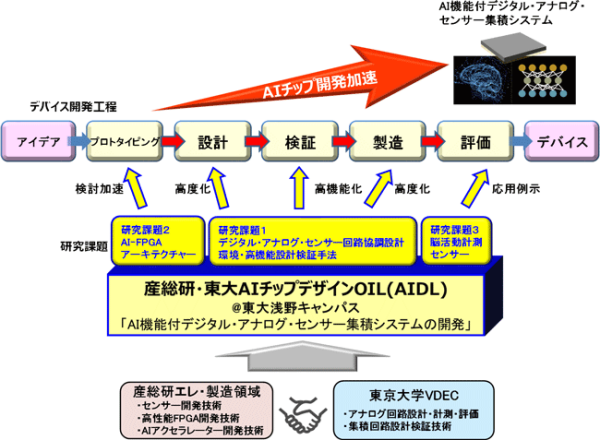

2019年9月2日、産総研は東京大学VDEC(大規模集積システム設計教育研究センター)と共同で「産総研・東大 AIチップデザインオープンイノベーションラボラトリ(AIDL)」を東京大学浅野キャンパスに設立たことを発表した。

産総研のオープンイノベーションラボラトリ(OIL)は、産総研の第4期中長期計画(平成27年度?令和元年度)で掲げている「橋渡し」を推進していくための新たな研究組織の形態。同研究組織では主に下記3つの研究課題に取り組む。

1.AI機能付デジタル・アナログ・センサー(DAS)集積システムを実現するためのアナログ・デジタル要素技術やシステムアーキテクチャー、設計検証手法の研究(エッジコンピューティング向け)

2.AI処理に適したFPGAアーキテクチャーの探索、ならびにAI処理に特化したFPGA開発アセットの構築、およびAIアクセラレーターを用いたAI実装技術の研究(画像解析応用技術の開拓など)

3.脳活動計測用のAI機能付きジタル・アナログ・センサー(DAS)集積システムの開発

産総研とVDECは既に昨年12月に「AIチップ設計拠点」を、東京大学浅野キャンパスに構築しており、EDAツールやエミュレーターなどの開発環境を整備している。

2019.08.30

2019年8月25日、ハードウェア設計言語・技術の標準化団体米Accellera Systems Inisiativeは、新たなSystemCのチュートリアルを公開した。

今回公開されたチュートリアルのタイトルは、"SystemC: Focusing on High-Level Synthesis and Functional Coverage for SystemC"

高位合成ならびに機能カバレッジにフォーカスしたチュートリアルで、SystemCワーキング・グループの活動アップデートも含め計5つのパートに分かれている。

チュートリアルは音声付きのビデオコンテンツとPDFが用意されており、内容構成とプレゼンターは以下の通り。

・High-Level Synthesis with SystemC: An Introduction

・High-Level Synthesis: Model Structure and Data Types

・High-Level Synthesis: Lessons Learned - Intel's Experience --

・Functional Coverage for SystemC (FC4SC) --

・Accellera SystemC Working Group Update

Presenters: Fred Doucet, Facebook; Mike Meredith, Cadence; Bob Condon, Intel; Dragos Dospinescu, AMIQ; Martin Barnasconi, NXP.

2019.08.30

2019年8月29日、市場調査会社TrendForceは、2019年Q2のファブレス半導体ベンダの売上ランキングを発表した。

発表によると2019年Q2売上Top10のうち上位5社の売上が軒並み前年実績割れ。前年実績に対して最も売上が減ったのは売上3位にランキングされているNVIDIAで前年比20.1%減。NVIDIAは3年ぶりに3四半期連続で前年実績を割り込んだ。TrendForceは米中貿易戦争、在庫過剰、家電製品の需要鈍化などを売上減少の要因と分析している。

一方でランキング6位から10位の企業は前年比で軒並み業績を上げている。6位のXilinxはデータセンターセグメントではわずかに影響を受けたものの、産業、通信、自動車の各セグメントで成長し前年比24.3%増、台湾のNovatekとRealtek、英Dialogも前年比2桁増の実績を残している。

2019.08.27

2019年8月21日、市場調査会社IC Insightsは、今年上半期の半導体大手の売り上げに関するレポートを発表した。

発表によると2019年上半期の半導体サプライヤー売上上位15社の売上合計は、昨年同時期の上位15社の実績と比較して18%も減少。この上半期で前年実績を上回ったのは、唯一14位にランキングされたSonyだけだった。

売上の落ち込みはメモリの不況に伴う市場の減退によるもので、ランキングにもメモリの苦境が現れている。メモリ依存度の高い昨年1位Samsungと3位SK Hynixは、それぞれ2位、4位に後退した。

2019.08.27

2019年8月26日、GLOBALFOUNDRIESは特許侵害でTSMCを米国およびドイツで提訴した事を発表した。

発表によるとGLOBALFOUNDRIESは計16の特許侵害でTSMCを提訴。特許を侵害した技術を使って製造した半導体の米国およびドイツへの輸入禁止と損害賠償を要求している。

2019.08.23

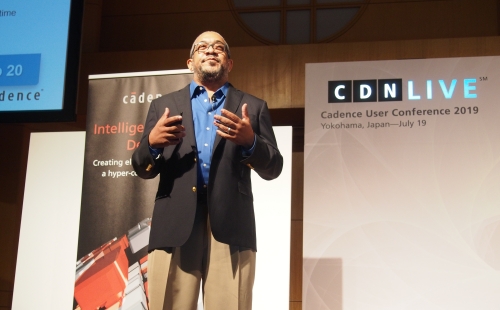

2019年7月19日、日本ケイデンスはみなとみらいで恒例のプライペート・イベント「CDNLive Japan 2019」を開催。1000人近い参加者を集めた。

「CDNLive Japan 2019」で行われた30以上のセッションのうち、半分以上はCadence製品のユーザーによる事例講演だったが、Cadenceによる講演も目を引くものが多かった。

ここでは、聴講したCadenceセッション「さらなるPPA最適化に向けてマシンラーニングを活用するデジタルICソリューション」について紹介する。講演したのは米国ケイデンス本社のデジタル・サインオフ・グループ、マーケティング及びプロダクト・マネジメント担当のバイス・プレジデントKT Moore氏である。

KT Moore氏の講演は、配置配線ツール「Innovus」を中心としたデジタル・インプリメント環境の話だったが、正直予想に反して面白かった。

まず、Cadenceツールの実績に関する話だが、相当ビジネスの調子がいいようで、KT Moore氏はデジタル・インプリメント環境としては業界のリーダーになったと明言。その裏付けとして様々な実績を挙げた。

・7nm デザインのテープアウト数は120以上

・半導体上位20社のうち17社が導入

・USのビッグカンパニーとの契約を複数獲得

・SamsungやMediaTekとの契約を拡大

中でもCadenceのデジタル・インプリメント環境が強く支持されているのは、モバイル及びデータセンター向けの汎用チップ、ネットワークやAI/ML向けのカスタムASIC、車載向け汎用チップの設計といった、いわゆる儲かりどころの分野で、既に5nm, 3nmといった先端プロセスにおいても複数プロジェクトを進行中。PPA(Performance, Power, Area)の最適化においてCadenceのソリューションは、抜きん出た能力を発揮しているという。

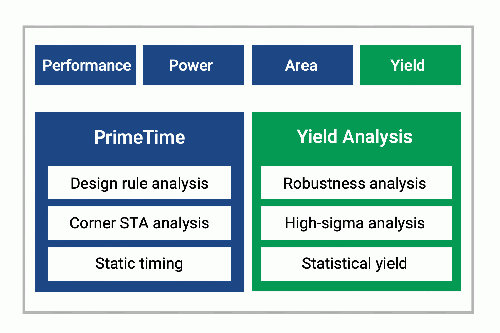

KT Moore氏によると、Cadenceは約6年近くかけてデジタル・インプリメント環境を再構築、その過程で精度を落とさず18ヶ月毎にTATの半減を実現してきたとのこと。インプリメント環境の中核をなすのは下記図の4製品で、フロントの論理合成「Genus」と配置配線「Innovus」は「iSpatial」と呼ぶ技術で高い相関性が実現されており、インプリTATの改善とPPAの向上に大きく寄与。論理合成ツール「Genus」は、強い競合製品がある中で先端プロセスデザインを中心にシェアを拡大中という話だ。

また、スタティック・タイミング解析ツール「Tempus」も売れ行き上々ということで、「Innovus」との緊密な連携によって実現する「Tempus」のタイミングECO機能は半導体上位20社の75%が利用しているという。KT Moore氏は、「Tempus」とIRドロップ解析ツール「Voltus」により、サインオフ精度のタイミング最適化とパワー最適化を合わせて実現できるのがCadenceのデジタル・インプリメント・フリーの大きな強みの一つであると繰り返し強調した。

今回のKT Moore氏の講演で興味深かったのが、デジタル・インプリメント環境におけるMachine Learning技術(以下、ML技術)の応用に関する話。昨今、EDAの世界でもML技術を用いた効率化や最適化の話が活発だが、CadenceはML技術関連の取り組みにかなり力を注いでいる様子で、KT Moore氏は幾つかの事例を示しながら、その内容を紹介してくれた。

まず「Tempus」は「Voltus」との連携によって実現するパワー・インティグリティ解析において、ML技術を用いることで、IRドロップのセンシティブなパスを特定する事が可能。この手法は従来手法では手の届かない深いパスにおけるリスクを検出するのに有効だという事で、実際に7nmモバイル向けデザインにおいて、同手法で新たなIRドロップのリスクを複数検出したという事例をKT Moore氏は紹介していた。

また、配置配線ツール「Innovus」においてもデザインのPPA最適化向けにML技術が利用されており、ユーザーが独自にトレーニングモデルを作り、社内の設計データを用いてモデルをトレーニングすることで、最適な配置配線を推論するという仕組みが既に実現されているという話。KT Moore氏によると、Cadenceではモデルのトレーニング用に安価な「Innovus」ライセンスも用意しているということで、この仕組みは既に複数の顧客で利用されており、PPAを平均約5%改善という結果をもたらしているという。なお、Cadence

ではツール内部での適用に限らず、論理合成から配置配線、サインオフ検証と一連のインプリメント・フロー全体におけるML技術の活用にも取り組んでいるという事だ。

※画像はCadence提供のデータ

個別にKT Moore氏に聞いた話では、同社内には各製品事業部をまたいで横断的に活動するML専門チームが組織されており、社内の製品開発に限らず例えばDARPAのプロジェクトなど社外においても、様々な企業、大学、団体らと積極的にML技術の設計適用に向けて協働しているという事だった。

今回のKT Moore氏の講演は、デジタル・インプリメント環境に対するCadenceの力の入れようと自信、そして更にML技術を加えてインプリ技術を強化しようという、Cadenceの並々ならぬ意気込みを強く感じさせるものだった。

※日本ケイデンス・デザイン・システムズ社

2019.08.23

2019年8月21日、Synopsysは、2019会計年度第3四半期(19年5-7月)の四半期決算を報告した。

発表によるとSynopsysの2019会計年度Q3の売上は、前年同時期比約9.4%増、前Q2比約2%増の8億5300万ドル、営業利益は前年比約25.8%増の9990万ドルだった。(※GAAP基準による会計結果)。この売上実績は同社の四半期売上記録を更新するもので、記録の更新はこれで7四半期連続となる。

SynopsysはこのQ3において、SoCパワー解析ソリューション「ZeBu Power Analyzer」、フォーマル検証ツール「VC Formal」のDatapath Validation アプリケーション、SoCの歩留まり解析および最適化ツール「PrimeYield」などを発表している。

Synopsysは2019会計年度Q4(19年8月-10月)の売上を8億3000万-6000万ドルと予測している。

2019.08.21

2019年10月3日(木)にセミナーイベント「Design Solution Forum 2019」(以下、DSF2018)がパシフィコ横浜アネックスホールで開催される。

今年で6回目の開催となるDSF2019は、セッション数、スポンサー数ともに過去最大の規模で開催。

下記5つのセッション・トラックに特別セッション企画を加え、計63のセッションが実施される予定となっている。

・Machine Learning Track AI/機械学習関連技術にフォーカス

・Essence of System Construction Track 最新の開発技術にフォーカス

・Internet of Everything Track IoTをベースに最先端の技術動向にフォーカス

・Open Source CPU Track MIPSおよびRISC-Vにフォーカス

・Arm Track Armソリューションにフォーカス

・特別セッション Rambus Edge to Cloud - End-to-end Security Solutionセミナー

また昨年に引き続きスタートアップ企業を招いた特別企画「スタートアップ×エンジニアネットワークで明日の新ビジネスを創ろう!」を実施。展示エリアの特設ゾーンでベンチャー各社の展示が行われる。

基調講演は「民間小型宇宙ロケットを実現する身近な組み込み技術」というタイトルで、インターステラテクノロジズ株式会社 Senior Computer Engineer 森岡澄夫氏が行う。この基調講演に合わせて会場内ではインターステラテクノロジズ社のロケット「MOMO」の模型やエンジン部品などが展示される予定だ。

なお今年のDSF2019で行われる各セッションは、定員に達し次第申し込み終了となるのでお申し込みはお早めに。

※DSF2019のプログラム詳細および参加登録は下記URLより。

https://www.dsforum.jp/2019/timetable/

2019.08.08

2019年8月6日、Synopsysは、車載ソフトウェア開発向けの仮想ECUプラットフォームを手掛けるドイツ企業QTronic社の買収を発表した。

今回の買収に関する条件などの詳細は不明。買収はSynopsysの2019会計年度Q4(8-10月)に完了する見込み。

QTronicは、自動車の制御ソフトウェアの開発をターゲットとした仮想ECUプラットフォーム「Silver」を提供する会社。「Silver」を用いることで仮想的なECUモデルを用いてPC上で制御ソフトウェアを実行できる。MATLAB/Simulinkや各種モデルベース開発ツールの生成したコードを実行することも可能。

QTronicによると、「Silver」は AMG, Audi, BMW, Bosch, Continental, Daimler, Ford, Honda, IAV, Porsche, Renault, Schaeffler, Volvo などのOEM/サプライヤで利用されているという。

2019.08.08

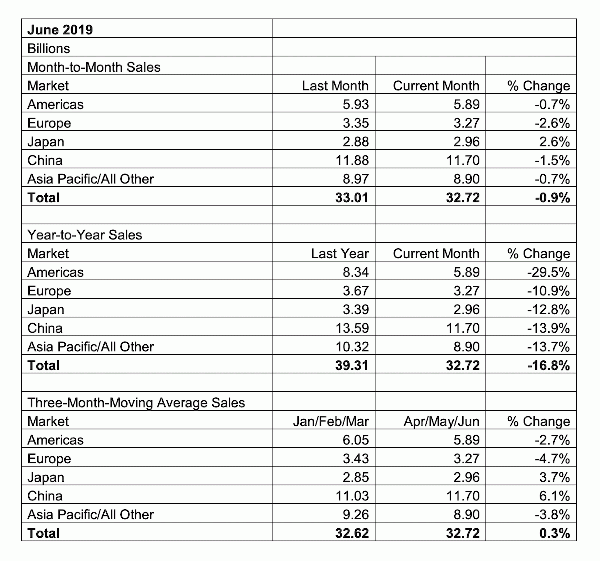

2019年8月5日、米SIA(Semiconductor Industry Association)は、2019年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年6月の世界半導体売上は、前年同月比16.8%減、前月比0.9%増の327.2億ドルという結果だった。売上実績の前年割れは2018年11月以降8ヶ月連続。2019年1月から6月までの上半期の売上合計は約1,960億ドルで前年同時期と比べると14.5%減となっている。今年に入り市況の悪化が続いているが、四半期単位で見るとQ1(1-3月)実績に対しQ2(4-6月)実績は0.3%と僅かながら増加した。

2019年6月の売上を地域別で見ると全ての地域で前年実績を下回ったが、5月実績と比較すると日本市場だけは2.6%増と売上を伸ばした。日本市場は5月に続いて2ヶ月連続で売上がプラスに転じているが、ドルベースでの実績のため為替レートの変動による影響も大きい。

日本市場の6月の売上は前月比2.6%増、前年比12.8%減の29.6億ドルで、売上を円ベースで換算すると前年比約15%減の約3,198億円となる。

2019.08.01

2019年7月5日、各種海外EDA製品を取り扱う株式会社ネクストリームは、新横浜のホテルでプライベートセミナ「Nextream Solution Seminar 2019」を開催。100名近くの参加者を集めた。

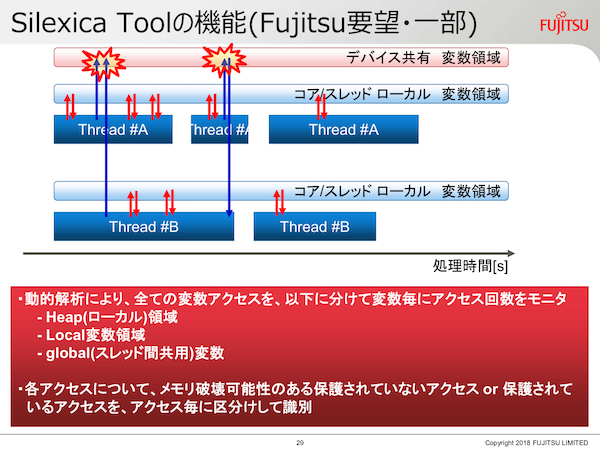

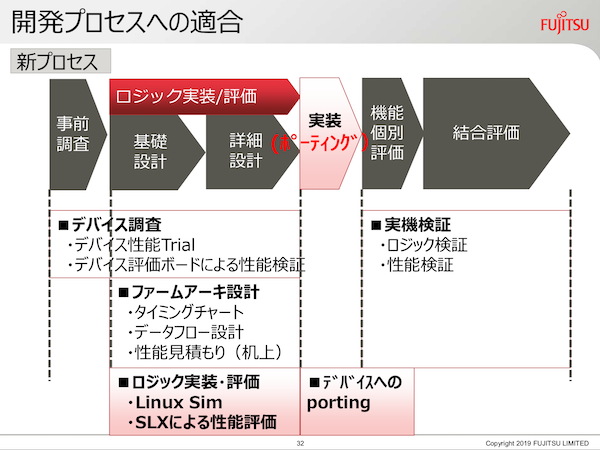

ここでは同セミナーの最終セッションとして行われた事例講演「携帯電話基地局ベースバンド処理開発へのSLX適用事例」についてレポートする。講演者は、富士通株式会社 ネットワークプロダクト事業本部 モバイルネットワーク事業部 シニアマネージャ 小野 義之 氏。

富士通 小野氏の講演は、5G向けの携帯基地局のベースバンド開発にネクストリームの取り扱うSilexica社のソフトウェア開発ツール「SLX」を活用したというもの。本来「SLX」は、マルチコア・プラットフォーム向けのソフトウェア開発に用いられるツールで、シングルコア向けに開発されたソフトウェアのマルチコアへの移植などで重宝されているが、今回の事例はファームウェアの解析に「SLX」を使ったという内容となる。

小野氏は入社以来、組み込みファームウェア開発一本というエンジニアでDSPによるリアルタイム処理の専門家。現在はシステムアーキテクトとして開発に従事しながら携帯基地局のベースバンド開発のあり方を追求している。

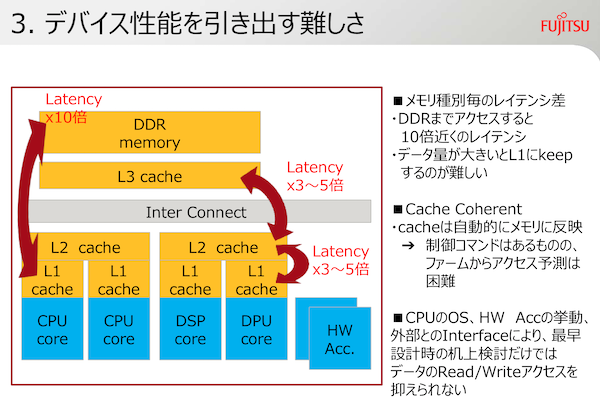

小野氏によると、5G基地局のベースベンド開発は厳しいリアルタイム性能の要求や、性能要求の異なるサービスの混在を背景とした設計の複雑さなど、これまでの3G、4G以上に大きな課題が多く、その開発費も膨大なものになりつつある。中でも小野氏が一番難しいと感じているのは「デバイスの性能をいかに引き出すか」という課題で、これが開発費高騰の原因になっているという。

「デバイス性能を引き出す」とは、すなわち基地局で使うチップをいかに上手く使いこなすかを意味するが、小野氏によると最近は複数のCPUと複数のDSPさらに数種類のASICアクセラレータがワンチップ化されているような複雑な大規模SoCが主流で、ハードウェアとして扱いが非常に難しくなってきているとの事。小野氏はその実情を以下のような例を挙げながら説明した。

・CPUとDSPのリアルタイム性能の違い:

→CPUとDSPでは3倍から10倍近い差がある

・マルチコア化/ヘテロジニアス構成により顕在化するデータの衝突:

→複数のバスに数十個のCPUコアと十数個のDSPコア

・キャッシュコヒーレンシの問題:

→データフローを設計しきれずデータの衝突が起こりレイテンシを悪化させる

・メモリアクセス・レイテンシ:

→多段キャッシュ構成によりレイテンシの差が大きくなる

小野氏曰く、CPUとDSPのコアの性能は上がってきていても、外のメモリアクセス、キャッシュのメモリアクセスがそれについて来ていないのが現状。そのため、いかにデータアクセスを少なくするか?そしていかにデータ衝突を回避するか?といった、データフロー設計がデバイス性能を引き出す(=CPU/DSPの使用効率を上げる)リアルタイム設計の最重要ポイントとなってくるとの事。小野氏は、CPU/DSPのコアが進化すればするほど、メモリアクセスのレイテンシの問題はより大きな影響を及ぼすようになると付け加えた。

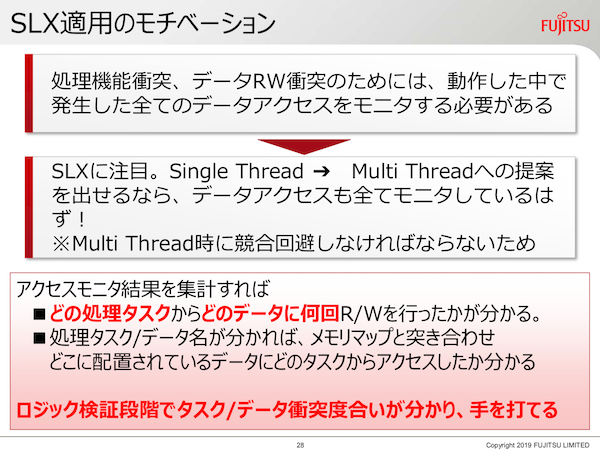

実際の開発の現場はどういった状況かというと、データ衝突を机上で見積もる事はほぼ不可能というくらいデータフローの設計が難しくなっていると小野氏。各処理の起動タイミングをイベント駆動型で考える難しさに加え、DSPだけではなくCPUも使って処理をするとなると、ある程度の予測はできたとしても正確に性能を見積ることは非常に難しく、結果的に設計段階では分からなかった事がシステム検証の段階で発覚し、再設計を強いられるといった事が起こるという。そこでこの事態を打開すべく取り組んできた中で、辿り着いた一つの答えがSilexicaのソフトウェア開発向けツール「SLX」の活用だった。

まず小野氏は上述した状況を踏まえ、不可能に近い机上検討によるデータ衝突の見積もりは諦めた。代わりにとりあえずファームウェアのコードを書いてみて、コードのロジック検証の段階で衝突する可能性のある箇所を分析するというやり方に変えた。実機動作を予測するデバイスシミュレーションでは時間が足りないので、細かいハードの動きはともかくファームウェアを論理的な観点でシミュレーションし、リードエラーや衝突の可能性をチェックした。ここで利用したのがSilexicaの「SLX」で、どの処理タスクからどのデータに何回リード/ライトを行ったか全てのデータアクセスを「SLX」を使ってモニタした。

小野氏によると、当初はシングルコア向けのソフトウェアをマルチコア向けにマルチスレッド化するツールとして紹介された「SLX」だったが、マルチスレッド化できるということは全てのデータアクセスをモニタしているはずと、ソフトウェアの解析ツールとしての可能性を見出し様々な機能の改修をSilexicaに依頼。約1年半の間、様々なツールの改修を経て現在の適用に至ったとのことで、「SLX」によってデータ衝突箇所を見つけ、アーキテクチャやデータ構造を変更するというプロセスで、データフローで衝突が起きないファームウェアを開発する事が可能となったという。

なお、富士通ではLinuxシミュレーションでロジック検証したファームウェアをそのままデバイスに実装できるコンバートツールを独自に用意。ファームウェアを基礎設計する段階からロジック実装と「SLX」を用いた性能評価を行い、そのイタレーションを回すことで設計工程の早期段階でアーキテクチャの改修が可能となった。

これにより後工程の評価工程での改修が激減。副次効果としてテ?ータ破壊やデータ競合による不正動作を根絶する事もできたという。小野氏によると「SLX」により開発プロセスを改善する事で、性能改善に関わる開発費を40%程度削減できたという話だ。

講演の終わりに聴講者からの質問に対し小野氏は、ファームウェア・アーキテクトの頭の中を可視化するツールをずっと探していたが見つけられなかったとした上で、「SLX」はSilexicaの対応のおかげで良いファームウェアの解析ツールになったとコメント。「今のやり方が正解とは限らない。技術の進化に合わせて開発の仕方も変えて行かなければならない。」という言葉で小野氏は講演を締めた。

2019.07.30

2019年7月29日、Rambusは各種インタフェースIPを手掛けるNorthwest Logicを買収する事を発表した。

今回合意に至ったRambusによるNorthwest Logicの買収は2019年Q3(7-9月)中に完了する見込み。

買収に関する取引条件などの詳細は明らかにされていない。

Northwest Logicのビジネスの中心は、各種メモリ、PCIe、MIPIのデジタルコントローラIPの販売で、市場でも大きな実績を残している。Rambusは自社の各種PHY IPとNorthwest Logicから獲得するコントローラを組み合わせて、包括的なメモリおよびSerDes IPソリューションの提供を目指す。

2019.07.24

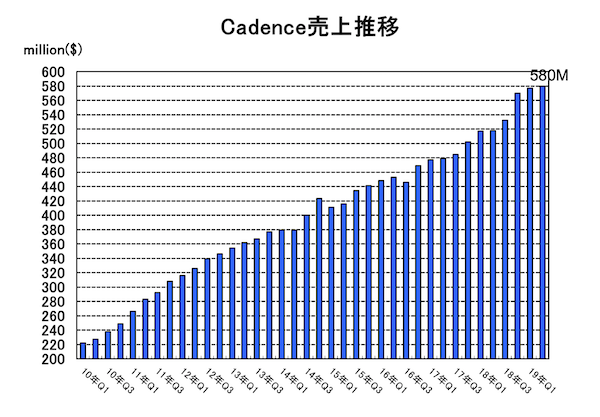

2019年7月23日、Cadenceは、2019会計年度第2四半期(2019年4-6月)の売上を報告した。

Cadenceの2019年Q2売上は、前年比約12%増、前期Q1比約0.5%増の5億8000万ドルで11四半期連続で四半期売上記録を更新した。営業利益は前年比約43%増の1億700万ドルだった。(※GAAP基準による会計結果)

CadenceはこのQ2に数々の大型製品をリリースしている。Design Automation Conferenceの開催に合わせての発表と思われるが、いいずれの製品も同社の今後の売り上げ増加に大きく寄与しそうだ。

・機械学習を用いた新技術搭載のフォーマル検証ツール「JasperGold Formal Verification Platform」※

関連ニュース・Vision/AI向けの新型DSP「Tensilica Vision Q7」※

関連ニュース・数十億ゲート対応の新型FPGAプロトタイピングシステム「Cadence Protium X1」※

関連ニュース・高精度高速大規模並列処理回路シミュレータ「Spectre X Simulator」※

関連ニュースCadenceは2019年Q3の売上を5億7000万-8000万ドル、2019年の総売上を23億1500万-3500万ドルと予測している。

2019.07.17

2019年7月16日、Armは新たなIPアクセス・プログラム「Arm Flexible Access」を発表した。

Armの発表によると「Arm Flexible Access」は、事前のライセンス契約無しにIPへのアクセスを可能とするプログラムで、一定の費用を支払うことでIPのライセンスを取得する前に設計プロジェクトを開始し、様々なIPの評価やプロトタイピングが可能となる。ライセンス契約はチップの製造が決定してからで、チップ製造時に使用した分だけロイヤリティを支払う形だ。

これまで一部のIPを除く大半のArm IPは、ライセンス契約をしてからでないとIPを利用する事が出来なかった。「Arm Flexible Access」を利用することで、ライセンス契約というプロセスそのものを省き、様々なIPの利用を検討できるようになる。なお「Arm Flexible Access」には、Arm Cortex-A, R, Mの各CPUファミリ、Mali GPU、セキュリティIP、システムIP、開発ツール、モデル、サポート、トレーニングなど、Armベースのチップ設計に必要なものが一通り含まれている。

「Arm Flexible Access」には2種類のパッケージがあり、利用料は安価なエントリー・パッケージが年間75,000ドル、スタンダード・パッケージが年間200,000ドル。いずれのパッケージもアクセス可能なIPの種類は同じだが、デープアウト可能なデザイン数が異なり、エントリー・パッケージは年間1品種、スタンダード・パッケージは年間25品種までとなっている。

Armは今回発表した「Arm Flexible Access」を同社の顧客の要望に耳を傾けた結果だとしているが、安価でアクセスの容易なRISC-VベースのプロセッサIPの普及を意識した結果とも見て取れる。

2019.07.16

2019年7月12日、Cadenceは日本のIPベンダNSITEXEによる採用事例を発表した。

発表によるとNSITEXEは、自動運転を主なターゲットに開発しているデータフロープロセッサ(DFP)IPの設計でCadenceのEDAツールを採用。論理合成、配置配線などCadenceの提供するデジタル設計フローをフル採用した。これによりNSITEXEは、以前利用していたソリューションよりも設計TATを75%削減。消費電力を8.5%、パフォーマンスを35%、面積を3.5%向上できたという。この事例についての詳細は、7/19に開催されるCadenceのイベント

「CDNLive Japan 2019」で発表される予定。

NSITEXEが採用したCadenceのデジタル設計フローには、Genus™ Synthesis Solution、Joules™ RTL Power Solution、Conformal® Equivalence Checker、Modus DFT Software Solution、Innovus™ Implementation Systemが含まれている。

2019.07.09

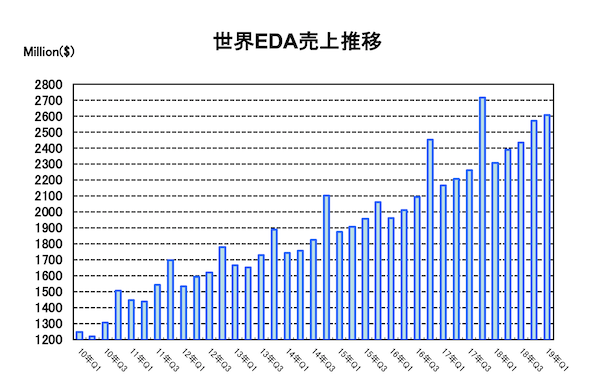

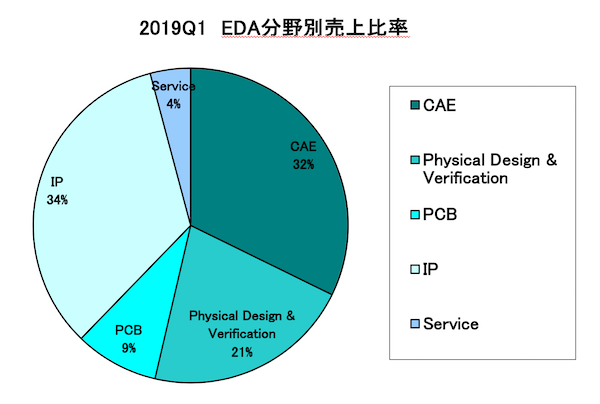

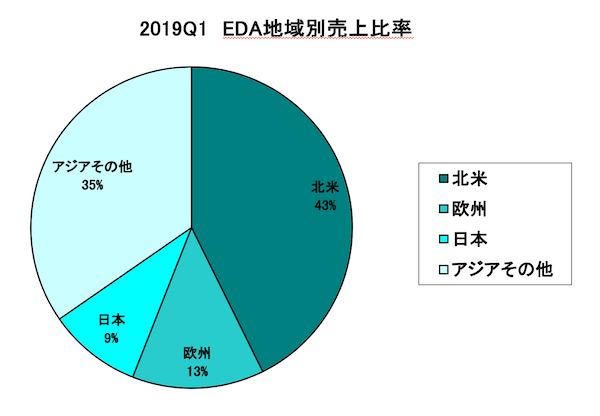

2019年7月8日、米ESD Allianceは、2019年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると2019年Q1(1-3月)の世界のEDA売上総額は、前年比約16.3%増、前18年Q4比約1.4%増の26億640万ドルだった。

前四半期の18年Q4は、2015年Q4以降3年ぶりに前年実績を割り込んでいたが、Q1は再び前年実績を上回る実績を残した。EDA業界の売上推移として、Q1売上が前年Q4売上を上回るのは極めて珍しい。

2019年Q1のEDA売上をカテゴリ別に見ると、サービス分野以外全ての製品分野で対前年比で2桁の成長を見せた。

2019年Q1のEDA売上を地域別に見ると、全ての地域で前年実績を下回った。中でもアジアその他地域は前年比29%増と大きく成長。同地域における売上として初めて9億ドルを突破した。

2019年Q1時点でのEDA業界の従業員数は前年比5.8%増の43,500人で過去最高記録を更新した。

2019年Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 8億4070万ドル 20.42Up

■IC Physical Design & Verification分野 5億5740万ドル 17.9%Up

■IP分野 8億7610万ドル 10.1%Up

■サービス分野 1億800万ドル 3.9%Down

■PCB/MCM分野 2億2410万ドル 15.9%Up

2019年Q1の地域別の売上と昨年同時期との比較は以下の通り。

■北米 11億1280万ドル 8.6%Up

■欧州 3億4590万ドル 2.8%Up

■日本 2億4470万ドル 1.4%Down

■アジアその他地域 9億290万ドル 29%Up

2019.07.09

2019年7月8日、FPGAを用いた機械学習の高速化ソリューションを手掛けるInAccelは、ロジスティック回帰アルゴリズムのトレーニングを高速化するFPGA向けのIPコアをオープンソースで公開した。

発表によるとInAccelのIPコアはXilinxのFPGA向けに最適化されたもので、Xilinxの提供するデータセンター向けのアクセラレータ・カード「Alveo U200/U250」および、AWSのf1インスタンス、Alibaba Cloudのf3インスタンスなどで利用する事が可能。ロジスティック回帰アルゴリズムのトレーニングにおいて、シングルスレッド実行と比較して最大70倍、8コア汎用CPU実行と比較して最大12倍のスピードアップを実現できるという。

InAccel IPコアの入手先:https://github.com/inaccel/logisticregression

InAccelはギリシャのスタートアップで、クラウド上のFPGAリソースの活用を容易化する事で機械学習を高速化するソリューションを提供している。同社のFPGAリソース・マネージャを利用することで、大規模アプリケーションのワークロードをサーバー内の複数のFPGAに分散したり、複数のアプリケーションでサーバー内の1つまたは複数のFPGAを共有する事が可能となる。

2019.07.05

2019年7月4日、Cadenceは、Samsung Foundryによる5nmLPEプロセスでのツール認証を発表した。

Samsungの5nm LPE(Low-Power Early)は、2020年に量産を開始する予定のEUVを用いたプロセス。今回Samsungは、CadenceのデジタルIC設計フローを構成する一連のEDAツールを5nm LPEプロセス対応ツールとして認証した。ファウンドリ競合のTSMCは約2ヶ月前に5nmプロセスでの各社のツール認証を発表している。またCadenceの競合Synopsysは一足早く先月の段階でSamsung 5nm LPEプロセスでのツール認証を発表している。

なお今月19日に開催されるCadenceのセミナー「

CDNLive Japan 2019」では、ソシオネクストがCadenceのツールを用いた5nmテストチップの開発事例を発表する予定。

2019.07.03

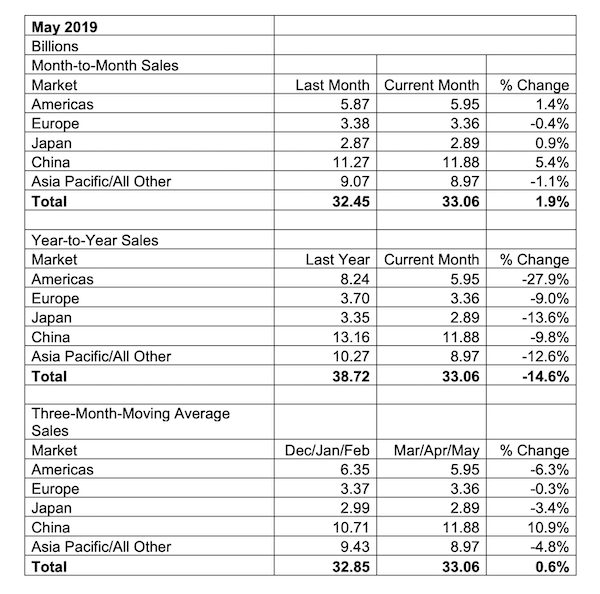

2019年7月1日、米SIA(Semiconductor Industry Association)は、2019年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年5月の世界半導体売上は、前年同月比14.6%減、前月比1.9%減の330.6億ドルという結果だった。売上が前の月の売上を上回るのは7ヶ月ぶりだが、メモリの市況を考えると今後の市場回復の見通しは依然良くない。世界半導体市場は2019年に入り1月から5月まで全て前年実績割れ。売上の減少は2018年11月以降7ヶ月連続となる。

2019年5月の売上を地域別で見ると全ての地域で前年実績を下回ったが、4月と比較すると中国市場が5.4%増とやや回復。微増ながら北米、日本市場もプラスに転じた。

日本市場の5月の売上は前月比0.9%増、前年比13.6%減の28.9億ドルで、売上を円ベースで換算すると前年比約13.7%減の約3174億円となる。

2019.06.28

2019年6月27日、ニューロモーフィック・チップを手掛けるBrainChipは、Socionextとの提携を発表した。

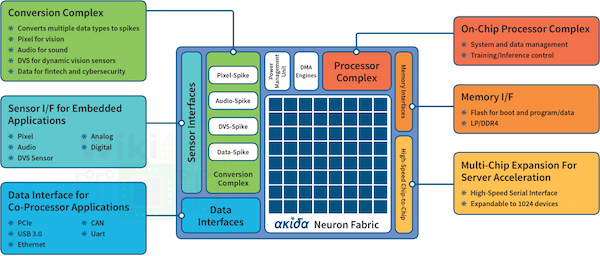

発表によるとBrainChipは、同社のエッジAI向けニューロモーフィックSoC「Akida」の量産を視野に、その開発および製造についてSocionextと提携した。Socionextは「Akida」のRTL以降のインプリメントを行い、TSMCでのチップ製造へと繋げるようだ。

Akidaのアーキテクチャ:Source BrainChip

BrainChipは今年Q3に「Akida」のサンプル出荷を予定しており、将来的に5つの製品を展開する計画。同社はIPコアのライセンス提供も行っている。ちなみにSocionextはAIチップを手掛けるGyrfalcon Technologyとも提携しており、同社のIPを用いたSoC製品を開発している。

2019.06.27

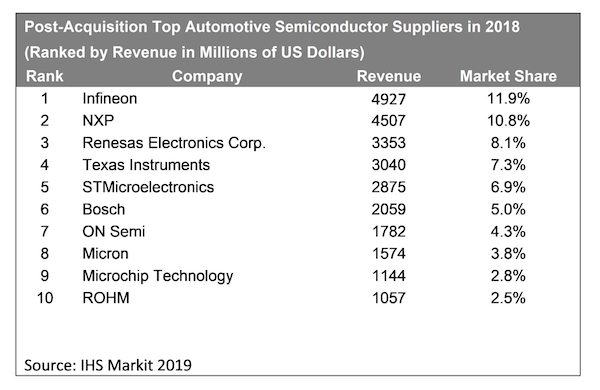

2019年6月26日、ElectronicsWeekly.comの記事:

市場調査会社IHSが昨年の売上ベースでまとめた車載半導体サプライヤのランキング。CypressがInfineonに買収された後、ランキングは下記の図のようになる。

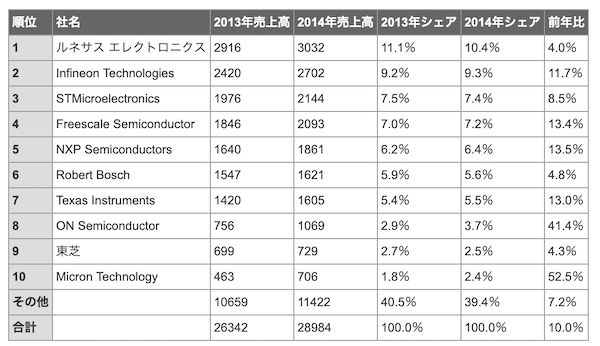

ちなみに同じくIHSがまとめた2014年時点のランキングはこちら。

ルネサスは2015年から首位陥落。

NXPはFreescaleを買収しシェアを拡大、InfineonもCypressの買収で今回首位に立った。

ルネサスはインターシルの買収効果が乏しい上に、車載半導体市場の伸びしろをうまく拾えていない。半導体市場アナリストのIC Insightsの調べでは、2014年から2018年にかけて車載半導体市場は50%以上成長している。

2019.06.26

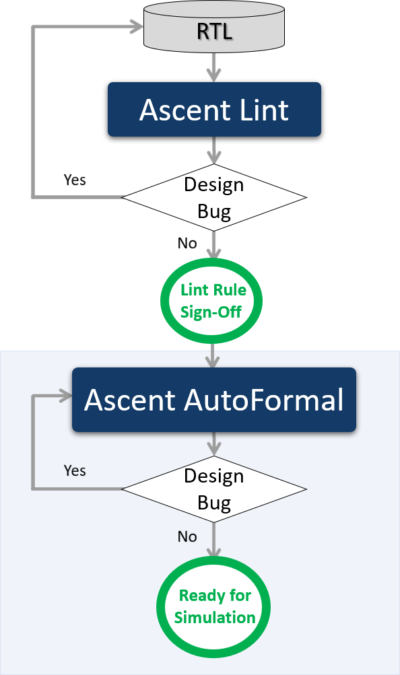

2019年6月25日、フォーマル検証技術をベースとしたEDAソリューションを手掛ける米Real Intentは、フォーマル検証ツール「Ascent AutoFormal」の性能向上を発表した。

発表によると「Ascent AutoFormal」の最新バージョンは、前バージョンと比較して10倍以上の性能向上と5倍のデザイン・キャパシティを実現した。これによりユーザーは、テストベンチが出来上がる前の設計初期段階でのRTLバグ検出を迅速に達成可能となる。

性能向上はシングルコアの場合で5-10倍、自動分割による複数コアの並列実行で2-4倍、数百万ゲートのデザイン規模に対応可能との事。また新しいエンジンは、特定のチェックに対する解析が収束しているかどうかを動的に判断し、必要に応じて新しいチェックに進む事が可能。RTLの詳細なデザイン情報を元に最初のフォーマル解析でクロック、リセット、FSM、ラッチなどの設計要素を正確に解析し、フォーマル解析のイタレーションを削減できる。

「Ascent AutoFormal」の最新バージョンは既にリリース済み。Real IntentはLintツール「Ascent Lint」と「Ascent AutoFormal」を組み合わせた二段階の早期RTL検証を推奨している。

2019.06.26

2019年6月25日、Mentor Graphicsは、中国Iluvatar CoreX社によるエミュレータの採用事例を発表した。

発表によるとIluvatar CoreXは、AIチップおよびそのソフトウェア開発向けにMentorのエミュレータ「Veloce Strato」を標準採用。Iluvatar CoreXの担当者は、「Veloce VirtuaLab PCIeやVeloce Protocol AnalyzerなどのMentorのVeloceソリューションは、特にハードウェアおよびソフトウェアの検証とデバッグにおいて、検証環境の重要な要素となっている。」とコメントしている。

Iluvatar CoreXは2015年設立の中国のファブレス・ベンチャーで、GPGPUアーキテクチャをベースとしたデータセンターおよびエッジ向けのAIチップを手掛けている。同社のチップは2020年に市販される予定だが、同社は既に最新の

DAWNBenchのディープラーニング・ベンチマーク、推論レイテンシ部門で3位にランキングされている。

Mentorの担当者のコメントによると、Mentorのエミュレータを導入するAIチップを手掛ける顧客が増えているようだ。

2019.06.20

2019年6月18日、オープンソース・ハードウェアの設計を推進するChips Allianceは、MetrixとImperasの2社が同団体メンバーに加わった事を発表した。

Chips Allianceは今年3月にLinux Foundationが立ち上げをアナウンスしたプロジェクトで、RISC-Vベースのオープンソース・ハードウェアの設計に関連する高品質なオープンソース・コードをホストおよびキュレートするする事を目的としている。

CHIPS Allianceの初期立ち上げメンバーは、Esperanto Technologies、Google、SiFive、Western Digitalの4社で、今年4月にAntmicroもメンバーに加入している。

今回新たにメンバーとなったMetrixはクラウドベースの低コストなシミュレーション環境を提供するカナダの企業。Imperasはバーチャル・プロトタイピング・ソリューションを手掛けるイギリスの企業。両社はオープンソースのISAであるRISC-Vの実装検証について貢献するという話。Metrixが具体的にどのような働きをするのかわからないが、Imperasは既にオープンソースで公開している「riscvOVPsim ISS」をChips Allianceの活動に寄与するようだ。

2019.06.20

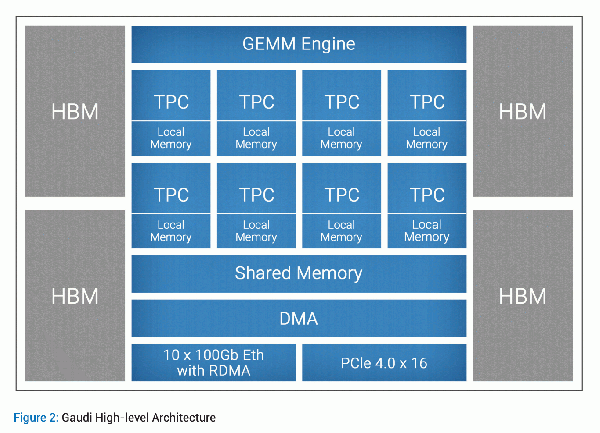

2019年6月17日、AIプロセッサーを手掛けるHabana Labsは、新製品となる学習用AIプロセッサ「Gaudi」を発表した。

Habana Labsは2018年Q4に推論用のAIプロセッサ「Goya」をリリースしており、今回発表した学習用の「Gaudi」は同社2品種目のAIプロセッサーとなる。

Habana Labsのホワイトペーパーによると、学習用「Gaudi」と推論用「Goya」の仕様上の違いは大きく4つ。

・第2世代の新型「TPC(Tensor Processor Core)」を搭載

・FP32, BF16, INT32, INT16, INT8, UINT32, UINT16, UINT8をサポート

・RDMA over Converged Ethernet(RoCE v2)機能を統合

・HBM2メモリを搭載

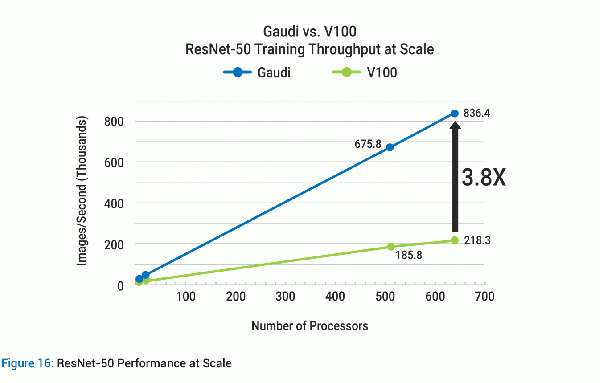

Habana Labsによると、「Gaudi」プロセッサをベースにしたトレーニングシステムは、同数の「NVIDIA Tesla V100 GPU」で構築されたシステムよりも最大4倍のスループットを実現。小さいバッチサイズでも高スループットを維持できるため、トレーニングシステムのパフォーマンスをほぼ線形にスケーリング可能で、数百の「Gaudi」プロセッサを用いた大規模システムも構築可能だという。

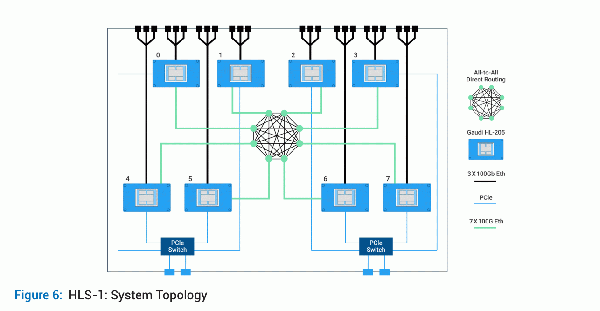

なお「Gaudi」プロセッサは「Goya」と同じく下記2種類のカードに搭載された形で提供される。100GイーサネットリンクとRoCE機能をサポートするAIプロセッサは業界初だという。

・HL-200 - 8ポートの100GbイーサネットをサポートするPCIeカード

・HL-205 - OCP-OAM仕様に準拠したメザニンカードで、10ポートの100Gbイーサネットまたは20ポートの50Gbイーサネットをサポート

※HLS-1と呼ぶHL-205を8枚、PCIeコネクタと24個の100Gbイーサネットポートを備える「Gaudi」システムと、同システムを複数搭載するための専用ラックも用意される。

※画像は全てHabana Labs Web上のデータ

学習用AIプロセッサ「Gaudi」は2019年後半に早期顧客にサンプル出荷が開始される予定。

2019.06.20

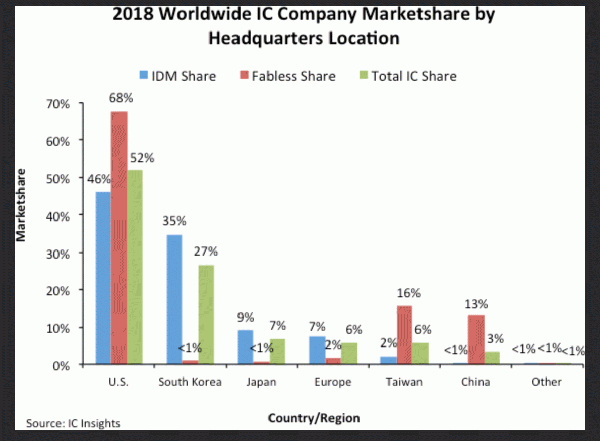

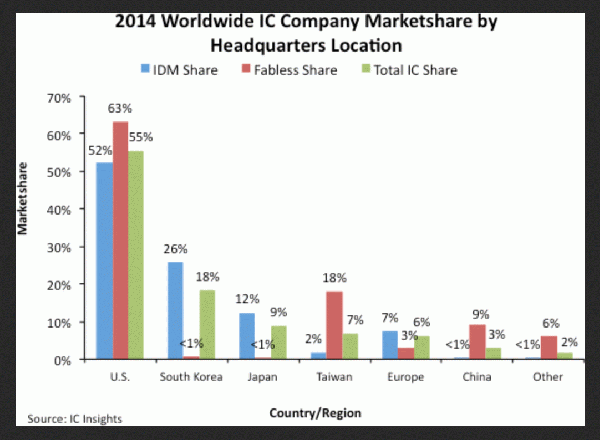

2019年6月18日、IC Insightsのレポート:

IC Insightsの発表によると、本社の所在地別で見た2018半導体市場シェアは以下の図の通り。

※画像はIC InsightsのWeb上のデータ

・米国はファブレス企業のシェアは伸びたがIDMのシェアが減り、全体的な市場シェアは3ポイント落ちた。

・韓国はIDMのシェアが大きく伸び、全体的な市場シェアは9ポイント伸びた。

・日本はIDMのシェアが減り、全体的な市場シェアは2ポイント落ちた。

・欧州は全体的な市場シェアは4年前と変わらず。ファブレスのシェアが1ポイント伸びている。

・台湾はファブレスのシェアが減り、全体的な市場シェアは2ポイント落ちた。

・中国はファブレスのシェアが伸びたが、全体的な市場シェアは4年前と変わらず。

この4年間で市場シェアを増やしたのはIDMのシェアが大きく伸びた韓国だけ。米、欧、中はファブレスのシェアは伸びているが、市場全体のシェアに対する影響は小さい。

2019.06.18

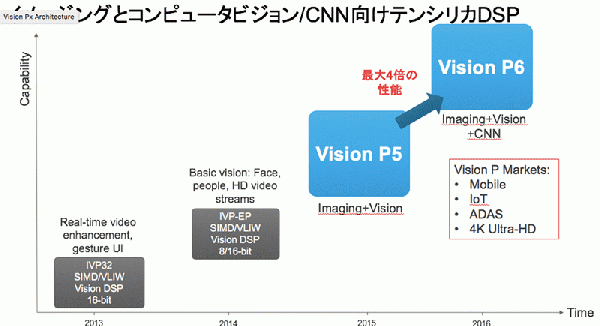

2019年6月14日、Cadenceは、東芝デバイス&ストレージ株式会社による同社Tensilica IPの採用事例を発表した。

発表によると東芝は、次世代車載SoCにCadenceの「Tensilica® Vision P6 DSP」を4コア実装し、SoC内の画像認識プロセッサとしてのパフォーマンス向上を実現。「Vision P6 DSP」により、様々な物体を高精度に検出し識別するための複雑なアルゴリズムを非常に低い消費電力で実行することが可能になったとしている。発表では東芝のSoCの製品名は明らかにされていないが、今年9月よりサンプルが出荷される予定のDNNアクセラレータを搭載した新型SoC「Visconti 5」と想像される。(※

関連ニュース)

※画像はCadence社Web上のデータ

東芝は、DSPコアの採用と合わせて自社のソフトウェア開発キット (SDK) にCadence Xtensa® Imaging Library (Xi-Lib) を統合。これにより東芝のSoCのユーザーが容易に「Vision P6 DSP」にアクセスすることが可能となると同時に、東芝自身が自社の既存のビジョンアルゴリズムをDSP向けに容易にポーティングすることが可能となった。なお、「Vision P6 DSP」コア、開発ツールおよびライブラリはすべて、SoCベンダがISO 26262の自動車安全水準のレベルD (ASIL D) 認証を獲得できるよう設計されており、東芝の新型SoCも機能安全要件に対応しているという。

2019.06.18

019年6月17日、Electronicsweekly.comの記事:

米半導体業界団体SIA(Semiconductor Industry Association)は、米国政府に対して中国への半導体チップ販売禁止の一部解除を求めた。

テレコム用のスイッチ機器を除く、国家の安全保障上のリスクと無関係の製品は中国への販売が許されるべきという主張がそのベースとなっている。

今回の要求は、Intel, Qualcomm, Micron, XilinxがSIAに働きかけた模様。

米国企業は昨年Huawei社に110億ドル相当の半導体チップを販売したと報じられており、米中貿易摩擦の結果として、Broadcomは今年20億ドルの損失を予測している。

2019.06.14

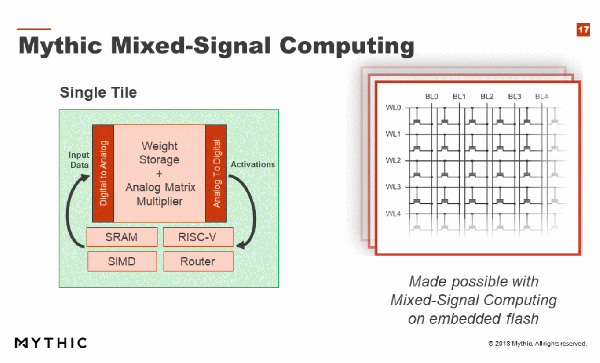

2019年6月12日、AIチップを手掛けるベンチャーMythicは、資金調達B-1ラウンドで3,000万ドルを調達した事を発表した。

発表によると今回のラウンドをリードしたのは、Valor Equity PartnersというSpaceXにも投資しているシカゴのベンチャー・キャピタルで、Micron、Lam Researchといった半導体関連企業も新たな投資家としてラウンドに参加した。今回のラウンドを含めた同社の累計調達額は8,600万ドルに到達。Softbankも同社に出資している。

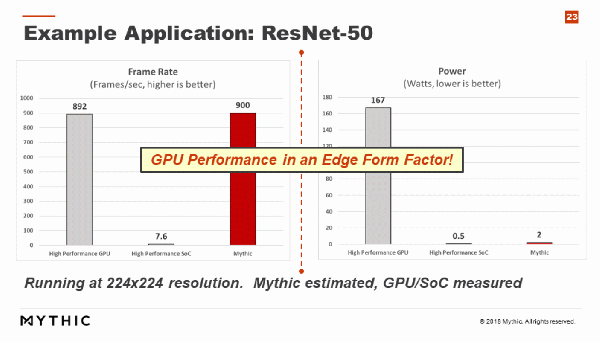

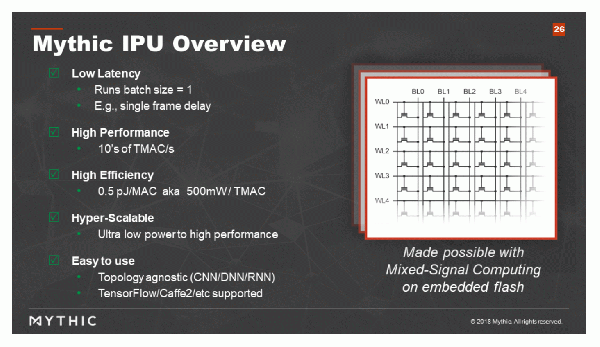

Mythicは2012年設立のAIチップ・ベンチャーで、テキサス州オースティンとカリフォルニア州レッドウッドシティーに拠点を置く。開発しているAIチップはデータセンターからエッジまでを狙う推論チップで、フラッシュメモリ・アレイを用いたアナログ・コンピューティングによりニューラルネットワークの行列演算を行うアプローチをとる。具体的には、メモリ素子を調整可能な抵抗として使用、入力は電圧として供給し、出力される電流を計測することで演算結果を得る。アナログ・コンピューティングで処理できないものはSIMD演算器を用いる。このアプローチにより、ニューラルネットワークの重みを記憶するためのメモリが不要となり、非常に高性能、低消費電力かつ高効率な推論処理が可能になる。Mythicは高性能GPU並みの推論パフォーマンスをハイエンドSoC並みの消費電力で実現できるとしている。

※画像はMythic社Web上のデータ

Mythicは、2019年第4四半期中に早期顧客向けの製品出荷を予定している。

2019.06.12

MPSoC 2019 国際フォーラムの開催のご案内です。

19th International Forum on MPSoC for Software-defined Hardware

開催期間:2019年7月8日〜12日

開催地:ザ・プリンス箱根芦ノ湖

参加登録 : http://www.mpsoc-forum.org

Society sponsors:IEEE CAS, IEEE CEDA, EDAA

Industrial sponsors:Synopsys, Arteris IP, ソシオネクスト

世界最高峰のSoC・IT技術専門家50名以上の講演者を招き、最先端のAI技術やIoT技術など、次世代コンピュータシステムを構築する最新のSW・HW技術に関して5日間に渡り熱い議論を繰り広げます。

皆様のご参加をお待ち申し上げます。

MPSoC 2019 General Co-Chairs

石原 亨・一色 剛

MPSoC 2019ハイライト:

基調講演 (Keynote):

7/ 8: 杉本 英樹氏 (CTO, NSITEXE, Inc., JAPAN)

7/ 9: Naim Ben-Hamida氏 (Director, Ciena, Canada)

7/10: 北山 浩透氏 (Automotive Industry CTO, IBM, JAPAN)

7/11: 山岡 雅直氏 (主任研究員, 日立製作所, JAPAN)

招待講演 (In-depth presentation):

長谷川淳氏 (ルネサス)

宮森高氏 (東芝)

松本祐教氏 (トプスシステムズ)

笠原博徳氏 (早稲田大学)

中村祐一氏 (NEC)

貞末多聞氏 (リコー)

新家昭彦氏 (NTT)

井上弘士氏 (九州大学)

高瀬英希氏(京都大学)

Yankin Tanurhan氏 (Synopsys)

K. Charles Janac氏 (Arteris Inc.)

Gerhard P. Fettweis氏 (TU Dresden)

Kiyoung Choi氏 (SNU)

Benoit de Dinechin氏 (KALRAY)

Arnaud Grasset氏 (Thales R & T)

Sunghyun Lee氏 (Openedges Tech.)

Ashkan Seyedi氏 (HP Labs)

Timothee Levi氏 (東京大学)

2019.06.12

2019年6月11日、ElectronicDesignの記事:

Marvellはサーバーチップ開発に関するArmとの提携拡大を発表した。Armは少なくとも今後3年間、Marvellの研究開発に「相当な」金額を投資することに合意した。

Marvellは、Intelの置き換えを狙うArmv8-Aアーキテクチャをベースにしたサーバー・プロセッサ「ThunderX2」を開発している。同チップは、既存のx86ベースのチップと比較して、高性能、低消費電力で所有コストを削減できるとされている。

MarvellとArmは過去10年間密に協力を進めていたが、更にその関係を強化しArmベースのサーバーチップ開発に力と資金を注ぐ。

Armは、Applied MicroのX-Gene CPUをベースにしたAmpere Computingのサーバチップの開発も支援している。

2019.06.10

2019年6月6日、RISC-Vベースのプロセッサ・コアを手掛けるSiFiveは、資金調達Dラウンドの成功を発表した。

発表によると今回SiFiveの資金調達Dラウンドを主導したのは、Sutter Hill Ventures、Chengwei Capital、Spark Capital、Osage University Partners、Huamiら既存の投資家で、新たにQualcomm Venturesも投資に加わった。同ラウンドでSiFiveは計6,540万ドルを調達。同社の累計調達額は1億2,500万ドルを超えた。

SiFiveは過去18ヶ月の間に従業員40人未満から400人以上に拡大。オレゴン本社の他に米国内に4つの拠点を構える他、インド、中国、韓国、台湾にも拠点を開設している。

SiFiveはRISC-Vベースのプロセッサ・コアとそれを用いたカスタムSoCの提供を主なソリューションとしており、既に同社ソリューションを用いたデザイン実績は100を超えるという。

2019.06.07

2019年6月6日、Electronics Weekley.comの記事:

ARMのビッグカスタマーの一人QualcommがRISC-Vベースのプロセッサ・コアを手掛けるSiFiveに出資するという。

SiFiveには既にSamsung, Intelも出資しており、同社の累計調達額は1億2500万ドルに達している。

チップベンダTop10のうち6社がSiFiveの顧客で、既にプロセッサ・コアのライセンス販売数は100以上との事。

2019.06.07

2019年6月6日、オープンソース・プロセッサの採用促進を目的としたグローバルな非営利組織「OpenHW Group」がその活動について発表した。

「OpenHW Group」は、オープンソース・プロセッサの利用に関するコラボレーションのためのプラットフォームを提供する非営利組織で、RISC-Vベースのオープンソースコア「CORE-Vファミリ」を提供すると共に、そのエコシステム開発を進めるために組織されたもの。

「OpenHW Group」を立ち上げたのは、RISC-V Foundationの元エグゼクティブディレクターであるRick O'Connor氏で、既に下記13のスポンサーを獲得。年内にスポンサーは25程度に増える見通しで、既にEclipse Foundationと戦略的パートナーシップを締結しているという。

Alibaba、Bluespec、CMC Microsystems、Embecosm、ETH Zurich(大学)、GreenWaves、Imperas、Metrics、Mythic AI、NXP、Onespin、Silicon Labs、Thales,

「OpenHW Group」が提供するRISC-Vベースのオープンソースコア「CORE-Vファミリ」については、未だ詳細が明らかにされておらずリリース予定も不明だが、「CORE-V」はプロセッサ・サブシステムIP、設計者向けのツール、ソフトウェアなどと合わせて提供されるようで、「OpenHW Group」は「CORE-Vファミリ」の提供を通じてSoCを設計するプロセッサコアの開発者、ハードウェアおよびソフトウェアエンジニアを支援するとしている。

「OpenHW Group」は現在メーリングリストの加入者を募集中。6/11からチューリッヒで開催されるWOSH / RISC-V Workshop Zurichに参加する予定。

2019.06.06

2019年6月4日、DigiTimesの記事:

業界筋の情報によると、2020年に発売予定のNvidiaのAmpere GPUは、TSMC 7nmではなくSamsungの7nm EUVプロセス技術を使用して製造される予定。

Samsungは明らかにTSMCの顧客を積極的に切り崩しにかかっている。生産能力の面では、AppleやAMDのニーズを抱えるTSMCの7nmプロセスよりもSamsungの7nm EUVプロセスに分がある。

2019.06.06

2019年6月4日、米SIA(Semiconductor Industry Association)は、2019年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2019年4月の世界半導体売上は、前年同月比14.6%減、前月比0.4%減の321.3億ドルという結果だった。これで2019年に入り1月から4月まで全て前年実績割れ。売上の減少は2018年11月以降6ヶ月連続となる。

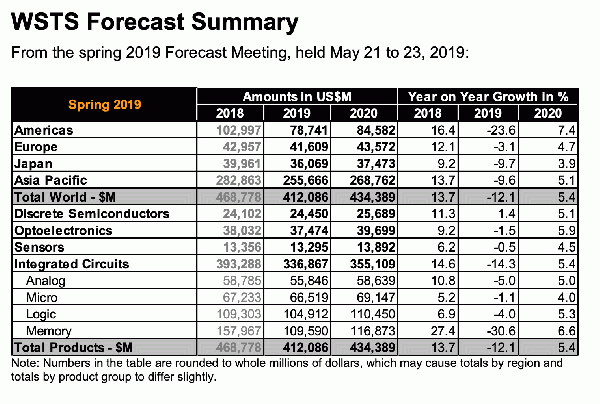

同日発表されたWSTSによる春季予測によると、2019年の世界半導体市場は前年比12.1%減の4120億ドルとなる見通し。WSTSは、昨年11月時点で2.6%のプラス成長、今年2月の時点で3%のマイナス成長と予測していた。

2019年4月の売上を地域別で見ると全ての地域で前年実績を下回った。中でも壊滅的なのは北米市場で前年比29.5%減の57.5億ドルだった。北米市場は5ヶ月連続で売上を落としている。

日本市場の3月の売上は前月比2.4%増、前年比10.9%減の29.3億ドルで、売上を円ベースで換算すると前年比約7.5%減の約3271億円となる。

調査会社IC Insightsの予測によると、このままQ2(4-6月)は売上が前年実績を割り込むが、そのリバウンドでQ3(7-9月)は若干回復する見通し。これまで4四半期連続で売上が落ちた事は一度もないという。

2019.06.05

2018年6月4日、WSTS(世界半導体市場統計)の2019年春季半導体市場予測が発表された。

発表によると2019年の世界半導体市場は前年比12.1%減の4120億ドル。ほぼ全ての製品カテゴリで売上が減少する見通し。来年2020年には5.4%のプラス成長が見込まれるが、売上額は2018年以下の水準に留まる。全てはメモリ売上の乱高下によるものと言っても過言ではない。メモリの売上は2018年は前年比27.4%増、今年は30.6%減、来年は5.4%増の見通し。メモリに比べれば第二の柱であるカスタム・ロジックの売上は安定している。地域別売上で見ると今年はシェア2位の北米市場の打撃が大きい。

なお、2019年の半導体市場についてWSTSは、昨年11月時点で2.6%のプラス成長、今年2月の時点で3%のマイナス成長と予測していた。

今年3月以降、調査会社の市場予測は軒並み下方修正されている。

2019.06.04

2019年5月28日、SynopsysはSoCの歩留まり解析および最適化ツール「PrimeYield」の提供開始を発表した。

Synopsysによると新製品「PrimeYield」は、特許技術の高速な統計的手法とマシンラーニング技術によって、これまでは不可能とされていたシリコン実装前の完全な統計的歩留まり解析を実現するもので、Synopsysはをデザイン・サインオフを再定義するブレイクスルー・ソリューションであると主張する。

従来は、統計的シミュレーションを完全に実行するには数日ないし数週間という膨大な時間を要し、その適用範囲も僅か数十セルが限界とされていた。しかしSynopsysは、開発した特許技術「パラメトリック歩留まり解析技術」と「統計的相関性モデリング技術」により、統計的歩留まり解析および最適化の適用範囲を数億セルにまで拡大。合わせてマシンラーニング技術を用いる事で、シミュレーションの劇的な高速化を実現した。これにより、大規模なSoCに対してもリコン前の歩留まり解析を実行することが可能となった。Synopsysは「PrimeYield」の実現する歩留まり解析を前倒しは、設計品質の面でも製造コストの面でもインパクトが大きいとしている。

※画像はSynopsys社Web上のデータ

Synopsysの説明によると、「PrimeYield」は「フルチップ・パラメトリック歩留まり解析技術」により、モンテカルロ・スタティックタイミング解析よりも1,000倍高速な統計的歩留まり解析が可能。マシンラーニング技術により、歩留まりへの相関性と感受性が統計的に高いとされているクリティカルなセルを短時間で特定することができるという。

2019.06.04

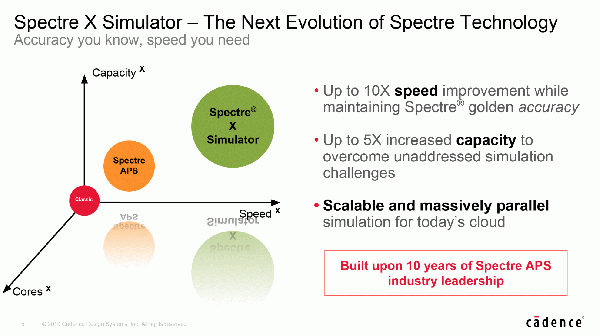

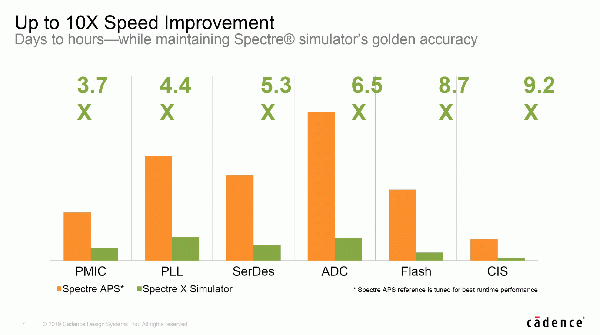

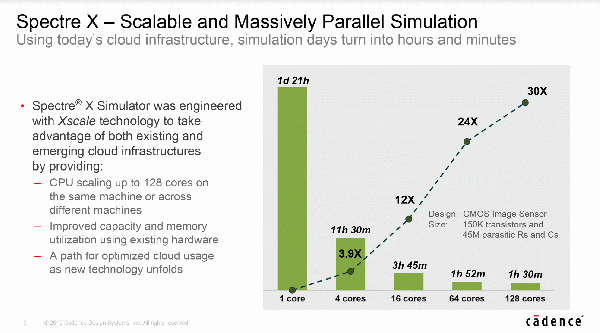

2019年6月4日、Cadenceは新製品となる大規模並列処理回路シミュレータ「Spectre X Simulator」を発表した。

発表によると「Spectre X Simulator」は同社の回路シミュレータ「Spectre」の後継製品で、処理できる回路規模を5倍に拡張、大規模並列処理によりSpiceレベルの精度を保ったまま10倍高速なシミュレーションを実現する。精度と処理速度のトレードオフは単一のパラメータにより容易にコントロール可能。並列シミュレーションでは、データセンターやクラウド環境上の数百個のCPUを用いた分散処理に対応する。利用にあたっては、各ファウンドリによって認証済の既存のデバイスモデルや、既存のSpectre設計フローをそのまま使用することができる。また、「Spectre AMS Designer」を活用したミックスシグナル検証にも対応する。

※画像はCadence提供のデータ

発表には先行ユーザーのMediaTek, Mellanox, Renesasらがコメントを寄せており、「Spectre X Simulator」の適用結果として、ポストレイアウト検証におけるシミュレーション速度を5-10高速化できたとしている。

2019.06.03

2019年5月30日、Mentor Graphicsは、AMDによる物理検証ツール「Calibre nmDRC」の成功事例を発表した。

今回発表されたAMDの事例の内容は以下の通り。

・7nm GPU「Radeon Instinct™Vega20」(132億トランジスタ)の物理検証において、MentorのDRCツール「Calibre nmDRC」を使用

・「Calibre nmDRC」はMicrosoftのクラウド環境「Azure」上で実行

・使用したAzure上のVirtual Machine(AMD EPYC™プロセッサ搭載)は計69台、4,140コア

・TSMC 7nm Calibreデザインキットを使用して、約19時間で2回の検証パスを完了

Mnetorによると、Calibreは最近の機能強化でメモリ要件を改善。7nmデザインのフルチップ検証において、メモリ要件を最大50削減した顧客が複数存在しているという。

Mentorの「Calibre」は、クラウドフローにおいてもTSMC 7nm/5nm FinFETプロセス向けツールとして認証されている。

2019.06.03

2019年5月31日、日本経済新聞の記事:

米国政府の取引禁止措置を受け、SynopsysがHuaweiとの取引を停止した。

Synopsysは従業員にHuaweiの半導体子会社HiSiliconに対するソフトウエア更新などの中止を通知した。

Synopsysは22日に発表した決算資料で、安全保障上懸念のある外国企業を列挙した米政府の「エンティティー・リスト」に入った特定企業との取引を停止したと言明。それはHuaweiを指しているとみられる。

関係者によるとCadenceもHuaweiとのメールなどのやり取りを自粛しているという。

2019.05.31

2019年5月30日、Wave Computingとバーチャル・プロトタイピング・ソリューションを手掛けるImperasは、無償の命令セットシミュレータ「MIPSOpenOVPsim」を発表した。

発表によると「MIPSOpenOVPsim」は、MIPSのオープンソース化を進める「MIPS Open™」コミュニティ向けに提供される無償の命令セットシミュレータで、2019年6月3日よりMIPS Openプログラム(https://www.mipsopen.com)からダウンロードできるようになる。

「MIPSOpenOVPsim」は、完全なシングルコアCPUを実装した命令精度のMIPS CPUシミュレータで、ホストPC上で1秒あたり5億命令以上の速度でシミュレーションを実行可能。MIPSベース・システム向けのソフトウェアの先行開発や、MIPS CPUコア設計の初期段階の実装テストや検証、コンプライアンス・テストの加速などに役立てることができる。

「MIPSOpenOVPsim」の対応するMIPS仕様と拡張機能は以下の通り。

・The MIPS 32 and 64-bit Instruction Set Architecture (ISA) Release 6

・MIPS SIMD Extensions v. 1.0

・MIPS DSP Extensions

・MIPS Multi-Threading (MT)

・MIPS MCU

・microMIPS Architecture

・MIPS Virtualization (VZ)

2019.05.31

2019年5月30日、Fudzillaの記事:

Fudzillaは、最近行われたファイナンシャル・アナリスト向けのイベントでXilinxのCEO Victor Pengが明らかにした事として、以下のような内容を報じている。

・Versalの早期アクセスプログラムには100社を超える顧客が集まった

・Versalは昨年既にテープアウトされ、今年サンプル出荷予定

・最初に出てくるVersalチップのトランジスタ数は370億以上

VersalはAIコア、AIエッジ、AI RF、プライム、プレミアム、HBMと計6種類の製品ラインナップで展開される計画だが、最初に出てくるチップがどのシリーズなのかは不明。ただ、最初に出てくるチップはシリーズ最大規模のチップではないようだ。市場動向からするとVersal AIエッジが先に出てくると見られる。トランジスタ数370億以上というと、NVIDIAのSoC「Xavier」の4倍以上となる。

2019.05.30

2019年5月29日、脳を模倣するニューロモーフィック・チップを手掛けるBrainChipは、AIコア「Akida」のIP販売を発表した。

発表によると「Akida」はASIC組み込み用のニューラル・プロセッシング・コアで、BrainChip独自のニューロモーフィック回路上で脳の動きを模倣するスパイキング・ニューラル・ネットワーク(SNN)を実行することが可能。推論および教師なし学習に対応する。スペックの詳細は明らかにされていないが、性能、面積、消費電力、コンフィギュラビリティの全てにおいて、既存ソリューションを上回るとされている。

ニューラル・プロセッシング・コア「Akida」は、IPとしてライセンス提供されるほか、チップ単体としても提供可能。チップはエッジ・アプリケーションをターゲットとしたスタンドアロンのニューラルネットワーク・プロセッサとして機能する。また、BrainChipが既に提供しているCyber securityアプリケーション用の「Akida」搭載USBドングル、開発用のリファレンスボードも用意されている。リファレンスボードは、USB3.0ポートを介してホストコンピュータや開発環境「Akida Development Environment(ADE)」と接続して使用することもできる。

ユーザーのニューラルネットワークは、ADEを用いてSNNに置き換えられ「Akida」のニューラルファブリック内で実行される。事前に訓練されたネットワークを実行することも、自律学習させることも可能。乗算・加算のみを高速処理するアクセラレータとは異なり、ニューラルネットワーク全体が実行される。SNNはCNNよりも低消費電力で「Akida」によるSNNは電力性能が非常に高いとされている。

今回発表されたニューラル・プロセッシング・コア「Akida」が既に同社がリリースしている「Akida NSoC」のコアと同等だとすると、「Akida」 は120万個のニューロンと100億個のシナプスを持ち、IntelおよびIBMのニューロモーフィック・チップよりも100倍優れた電力効率を発揮する。(Intel:Loihi, IBM:TrueNorth, いずれもテストチップ)

BrainChipは既にオーストラリアで上場しており、スパイキング・ニューラル・ネットワーク技術を用いたビジネスを展開しており、警察や空港、カジノなどにソリューションを提供している。

2019.05.29

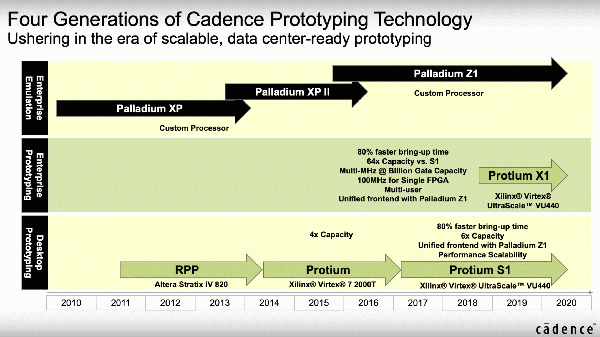

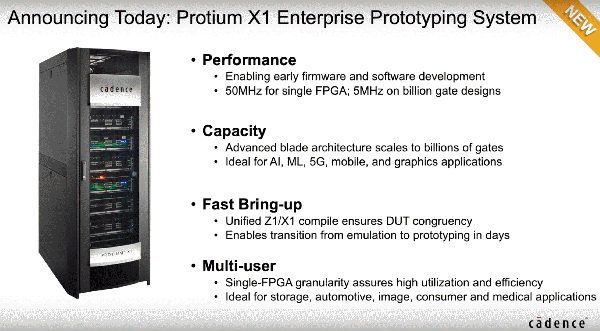

2019年5月28日、Cadenceは、FPGAベース・プロトタイピング・システムの新製品「Cadence Protium X1」を発表した。

発表によると「Cadence Protium X1」は、FPGAベース・プロトタイピング・システムとして同社4世代目の製品で、既存の最上位製品「Protium S1」とは異なる新たなアーキテクチャーにより新規開発されたもの。ベースとなるFPGAは、「Protium S1」と同じXilinxの20nm FPGA「Virtex Ultra Scale VU440」を使用している。

「Protium X1」はデータセンターへの設置を前提に最適化されたシステムで、FPGAボードを搭載したブレードを最大8台搭載できる筐体(ラック)が用意されている。ブレード1台当たりのデザイン容量は1億5000万ゲートで1ラック当たり12億ゲート。ラックは最大32台接続可能で最大1,536個のFPGAを利用できる。この豊富なFPGAリソースにより数十億ゲートの大規模デザインにも対応可能で、ブレード1台当たり最大6名のマルチユーザーで利用することも可能。また、新たなデザイン分割機能、インターコネクト技術などにより性能も大きく向上されており、「Protium X1」は数十億ゲートのデザインでも最大5MHz、シングルFPGAであれば100Mhzの実行速度を提供できるという。(「Protium S1」では4億ゲートを超えるデザインではパフォーマンスが低下していた)

なお、「Protium X1」はエミュレーション・システム「Palladium Z1」と共通のフロントエンドを使用しており、従来製品同様、容易な適用、早期立ち上げを実現。Cadenceは、エミュレーションからプロトタイピングへ数日で移行できるとしている。機能面では、数千万クロックサイクル/数千の信号をリアルタイムにキャプチャーする「ハイパフォーマンス・データキャプチャー・カード」が新たに用意されたほか、再コンパイルすることなくすべての信号に動的アクセスが可能となる新機能「Prototyping Full Visibility」が追加されている。

「Protium X1」は既に出荷中で、NVIDIAがGPUのソフトウェア開発で「Protium X1」を使用したというプレスリリースが出ている。

2019.05.29

2019年5月23日、Synopsysは、新しいパワー解析ソリューション「ZeBu Power Analyzer」を発表した。

発表によると「ZeBu Power Analyzer」は、FPGAベースのエミュレーション・システム「ZeBu Server 4」に新しいマルチスレッドの電力解析エンジンを組み合わせたソリューションで、数十億サイクルにも及ぶ複雑なソフトウェアを実行した際のSoCの電力消費をシステマティックに解析することが可能。Synopsysは、設計者が想定したシナリオではなく実際のソフトウェアを用いた高精度なパワー解析により、電力を大量消費する箇所を見逃すリスクを大幅に削減できるとする。

また、「ZeBu Server 4」を用いる事でパワー解析を大幅に高速化。従来のシミュレーションベースの手法で数か月かかるパワー解析をわずか数時間で実行でき、従来シミュレーションベース手法と比較すると1000倍高速なパワー解析が可能。パワーサインオフ・ツール「PrimePower」とのシームレスな連携により、サインオフ検証へと繋げることができるという。

なお「ZeBu Power Analyzer」は既に出荷中で、主要なZeBuユーザーの多くが活用しているとの話。発表にはMediaTekが「ZeBu Power Analyzer」のユーザーとしてコメントしている。

-thumb-600x72-5398.png)