NEWS

2021.12.03

2021年12月2日、Cadenceはクラウド上でのサインオフ検証に関するTSMCおよびMicrosoftとの協業とその成果を発表した。

発表によるとCadence, TSMC, Microsoftの3社はクラウド環境の活用によるサインオフ検証の高速化に向けて協業。100億超トランジスタの大規模デザインの検証時間を大幅に短縮することに重点を置き取り組みを進めてきた。その結果、従来のスタティック・タイミング解析では数日かかっていた100億超トランジスタ級デザインのタイミング・サインオフを数時間で完了することが可能となった。それを実現するのはMicrosoftのクラウド環境「Azure」と、Cadenceの提供するクラウド環境上のEDAツールを管理するプラットフォーム「Cadence CloudBurst」、そしてCadenceのスタティック・タイミング解析ツール「Tempus」で、TSMCのプロセスを採用した顧客はこれら環境によるTAT短縮、計算機コストの削減といった恩恵に預かることができる。

Cadenceのスタティック・タイミング解析ツール「Tempus」には、分散スタティックタイミング解析 (DSTA) として知られる大規模分散型並列処理機能が備えられている。

膨大な計算機リソースを利用するEDAツールを用いたチップ設計は、ここ数年でクラウドへの以降が本格化しつつあり、ファウンドリ、EDAはベンダ、クラウドベンダが三つ巴となってソリューションの拡充に力を注いでいる。そんな状況もあり、どれだけ高速にEDAツールを走らせることができるか?が、サーバーチップのパフォーマンスの1つの指標になってきていたりする。

2021.12.03

2021年12月2日、RISC-Vプロセッサを手掛けるSiFiveは、RISC-Vコアの新製品「Performance P650」を発表した。

新製品「P650」は今年6月に発表された「P550」を改良したコアで命令幅の拡張によりクロックサイクルあたりのパフォーマンスを40%向上。追加のアーキテクチャ拡張により最大クロック周波数が向上し、「P550」と比較して50%増、Armの「Cortex-A77」を上回るパフォーマンスを実現する。

SiFiveによると「P650」はSPECInt2006のスコアで11/GHzを達成する見込みで、SIFiveは「P650」を業界最速のRISC-Vプロセッサと主張する。ちなみにこれまで業界最速をうたっていた「P550」のSPECInt2006のスコアは8.65/GHzだった。

なお「P650」はコヒーレント・マルチコア・コンプレックスを使用して最大16コアにスケーラブルに拡張可能。プラットフォームレベルのメモリ管理や割り込み制御ユニットなどのシステムコンポーネントを備え、仮想化のための新しいRISC-Vハイパーバイザー拡張機能をサポートする。

SiFiveは「P650」のアーキテクチャプレビューを2022年のQ1に主要な顧客に提供し、その後2022年夏頃に製品の一般提供を開始する予定。

2021.12.02

2021年11月29日、Synopsysは同社のAIベース設計システム「DSO.ai」を活用したSamsungの成功事例を発表した。

発表によるとSamsungは最先端のモバイル向けSoCの設計でSynopsysのAIベース設計システム「DSO.ai」を活用。その結果、チップの動作周波数100MHz超と当初の設計目標を上回る性能を実現すると同時にチップ全体の消費電力を大幅に削減することに成功した。設計期間は従来の人手設計よりも数週間早かったという。

Synopsysの「DSO.ai(Design Space Optimization AI)」は、フィジカル設計向けのAIアプリケーションで、これまで人間が考えて行っていた様々な工程での各種パラメータ設定を自律的に最適化することが可能。強化学習を実行しながら、最適なPPAを達成するための最適なアクションを探索する。

「DSO.ai」は2020年3月の発表以降18ヶ月間で15以上の顧客、50以上のプロジェクト、15以上のアプリケーションで利用されてきた実績があり、人手による設計では困難な設計結果を残している。Synopsysによると、設計フローの最適化、フロアプランの最適化、ライブラリの最適化、カスタムクロックの生成、PDNの最適化、ボルテージ・スケーリング、DTCO(Design Technology Co-Optimization)などにおいて「DSO.ai」が活用されているという。

Samsungは「DSO.ai」発表当初からSynopsysのパートナーとして同技術を積極的に活用しており、今回の成果を「AI技術を用いたチップ設計の記念すべき一里塚となった」とコメントしている。「DSO.ai」は高度な自律設計能力だけでなく極めて高い設計生産性を実現できる点も大きな評価を得ているようだ。

なおSamsungは今回設計したモバイルSoCを自社の最先端プロセスで製造する予定。

2021.12.02

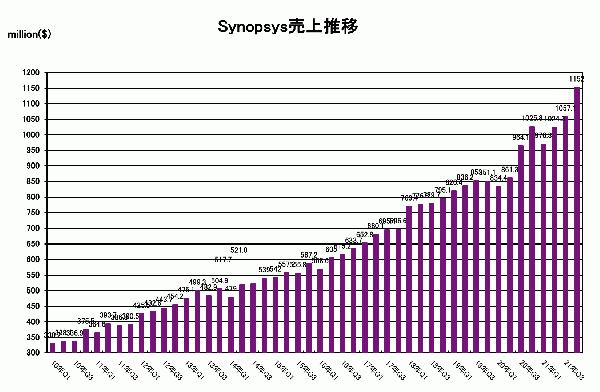

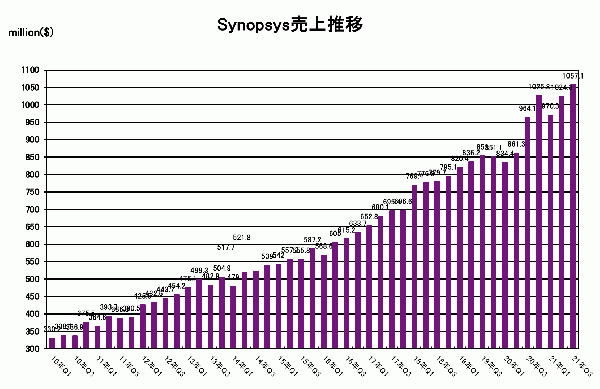

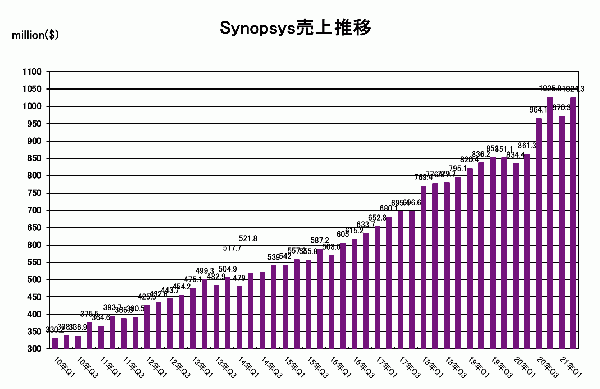

2021年12月1日、Synopsysは、2021会計年度第4四半期(21年8-10月)の四半期決算を報告した。

発表によるとSynopsysの2021会計年度Q4の売上は、前年同時期比約12.4%増、前Q3比約8.9%増の11億5200万ドルで四半期売上として過去最高を記録した。なおQ4の営業利益は前年比約2%増の2億140万ドルだった。(※GAAP基準による会計結果)

Synopsysの2021会計年度の売上額合計は、前年比14.1%増の42億400万ドルで過去最高。営業利益の合計は前年比約14%増の7億4750万ドルだった。

Synopsysはこの10年間で売上を約2.7倍に拡大した。

Synopsysは、2022年度Q1(11-1月)の売上を12億5000万-8000万ドル、2022会計年度の売上を47億2500万-47億7500万ドルと予測している。

2021.11.19

2021年10月20日、各種組み込みソフトの開発ソリューションを手掛ける京都マイクロコンピュータ株式会社(KMC)は、同社の組み込みソフト開発プラットフォーム「SOLID」のバージョンアップを発表した。

KMCの提供する「SOLID」は、同社が開発したTOPPERSベースの独自RTOS「SOLID-OS」と同RTOSベースの組み込みソフト開発環境(IDE,コンパイラ,デバッガ)をセットで提供するプラットフォームで、2017年発売以降すでにプリンタやデジカメなど複数の商用製品で採用されており、RTOSと開発環境を一体化させるというこれまでなかったアプローチで組み込みソフト開発の効率化・品質向上を実現している。

発表によると最新の「SOLID Ver.3.0」では、次世代のプログラミング言語として注目されているRustが利用可能となる。これはOSSを取り込んだ製品開発に実績と自信がある同社ならではの対応で、「SOLID」のRust対応を実現することで更なるソフトウェアの品質向上と開発効率の向上を目指す。

KMCによると、既に今年9月末に「SOLID-OS」がRustにTier3ターゲットとして追加されており、Rust対応の「SOLID Ver.3.0」は今年12月にリリースされる予定となっている。今回のRust対応では「SOLID」でRustによる記述が可能になるだけではなく、各種Rustの標準ライブラリも利用可能となるということだ。

なお、「SOLID」のRust対応に関する詳細は、先日開催されたDesign Solution Forum 2021にてKMCの辻氏がスポンサーとして講演しているので、

そちらの録画ビデオを参照頂きたい。 ※登録すればどなたでも視聴可能

2021.11.19

2021年10月12日、Siemensは配置配線ツール「Aprisa」のバージョンアップを発表した。

発表によると最新バージョン「Aprisa 21.R1」では下記のような大幅な機能強化が施され、前世代製品よりも最大2倍高速に動作することが可能となった。

・平均フルフロー・ランタイムが30%削減、大規模/複雑な設計の場合ランタイムが最大2倍高速に

・配置、配線、クロックツリー合成、タイミング分析など全ての主要エンジンを機能強化

・大規模設計で平均30%、複雑な設計で最大60%メモリフットプリントを削減

Siemensの配置配線ツール「Aprisa」は、Avatar Integrated Systemsが開発したEDAツールでその起源はATopTechにある。Siemensは昨年12月にAvatar社を買収し「Aprisa」を手に入れた。「Aprisa」は先端プロセス設計で一定の評価を得ており、Samsung, Broadcom, Cypress, Mellanox, Xilinxなど複数の大手企業がユーザーとなっていた。ここ最近の顧客状況は定かではないが「Aprisa」はTSMC N6プロセスで認証されており、今回の発表でも「6nm、5nm、4nmプロセスに対応」と紹介されている。Siemensは、「Aprisa」のR&Dチームを2倍以上に増やすなど「Aprisa」への投資を積極的に進めており、Cadence同様、Synopsysの牙城の切り崩しを狙っているようだ。

2021.11.18

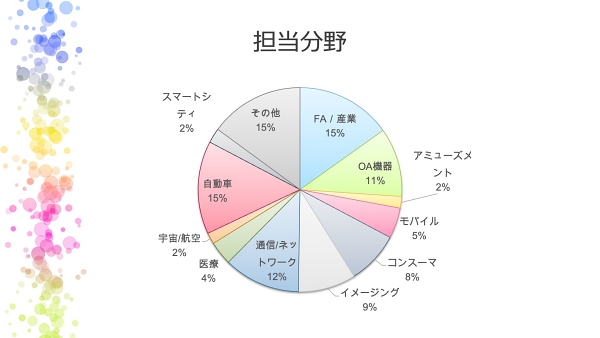

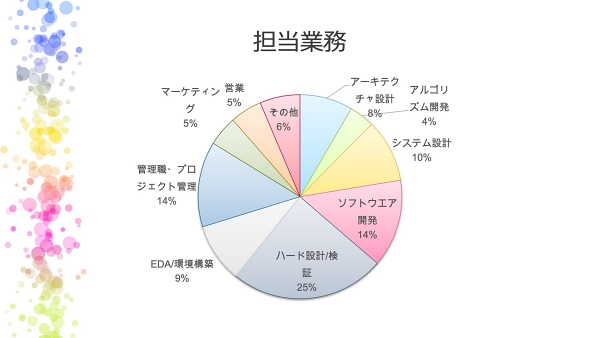

2021年11月4日、5日の2日間、技術者向けのセミナーイベント「Design Solution Forum 2021(DSF2021)」が初となる2日間完全オンライン形式で開催された。

今回で8回目の開催となるDSF2021は、史上2番目に多い1,164名の登録者を集めた。

藤井氏は半導体市場で存在感を増しているプラットフォーマー各社の先端チップを紹介した上で、チップの処理性能を現在の1000倍以上に高めるこれからのチップ開発の姿を解説。半導体設計への投資の少なさに懸念を示しつつ、日本の半導体企業のビジネスにはまだまだ伸びしろがあるとエールを送った。※オンデマンドでご視聴頂けます。

2日目の基調講演は一般社団法人サイバースマートシティ創造協議会 代表理事の豊崎氏が登壇。豊崎氏は自ら推進している「スマートシティ・プロジェクト」を日本の電機産業再興のためのプロジェクトと称し、これまでの道のりと今後の展望を紹介。長年半導体業界で活躍してきた豊崎氏は、チップ開発とスマートシティ開発の類似性を指摘し、スマートシティ開発は半導体エンジニアの知識が活かせる新しいフィールドだと語った。

惜しくも僅差で最優秀講演賞を逃した京セラドキュメントソリューションズ株式会社、田中 邦彦氏の講演

「複合機で実現するエッジAI開発事例」も聴講者の評価が高かった。※オンデマンドでご視聴頂けます。

毎回様々な分野、様々な立場のエンジニアが集うDSFだが、今回のDSF2021ではレガシーな事業分野に属さない「その他」分野の参加者が増え、アーキテクチャ設計、システム設計、アルゴリズム開発など上流設計に携わるエンジニアの参加が増加した。

開催時期は未定だが、また来年もDesign Solution Forum 2022が開催される予定となっている。

2021.11.03

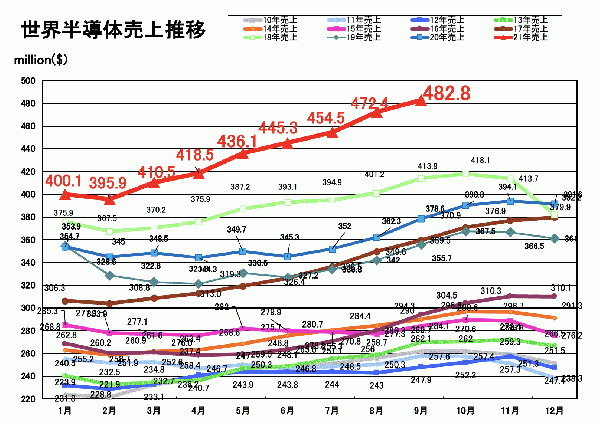

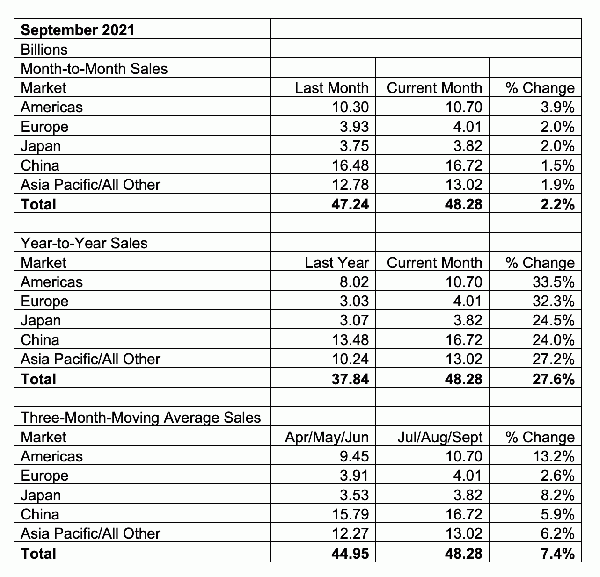

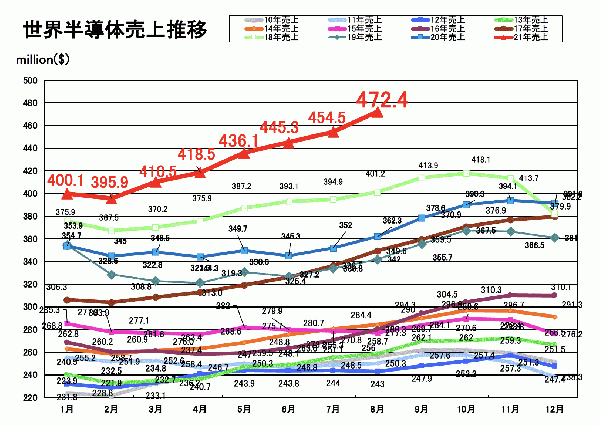

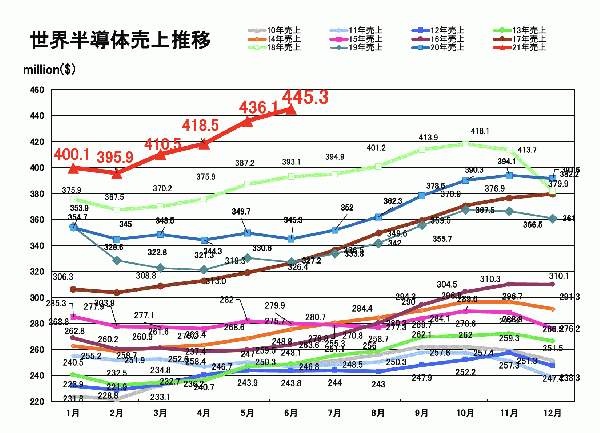

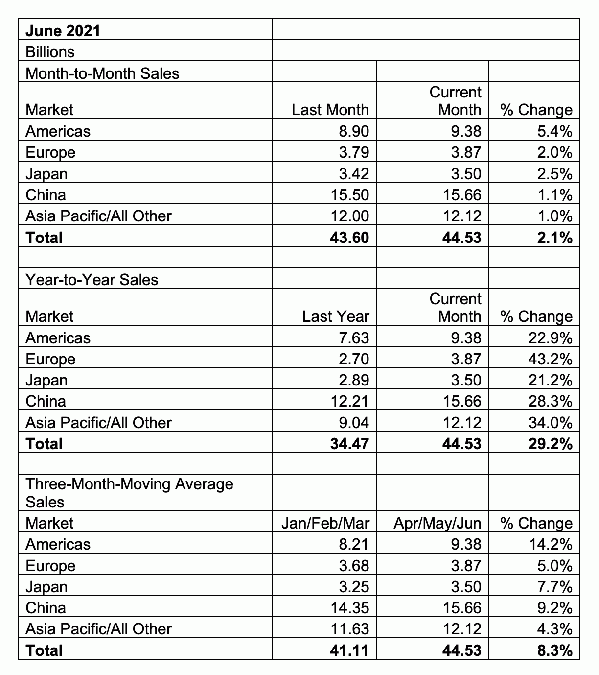

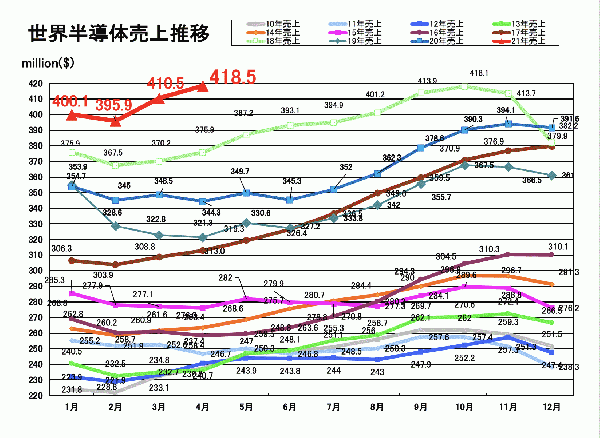

2021年11月1日、米SIA(Semiconductor Industry Association)は、2021年9月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年9月の世界半導体売上は、前年同月比27.6%増、前月比約2.2%増の482億8000万ドルだった。この実績は単月の売上としては過去最高。好調を維持する今年の半導体市場は4月より6ヶ月連続で単月売上記録を更新中。単月売上が前年同時期を超えるのは20ヶ月連続で、2021年の売上は過去最高を記録した2018年を超えるのがほぼ確実となってきた。

SIAの集計によると2021年Q3(7-9月)の世界半導体売上額は前年比27.6%増、2021年Q2比7.4%増の計1,448億ドルで、このQ3は半導体ユニットの出荷数においても過去最高だっという。

2021年9月の世界半導体売上を地域別にみると、全ての地域で前年比24%を超えるプラス成長を記録。欧州は7,8月に続いて前年比30%を超える売上増、北米も8月に続いて30%増を超える大きな成長を示した。

日本市場も前年比24.5%増と好調で売上を円ベースで換算すると前月比約2.2%増、前年比約30%増の約4,210億円となる。日本市場の売上が前年同月比プラス成長となるのは11か月連続。

2021.10.26

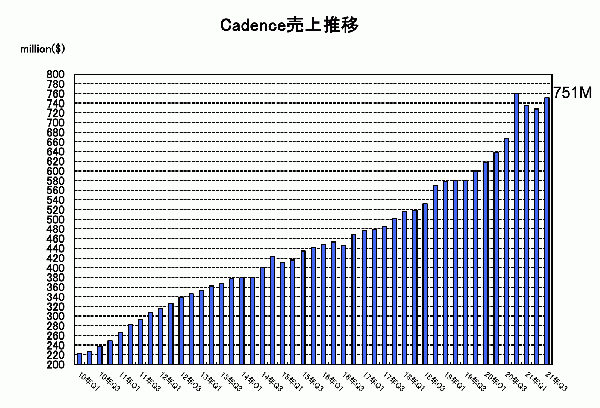

2021年10月25日、Cadenceは、2021会計年度第3四半期(2021年7-9月)の売上を報告した。

Cadenceの2021年Q3売上は、前年比約12.6%増、前期Q2比約3.1%増の7億5100万ドル、営業利益は前年比約8.6%増の1億7600万ドルだった。(※GAAP基準による会計結果)

Cadenceの当Q3実績は同社のQ3売上記録として過去最高。Cadenceは2020年Q4から4四半期連続で売上7億ドル超を維持している。

CadenceはこのQ3に以下のような新製品およびニュースを発表している。

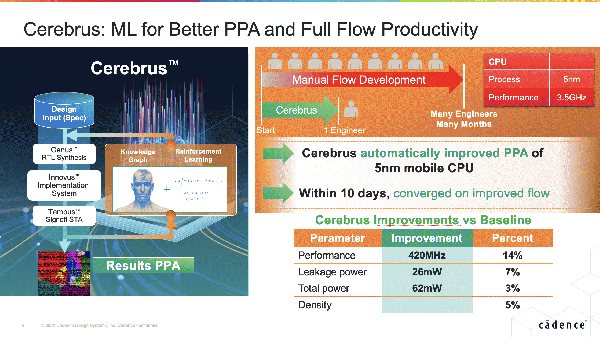

・マシンラーニングベースの設計システム「Cerebrus」を発表

・2021年12月にAnirudh DevganがCEOに就任することを発表

・AI SoC向けのAIエンジン「Tensilica AI プラットフォーム」を発表

・3DIC向けの新製品「Integrity 3D-ICプラットフォーム」を発表

Cadenceは2021年Q4の売上を7億4500万-6500万ドルと予測。2021年の年間売上予測を29億6000-29億8000万ドル程度と上方修正している。

2021.10.19

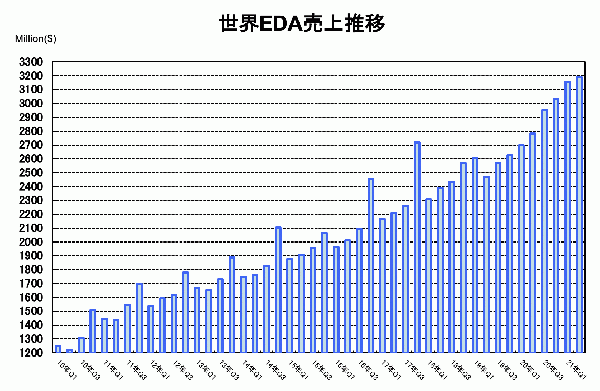

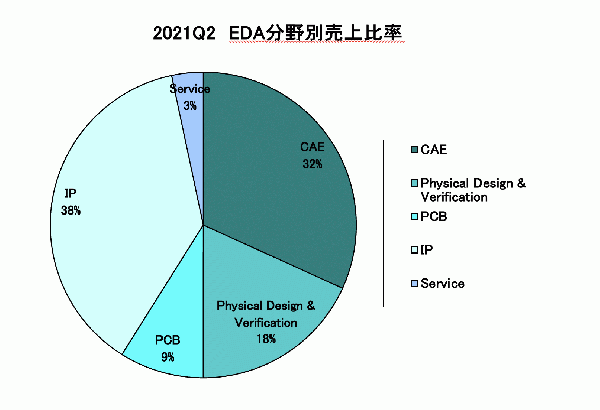

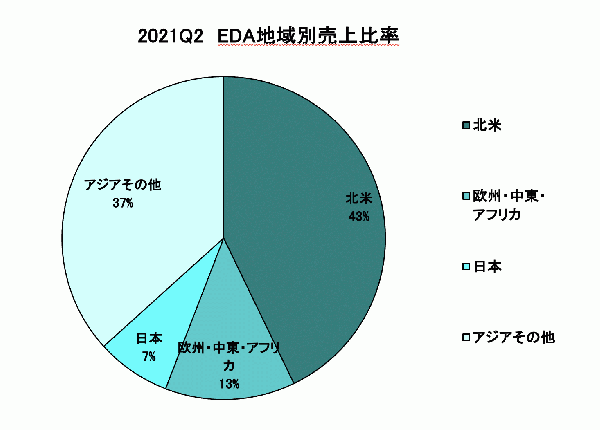

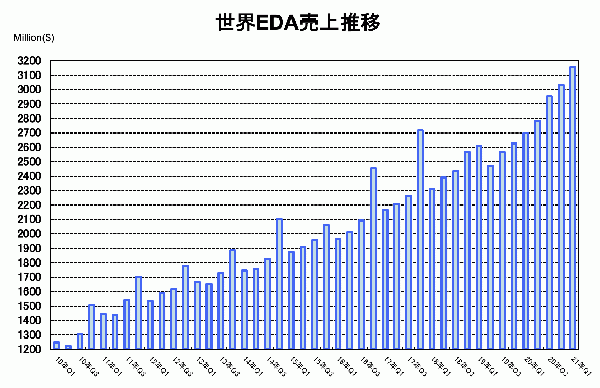

2021年10月12日、米ESD Allianceは、2021年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2021年Q2(4-6月)の世界のEDA売上総額は前年比約14.6%増、前Q1比約1%増の31億9140万ドルで、四半期売上記録を更新した。売上記録の更新は5四半期連続。四半期売上が前年実績を上回るのは10四半期連続となる。

2021年Q2のEDA売上をカテゴリ別に見ると、IC Physical Design & Verification分野以外は全て前年比で2ケタ成長を記録した。中でもIP分野は大きな成長を見せ四半期記録を塗り替えた。

2021年Q2のEDA売上を地域別に見ると、日本市場以外は全て前年比でプラス成長。最大市場の北米が18.3%増と最大の成長を示した。

2021年Q2時点でのEDA業界の従業員数は前年比7.3%増の49,964人でQ1よりも約1.9%増加した。

2021年Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 10億1460万ドル 10.1%Up

■IC Physical Design & Verification分野 5億8150万ドル 0.4%Down

■IP分野 12億490万ドル 27.1%Up

■サービス分野 1億610万ドル 23.1%Up

■PCB/MCM分野 2億8440万ドル 16.8%Up

2021年Q2の地域別の売上と昨年同時期との比較は以下の通り。

■北米 13億6730万ドル 18.3%Up

■欧州・中東・アフリカ 4億1500万ドル 9.9%Up

■日本 2億3790万ドル 1%Down

■アジアその他地域 11億7120万ドル 15.9%Up

2021.10.08

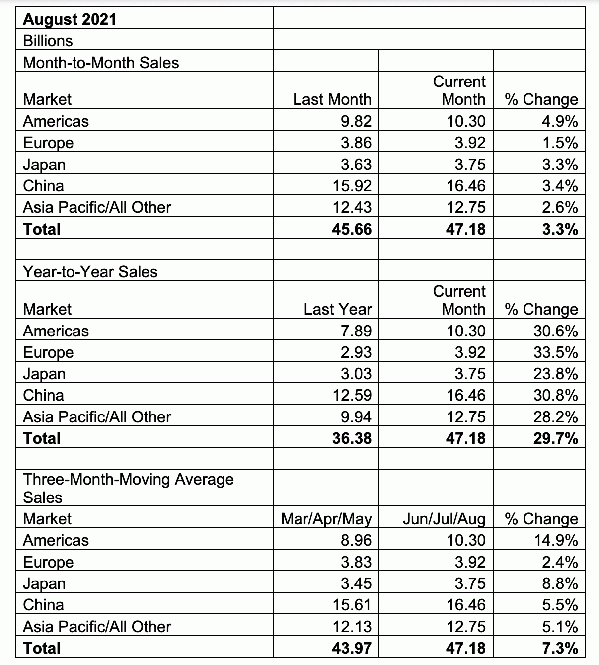

2021年10月4日、米SIA(Semiconductor Industry Association)は、2021年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年8月の世界半導体売上は、前年同月比29.7%増、前月比約3.3%増の471億8000万ドルだった。この実績は単月の売上としては過去最高。単月売上記録の更新は5ヶ月連続となる。単月売上が前年同時期を超えるのは19ヶ月連続で、2021年の売上は過去最高を記録した2018年を大きく上回る形で推移している。

2021年8月の世界半導体売上を地域別にみると、全ての地域で前年比20%を超えるプラス成長を記録。北米、欧州、中国市場は前年比30%増を超える大きな成長を示した。

日本市場も前年比23.8%増と好調を維持しており、売上を円ベースで換算すると前月比約3%増、前年比約28.2%増の約4,118億円となる。日本市場の売上が前年同月比プラス成長となるのは10か月連続。

2021.10.07

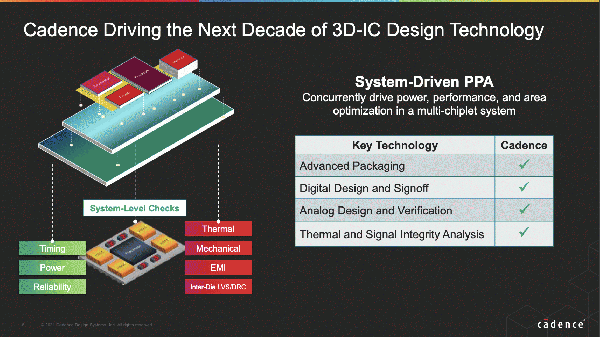

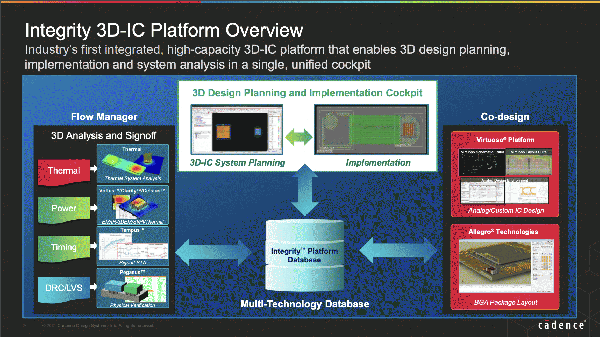

2021年10月6日、Cadenceは新製品「Integrity 3D-ICプラットフォーム」を発表した。

「Integrity 3D-ICプラットフォーム」は2.5Dおよび3Dなどマルチダイ・システムの設計と先進的なパッケージングのための統合開発環境で、「3Dデザインプランニング、インプリメンテーション、システム解析を一元化し共通のコックピット上に統合」というのがCadenceが強調する謳い文句となっている。

3Dデザインプランニング機能としては、ダイを単なる箱としてではなくダイのレイアウト(クリティカル・パス)を考慮した上でGUIで視覚的に積層のプランニング行うことが可能。このプランニングの段階でシステムレベルの各種解析が可能な点が3DIC設計統合環境ならではの「Integrity 3D-ICプラットフォーム」の大きな強みだ。

システム解析としては、ダイを重ね合わせた場合の解析、パッケージングを考慮した解析などプランニングされた動作条件に応じた、熱、パワー、タイミングの解析が可能。それら解析は「Integrity 3D-ICプラットフォーム」のデータベースを介してCadenceの各ツール(Voltus, Clarity, Celsius, Tempusなど)が実行する。サードパーティー・ツールとの連携ではなく、熱解析やパワー解析も自前のツールで統合的に対応できる点も強みだとCadenceは強調している。

インプリメンテーション機能としては、先端ノード設計で実績を重ねているデジタル設計環境「Innovus」を軸にアナログ設計環境「Virtuoso」、パッケージ設計環境「Allegro」を用いた協調設計が可能。これらツール間の連携も「Integrity 3D-ICプラットフォーム」のデータベースを介して行われる形となる。

このように新製品「Integrity 3D-ICプラットフォーム」は、Cadenceの最新の主要ツールをまとめあげることで3DIC設計に対応するソリューションで、2Dデザインの3D化や3DデザインのPPA最適化に大きく貢献することが可能。Cadenceが本格的な3DIC時代の到来に向けて放つ目玉ツールの一つと言っても過言ではないだろう。

なお発表には「Integrity 3D-ICプラットフォーム」の先行ユーザー数社がコメントを寄せているが、昨今は先端プロセスに限らず40nmプロセスを使って3DICを開発するような事例もあるなど、製造技術の進化に伴い日本国内においても3DICの開発に取り組む企業が増えているという話だ。

2021.10.06

2021年10月5日、RISC-Vプロセッサを手掛けるIPベンダBluespecは、新製品「MCU RISC-V processor family」を発表した。

Bluespecの新製品「MCUファミリ」はXilinxのFPGAでの実装をターゲットとした超小型のRISC-VプロセッサでLUT数2,000以下で実装可能。制御ロジックを含むアプリケーションを実装する際に同プロセッサを利用すればFPGA上のリソースを節約できる。Bluespecは同プロセッサの無償評価版を提供中。「MCUファミリ」には、Artix-7 搭載のFPGA開発ボード「Digilent Arty」用のオープンソース・ツールチェーンとリファレンス・デザインが含まれている。

BluespecはFPGAユーザーを対象にRISC-Vプロセッサの普及を狙っており、「MCUファミリ」を含めて計3種類のRISC-Vプロセッサ・ファミリを提供している。

2021.10.03

2021年10月1日、セミナー・イベント「Design Solution Forum 2021」の参加登録がスタートしました。

今年のDSF2021は初の完全オンライン開催で11/4, 11/5, の2日間に渡って開催します。

講演トラックは未来を創る技術を語るHot-Techトラック、すぐに活用できる技術を語るCool-Techトラック、特別企画を中心とした特別トラックの3本柱。

基調講演には日本シノプシスの藤井社長、アーキテクトグランドデザイン株式会社チーフアーキテクトの豊崎氏をお迎えして、半導体開発とスマートシティの未来についてご講演頂きます。

2日間で計45セッションを実施する今年のDSF2021は、例年以上にバラエティに富んだ内容構成となりました。DSF実行委員による特別企画も多数予定されています。

是非この機会にセミナー・イベントDSF2021に参加頂き、エンジニア同士の技術交流と合わせてエレクトロニクス業界の今を感じて頂ければと思います。

2021.09.24

2021年9月22日、AIチップベンチャーの米Syntiantは新製品「Syntiant NDP200 Neural Decision Processor」を発表した。

SyntiantのAIプロセッサは常時オンのバッテリー駆動デバイスをターゲットにした超低消費電力の推論プロセッサで、既に出荷している「NDP100」シリーズ製品は累計出荷数100万個を超えている。

今回発表した「NDP200」は、プログラム可能なCadenceの「Tensilica HiFi 3 DSP」を搭載しており、推論を用いたビジョン処理に加えて従来の画像処理や音声処理、センサー・フュージョンなど複数のアプリケーションを同時実行可能。高精度な推論によるビジョン処理を1mW未満の消費電力で実行できるとしている。また「NDP200」のテンソル・スループットは「NDP100」の25倍ということで推論パフォーマンスも引き上げられている。

SyntiantのAIプロセッサは、メモリとMAC機能を組み合わせることでデータの移動を最小限に抑えることで電力効率とパフォーマンスを向上させており、市場のMCUやDSPソリューションの約半分のダイサイズで約100倍の電力効率と10倍のスループットを提供できるとしている。

例えばArm A53プロセッサを使用したバッテリ駆動のデバイスでは3日半しか連続実行できないアプリケーションを「NDP200」で動かすと1年間連続実行できるという。

2021.09.24

2021年9月22日、IC Insightsの記事:

半導体業界専門の調査会社IC Insightsは、2021年の半導体ファウンドリの総売上を1,072億ドルと予測している。1,000億ドルを超えるのは史上初。成長率にすると前年比23%増となり、これは2017年の記録的な成長率に匹敵する。(2017年はSamsungが内製LSIをファウンドリ売上として計上し始めた年)

ファウンドリの総売上は2025年まで平均成長率11.6%ので増加し続け、2025年に1,512億ドルに達すると予想されている。

今年のファウンドリ総売上の内訳は、TSMCなど専業ファウンドリの売上が前年比24%増の871億ドル。Samsung/IntelなどIDMによる売上が前年比18%増の201億ドル。

IC Insightsの予測では、IDMによるファウンドリ売上は2025年に261億ドルに到達。平均成長率は9.0%となっている。

2021.09.15

2021年9月13日、CadenceはTensilicaシリーズIPの新製品「Tensilica AI Platform」を発表した。

「Tensilica AI Platform」はAI機能を備えるSoCへの組み込み用に用意されたAI専用のIPで、下記3種類の製品ファミリが用意されている。

AI Base:

既存のTensilica DSP向けに用意されるAI処理用の拡張ISA(命令セット)

AI Boost:

新型のコンパニオンAI neural network engine (NNE)

演算性能64から256GOPSまでスケーラブルに対応、推論あたりの消費電力を80%削減し、スタンドアローンTensilica DSPと比較して4倍以上のTOPS/Wを実現

最初の製品として「Tensilica NNE 110」を用意する

AI Max:

AI BaseとAI Boostを組み合わせたアクセラレーターで「Tensilica NNA」と呼ぶ

Tensilica NNA 110、NNA 120、NNA 140、NNA 180マルチコア・アクセラレーターオプションを提供

マルチコアNNAアクセラレーターは最大で32TOPSまで拡張可能、将来的に数百TOPSに対応するスケーラビリティをターゲットとしている

※画像はCadence社HP上のデータ

これら全てのNNEおよびNNA対応製品には、パフォーマンスを向上するためのランダムスパース演算、メモリーの帯域幅を減らすためのランタイムテンソル圧縮、モデルのサイズを縮小するためのプルーニングとクラスタリング機能が含まれている。

あらゆるSoCにAI機能が実装されるようになった今日のSoC開発を加速するために用意されたのが「Tensilica AI Platform」であり、Cadenceは長年のTensilica IPの実績をベースに様々なアプリケーションへの展開を狙っている。

「Tensilica AI Platform」の提供は今年Q4から開始の予定。発表にはGoogle, Kneron, NXPらがコメントを寄せている。

2021.09.14

2021年11月4日、5日の2日間、技術者のための技術者による技術セミナー「Design Solution Forum 2021」がオンライン・イベントとして開催されます。

今年のDSF2021は初のフルオンライン・イベントになりますが、前回のDSF2020同様ライブ配信に拘り、計40以上の様々な講演と併せてどなたでも参加頂ける特別企画の実施を計画しています。

特別企画では参加頂いた方に副賞も用意していますので、講演の聴講者としてだけではなく、DSF2021での発信者として是非セミナーにご参加下さい。

特別企画の参加者は以下の通り9/30まで募集しております。

「リモート環境の自慢大会」

エンジニアのリモート環境の自慢大会をオンラインで開催します。

優勝者には賞品を贈呈しますので、我こそはと言う方はぜひ応募してください。

「Myガジェット自慢大会」

自慢のガジェット、みんなに教えたいガジェットのリモート展示企画です。

優勝者には賞品を贈呈しますので、苦労して手に入れたこだわりの愛用品などを教えてください。

「みんなに教えたい!ウチの会社の面白いトコ・すごいトコ・変なトコ」(参加企業募集)

面白い会社、すごい職場、変なところをリモートで紹介してください。

地方の企業も大歓迎ですし、「会社紹介から採用につながったらいいな・・・」といった下心も大歓迎です。

「Design Solution Forum 2021」は、10月上旬より参加登録開始の予定です。

2021.09.14

2021年9月13日、Synopsysは新製品「PrimeSim Reliability Analysis」を発表した。

「PrimeSim Reliability Analysis」は、大手半導体ファウンドリの認証を取得している信頼性解析のサインオフツールで、マシン・ラーニング機能を併用し信頼性解析に伴う以下の各処理を高速に実行できる。

・高シグマ値のリーフセル・キャラクタライゼーション

・スタティック回路チェック

・パワー/シグナル・インテグリティ解析

・EM/IRドロップのサインオフ解析

・MOS経年劣化解析

・アナログ・フォルト・シミュレーションによる機能安全性/テストカバレッジ解析

「PrimeSim Reliability Analysis」を使うべき理由として大きく謳われているのは、製品ライフサイクルの初期段階、通常稼働段階、終期段階で起こりうるシナリオや機能安全など各種規格に準拠した総合的な信頼性検証を実行できるという点。これによりSoCの過剰設計やコスト増加要因となる開発後期段階でのECOを防止するだけでなく、SoCの機能安全、信頼性、全体性能を改善することができるという。

「PrimeSim Reliability Analysis」は、車載、航空宇宙、防衛、医療、5GなどミッションクリティカルなSoCの開発に向けて用意されたソリューションで、既に半導体大手各社が採用している。

※画像はSynopsys提供のデータ

2021.09.09

2021年9月8日、QuickLogicはeFPGA IPのジェネレーター「Australis」のリリースを発表した。

「Australis」はQuickLogicが提供するeFPGA IPをカスタマイズして実装するためのIPジェネレーターで、「Open Source FPGA Foundation」の提供する「OpenFPGA IPジェネレーター」をベースとしている。同ジェネレーターを利用することで、カスタマイズされたeFPGA IPを数日でGDSII形式まで落とし込むことが可能になるという。

「Open Source FPGA Foundation」はオープンソースのFPGA設計ツールとIPブロックの普及推進を目的に組織された団体で、QuickLogicも創立メンバーとして参画している。QuickLogicはオープンソース・ソフトおよびツールに積極的に投資しており、自社のソリューションに積極的にオープンソースを取り込んでいる。

2021.09.09

2021年9月8日、CadenceはSamsungと共同開発したMixed-Signal OpenAccess PDKの提供を発表した。

今回提供が発表されたMixed-Signal OpenAccess PDKは、Samsungの28nm FD-SOIプロセスがら最新のGAAベース 3nmプロセスまでサポートしているという。

2021.09.07

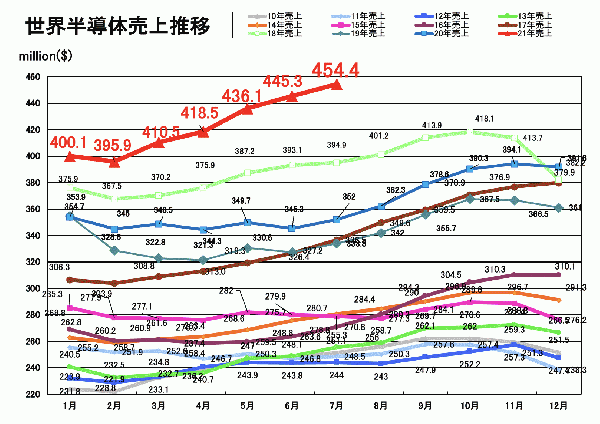

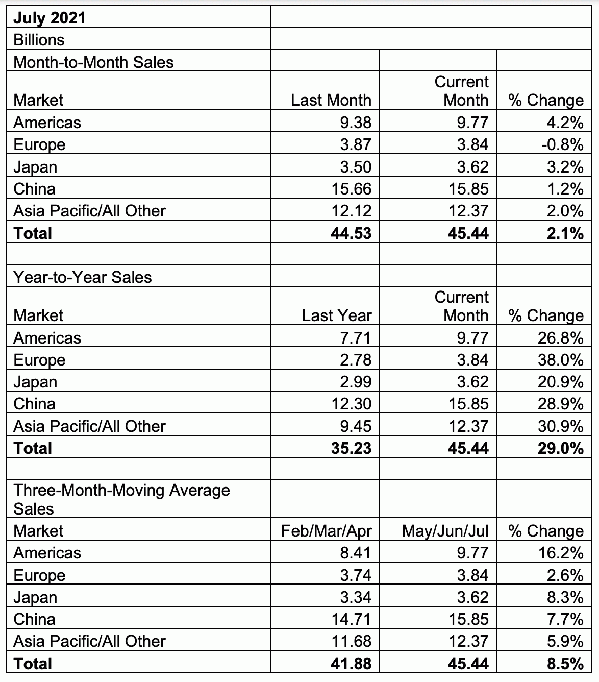

2021年9月3日、米SIA(Semiconductor Industry Association)は、2021年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年7月の世界半導体売上は、前年同月比約29%増、前月比約2.1%増の454億4000万ドルだった。この実績は単月の売上としては過去最高で4月に続いて4ヶ月連続で記録を更新。単月売上が前年同時期を超えるのは18ヶ月連続で、2021年の売上は過去最高を記録した2018年を上回る勢いを維持している。

2021年7月の世界半導体売上を地域別にみると、全ての地域で前年比20%を超えるプラス成長を記録。6月に続いてかつてない活況にあり、欧州は前年比38%増、アジアその他地域は前年比30%増を超える大きな成長を示した。

日本市場も前年比20.9%増と好調を維持しており、売上を円ベースで換算すると前月比約3.5%増、前年比約25%増の約3,988億円となる。日本市場の売上が前年同月比プラス成長となるのは9か月連続。

2021.09.03

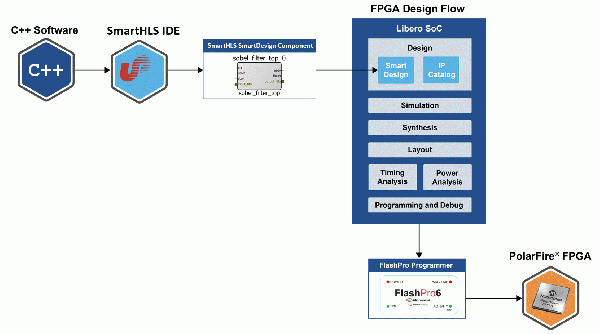

2021年9月2日、Microchipは提供するFPGA「PolarFire FPGA」向けの設計ツール「SmartHLS」のリリースを発表した。

「SmartHLS」はC++コードからRTLを自動生成する高位合成ツールで、「PolarFire FPGA」およびRISC-Vプロセッサを搭載する「PolarFire SoC」の開発に利用できる。

Microchipによると「SmartHLS」はオープンソースのEclipseベースのツールで、複数のハードウェア命令を同時に実行して複雑なハードウェア並列処理を単純化するマルチスレッドAPIで他のHLSツールよりも迅速な開発が可能。Microchipの提供する「VectorBlox™ニューラル ネットワーク ソフトウェア開発キット」を使うと、FPGA ベースのハードウェア・アクセラレータを効率的に開発できるという。

「SmartHLS」は「PolarFire FPGA」向けの設計スイート「Libero SoC」の一部であるが、独立したツールとしても利用可能。Microchipのウェブサイトで入手できる。

2021.09.02

2021年9月1日、高性能RISC-Vプロセッサを手掛ける米Ventana Micro Systemsは、資金調達Bラウンドで3800万ドルを調達した事を発表した。

発表によると今回の資金調達ラウンドは、Marvellの創始者として知られるSehat Sutardja氏とWeili Dai氏を含む半導体業界の投資家が主導。同社の累計調達額は5300万ドルとなった。

Ventana Micro Systemsはデータセンタークラスの高性能RISC-Vプロセッサを開発しているIPベンダで創業は2018年。本拠地はカリフォルニア州クパチーノ、テキサス州やインドにも拠点を持つ。CTOのGreg Favor氏は、Applied Micro、Ampere ComputingでArmベースのサーバー向けプロセッサを開発していた人物。

Ventana Micro Systemsの面白いところは、自社開発した高性能RISC-Vプロセッサとチップレット技術を組み合わせて、カスタマイズ可能なSoCチップレットとして提供している点。このアプローチにより様々なプロセスでRISC-Vプロセッサのシリコン実装が可能。一般的なIPモデルよりもSoCの開発時間とコストを大幅に削減できるという。ちなみに同社がチップレットに用いているD2Dソリューションは、OCP Open Domain-Specific Architecture(ODSA)インタフェース規格に準拠しているようだ。

2021.09.02

2021年9月1日、エッジ向け推論チップを手掛けるイスラエルのHailoはマクニカとの提携を発表した。

Hailoは昨年9月に日本法人を設立。ソシオネクストとの映像解析ソリューションの共同開発、AIアクセラレータ・モジュールの販売など、既にエッジ向け推論チップ「Hailo-8」を核としたビジネスを展開している。

今回の提携により、今後はマクニカもHailoの製品を販売することになる。

2021.08.30

2021年8月30日、Synopsysは損保ジャパンによる同社製品「Coverity」の採用事例を発表した。

「Coverity」はソフトウェアのバグやセキュリティの脆弱性などを静的に解析するソフトウェア開発向けのツールでソースコードの品質向上に活用されている。

損保ジャパンは2015年から取り組み始めた30年振りとなる自社基幹システムの全面刷新で「Coverity」を採用。同プロジェクトは最大3000人の開発者が参加する大規模なもので、「Coverity」はセキュリティ問題の回避などソースコードの品質確保の効率化に貢献した。

プロジェクトに関わった損保ジャパンの子会社、SOMPOシステムイノベーションズの検証では、「Coverity」の誤検知率は他社製品比で約半分、セキュリティ問題を含む重大な不具合の検出率は1.6倍高かったという。

損保ジャパンが再構築した基幹システムは既に稼働を開始しており、同社では今後システムの保守において「Coverity」を活用していく計画。

2021.08.20

2021年8月18日、Synopsysは、2021会計年度第3四半期(21年5-7月)の四半期決算を報告した。

発表によるとSynopsysの2021会計年度Q3の売上は、前年同時期比約9.6%増、前Q2比約3.2%増の10億5710万ドルで四半期売上として過去最高を記録した。なおQ3の営業利益は前年比約21%減の1億9860万ドルだった。(※GAAP基準による会計結果)この実績はQ2実績報告時の予測値10億300万-600万ドルを上回るものとなる。

Synopsysは、来期Q4(8-10月)の売上を11億3800万-6800万ドル、2021会計年度の売上を41億9000万-42億2000万ドルと予測を上方修正している。

2021.08.17

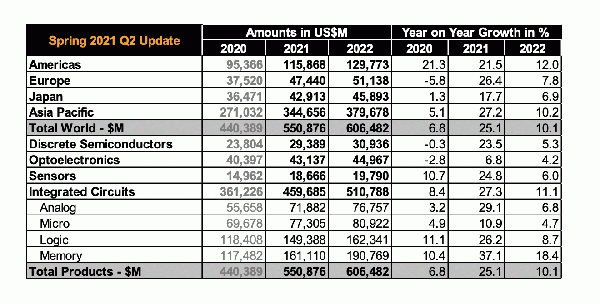

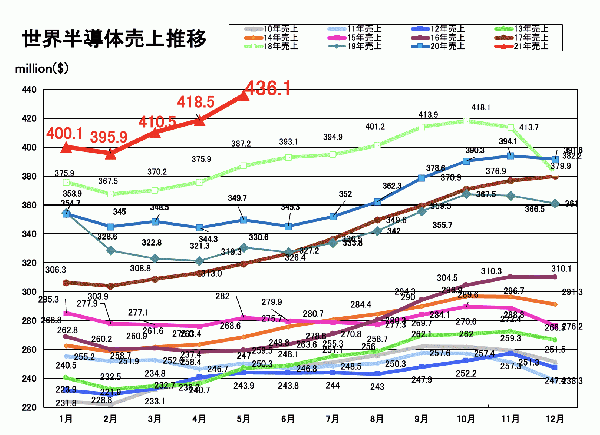

2021年8月16日、WSTSは、2021年第2四半期の半導体市場の売上額を公開し、それをベースに今年の市場予測をアップデートした。

※画像はWSTS Web上のデータ

WSTSの発表によると、今年の世界半導体市場は前年比25.1%増の5,510億ドルに到達する見込みで、当初予測の前年比19.7%増を上回る見通し。

主要な製品カテゴリ全てが成長する見通しで、メモリ37.1%、アナログ29.1%、ロジック26.2%と予測されている。

地域別では、アジア太平洋地域27.2%、ヨーロッパ26.4%、南北アメリカ21.5%、日本17.7%と全ての地域で2桁成長を達成する見込み。

2022年は更なる成長が予想されており、前年比10.1%増の6,060億ドルに達する見通し。

2021.08.05

2021年8月2日、米SIA(Semiconductor Industry Association)は、2021年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年6月の世界半導体売上は、前年同月比約29.2%増、前月比約2.1%増の445億3000万ドルだった。この実績は単月の売上としては過去最高で4月に続いて3ヶ月連続で記録を更新。単月売上が前年同時期を超えるのは17ヶ月連続で、2021年の売上は過去最高を記録した2018年を上回る勢いを維持している。

2021年6月の世界半導体売上を地域別にみると、全ての地域で前年比20%を超えるプラス成長を記録。5月に続いてかつてない活況にあり、欧州は前年比40%、アジアその他地域は前年比30%を超える大きな成長を示した。

日本市場も前年比21.2%増と好調を維持しており、売上を円ベースで換算すると前月比約5.3%増、前年比約24%増の約3,853億円となる。日本市場の売上が前年同月比プラス成長となるのは8か月連続。

2021.08.02

2021年7月26日、Cadenceは、2021会計年度第2四半期(2021年4-6月)の売上を報告した。

Cadenceの2021年Q2売上は、前年比約14.1%増、前期Q1比約1.1%減の7億2800万ドル、営業利益は前年比約19%増の1億5600万ドルだった。(※GAAP基準による会計結果)

このQ2実績は同社のQ2売上記録として過去最高。Cadenceは2020年Q4から3四半期連続で売上7億ドル超を維持している。

CadenceはこのQ2に以下のような新製品およびニュースを発表している。

Cadenceは2021年Q3の売上を7億3000万-5000万ドルと予測。2021年の年間売上予測を29億2500-29億6500万ドル程度と上方修正している。

2021.07.27

2021年7月26日、Cadenceは新製品「Cerebrus™ Intelligent Chip Explorer」を発表した。

発表によると新製品「Cerebrus」は、デジタル設計フローの革新を狙うマシンラーニング・ベースの新製品で、AI機能を用いることで高度に設計を効率化。合わせて設計品質を大幅に向上することができる。Cadenceの説明によると「Cerebrus」を利用することで、従来手法と比較して設計生産性を最大10倍も向上することが可能。PPAを最大20%も改善することができるという。

「Cerebrus」は独立した製品というよりは、オプション機能のようにツールの処理を補助するような役割を果たすツールで、Cadenceのデジタル設計フローの基幹をなす論理合成ツール「Genus」、配置配線ツール「Innovus」、タイミング解析ツール「Tempus」、それぞれと組み合わせて使うことが可能。またこれらツールによる一連の処理に対して利用することもできる。

具体的には、これまで設計者が独自の知見で対応していた様々な回路のチューニング作業を「Cerebrus」で自動化することが可能。ツールのオプション変更やタイミング制約などの設計制約の変更、フロアプラン形状の変更やライブラリのチューニングなど、目標とするPPAに向けて回路を繰り返し最適化する作業に「Cerebrus」を当てはめることが可能で、極端な話、熟練の設計者が時間をかけて得る最適解を一般の設計者でもプッシュボタン式に得られるようになる。そのAI機能についての詳細は不明だが、性能、面積、電力とそれぞれに目標性能を設定し、それに見合った人間では長時間を要さなければ見つけられないような解を「Cerebrus」はすぐに見つけてくれるということだ。

Cadenceが示した5nmモバイルCPUの設計例では、複数エンジニアが数ヶ月かけて実装した設計結果よりも、設計者一人で「Cerebrus」を用いて設計した結果の方が優れており、要した設計期間は10日以内だった。また別のCPU設計例では、フロアプランニングに対して「Cerebrus」を適用したところ、当初の目標性能を上回る結果を得られたという。他にも既にルネサスやSamsungなど大手先行ユーザーが「Cerebrus」を利用して成果を上げているということで、その成果についてコメントを寄せている。

※画像はCadence提供のデータ

Cadenceはシステム分野へのソリューション拡張と合わせて、AI/マシンラーニング技術の取り込みにも積極的に力を注いでおり、今回発表した「Cerebrus」は大型の新ソリューションとなる。今後EDAの世界でもAI/マシンラーニングによる技術革新が益々進むと思われ、それによる設計の進化が楽しみな時代になってきた。

2021.07.16

2021年7月14日、米ESD Allianceは、2021年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2021年Q1(1-3月)の世界のEDA売上総額は前年比約17%増、前Q4比約4.1%増の31億5717万ドルで、四半期売上として過去最高記録を更新した。売上記録の更新は前Q4に続いて4四半期連続。四半期売上が前年実績を上回るのは9四半期連続で前年比で15%を超えたのは2011年以来5回目となる。

2021年Q1のEDA売上をカテゴリ別に見ると、IC Physical Design & Verification分野が前年比34.4%増と大きく伸びた。IP分野は四半期として過去最高となる売上を記録した。

2021年Q1のEDA売上を地域別に見ると、日本市場以外は全て前年比でプラス成長。アジア・パシフィックが対前年比の成長率26.9%でトップ。最大市場の北米も15%増と好調を継続した。欧州・中東・アフリカ市場も2桁成長率を達成している。

2021年Q1時点でのEDA業界の従業員数は前年比6.7%増の49,024人でQ4よりも約3.2%増加した。

2021年Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 9億57410万ドル 14%Up

■IC Physical Design & Verification分野 6億8250万ドル 34.4%Up

■IP分野 11億1300万ドル 12.9%Up

■サービス分野 9890万ドル 0.1%Up

■PCB/MCM分野 2億8920万ドル 15.3%Up

ESDA2020Q4Cat.png

2021年Q1の地域別の売上と昨年同時期との比較は以下の通り。

■北米 12億8530万ドル 15%Up

■欧州・中東・アフリカ 4億4730万ドル 14%Up

■日本 2億5880万ドル 3.7%Down

■アジアその他地域 11億6630万ドル 26.9%Up

2021.07.13

2021年7月13日、デンソー子会社のIPベンダNSITEXEは、同社の開発したDFP(Data Flow Processor)「DR1000C」がISO 26262 ASIL D Ready認証を取得したことを発表した。

NSITEXEによると、RISC-V Vector Extensionを実装したプロセッサとして、ISO 26262 ASIL D Readyの認証を受けるのは、同社の「DR1000C」が世界初だという。

NSITEXEの開発するDFP(Data Flow Processor)は、世界初の車載向けRISC-Vベースプロセッサであり、RISC-VベースプロセッサとしてISO 26262 ASIL D の認証を受けたのも世界初だった。今回の認証により同社のDFPは3回目の世界初を実現したことになる。

今回ASIL D認証を受けた「DR1000C」は、モデル予測制御、AI推論、センサー処理など、セーフティクリティカル・システムをターゲットとした車両制御マイコンの高負荷演算処理をオフロードするのに最適なプロセッサIPで、最大16個のハードウエア・スレッドがベクトル・プロセッサを効率的に使用することで非常に高い電力性能を実現。以下のようなハードウエア・ランダム故障を検出する機能が統合されているため、外部に特殊な安全機構を追加せずにASIL Dの安全要求を達成可能だという。

・メモリの誤り訂正コード(ECC)

・プロセッサ部のデュアルコアロックステップ機構

・バスのプロトコル診断機能

・エラーマネジメントユニット:自己診断用のエラー注入及び各エラーのホストへのレポートやステータスを管理

また「DR1000C」のベクトルプロセッサ部は、ロックステップ診断とソフトウエア診断を切り替えて使用できるため、実行するアプリケーションの性能要求と求められる安全基準によって様々なユースケースに対応可能。「DR1000C」用のSDK(Software Development Kit)およびHSK(Hardware Safety Kit)を利用することで、ユーザーはアプリケーション開発の効率化、認証取得の期間短縮といったメリットも享受できる。

なおNSITEXEは「DR1000C」を車載制御専用プロセッサとしている訳ではなく、FA等の産業機器、RADAR等のセンサー処理など、様々な組込み領域のアプリケーションへ応用可能だとしている。

2021.07.07

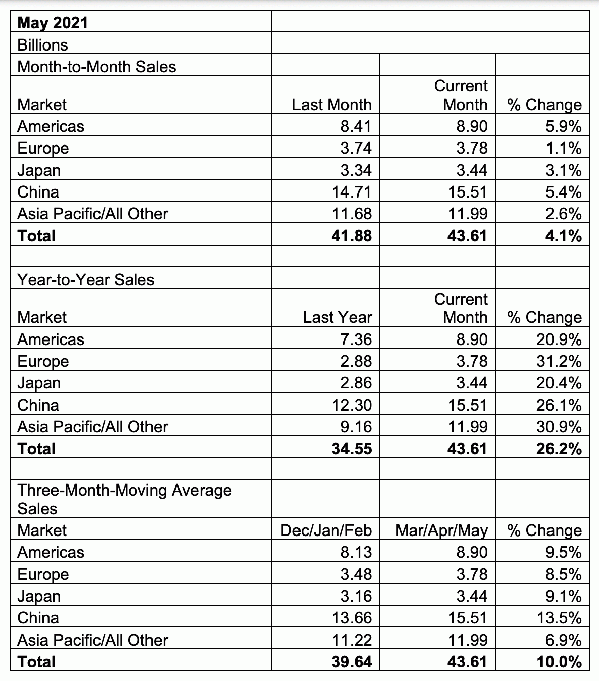

2021年7月6日、米SIA(Semiconductor Industry Association)は、2021年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年5月の世界半導体売上は、前年同月比約26.2%増、前月比約4.1%増の436億1000万ドルだった。この実績は単月の売上としては過去最高。単月売上が前年同時期を超えるのは16ヶ月連続で、2021年の売上は過去最高を記録した2018年を上回る勢いを維持している。

2021年5月の世界半導体売上を地域別にみると、全ての地域で前年比20%を超えるプラス成長を記録。ここまでの活況は過去を振り返っても無い。欧州およびアジアその他地域にいたっては、前年比30%を超える大きな成長を示している。

日本市場も前年比20.4%増と好調を維持しており、売上を円ベースで換算すると前月比約2.6%増、前年比約22.3%増の約3,656億円となる。日本市場の売上が前年同月比プラス成長となるのは7か月連続。

2021.07.05

2021年7月2日、図研は新製品「GENESYS-CR」の発売を発表した。

「GENESYS-CR」は、図研が2019年に買収したMBSEツールベンダ「Vitech」のツール「GENESYS」をベースに開発されたMBSEツールで、エレキ設計における要求と設計のトレーサビリティの最適化を実現するもの。

図研はMBSE(Model Based Systems Engineering)への取り組みを明確に打ち出し、数年前からMBSEによるシステム設計手法と自社のエレキ設計環境を繋ぐためのソリューションを提供し始めている。

今回発表された「GENESYS-CR」は、図研のMBSEモデリングツール「GENESYS」と回路設計ツール「CR-8000 Design Gateway」をつなぐもので、「GENESYS」を用いて作成した要求-機能-検証モデルと「Design Gateway」で設計した回路を対応させ、要求とその設計(回路)のトレースを実現。これにより回路に対する要求や課題の参照、設計変更の影響範囲の確認などが可能となる。

「GENESYS-CR」はあらかじめエレキ設計に特化した要求のカテゴリや検証定義のテンプレートが用意されており、MBSEに精通していないエレキ設計者でも容易にモデリングが可能。Excelでまとめられた既存の設計データをインポートしたり、様々なドキュメント形式で作成したモデルをエクスポートすることができる。

図研はMBSEによる設計上流工程での要求分析や仕様検討が大規模・複雑化するエレキ設計に有効であると考えており、今回発売した「GENESYS-CR」を活用し、ドキュメントベースの開発をモデルベースに切り替えることで、設計の効率化、品質向上だけでなく、製品開発における知見の構築、設計ノウハウの資産化も可能になるとしている。

EDA Expressではオンライン・インタビュー企画の第四弾として、図研からゲストを招いて「MBSEの日本の実情」についてインタビューを行う予定。

https://www.eda-express.com/2021/07/zoom-mbse.html

2021.07.01

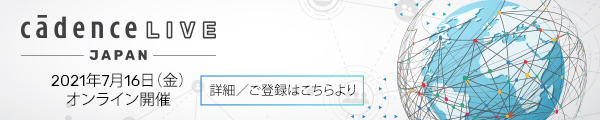

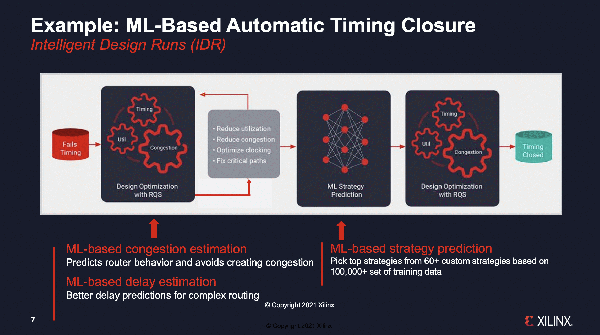

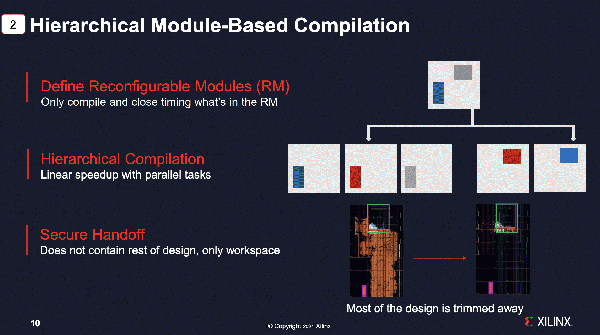

2021年6月23日、Xilinxは同社の提供するFPGA設計環境「Vivado」に機械学習による最適化機能を実装した「Vivado® ML Edition」のリリースを発表した。

Xilinxによると「Vivado ML Edition」には、「Intelligent Design Runs (IDR)」と呼ぶ機械学習ベースの自動タイミング収束機能が用意されており、機械学習を用いて配線における混雑予測や遅延予測を行い、最適な戦略を導き出しタイミングを収束させることが可能。これによりタイミング収束のためのイタレーション作業が不要となり、現行の「Vivado HLx Edition」と比較してQoR(結果の品質)を最大50%、平均10%向上できる。同機能はプッシュボタン式に実行可能で複雑なデザインにおいて特に効果を発揮するという。

また、抽象化シェルというコンセプトの導入により、システム内の複数のモジュールを定義し、インクリメンタルかつ並列にコンパイル可能に。これにより、従来のフルシステムのコンパイルと比較してコンパイル時間を平均5分の1、最大17分の1に短縮できる。抽象化シェルはモジュールを除くデザインの詳細を隠蔽するため、IPの保護にも役立つ。

更に「Block Design Containers」と呼ぶIPのインテグレーター機能により、モジュラーベースのグラフィカルなデザインが可能で、デザインの再利用やチームによる協調設計が容易になるほか、「Dynamic Function eXchange」と呼ぶ機能を使うことで、OTAで数ミリ秒でデザイン・モジュールを読み込み、実行する機能を動的に切り替えるということができるという。

「Vivado ML Edition」は、無償の「Standard Edition」と有償の「Enterprise Edition」があり、無償版はサポートするデバイスが限定される。有償版はノードロック・ライセンスが2,995ドル、フローティング・ライセンスが3,595ドルとなっている。

※画像は全てXilinx社Web上のデータ

2021.07.01

ハードウェア設計関連の様々なテーマについて、ゲストを招待してオンライン(Zoom)で色々な話をライブで聴くという企画です。

新企画「オンライン・インタビュー」は、特定のテーマについてゲストに話を聞くだけでなく、聴講者の方々も含めた参加者全員が情報交換や意見交換できるよう、少人数制のミーティング形式で開催します。

顔出しは自由、発言、チャットは基本的に制限無し。オープンな形でありながら、クローズドなライブ・イベントとして開催しますので、情報収集の場、業界関係者とのコミュニケーションの場としてご利用下さい。

オンライン・インタビュー企画の第四弾は、「MBSEについて日本の実情を聞いてみる」と題して、株式会社図研様よりゲストを招いて開催します。

モデルベース・システムズエンジニアリング(MBSE)について知る良い機会です。

MBSEにご興味ある方は是非お気軽にお申し込み下さい。

EDA Express オンライン・インタビュー 第4回

テーマ :MBSEについて日本の実情を聞いてみる

ゲスト :株式会社図研 事業本部 PI推進部 部長 稲石 浩通氏、

同グループリーダー 阿部 稔氏

開催日時 :7月28日(水)16:00-17:00 ※途中入退出可能

参加 :無料、最大20名の参加者を想定しています

インタビュー構成:

・稲石様/阿部様のプロフィールについて(職歴、趣味など)

・MBSEとは?

-基本的な考え方、MBSEの利点

-メソドロジー、ツール

-世の中のトレンド

・MBSEのススメ

−導入メリット、期待される効果

-国内活用事例

・MBSEあるある

-よくある誤解、犯しがちなミス

-よくある相談、現場の課題

−導入する上での注意点

・参加者からの質問

インタビュアーはEDA Express 菰田が担当。インタビュー終了後は雑談タイムとします。

※オンライン・インタビューに関するご質問等は

こちら までお願いします。

2021.06.23

2021年6月22日、RISC-Vプロセッサを手掛けるSiFiveは、RISC-Vコアの新製品「Performanceファミリ」を発表した。

「Performanceファミリ」として発表されたRISC-Vコアは「P270」と「P550」の2品種。

「P270」は、RISC-Vベクトル拡張v1.0を完全にサポートするSiFive初のLinux対応プロセッサで、RISC-V RV64GCV ISA互換、8ステージ、デュアルイシュー、高効率のインオーダー・パイプラインを備える。SiFiveは「P270」を「古いSIMDアーキテクチャの理想的な代替品」と謳う。(SiFiveは既存のSIMDソフトウェアを一般的なレガシー・アーキテクチャからRISC-V Vectorアセンブリコードに変換するSiFive Recodeを提供している。)

もう一つの「P550」は、「SiFiveU84」を改良したSiFiveのRISC-Vプロセッサとして最高のパフォーマンスを誇るプロセッサで、SiFiveは現在市場に流通しているRISC-Vプロセッサの中で最速と自負する。SiFiveによると「P550」は、SPECInt2006のスコアで8.65/GHzを達成。Arm Cortex-75と同等の面積でArm Cortex-75を上回るパフォーマンスを提供する。アーキテクチャはRISC-V RV64GC ISA互換、13ステージ、トリプルイシュー、アウトオブオーダー・パイプラインを備えている。

なお先頃SiFiveを買収する可能性が報じられた開発パートナーのIntelは、SiFiveの「P550」を用いたプロセッサ「HorseCreek」を自社の7nmプロセスで製造することを明らかにしている。

SiFiveの社長兼CEO Patrick Little氏は今回の発表について、「SiFiveとRISC-Vムーブメントの両方に新しい時代の到来を告げるものであり、RISC-Vが従来の32ビット・アーキテクチャのコストダウンした代替品にのみ適していた時代は過ぎ去った。」とコメントしている。

https://www.sifive.com/blog/the-heart-of-sifive-is-performance-intelligence-

2021.06.22

2021年6月21日、SoC組み込み型のFPGAコアを手掛けるFlexLogix Technologiesは、Socionextとのライセンス契約を発表した。

FlexLogixによると、Socionextは大手通信会社の5Gワイヤレス基地局プラットフォーム向けの7nm ASIC開発でFlexLogixの組み込み型FPGA「EFLEX」を採用。

「EFLEX」を活用することで再プログラム可能なASICを実現し、従来別のFPGAで対応していたキャリアの要求に応じたプロトコル変更などのアップデートにASIC単体で対応できるようになった。FPGAを一つを無くしたことで基地局のパフォーマンス向上と電力削減というメリットも得られたという。

2021.06.21

2021年6月18日、Cadenceは新型のDSP「Tensilica FloatingPoint DSP」を発表した。

新製品「Tensilica FloatingPoint DSP」は、その名の通り浮動小数点型の演算処理に特化して設計されたIPコアで、Tensilica FloatingPoint KP1、KP6、KQ7、KQ8と4種類の製品ラインナップがある。KP1およびKP6は低消費電力性能重視、KQ7およびKQ8はパフォーマンス重視のDSPとなる。

Cadenceによると、「Tensilica FloatingPoint DSP」は、既存のTensilica DSPと共通の命令セットアーキテクチャで既存のTensilica DSPがサポートするベクトル浮動小数点ユニット (VFPU) を共有しているため、他のTensilica DSPからの移植が容易であり浮動小数点演算処理を容易にオフロードできる。

「Tensilica FloatingPoint DSP」の4製品がサポートするプラットフォーム、SIMDビット幅、ALU、浮動小数点型は下記図の通り。

Cadenceの説明では「Tensilica FloatingPoint DSP」は、VFPUを備えたTensilicaの固定小数点型DSPと比較して融合積和 (FMA) 演算性能を25%向上。また、同等クラスのVFPUを備えた固定小数点型DSPと比較して、最大で40%のエリア縮小を実現するという。

なお「Tensilica FloatingPoint DSP」のソフトウェア環境としては、最小限の労力でスカラーコードがVFPUを活用するよう自動ベクトル化および最適化を行う機能や、Eigen、NatureDSP、SLAM、数値演算用の各種ソフトウェアライブラリ、既存の浮動小数点共通ソフトウェアスタックから「Tensilica FloatingPoint DSP」への移行や「Tensilica FloatingPoint DSP」ファミリ製品間でのシームレスな移行を可能にする環境が用意される。

2021.06.18

2021年6月16日、RambusはIPベンダPLDA社およびAnalogX社の買収を発表した。

PLDAはPCI Expressを中心にCXL,CCIXなどインタフェースIPに注力するIPベンダで、ワールドワイドで6,000以上のライセンス実績を持つ。Rambusは今回の買収によりPLDAの提供するCXL 2.0、PCIe 5.0、PCIe 6.0コントローラーおよびスイッチIPを手に入れ、データセンター向けのインタフェースIPソリューションの拡充に期待を寄せている。

AnalogXは元IntelのSerDes開発者らが創業したカナダのIPベンチャーで、低電力のマルチプロトコル・インタフェースIPやダイ間およびチップ間のインターコネクトIPなどを手掛けている。Rambusは今回の買収によりAnalogXのSerDes技術を取り込み、自社のインタフェースIPの強化に繋げる狙い。

なお今回発表された両社の買収は今年第3四半期に完了する予定。

2021.06.17

2021年6月16日、IC Insightsの記事:

IC Insightsは2021年の世界半導体市場の成長率を前年比19%増から24%増に上方修正した。

メモリ、ロジック、アナログICいずれも見通しが好調で、メモリ市場を除いても今年の半導体市場は前年比21%増の成長が見込まれる。

ちなみにWSTS(世界半導体市場統計)は、今年の世界半導体市場の成長率を前年比8.8%増と予測している。

アナログIC市場は前年比25%増の成長、ロジック市場は前年比24%増の成長が見込まれ、ロジック市場では産業向けや自動車、コンスーマ向けが大きく伸びる見通し。

2021.06.15

2021年5月26日、Cadenceは3D電磁界解析ソルバー「Clarity™ 3D Solver」をクラウド環境に対応させた新ソリューション「Cadence® Clarity™ 3D Solver Cloud」を発表した。

Cadenceによると「Clarity™ 3D Solver Cloud」は、Amazon Web Services (AWS)のクラウド環境で利用可能なソリューションで、3D有限要素法 (FEM) シミュレーションの対応規模を32コアから数千コアまで拡張できる環境を提供する。

「Clarity™ 3D Solver Cloud」は、ローカルコンピューター上の計算機リソースとAWSクラウド上のリソースを併用できるハイブリッド式の手法により、クラウドにシミュレーションの暗号化データのみを送信、シミュレーション結果はローカルのオンプレミス・コンピューターに戻され、AWS上のデータは即座に削除されるという形でデータの安全性を確保する。ユーザーはシンプルで使い勝手の良いプッシュボタン形式のインターフェイスを用いて、データの安全性を確保しながらクラウド上でシミュレーションを実行可能。クラウド環境を利用することでシミュレーション・ニーズに応じた演算リソースの自由な拡張が可能でEM解析のTATを大幅に削減できる。

「Clarity™ 3D Solver」は2019年に市場投入されて以降、大規模デザインへの対応能力と高速なシミュレーション性能で多くの支持を集めている。今回のクラウド対応により、「Clarity™ 3D Solver」のEM解析能力は更に強力なものになる。

2021.06.15

2021年5月26日、Cadenceは3D電磁界解析ソルバー「Clarity™ 3D Solver」をクラウド環境に対応させた新ソリューション「Cadence® Clarity™ 3D Solver Cloud」を発表した。

Cadenceによると「Clarity™ 3D Solver Cloud」は、Amazon Web Services (AWS)のクラウド環境で利用可能なソリューションで、3D有限要素法 (FEM) シミュレーションの対応規模を32コアから数千コアまで拡張できる環境を提供する。

「Clarity™ 3D Solver Cloud」は、ローカルコンピューター上の計算機リソースとAWSクラウド上のリソースを併用できるハイブリッド式の手法により、クラウドにシミュレーションの暗号化データのみを送信、シミュレーション結果はローカルのオンプレミス・コンピューターに戻され、AWS上のデータは即座に削除されるという形でデータの安全性を確保する。ユーザーはシンプルで使い勝手の良いプッシュボタン形式のインターフェイスを用いて、データの安全性を確保しながらクラウド上でシミュレーションを実行可能。クラウド環境を利用することでシミュレーション・ニーズに応じた演算リソースの自由な拡張が可能でEM解析のTATを大幅に削減できる。

「Clarity™ 3D Solver」は2019年に市場投入されて以降、大規模デザインへの対応能力と高速なシミュレーション性能で多くの支持を集めている。今回のクラウド対応により、「Clarity™ 3D Solver」のEM解析能力は更に強力なものになる。

2021.06.11

2021年6月10日、Xilinxはソフトウェア解析ツールを手掛ける独Silexicaの買収を発表した。

Silexicaはマルチコア・システム向けのソフトウェア開発ツール「SLX」を提供するツールベンダで、XilinxのパートナーとしてXilinxの高位合成フローをサポートしていた。

「SLX」はソフトウェアの構造や性能、消費電力など様々な解析機能を持つツールで、シングルコア向けのコードをマルチコア・システム向けに自動分割/マッピングしたり、高位合成向けにソフトウェアのハード化対象を解析するなど、組み込みシステムの開発で重宝されている。

今回Xilinxは、「SLX」の技術を自社の開発環境「Vitis」に統合するためにSilexicaを買収。XilinxのFPGAおよびSoC上でアプリケーションを構築するソフトウェア開発者により良い開発環境を提供するとしている。

2021.06.10

2021年6月9日、CadenceはPCBおよびシステム設計向けの新製品「Allegro® X Design Platform」を発表した。

Cadenceの説明によると新製品「Allegro® X Design Platform」は、PCBおよびシステム設計向けに論理設計/物理設計、システム解析、設計データ管理を統合した業界初のシステム設計プラットフォームで、複数の領域に跨った作業が必要となるシステム設計の生産性を高めることができる。

具体的には、2次元/3次元、シングルボード/マルチボード上で論理設計および物理設計を行うためのフレームワークを提供。以下のようなCadenceのツールと連携してシステム設計を行うことが可能だという。

・シミュレーション/解析ツール

Cadence Clarity™ 3D Solver、Celsius™ Thermal Solver、Sigrity™ technology、PSpice®

・設計データ管理ツール Allegro Pulse

・RF設計ツール AWR® Microwave Office®

また「Allegro® X Design Platform」は、オンプレミス環境だけでなくパブリックなクラウド環境でも利用可能でGPUを用いた演算の高速化も可能。Cadenceは基板のレンダリングなどインタラクティブな処理の演算パフォーマンスを最大で20倍向上させることができるとしている。

さらに、電源供給ネットワーク (PDN)設計、デバイス配置、信号相互接続において、マシンラーニング技術を応用した最適化も可能だという。

Cadenceはシステム設計分野におけるソリューションを急速に拡大しているが、今回発表された「Allegro X Design Platform」は、システム設計とPCB設計を統合する大型の新製品と言えるだろう。同製品は2021年の第4四半期に一般向け販売を開始する予定とのこと。

2021.06.10

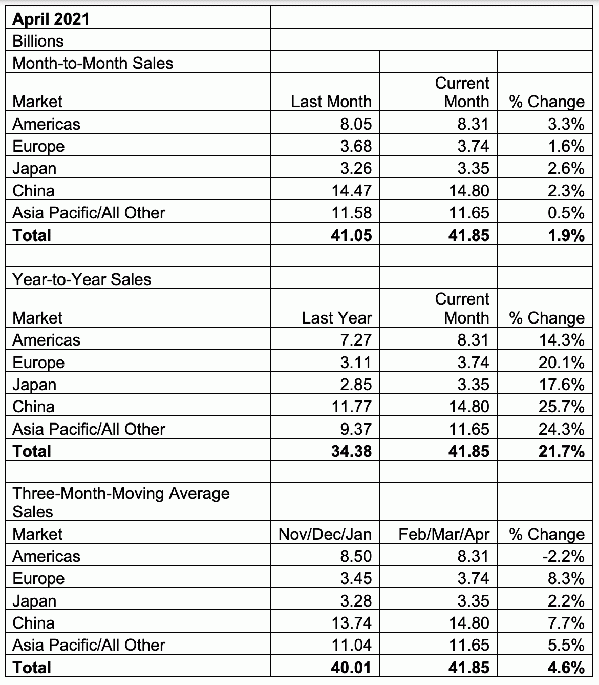

2021年6月9日、米SIA(Semiconductor Industry Association)は、2021年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年4月の世界半導体売上は、前年同月比約21.7%増、前月比約1.9%増の418億5000万ドルだった。この実績は4月の売上としては過去最高。単月売上が前年同時期を超えるのは15ヶ月連続で、2021年の売上は過去最高を記録した2018年を上回る水準で推移している。

なお時同じくして発表されたWSTSの世界半導体市場予測によると、2021年は前年比19.7%、2022年は前年比8.8%の成長率を達成するとみられている。

成長に最も大きく貢献するのはやはりメモリで前年比31.7%増となる見通し。メモリに次いでセンサー22.4%、アナログ21.7%と、ほとんどの分野で2桁の成長率を達成すると予測されている。

地域別の成長率では、中国を含むアジア太平洋が23.5%、ヨーロッパ21.1%、日本12.7%、南北アメリカが11.1%と予測されている。

2021年4月の世界半導体売上を地域別にみると、全ての地域で売上前年比2桁増を達成。中国市場、アジアその他地域だけでなく、欧州も前年比20.1%と大きな成長を示した。

日本市場も前年比17.6%増と好調で、売上を円ベースで換算すると前月比約3.2%増、前年比約18.8%増の約3,656億円となる。日本市場の売上が前年同月比プラス成長となるのは6か月連続。

2021.06.09

2021年6月8日、Siemensは独ProDesignのFPGAベース・プロトタイピング製品事業を買収したことを発表した。

Siemensが買収したのはProDesignのソリューションの中心に位置するFPGAベース・プロトタイピング環境「ProFPGA」ファミリ製品で、同製品の開発・サポートチームもSiemensに移籍するようだ。取引条件など買収に関する詳細は明らかにされていない。

Siemensは先日、同社として初となるFPGAベース・プロトタイピング環境「Veloce Primo」および「Veloce proFPGA」を発表し、FPGAプロトタイピング市場への参入を果たしたが、デスクトップ・タイプの「Veloce proFPGA」はProDesignのOEM製品だった。

※関連ニュース:

Siemensの発表によると、「proFPGA」製品は15か国、120のアクティブ・ユーザーに1,900を超えるシステムを納入した実績があり、今回の買収によりSiemensはFPGAプロトタイピング市場における強力なポジションを獲得できるとしている。

ProDesignは「ProFPGA」事業を売却したあとも企業として存続し、コンサルティングや設計・開発、プロトタイピングなど各種サービスの提供を続けるという。

2021.05.27

2021年5月19日、Synopsysは、2021会計年度第2四半期(21年2-4月)の四半期決算を報告した。

発表によるとSynopsysの2021会計年度Q2の売上は、前年同時期比約19%増、前Q1比約5.6%減の10億2430万ドルで、営業利益は前年比約78%増の1億9510万ドルだった。(※GAAP基準による会計結果)この実績はQ1実績報告時の予測を上回るものとなる。

SynopsysはこのQ2において、以下のような発表を行なっている。

Synopsysは、来期Q2(2-4月)の売上を10億300万-600万ドル、2021会計年度の売上を40億3500万-8500万ドルと予測している。

2021.05.20

2021年5月20日、CadenceはFastSPICEの新製品「Spectre® FX Simulator」を発表した。

Cadenceによると新製品「Spectre® FX Simulator」は、新たに開発された新しいFastSPICEソルバーにより、パフォーマンスと精度が飛躍的に向上されており、フルチップ、サブシステムレベルのデザインのタイミング、機能、消費電力を高い精度で確認することが可能。市場の最新FastSPICEシミュレータと比較して、同等以上の精度で最大3倍のパフォーマンスを実現するとしている。

大きな特徴としては、過渡解析シミュレーションを最大32コアで並列実行可能なスケーラビリティ、最小限の調整で最適な精度とシミュレーション速度を得ることが可能な直観的なユースモデル、スタティック/ダイナミックな回路チェック、ALTER解析、スイープ解析、モンテカルロ解析など幅広い検証機能などが挙げられており、「Virtuoso® ADE Product Suite」とシームレスに統合されているなど、導入も容易だという。

発表にはルネサスの担当者がユーザーとしてコメントを寄せているが、

別プレスリリースにてJVCケンウッドが「Spectre® FX Simulator」を含むCadenceの複数のカスタム、アナログ、デジタル設計・検証ソリューションを採用したと報じられている。JVCケンウッドではCadenceのツールにより、市場投入までの時間を40%短縮できた開発事例もあるということだ。

なおSPICEの分野では先ごろSynopsysも新製品を発表しており、新世代の製品へと市場が移り変わる時期になってきているようだ。