NEWS

2021.05.18

2021年5月13日、Synopsysは新型のエミュレーション・システム「ZeBu EP1」のリリースを発表した。

Synopsysの提供する「ZeBu」シリーズのエミュレーション・システムは、CadenceやSiemensのエミュレーターと異なりFPGAをベースとしているが、今回発表された新製品「ZeBu EP1」は、Xilinxの16nm FPGA「Virtex UltraScale+ VU19P」が搭載されている。

ここのところ「Virtex UltraScale+ VU19P」を搭載したプロトタイピング・システムのリリースが各社から相次いでいるが、その流れの中でエミュレーター「ZeBu」も最新の大規模FPGAをベースとするシステムに刷新された形だ。

Synopsysによると新製品「ZeBu EP1」のエミュレーション動作性能は10MHzでSynopsys曰く業界最速。これはSynopsys独自のダイレクト・コネクト・アーキテクチャをベースにデザイン間の通信を最適化することで実現されている。

また「ZeBu EP1」は、今年2月に発表したパワー解析機能「ZeBu Empower」を用いたパワー解析も可能。現実的なソフトウェア・ワークロードを使って、プレシリコンの段階で電力消費を分析できるため、設計サイクルの早い段階で電力バグのリスクやSoC電力目標のリスクを大幅に削減できる。

速さとパワー解析機能に加えてシステムレベルのデバッグ機能も「ZeBu EP1」のウリの一つで、Synopsysは数十億サイクルのソフトウェア・ワークロードを実行しつつ、数十億ゲートの複雑なSoCを効率的にデバッグすることができるとしている。

従来から「ZeBu」を用いたソリューションの一つとなっている「Hybrid Emulation」機能も健在で、仮想プロトタイピング環境「Virtualizer®」との連携によりエミュレーション処理能力を大幅に向上することが可能。そのための仮想モデル(プロセッサ、メモリ、インタフェースなど)を豊富に用意している。

「ZeBu」上に実装するモデルとしては、PCIe 5.0、USB3、SATA、Ethernet、NVMeのホスト/デバイス・モデルが用意されており、SoC上で動作する実際のOS、ドライバ、アプリケーション・ソフトウェアを用いて、ホストからデバイスに至るソフトウェア・スタックの検証が可能だという。

新型の「ZeBu EP1」は既に出荷が開始されている。

2021.05.13

2021年5月11日、AIチップを手掛けるベンチャーMythicは、資金調達Cラウンドで7,000万ドルを調達した事を発表した。

発表によると今回のラウンドをリードしたのは、世界最大の投資運用企業BlackRockとHewlett Packard Enterprise(HPE)の両社。前回のラウンドから約2年が経過した今回の調達によりMythicの合計調達額は1億6,250万ドルに達した。

Mythicは新たに調達した資金により、推論チップの量産、ハード/ソフトの製品開発、顧客サポート強化を進めるとしている。Mythicは2019年末から製品出荷を開始しており、既にAPAC、ヨーロッパ、米国に顧客を抱えているようだ。

Mythicのアナログベースの推論チップについては、下記の記事を参照。

2021.05.13

2021年5月10日、DSPコアを手掛けるCEVAは、チップ設計サービスを手掛ける米Intrinsix社の買収を発表した。

Intrinsixはチップ設計のスペシャリストとして35年の実績を持つ北米の設計サービス会社。Intel、IBM、Leidos、Lockheed Martinなどを顧客に持ち、1500件以上の設計経験がある。インターフェイスIPに関する専門知識が豊富で、航空宇宙および防衛分野で強力な足場を築いているほか、チップレットおよびセキュアプロセッサー開発などDARPAプロジェクトにも参画している。

CEVAは自社の技術・IPとIntrinsixの幅広いチップ設計機能とIPを組み合わせることで、完全なターンキーIPプラットフォームの提案が可能になるとしている。今後は、5Gインフラ、自動車、航空宇宙および防衛、医療、ロボット、産業用IoTなどの市場に向けて、自社IPを用いたカスタムチップの設計サービスも展開していく構えだ。

CEVAによるIntrinsixの買収は3300万ドルの現金取引で2021年Q2に完了する予定。

2021.05.07

2021年5月6日、市場調査会社IDCは2020年の世界半導体市場の売上統計を発表した。

IDCの統計によると2020年の世界の半導体市場の売上合計は前年比10.8%増の4,640億ドル。

2021年は前年比12.5%増の5,220億ドルに達すると予測している。

IDCによる分野別の売上統計および2021年予測は以下の通り。

PCやサーバーなどのコンピューティング・システム:

前年比17.3%増の1,600億ドルで半導体市場全体を上回る成長率。

PCプロセッサの需要は今年も年間を通して堅調で、2021年は前年比7.7%増の1,730億ドルになる見通し。

モバイル/携帯電話:

携帯電話の出荷は今年10%以上減少したが、5Gへのシフト、メモリ搭載量の増加、センサー、RFの増加などにより、携帯電話の半導体の収益は回復した。

2021年は、出荷される携帯電話の34%が5G対応となる見通しで、2021年の携帯電話の半導体収益は前年比23.3%増加の1,470億ドルになる見通し。

コンシューマー:

ゲーム機、タブレット、ワイヤレス・ヘッドホン/イヤフォン、スマートウォッチ、OTTストリーミング・メディアデバイスの好調な販売により、前年比7.7%増の600億ドルを達成。中でもApple、AMD、Intelが大きな成長を見せた。

2021年はMicrosoftとSonyの新型ゲーム機、Appleのウェアラブル製品が引き続き好調で、成長率は前年比8.9%に加速する見通し。

自動車:

火災と工場の閉鎖が自動車用半導体市場にさらに影響を及ぼし、一部の製品の供給制約は2021年まで続くも2021年は13.6%増となる見通し。

2021.05.07

2021年4月28日、IC Insightsのレポート:

2020年、世界半導体市場におけるファブスベンダの売上が占める割合は、過去最高の32.8%を記録した。

2010年から2020年のIDMの平均成長率は僅か3%で、半導体市場全体の成長率を下回っている。

IDMはメモリの売上が大きいのでメモリ市場の影響による成長率の格差が激しい。

これに対してファブレスベンダの平均成長率は8%で、半導体市場全体の成長率の倍に相当する。

IC Insightsは今後5年間でファブレスベンダの売上シェアが35%程度まで伸びると予測している。

ちなみにファブレスベンダ売上トップ5のうち、Broadcom以外の4社(Qualcomm、NVIDIA、MediaTek、AMD)は、2020年に前年比30%増を超える大きな成長を記録している。

2021.05.06

EDA Expressの新企画、Zoomを使った「オンライン・インタビュー」のご案内です。

ハードウェア設計関連の様々なテーマについて、ゲストを招待してオンライン(Zoom)で色々な話をライブで聴くという企画です。

昨今、ウェビナーやバーチャル展示会などイベントのオンライン開催が当たり前になってきましたが、ここだけの話やちょっとした雑談といった、対面ならではの「生のコミュニケーション」はなかなかオンラインでは実現できていません。

新企画「オンライン・インタビュー」は、特定のテーマについてゲストに話を聞くだけでなく、聴講者の方々も含めた参加者全員が情報交換や意見交換できるよう、少人数制のミーティング形式で開催します。

顔出しは自由、発言、チャットは基本的に制限無し。オープンな形でありながら、クローズドなライブ・イベントとして開催しますので、情報収集の場、業界関係者とのコミュニケーションの場としてご利用下さい。

オンライン・インタビュー企画の第三弾は、「今さら聞けない検証IPについて聞いてみる」と題して、SmartDV社の設計/検証IPを取り扱う株式会社ネクストリーム様よりゲストを招いて開催します。ご興味ある方は是非お気軽にお申し込み下さい。

EDA Express オンライン・インタビュー 第3回

テーマ :今さら聞けない検証IPについて聞いてみる

ゲスト :株式会社ネクストリーム 技術部 部長 守田 直也様

開催日時 :5月26日(水)PM 60分間

※12:00〜、14:00〜、16:00〜の中で希望が多い時間で開催します

参加 :無料、最大20名の参加者を想定しています

インタビュー構成:

・守田様のプロフィールについて(職歴、趣味など)

・検証IPとは?

-機能、種類、など

-検証IPの利用に関する世の中のトレンド

−最近の使われ方、国内/海外の違い、など

・検証IPのススメ

−活用メリット、活用事例、など

・検証IPあるある

−利用する上での注意点、よくある失敗事例、など

・参加者からの質問

インタビュアーはEDA Express 菰田が担当。インタビュー終了後は雑談タイムとします。

お申し込み:

こちら(Googleフォーム)よりお願いします。

※オンライン・インタビューに関するご質問等はこちら までお願いします。

2021.05.06

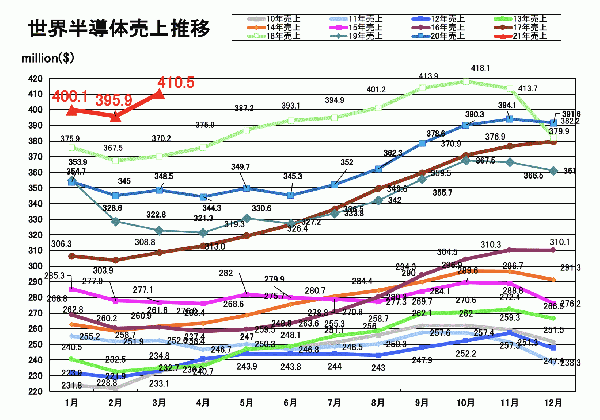

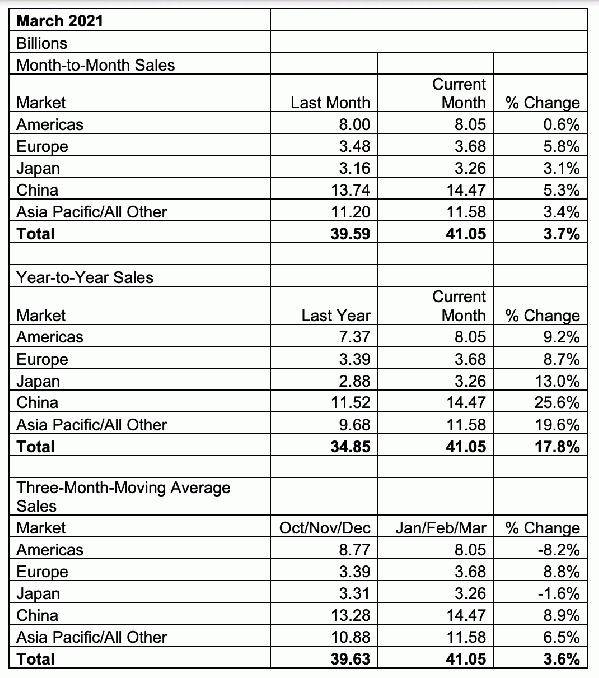

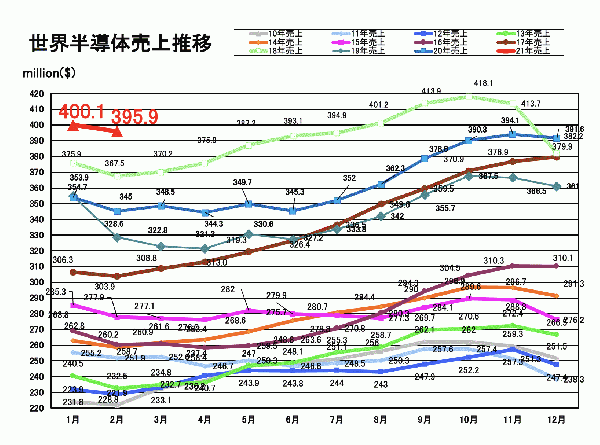

2021年4月30日、米SIA(Semiconductor Industry Association)は、2021年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年3月の世界半導体売上は、前年同月比約3.7%増、前月比約3.7%増の410億5000万ドルだった。この実績は3月の売上としては過去最高。単月売上が前年同時期を超えるのは14ヶ月連続。

2021年Q1(1-3月)の売上合計は前年比17.8%増の約1,231億ドルで、過去最高売上を記録した2018年を上回る水準で推移している。

2021年3月の世界半導体売上を地域別にみると、全ての地域で売上前年比増を達成。中でも中国市場は前年比25.6%増と強力な成長を見せた。アジアその他地域も好調を維持しており、2月を上回る前年比19.6%の成長となっている。北米市場は前年比9.2%増の成長で依然右肩上がりの成長を継続している。

日本市場は前年比13%増とアジアその他地域に次ぐ成長率で2月に続いて好調をキープした。売上を円ベースで換算すると前月比約6%増、前年比約14.6%増の約3,542億円となる。日本市場の売上が前年同月比プラス成長となるのは5か月連続。

2021.04.30

2021年4月26日、Cadenceは、2021会計年度第1四半期(2021年1-3月)の売上を報告した。

Cadenceの2021年Q1売上は、前年比約19%増、前期Q4比約3.2%減の7億3600万ドル、営業利益は1億8700万ドルだった。(※GAAP基準による会計結果)

このQ1実績は同社のQ1売上記録として過去最高。前Q4に続いて四半期売上7億ドル超を維持した。

CadenceはこのQ1に以下のような新製品およびニュースを発表している。

・CFDシミュレーションの業界大手ベルギーNUMECA社を買収

・PCBおよびICパッケージ向けSI/PI解析ツールの新製品「Sigrity X」を発表

・マシンラーニングを用いたDFMサインオフでGlobalFoundriesと協業

Cadenceは2021年Q1の売上を7億500万-2500万ドル、2021年の年間売上を28億8000-29億3000万ドル程度と予測している。

2021.04.28

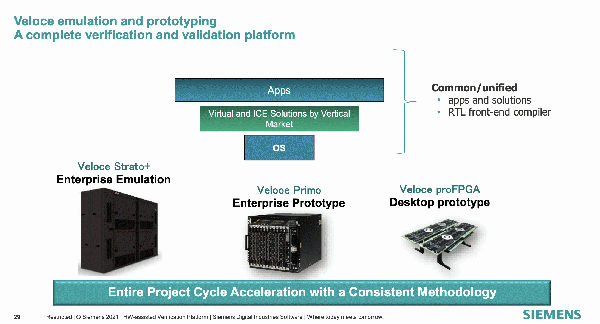

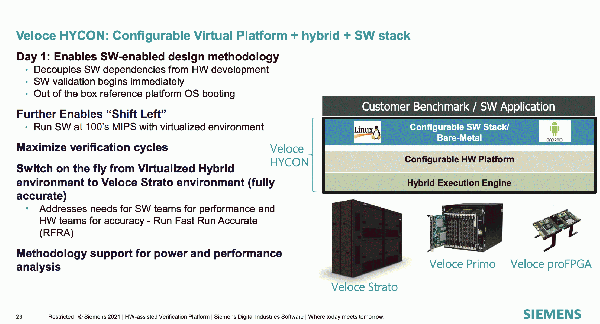

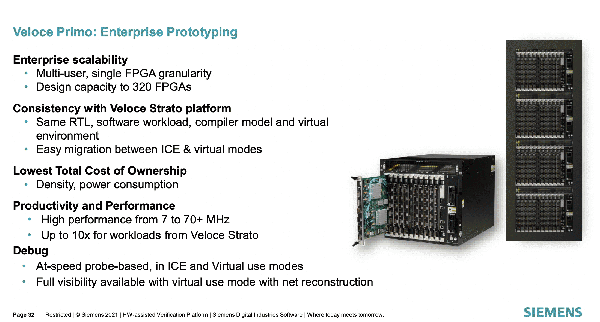

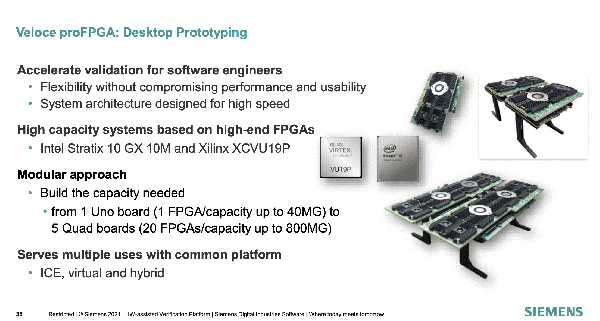

2021年4月21日、Siemensはハードウエアベースの検証ソリューションとして3種類の新製品を発表した。

※この発表は3月26日にSiemensが発表したものをあらためて傘下のメンター・グラフィックス・ジャパンを通じて発表したものとなる。

今回Siemensが発表したのは、エミュレーターの新型製品「Veloce Strato+」、FPGAベースのプロトタイピング・システム「Veloce Primo」および「Veloce proFPGA」の3製品。「Veloce Strato+」は既存エミュレーターの後継製品で、「Veloce Primo」および「Veloce proFPGA」はSiemens(Mentor)として初のFPGAプロトタイピング・システムとなる。

「Veloce Strato+」は「Crystal 3+」と呼ばれるSiemensの独自の2.5Dチップ(恐らく16nmチップ)が搭載され、デザイン容量は既存の「Veloce Strato」の1.5倍に拡張された。Siemensは、「Veloce Strato+」のデザイン容量は市場トップの150億ゲートを実現し、デザインのコンパイル速度、実行速度は業界最速だとしている。

また、今回「Veloce Strato+」のリリースに合わせて、「Veloce HYCON(HYbrid CONfigurable)」と呼ばれる仮想プラットフォームが新たに用意された。同環境上で仮想プロセッサモデルを実行することが可能で、ソフトウェアの早期検証や「Veloce Strato+」と接続したハイブリッド・エミュレーションが可能になる。

なお、「Veloce Strato+」と「Veloce Strato」はシャーシが同じでボードを差し替えるだけで既存システムのグレードアップが可能。「Veloce Strato」のユーザーとして知られるAMDは、第2世代および第3世代のEPYCプロセッサーの開発で「Veloce Strato」を利用しており、「Veloce Strato+」も先行導入しているという。

「Veloce Primo」と「Veloce proFPGA」はいずれもXilinxの16nmFPGA「Virtex UltraScale+ VU19P」を搭載するプロトタイピング・システムで、「Veloce Primo」はエンタープライズ向け、「Veloce proFPGA」はデスクトップ向けという位置付け。大型シャーシに最大10枚、計320個のFPGAを搭載できる「Veloce Primo」は最大80億ゲートのデザイン容量を誇り、実行速度は最大70Mhzに達するとされる。「Veloce proFPGA」の方は独ProDesignよりOEM供給される製品で、1つのボードに最大4個のFPGAを搭載可能。ボードを5枚連結することで最大8億ゲートのデザインに対応できる。

※画像はSiemens提供のデータ

どちらのプロトタイピング・システムもフロントエンド環境が「Veloce Strato+」と同じであるためエミュレーターからのデザイン移行が容易であり、同じRTL、同じ仮想環境、同じトランザクター/モデルを使用してシステム検証を実行可能。Siemensは、仮想環境、エミュレーター、FPGAベース・プロトタイピングと三位一体となった包括的な検証環境により、より高度・高速な検証、検証サイクルの短縮が実現できるとする。

ここのところCadence,Synopsysと新型エミュレーター/FPGAプロトタイピング・システムの発表が相次いでいるが、その背景にはチップの大規模化に伴う高速・大容量な検証ソリューションへのニーズの高まりがある。これまでエミュレーターの分野ではCadenceとSiemens(Mentor)の2社が競い合ってきたが、そこにFPGAベースのプロトタイピング・システムも加わることで、同分野のシェア争いはSynopsysやS2Cなど他のベンダも含めてより激化していくことだろう。

2021.04.28

2021年4月27日、Xilinxは7nmプロセスで製造するACAP (Adaptive Compute Acceleration Platform)製品、「Versal AI Core」シリーズと「Versal Prime」シリーズの量産開始を発表した。

「Versal AI Core」は、機械学習や高度な信号処理などをターゲットとしたハイパフォーマンス・デバイスで、Versalファミリの中で最高のコンピューティング性能と最小のレイテンシーを提供する。「Versal Prime」は、様々な市場やアプリケーションに適用可能なVersalファミリのベースとなるデバイス。いずれのデバイスも既に先行顧客に提供され製品やサービスに組み込まれている。

また、Versalファミリのもう一つの製品「Versal Premium」も先行顧客への提供が開始されたとのこと。同デバイスは高度に統合され電力が最適化されたコアを備えており、Versalファミリの中で最高の帯域幅と演算密度を誇る。

2021.04.28

2021年4月27日、データセンター向けのAIプロセッサ「IPU-Processor」を手掛ける英Graphcoreは、日本法人グラフコア・ジャパン株式会社の設立を発表した。

発表によるとグラフコア・ジャパン株式会社の代表取締役社長に就任した中野守氏は、Cray、HPE、Compaq、DECなどHPC分野で活躍してきた人物。Graphcoreは、SCSK株式会社およびHPCシステムズ株式会社の2社を日本国内における販売パートナーとして製品の国内展開を進めていく。なおSCSKは既に国内複数の大手企業からGraphcoreシステムの受注を獲得しているという。

Graphcoreは累計調達額7億1,000万ドル以上で、AIプロセッサのトップ企業のうちの1社。同分野ではCerebras Systemsが先行して日本法人を設立している。

2021.04.23

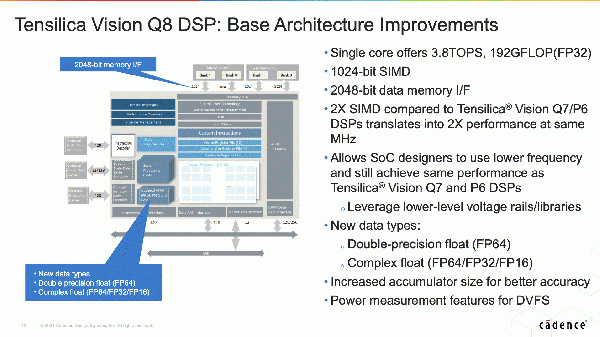

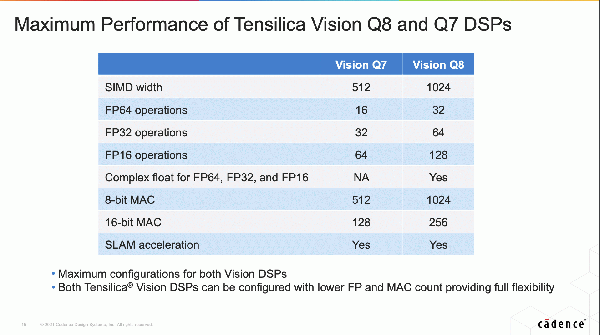

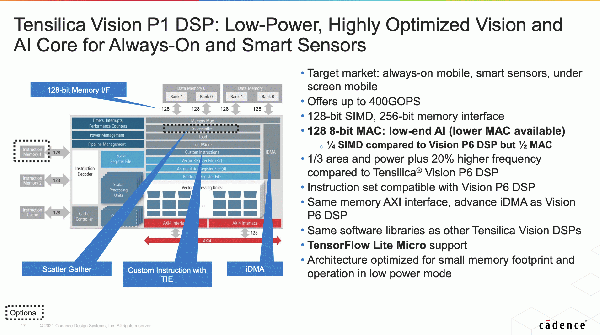

2021年4月22日、Cadenceは、エンベデッドビジョンおよびAI向けDSPの新製品2品種を発表した。

今回Cadenceが発表したのは、Tensilica Vision DSP製品ファミリーとしてラインナップされる「Tensilica Vision Q8 DSP」および「Tensilica Vision P1 DSP」の2品種。

「Tensilica Vision Q8 DSP」は、既存の「Tensilica Vision Q7 DSP(512ビットSIMD)」の倍の1024ビットSIMDアーキテクチャの第7世代のハイエンドDSPコアで、Tensilica Vision DSP製品ファミリーのフラッグシップ製品という位置付け。

「Vision Q8」は、「Vision Q7」の2倍にあたる最大3.8TOPSのパフォーマンスと2倍のメモリー帯域幅を実現しており、システムデザインの簡素化によりシングルコアでの消費電力を最大20%低減する一方、MAC数が追加されたことなどによりAIパフォーマンスは最大4倍に引き上げられた。

「Tensilica Vision Q8 DSP」は1つのチップに最大4コア構成で利用可能で、パフォーマンスを要求するハイエンドモバイル、マルチカメラ車載アプリケーションなどを主なターゲットとする。

ハイパフォーマンスDSPコアとして開発された「Tensilica Vision Q8 DSP」に対し、「Tensilica Vision P1 DSP」は128ビットSIMDアーキテクチャで電力効率重視の小型ローパワーDSPコアという位置付けで、スマートフォンのAI処理などで実績のある既存の「Vision P6 DSP」と比較すると、面積と消費電力は3分の1、パフォーマンスは約半分程度となっており、スマートセンサー、AR/VRグラス、IoT/スマートホーム機器など、AI処理を行う常時接続アプリケーションを主なターゲットとしている。

※画像はCadence提供のデータ

新製品の「Vision Q8 DSP」および「Vision P1 DSP」はいずれも既存のDSP同様、N-waySIMDプログラミングモデルを採用しており、異なるSIMD幅を持つ既存のTensilica Vision DSPからソフトウェアを容易に移行可能。すなわちコアの選択により、同じソフトウェアでパフォーマンスをスケーラブルに変更できる。

また、いずれのDSPコアもニューラルネットワーク向けの「Xtensa ® Neural Network Compiler (XNNC) 」、「Android Neural Networks API (ANN API) 」、1700種以上のOpenCVベースのVision Library関数、OpenCL、Halideコンパイラーに対応。さらに機能安全規格 ISO26262、ASIL Bランダムハードウェア故障およびASIL Dシステマティック故障の認証を取得しており、車載向けアプリケーションにも利用できる。

「Tensilica Vision Q8 DSP」は既に出荷が開始されており、「Tensilica Vision P1 DSP」は2021年のQ2に一般リリースの予定。

CadenceのTensilicaシリーズ製品は、DSPとしては世界トップシェアを誇り300以上の顧客を持ち累計出荷数は70億以上。CadenceはプロセッサIPのライセンス売上としてArmに次ぐ世界2位の座をキープしている。

2021.04.21

2021年4月21日、ルネサス エレクトロニクスとRISC-Vプロセッサを手掛けるSiFiveは、車載アプリケーション向けの次世代ハイエンドRISC-Vソリューションの共同開発を目的とした戦略的パートナシップの締結を発表した。

今回の発表は早い話がルネサスの開発している各種車載向けチップにSiFiveのRISC-Vプロセッサを採用するというもの。SiFiveはルネサスに自社のRISC-Vコアをライセンス供与するという。

車載向けチップという意味ではデンソー子会社のNSITEXEもRISC-Vコアを用いたプロセッサを開発しているなど、RISC-Vの波は車載半導体の分野にも徐々に浸透し始めている。

2021.04.21

2021年4月20日、Synopsysは開催中のユーザー・カンファレンス「SNUG® World」にて、回路シミュレーションのための新たなソリューション「PrimeSim Continuum」を発表した。

発表によると「PrimeSim Continuum」は、Synopsysの保有する回路シミュレーション・エンジンおよび技術を統合したカスタム設計向けのオールインワン・ソリューションで、新開発された「PrimeSim SPICE」および「PrimeSim Pro」と、既存の「PrimeSim HSPICE®」、「PrimeSim XA」を合わせた計4つのシミュレータを一つの環境でシームレスに扱うことができる。

今回Synopsysが「PrimeSim Continuum」を用意した背景には、益々複雑さを増す今日のチップ設計の問題があり、回路シミュレーションにおいても複合的なソリューションが必要とされている。同じダイまたはパッケージにアナログ、デジタル、ミックスドシグナルと多様な異種コンポーネントが統合されており、それらは場合により異なるプロセスノードで構築されていたり、2.5Dまたは3Dアーキテクチャで垂直統合されていたりするなど、今日のSoCを考えるとコンポーネント毎に様々な回路シミュレーションのアプローチが必要になるためだ。

Synopsysによると、「PrimeSim Continuum」の中核を担う「PrimeSim Pro」は、次世代のFastSPICEアーキテクチャを基に開発されており、DRAMやフラッシュ・メモリー・デザインに対して高速/大規模な解析を実行可能。既に同ツールを利用したSamsungのメモリ開発担当者は「PrimeSim Pro」を最速のFastSPICEであると称し、実際に電源供給ネットワーク・デザインのフルチップ・シミュレーションを従来比5倍のスピードで実現したとコメントしている。

もう一つ新たに開発された「PrimeSim SPICE」は、独自のGPUテクノロジを組み込んだ次世代アーキテクチャにより、NVIDIAのGPUを使いサインオフ精度を維持したままアナログやRFデザインなどの高速な解析を実現可能だという。

なおSynopsysは4つの回路シミュレータを統合して利用するために「PrimeWave」と呼ぶ新たな環境も用意した。「PrimeWave」は「PrimeSim Continuum」のシミュレーション・エンジンの共用コックピットのような環境で、デザインのセットアップ、分析、後処理の最適化などを担うということだ。

Synopsysは「PrimeSim Continuum」を用いることでサインオフ精度を維持したまま回路シミュレーションの実行時間を1/10に短縮できるとしているが、Samsungのファンドリ・デザイン・プラットフォーム担当者によると、実際に最新の56Gbit Ethernetデザインのシミュレーションにおいて、サインオフ精度を維持しながらシミュレーション速度を10倍高速化することに成功。検証工数を数日単位から数時間単位に短縮できたとしている。

SPICE/回路シミュレータの世界では、10年以上前にBerkeley Design Automationが高速高精度なSPICEをリリースして以降、大きな注目を集めた新製品のニュースは恐らく無い。(Berkeley Design Automationはその後2014年にMentor Graphicsに買収された。)今回のSynopsysの「PrimeSim Continuum」の発表は、久しぶりにSPICEユーザーを湧かせるニュースになりそうだ。

2021.04.20

2021年4月15日、Siemensはフォーマル検証ツールを手掛ける独OneSpin Solutionsを買収することを発表した。

SiemensはMentor Graphicsを買収してからもEDAソリューションの拡充を継続しており、昨年は配置配線ツールのAvatar Integrated Systems、SoC解析&デバッグソリューションのUltraSoCなどを買収している。

OneSpin Solutionsは、Infineon TechnologiesとSiemensのエンジニアが2005年に立ち上げたEDAベンダで、元々ドイツを地盤にSiemensとの繋がりは強い。

OneSpin Solutionsのフォーマル検証ツールはワールドワイドで一定の実績を残しており、日本国内にも複数のユーザーを抱えている。昨今は自動車、RISC-V、FPGAなど、様々な分野、アプリケーションを切り口に、フォーマル検証ソリューションの展開を進めていた。

買収に関する詳細は明らかにされていないが、OneSpin Solutionsのツールや技術は今後SiemensのIC検証製品スイートの一部として受け継がれていくことになる。

2021.04.20

2021年4月16日、Cadenceは、CFD (数値流体力学) 用のメッシュ・ジェネレーターを手掛ける米Pointwise社を買収したことを発表した。

Pointwise社はCFD用のメッシュ生成ソフトの分野では世界的なリーダーと言える存在で、メッシュ生成に30年以上取り組んできた実績があり、その製品はワールドワイドで700サイト以上の顧客を持つ。日本では株式会社ヴァイナスが代理店として長年Pointwiseの製品を販売している。

Cadenceは先ごろCFDシミュレーター大手のベルギーNUMECA社を買収したばかりで、今回のPointwise社の買収により、NUMECAのCFD技術を補完する形でシステム解析分野の製品ポートフォリオを拡充できるとしている。

Cadenceは近年、システム解析領域のソリューション拡充に力を注いでおり、新製品の投入と合わせて積極的に企業買収も進めている。同分野で力のあるAnsysのソリューションに真っ向から立ち向かい、新たな市場を獲りに行く姿勢を明確に見せている。

2021.04.16

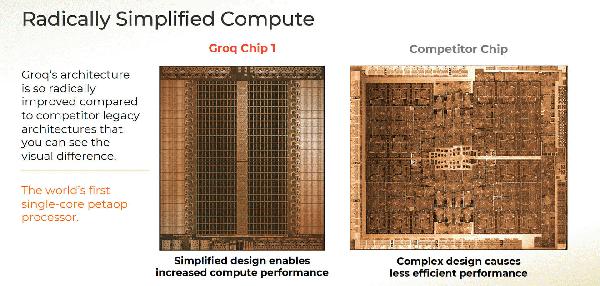

2021年4月14日、元GoogleのTPU開発エンジニアが創業したAIチップベンチャー米Groqは、資金調達Cラウンドで3億ドルを調達したことを発表した。

発表によると3回目となる今回の資金調達は、Tiger GlobalManagementとD1Capitalの2社のリードによって進められた。

Groqの累計調達額は3億6700万ドルで、調達した資金は人材確保と開発中の次世代製品の加速に充てるとしている。ちなみに2020年時点での同社の従業員数は122人。

Groqは既に開発したAIプロセッサ「TSP(Tensor Streaming Processor)」と同プロセッサを搭載したカード、ラックをリリースしており、Nimbixのクラウドサービスでも利用されている。報道されている内容によると金融業界や米国の国立研究所など数社が既に同社の顧客になっているようだ。

Groqの「TSP」は巨大なシングルコアのチップで、大量のSRAMと演算ユニットで構成されるシンプルなアーキテクチャが特徴。このアーキテクチャは同社が提唱する「ソフトウェア・ファースト」という考え方から生まれたもので、独自のプログラミング言語を用いた同社曰く非常に簡単なプログラムでチップを動かす。これによりエネルギー効率を高めレイテンシを削減する事が可能で、Groqは「TSP」を業界最速のシングルコア・チップであると主張する。実際のベンチマーク結果によると「TSP」のレイテンシは主要なGPUの10分の1程度で、プロセッサ分野に詳しい調査会社Linley Groupも「TSP」を最速のディープラーニング・アクセラレータと評していた。(2020年1月時点)

※画像はGroq社Web上のデータ

2021.04.15

2021年4月12日、Synopsysはネットワーキング向けの設計IPを手掛ける独MorethanIP社の買収を発表した。

SynopsysによるとMorethanIPの買収は今年5月に完了の予定。その取引に関する詳細は明らかにしていない。

MorethanIPの主力製品はASIC/FPGA向けのEthernet コントローラIP。

Synopsysは今回の買収により、MorethanIPの200G/400G/800G Ethernet向けのMACならびにPCS(Physical Coding Sublayer:データの符号化層)IPが同社のEthernet IPに加わることになり、高性能/低レイテンシの要件を満足させる完全なEthernet コントローラ/PHY IPソリューションの提供が可能になるとしている。

2021.04.15

2021年4月13日、IC Insightsのレポート:

IC Insightsの調べによると、2020年世界半導体売上における地域別シェアは以下の通り。

この数値はIDMの売上とファブレスの売上の総計から算出されている。

米国企業55% IDM,ファブレス共に強い

韓国企業21% IDMが強い

台湾企業7% ファブレスが強い

欧州企業6% IDMが強い

日本企業6% IDMが強い

中国企業5% ファブレスが強い

1990年当時、日本企業のシェアは49%で米国企業の35%を上回っていた。

2021.04.15

2021年4月13日、ニューロモーフィック・チップを手掛けるBrainChipは、エッジAI向けプロセッサ「Akida™AKD1000」の量産開始を発表した。

BrainChipは当初2020年のチップ量産を計画していたが、ESのテストを経て「AKD1000」をエンハンスしオリジナルのデザインよりも更に低消費電力の動作モードを追加したとしている。

「AKD1000」のインプリメント(RTL以降の実装)は、パートナーのSocionextが行いTSMCへリリースしており、今年8月頃から供給が開始される予定。

BrainChipの「Akida」は、超低遅延、超低消費電力をうりにしており、Socionextのマルチコア・プロセッサ「SynQuacer」と組み合わせた動画/画像解析ソリューションもあるようだ。Socionextは「Akida」の販売についても協力する。

2021.04.15

2021年4月13日、ニューロモーフィック・チップを手掛けるBrainChipは、エッジAI向けプロセッサ「Akida™AKD1000」の量産開始を発表した。

BrainChipは当初2020年のチップ量産を計画していたが、ESのテストを経て「AKD1000」をエンハンスしオリジナルのデザインよりも更に低消費電力の動作モードを追加したとしている。

「AKD1000」のインプリメント(RTL以降の実装)は、パートナーのSocionextが行いTSMCへリリースしており、今年8月頃から供給が開始される予定。

BrainChipの「Akida」は、超低遅延、超低消費電力をうりにしており、Socionextのマルチコア・プロセッサ「SynQuacer」と組み合わせた動画/画像解析ソリューションもあるようだ。Socionextは「Akida」の販売についても協力する。

2021.04.14

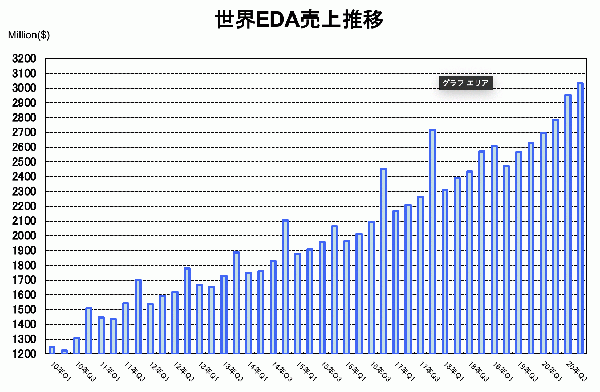

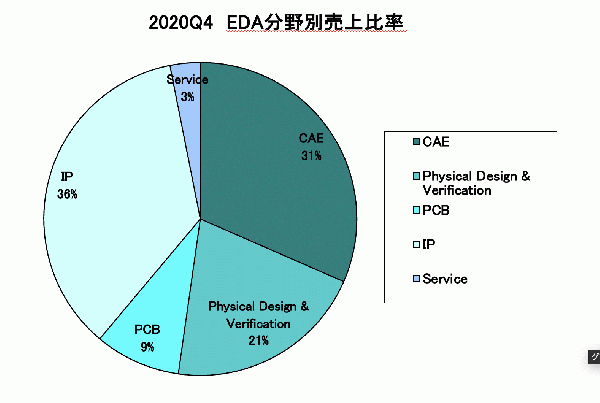

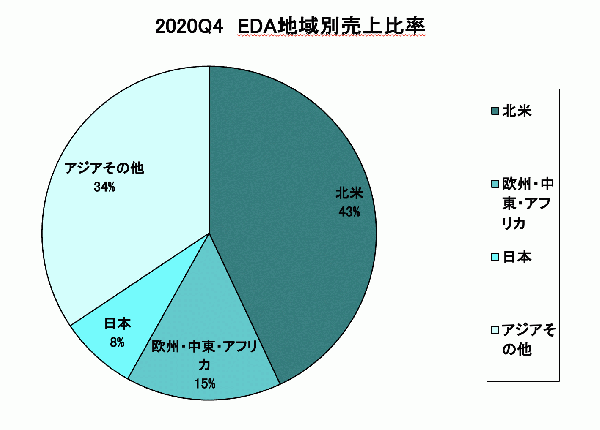

2021年4月13日、米ESD Allianceは、2020年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2020年Q4(10-12月)の世界のEDA売上総額は前年比約15.4増、前Q3比約2.6%増の30億3150万ドルで、四半期売上として過去最高記録を更新した。売上記録の更新は前Q3に続いて3四半期連続。四半期売上が前年実績を上回るのは8四半期連続で前年比で15%を超えたのは2011年以来4回目となる。

2020年の売上合計は前年比12.4%増の114億6730万ドルとなり、過去最高を更新した。

2020年Q4のEDA売上をカテゴリ別に見ると、IC Physical Design & Verification分野が前年比36.6%増と大きく伸びた。前Q3で初めて10億ドルの大台に乗せたIP分野はQ4も同水準の売上を維持した。

2020年Q4のEDA売上を地域別に見ると、Q3に続いてアジア・パシフィックが力強い成長を維持。最大市場の北米も13.8%増と好調継続で売上13億ドル台をキープした。欧州・中東・アフリカ、そして日本市場も一桁ながら前年比増を達成している。

2020年Q4時点でのEDA業界の従業員数は前年比6.7%増の47,478人でQ2よりも3%増加した。

2020年Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 9億5690万ドル 9.4%Up

■IC Physical Design & Verification分野 6億3710万ドル 36.6%Up

■IP分野 10億5290万ドル 16.9%Up

■サービス分野 9160万ドル 2.2%Up

■PCB/MCM分野 2億9290万ドル 0.8%Down

2020年Q4の地域別の売上と昨年同時期との比較は以下の通り。

■北米 13億400万ドル 13.8%Up

■欧州・中東・アフリカ 4億5720万ドル 2.7%Up

■日本 2億2820万ドル 8%Up

■アジアその他地域 10億4200万ドル 23.4%Up

※ESDA(Electronic System Design Alliance)

2021.04.14

2021年4月13日、SEMIは2020年の世界半導体製造装置の売上統計を発表した。

発表によると、2020年の世界半導体製造装置の売上額は前年比19%増と急増し、過去最高の712億ドルに到達した。

市場として最も伸びたのは中国で前年比39%増の187億2000万ドルと、初めて地域別売上でトップとなった。

2位の台湾は171億5000万ドルと昨年とほぼ変わらず横ばい、3位の韓国は前年比61%増との160億ドルと大きく売上を伸ばし台湾に迫った。

日本と欧州もそれぞれ前年比21%増、16%増と売上を伸ばしたが、北米だけは前年比20%減と売上を落とした。

製品分類別では、ウエハ加工装置 前年比19%増、フロントエンド機器 前年比4%増、組み立てとパッケージング機器 前年比34%増、テスト機器 前年比20%増という結果だった。

半導体製造装置市場は今年に入っても活況が継続しており、今年は更に年間売上を伸ばす見通しだ。

2021.04.14

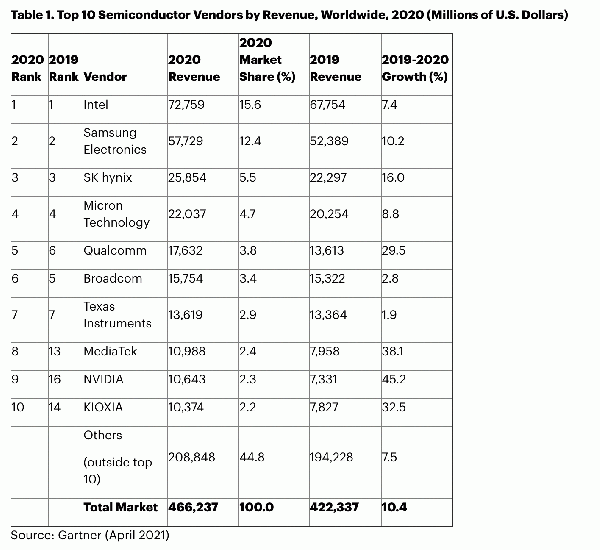

2021年4月12日、Gartnerは2020年半導体売上ランキングの最新版を発表した。

Gartnerによると2020年の世界半導体売上額は、前年比10.4%増の4,662億ドル。今年1月時点で発表していた数値から若干増加した。Top10に変更はなく、MediaTek、NVIDIA、KIOXIAがTop10入りを果たしている。Top10から外れたのは、TI、STMicroelectronics、NXPの3社。

2021.04.14

2021年4月13日、シリコンバレーのAIチップ・スタートアップSambaNova Systemsは、資金調達Dラウンドで6億7600万ドルを調達したことを発表した。

発表によると今回の投資ラウンドを主導したのはソフトバンク・ビジョンファンド2で、新たな投資家2社も参加。既存投資家のBlackRock、Google Ventures, Intel Capital, Walden Internationalらがこれに続いた。なお、Walden InternationalのチェアマンはCadenceのCEO Lip-Bu Tan氏で、同氏はSambaNova Systemsの会長に就任している。

今回SambaNovaが集めた投資額は6億7600万ドルで、これまでの調達額を合わせると同社の累計調達額は11億3200万ドルとなる。AIチップの世界では、米SambaNova、英Graphcore、中国Enflame Technologyの3社がそれぞれ累計約500億円を調達し資金力争いをリードしていたが、今回のラウンドでSambaNovaが業界ダントツの資金力を誇る会社となった。同社の評価額は50億ドルを超えるという。

SambaNova Systemsは、2017年に現CEOのRodrigo Liang氏とスタンフォード大のKunle Olukotun教授、同じくスタンフォード大のChristopher Ré准教授の3人が立ち上げたベンチャー。CEOのRodrigo Liang氏は元OracleでSPARCプロセッサを開発していたエンジニア、Kunle Olukotun教授は「マルチコアプロセッサの父」として知られている。

SambaNovaは「Dataflow-as-a-Service」と呼ぶサブスクリプション・ベースの拡張可能なAIサービスプラットフォームを提供しており、その中核をなすAIプロセッサが「ReconfigurableDataflowUnit™(RDU)」。同AIプロセッサは独自の機械学習アルゴリズムとソフトウェア定義型の再構成可能なハードウェアを組み合わせたコンピューティング・プラットフォームで、アプリケーションに最適化されたハードウェア構成でAI処理を実行できるとされている。

2021.04.09

2021年4月5日、SynopsysはFPGAベース・プロトタイピング・システム「HAPS-100」のリリースを発表した。

新製品「HAPS-100」は、既存の「HAPS-80」の後継となるプロトタイピング・システム「HAPS」シリーズの最上位製品で、Synopsysはプロトタイピング性能とデバッグ性能の向上を明言している。

※画像はSynopsys社Web上のデータ

これまでSynopsysが「HAPS」の新製品を発表する際は、必ず搭載されるFPGAについての説明があったが、今回は搭載FPGAに関する情報は出ていない。しかし、発表のタイミングや他社ソリューションの状況を考えると、Xilinxの16nm FPGA「Virtex UltraScale+ VU19P」が搭載されていると想像される。

同じXilinxの16nm FPGAを搭載するプロトタイピング・システムは、既にS2C, ProDesignがリリースしており、Cadenceも新製品を発表したばかり。FPGAベースのプロトタイピング・システムとして差別化を図るためには、搭載するFPGAデバイス以外の部分が重要となるため、今回Synopsysはあえてデバイスには触れず独自の技術によるプロトタイピング性能やデバッグ性能を強調したということだろう。

Synopsysによると「HAPS-100」の実行性能は複雑なSoCの場合で20〜50MHz、インターフェイスIPの場合は最大500MHzとかなり高速。これは「HAPS-80」同様、「HAPS」独自のFPGA間通信多重化技術やフロントエンド環境「Proto Compiler」のコンパイル技術などによって実現されていると考えて良いだろう。またデバッグ性能としては信号キャプチャ数が4倍になったということで、1つのFPGAあたり4000以上の信号をアットスピードでキャプチャする事ができるようだ。(HAPS-80では1つのFPGAあたり1000以上の信号をキャプチャ可能と説明されていた)

更に新しい「HAPS-100」には、マルチデザイン、マルチユーザーの並列利用を管理する「HAPSゲートウェイ」と呼ばれるソフトウェアも用意され、リモートアクセスによる多拠点利用などの運用性も高められたようだ。

「HAPS」はFPGAプロトタイピング・システム市場で強力な支持を集めており、既存製品の「HAPS-80」は2015年9月の発売から約4年間で販売台数3000台を超えていた。

2021.04.09

2021年4月8日、非営利団体「Open Source FPGA Foundation(OSFPGA Foundation)」の設立が発表された。

OSFPGA Foundationは、オープンソースのFPGA設計ツールとIPブロックの普及推進を目的に組織された団体で、Open−Silicon社の創業者でSiFiveの会長も務めていた

Naveed Sherwani氏が会長を務める。ボードメンバーには大学や研究機関の研究者が名を連ねており、FPGAベンダからはQuickLogicの社長兼CEOであるBrian Faith氏も参画している。同氏はオープンソースのチップ設計を目指す「CHIPS Alliance」やRISC-Vベースのオープンソースコアを提供する「OpenHWGroup」でも積極的に活動している人物として有名だ。

OSFPGA Foundationの

Githubページには既に数種類のツールやIPのリソースがアップされており、OSFPGA Foundationはこれらツール/IPに加え、新たなオープンソース・ツールやIPの開発とその普及をサポートしていく。オープンソースとして世に出ているツールやIPを利用しやすくする事で、更なるFPGAエコシステムの拡大を目指すというのが同団体の狙い。

2021.04.07

米国の政府機関DARPA(国防高等研究計画局)は、昨年の12月に「DARPA Toolbox」なる取り組みについて発表した。

「DARPA Toolbox」は、DARPAが支援する各種プログラムの研究者のために市販のEDAツールとIPへの低コストのアクセスを提供するためのイニシアチブで、回路設計に伴うコスト的な障壁を取り除き、イノベーション・プロセスへの参加を拡げることを目的としている。

「DARPA Toolbox」の下で最初にDARPAとの商業的パートナーシップを結んだのはArmで、DARPAの研究者は契約期間の3年間、全ての商用Arm製品を利用できるようになった。Armに続いてHDLパーサーで有名なVerificそしてIPベンダのCEVAも同イニシアチブに参画し、3月には組み込み型FPGAのFlexlogixが、そしてつい先日RISC-VベースIPの大手SiFiveも同イニシアチブに加わった。

DARPAプログラムの研究者は無料でIPやツールを使える訳ではないが、「DARPA Toolbox」を介して大幅な割引料金でライセンスにアクセスできる。IPベンダやツールベンダは「DARPA Toolbox」を介して未来の顧客獲得の機会を得ることができるので、Win-Winの構図となる。「DARPA Toolbox」への参画はDARPAの研究者のニーズに裏付けされたものとも言える。

2021.04.07

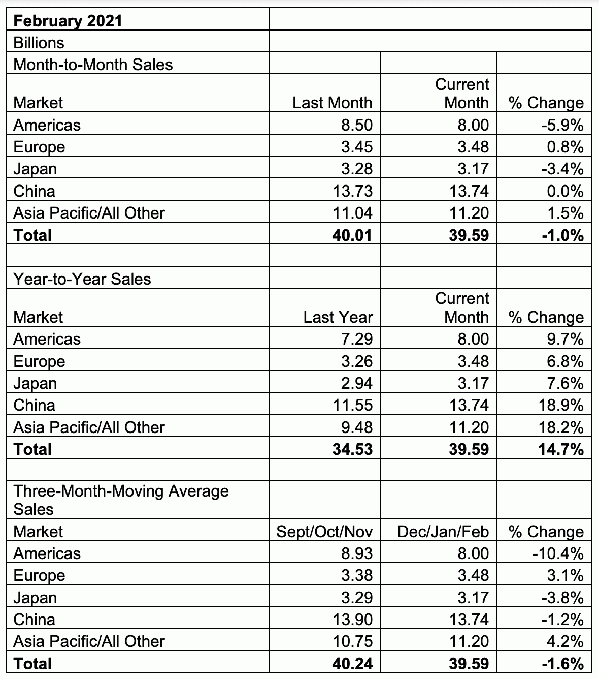

2021年4月5日、米SIA(Semiconductor Industry Association)は、2021年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると2021年2月の世界半導体売上は、前年同月比約14.7%増、前月比約1%減の395億9000万ドルだった。この実績は2月の売上としては過去最高。単月売上が前年同時期を超えるのは13ヶ月連続で、2021年の売上は1-2月と過去最高だった2018年を上回る水準で推移している。

2021年2月の世界半導体売上を地域別にみると、全ての地域で売上前年比増を達成。北米市場は2021年1月まで13ヶ月連続で対前年比の成長率が2ケタ増であったが、2月は9.7%の成長に留まった。ここにきて中国、アジアが強い成長を見せており、ともに1月に続いて対前年比2ケタ増となった。

日本市場は1月に続いて前年比7.6%増と好調をキープした。売上を円ベースで換算すると前月比約1.7%減、前年比約3.3%増の約3,340億円となる。日本市場の売上が前年同月比プラス成長となるのは4か月連続となる。

2021.04.06

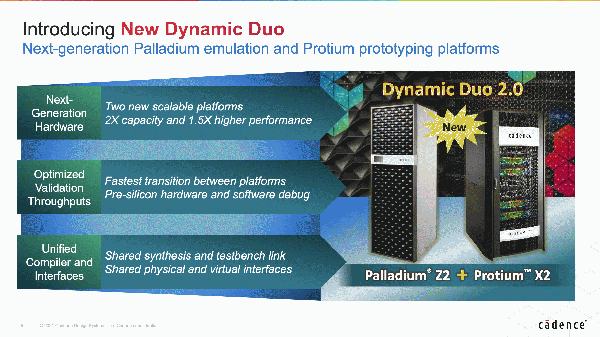

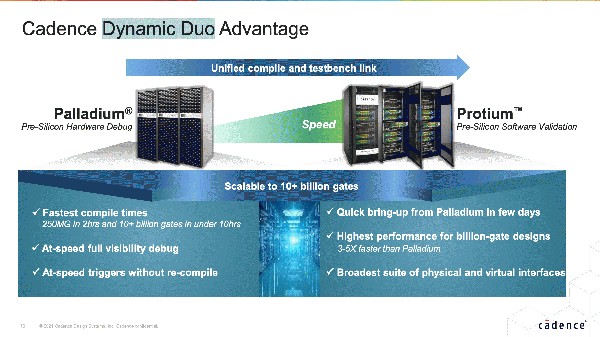

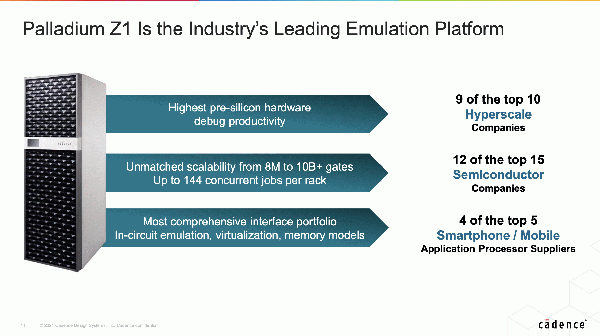

2021年4月6日、Cadenceは新型のハードウェアベース検証環境「Palladium Z2」と「Protium X2」を発表した。

発表された新製品「Palladium Z2」と「Protium X2」は、それぞれCadenceの既存のエミュレーター「Palladium Z1」とFPGAベース・プロトタイピング・システム「Protium X1」をベースに改良されたもので、Cadenceによるとデザイン容量(対応可能な回路規模)は両製品共に2倍にスケールアップ、パフォーマンス(速度)は1.5倍に向上した。

Cadenceはそのデザイン容量、パフォーマンスについて正確な数値を示していないが、「Palladium Z2」では100億ゲート以上、「Protium X2」では数十億ゲートのデザインに対応可能。「Palladium Z2」は数MHz、「Protium X2」は10MHz以上の実行速度が出せるようだ。

これら容量と性能の向上は、製品内で使用されているチップが変わったことによるもので、「Palladium Z2」内の専用プロセッサも「Protium X2」内のFPGAも恐らく1世代上のプロセス技術を用いたチップにアップグレードされた。恐らくというのはCadenceが発表でこれら内蔵チップについて明言していないからであるが、発表に寄せられたXilinxのコメントを見ると「Protium X2」は、16nm FPGA「Virtex UltraScale+ VU19P」をベースに開発されたと書かれている。これが確かであれば、「Palladium Z2」内の専用プロセッサも16nm チップという可能性が高い。

それはさておきCadenceとしては、製品内の搭載チップの詳細はソリューションの本質ではないと考えているようで、「Dynamic Duo」というキーワードでエミュレーターとFPGAベース・プロトタイピングの両ソリューションを提供している事に意味があると強調している。前世代製品の「Palladium Z1」と「Protium X1」がそうであったように、「Palladium Z2」と「Protium X2」もフロントエンドのインプリメント環境が同じであり、デザインの移行が非常に容易。つまり、エミュレーターで固めたRTLをすぐにFPGAプロトタイピング環境に移行してソフトウェアの検証を行うといった事が可能となる。日本ケイデンスの夏井氏によると、通常2〜3ヶ月かかるFPGAプロトタイピング環境の立ち上げも、「Palladium Z2」から「Protium X2」への移行であれば数日で完了できるという話だ。夏井氏はその大きな理由として、シンプルでインプリしやすい回路を吐き出すフロントエンド環境におけるコンパイル技術を挙げた。

なお「Palladium Z2」はこれまで通り非常に高速なコンパイル性能が売りのひとつで、2億5千万ゲートのデザインで2時間以内、100億ゲート超のデザインでも10時間以内にコンパイルが完了すると公称しているが、これは控えめの数値で実際には2億ゲートのデザインを1時間程度でコンパイル可能だという。(Palladium Z1の実績)また、デザイン容量に関しても「Palladium」シリーズはかなり控えめな数値をユーザーに伝えているようで、実際に使用してみると公称値の1.5倍相当のデザインでも問題なく実装できてしまうようだ。

日本ケイデンスの夏井氏によると、海外ではエミュレーターのデザイン容量に対する要望が非常に強く、中には170億ゲートといった巨大なデザインを扱う顧客も存在するとのこと。市場における「Palladium」のシェアは強力で、メモリベンダを除くほぼ全ての半導体大手、ファブレス大手が「Palladium」のユーザーだという。また最近はソフトウェアの開発規模およびコストの上昇に伴い、エミュレーターだけでなくFPGAプロトタイピング環境に対してもより大きなデザイン容量が求められており、「Palladium」と共に「Protium」を導入する顧客が増えているという。今回の発表にはXilinxの他にArm, NVIDIA, AMDがコメントを寄せているが、いずれも「Palladium Z2」と「Protium X2」の両製品をIP/チップ開発に活用している顧客だ。

ちなみにCadenceのホームページには「Palladium」関連の動画が幾つかアップされており、NVIDIAやキオクシア(東芝メモリ)が「Palladium」の導入について語っている。NVIDIAの建物の中で多くの「Palladium」の筐体が使われていることが分かる潜入レポート的なビデオなどもあり面白い。

2021.04.05

EDA Expressの新企画、Zoomを使った「オンライン・インタビュー」のご案内です。

ハードウェア設計関連の様々なテーマについて、ゲストを招待してオンライン(Zoom)で色々な話をライブで聴くという企画です。

昨今、ウェビナーやバーチャル展示会などイベントのオンライン開催が当たり前になってきましたが、ここだけの話やちょっとした雑談といった、対面ならではの「生のコミュニケーション」はなかなかオンラインでは実現できていません。

新企画「オンライン・インタビュー」は、特定のテーマについてゲストに話を聞くだけでなく、聴講者の方々も含めた参加者全員が情報交換や意見交換できるよう、少人数制のミーティング形式で開催します。

顔出しは自由、発言、チャットは基本的に制限無し。オープンな形でありながら、クローズドなライブ・イベントとして開催しますので、情報収集の場、業界関係者とのコミュニケーションの場としてご利用下さい。

オンライン・インタビュー企画の第二弾は、「今さら聞けないFPGAプロトタイピングについて聞いてみる」と題して、FPGAプロトタイピング・システムを手掛けるS2Cジャパン様よりゲストを招いて開催します。ご興味ある方は是非お気軽にお申し込み下さい。

EDA Express オンライン・インタビュー 第2回

テーマ :今さら聞けないFPGAプロトタイピングについて聞いてみる

ゲスト :S2Cジャパン株式会社 代表取締役 辻 智之様

開催日時 :4月28日(水)PM 16:00-17:00 60分間 ※途中入退出可

(12:00〜、14:00〜、16:00〜の中で希望が多い時間で開催します)

参加 :無料、10-20名程度最大20名の参加者を想定しています

インタビュー構成:

・辻様のプロフィールについて(職歴、趣味など)

・昨今のFPGAプロトタイピング事情について

−最近の使われ方、国内/海外の違い、など

・FPGAプロトタイピングのススメ

−理想的な使い方、活用する上で重要なポイント、など

・FPGAプロトタイピングの落とし穴

−よくある失敗事例、など

・参加者からの質問

インタビュアーはEDA Express 菰田が担当。インタビュー終了後は雑談タイムとします。

お申し込み:

こちら(Googleフォーム)よりお願いします。

※オンライン・インタビューに関するご質問等は

こちら までお願いします。

2021.04.02

2021年3月29日、バーチャル・プロトタイピング・ソリューションを手掛ける英Imperasは、RISC-Vベースのプロセッサ・コア「CORE-V」のISSをリリースしたことを発表した。

「CORE-V」は非営利組織「OpenHW Group」が開発および提供するRISC-Vベースのオープンソースコアで、開発中も含めてCORE-V Familyとして4種類のプロセッサ・コアが存在しており、その一部はSystem VerilogのRTLコードが公開されている。

今回ImperasがリリースしたISSは「riscvOVPsimCOREV」という名称でCORE-V Familyの4種類のコアをサポート。「riscvOVPsimCOREV」は、「CORE-V」リファレンス・モデルとして無料で提供される。ライセンスはImperas独自のフリーウェア・ライセンスで商用にも利用可能。シミュレーター・パッケージには、Apache 2.0ライセンスの下でライセンスされる完全なオープンソースモデルも含まれており、

githubで公開されている。

Imperasは「OpenHW Group」の創設時からメンバーとしてオープンソースコアの普及活動に貢献している。

2021.04.01

ご好評につき満員となりましたので、本インタビュー・イベントの参加登録は終了致しました。

EDA Expressの新企画、Zoomを使った「オンライン・インタビュー」のご案内です。

ハードウェア設計関連の様々なテーマについて、ゲストを招待してオンライン(Zoom)で色々な話をライブで聴くという企画です。

昨今、ウェビナーやバーチャル展示会などイベントのオンライン開催が当たり前になってきましたが、ここだけの話やちょっとした雑談といった、対面ならではの「生のコミュニケーション」はなかなかオンラインでは実現できていません。

新企画「オンライン・インタビュー」は、特定のテーマについてゲストに話を聞くだけでなく、聴講者の方々も含めた参加者全員が情報交換や意見交換できるよう、少人数制のミーティング形式で開催します。

顔出しは自由、発言、チャットは基本的に制限無し。オープンな形でありながら、クローズドなライブ・イベントとして開催しますので、情報収集の場、業界関係者とのコミュニケーションの場としてご利用下さい。

オンライン・インタビュー企画の第一弾は、「検証屋さんが使う検証高速化/効率化ノウハウについて聞いてみる」と題して、検証サービスを手掛けるベリフォア社様よりゲストを招いて開催します。ご興味ある方は是非お気軽にお申し込み下さい。

EDA Express オンライン・インタビュー 第1回

テーマ :検証屋さんが使う検証高速化/効率化ノウハウについて聞いてみる

ゲスト :株式会社ベリフォア 代表取締役 久保田 雄三様

開催日時 :4月27日(火)PM 14:00-15:00 60分間 ※途中入退出可

(12:00〜、14:00〜、16:00〜の中で希望が多い時間で開催します)

参加 :無料、10-20名程度最大20名の参加者を想定しています

インタビュー構成:

・久保田様のプロフィールについて(職歴、趣味など)

・昨今の検証事情について(言語、メソドロジ、世の中のトレンドなど)

・検証現場の課題について

・検証の高速化/効率化について

・VAXEL(バクセル)って何ですか?

※ベリフォア社が取り扱うシミュレーション・アクセラレーター

・参加者からの質問

インタビュアーはEDA Express 菰田が担当。インタビュー終了後は雑談タイムとします。

お申し込み:

こちら(Googleフォーム)よりお願いします。

※オンライン・インタビューに関するご質問等は

こちら までお願いします。

2021.03.26

2021年3月23日、CadenceとGlobalFoundriesは、DFMサインオフ検証環境の整備に関する両社の協業について発表した。

発表によると両社はGlobalFoundriesの12LP、12LP+プロセス向けにCadenceのDFMパターン解析ツール「Cadence® Litho Physical Analyzer」を最適化。

具体的には「Cadence® Litho Physical Analyzer」に搭載されるマシンラーニング機能向けに、GlobalFoundriesがマシンラーニング・モデルを開発し、それらを活用することでDFMホットスポットの検出効率を高めた。その結果、従来のパターンマッチングチェック機能と比較してホットスポットの検出効率を最大33%向上させることに成功。ツールの実行時間はプラス10%未満で抑えることができたという。

GlobalFoundriesは、同社が開発したマシンラーニング・モデルを搭載した「Cadence® Litho Physical Analyzer」を12LP、12LP+プロセスで認証。合わせて12LPプロセス・デザイン・キット(PDK)のアップデート版として、マシンラーニング機能をサポートするためのDFMキットをリリースしたとのこと。なお、2021年第2四半期には12LP+バージョンのDFMキットのリリースも予定しているということだ。

2021.03.26

2021年3月25日に発表されたTrendForce社による2020年ファブレス半導体ベンダ売上ランキング。

※画像はTrendForce社Web上のデータ

COVID-19の影響によりノートPCとネットワーク製品の需要が急増したことにより、それら製品向けのコンポーネントを供給するファブレス半導体ベンダは大きく成長した。上位10社の売上総額は前年比26.4%増、上位10社の中で最も成長したのはNvidiaでが売上は前年比52.2%増だった。

トップのQualcommはクアルコムは、Appleによるベースバンド・プロセッサの再採用、米国によるHuaweiの制裁による他のスマホメーカーの生産増により、Broadcomを追い抜くことができた。2位Broadcomは米中貿易戦争の影響を受けたが、Apple iPhone向けのRFフロントエンド製品の供給がその穴を埋めた。3位のNVIDIAは、Mellanoxの買収によりデータセンター・ソリューションが大幅に強化され、同分野の売上が前年比121.2%増の64億米ドル近くに増加した。

MediaTek、Novatek、Realtekの台湾の3社も、前年比30%増以上の大きな成長を遂げた。やはりノートブックやネットワーキング製品、ドライバーICやTV SoCなど、COVID-19の影響による恩恵に授かった。

AMDはIntelが10nmプロセスで足踏みする中、ノートPC、デスクトップPC、およびサーバーCPU市場に大きく参入し、前年比45%像の97億ドルと大きく成長した。Xilinxは米中貿易戦争の影響で売上を落としたが、直近の四半期ごとの売上推移を見ると順調に売上を回復している。

ファウンドリの容量不足は2021年も年間を通じて続くと予想され、ファブレス半導体ベンダ各社は割り当てられたファウンドリ容量の確保に向けIC製品の見積もりを引き上げる可能性があり、2021年は更なる高収益を実現すると見られる。

2021.03.23

2021年3月22日、組み込み型FPGAならびに推論アクセラレータを手掛けるFlex logixは、資金調達Dラウンドで5500万ドルの調達に成功したことを発表した。

Flex logixによると今回の投資をリードしたのは、PayPal創業者として有名なピーター・ティール氏が創業したベンチャー・キャピタル「Mithril Capital」で、複数のベンチャー・キャピタルがこれに続いた。

同社は組み込み型FPGAでの実績をベースに推論アクセラレータへの投資を進めており、今年半ばには推論アクセラレータ「InferX X1」チップと搭載ボードの量産が開始される予定。Flex Logixは、推論処理における「InferX X1」のスループットの高さを強調しており、それは多数のリコンフィギュラブル・テンソル・プロセッサと同社の特許技術である再構成可能な高帯域ノンブロッキング・インターコネクトを組み合わせた独自のアーキテクチャによるものだとしている。

2021.03.23

2021年3月17日、Synopsysは、IP製品群「DesignWare」の新製品としてPCI Express 6.0の設計および検証IPを発表した。

SynopsysによるとPCI Express 6.0の検証IPは既にリリース済で、コントローラおよびPHY IPは今年Q3より早期顧客に提供し始める予定。

これらIPは、64GT/秒のデータ転送速度、4値パルス振幅変調(PAM-4)、FLIT(Flow control unit)モード、ローパワーステートといったPCI Express 6.0の標準仕様に対応している。

なおコントローラIPは、新しいMultiStreamアーキテクチャにより低レイテンシを実現しており、既存のPCIeコントローラIPと比べて2倍の転送速度を実現。

5nmプロセスのPHY IPは、独自のアナログおよびDSP技術により、チップ間接続、ライザーカード接続、バックプレーン接続時の消費電力を20%削減可能だという。

2021.03.19

2021年3月16日、IC Insightsのレポート:

IC Insightsのレポートによると、7nmと5nm両方のICの量産で真に最先端と見なすことができるのはSamsungとTSMCの2社で、Intelは半導体業界の設備投資競争から脱落している。Intelは過去27年間のうち25年間、設備投資額で上位2位に入っていたが、2020年はSamsungの半額しか投資しておらず、今年もSamsung/TSMCの投資額を大幅に下回る見通し。IC Insightsは、Samsugn/TSMCの両社は今年それぞれ280億ドルを費やすと予想している。

Samsungは2017年以降設備投資額を増やしており、2017年から2020年の設備投資額は計932億ドル。この金額は同時期における中国の半導体企業の全投資額の倍以上に相当。TSMCは直近売上の47%を占める7nmおよび5nmプロセスの規模拡大に向けて設備投資を増やす計画。現在、巨額の設備投資に見合う企業は他にないため、SamsungとTSMCは、先端プロセス技術に関して競合他社との距離をさらに広げる可能性がある。

2021.03.19

2021年3月18日、大阪のAIチップベンチャーArchiTekと商用RISC-VプロセッサIPの大手SiFiveは、ArchiTekの最初の製品となるAIプロセッサ「AiOnIc」について発表した。

発表によると、ArchiTeKの開発したAIプロセッサ「AiOnIc」には、独自のエンジン「ArchiTekIntelligence®PixelEngine(aIPE)」に加えてSiFive社のE3シリーズRISC-VプロセッサIPが搭載されており、CPU、GPU、専用LSIの利点を組み合わせてハードウェアの使用を動的に調整することが可能。このアーキテクチャにより汎用的なCPUやGPUよりも大幅に低電力かつ高効率なAI処理を実現する。

「AiOnIc」はエッジでのAI処理をターゲットとしたプロセッサで非常に小型である事も特徴の一つ。TSMC12nmプロセスで作られるチップのサイズは4.5ミリ角で、その低電力性能によりファンレス設計が可能だという。

ArchiTekの独自のエンジン「ArchiTekIntelligence®PixelEngine(aIPE)」は、予め用意される信号処理、ソート、多機能DMA、行列演算/逆行列演算、FFT向けのエンジンと汎用的なGPUで構成されており、ハードウェア浮動小数点ユニットを含む5ステージ・パイプラインを備えた32ビットRISC-Vプロセッサ「SiFiveE3シリーズコア」と組み合わせることで様々なアルゴリズムに対応することが可能。例えばSLAM処理を汎用CPUの20分の1の時間、OpenPoseを用いた人間の姿勢推定をGPUの3.8倍の速度で処理できるという。

なお、ArchiTekのCEO兼CTOである高田周一氏は、SiFiveE3シリーズコアIPにより、パフォーマンス、電力、およびエリアの目標を達成することができ、SiFiveの設計環境CoreDesignerとSiFiveの代理店DTSインサイトの協力が開発時間の短縮に役立ったとコメントしている。

2021.03.18

2021年3月17日、CadenceはPCBおよびICパッケージ向けSI/PI解析ツールの新製品「Sigrity X」を発表した。

Cadenceによると新製品「Sigrity X」は、「過去10年間で最も重要なSigrity技術のブレークスルー」と称するほど大幅な改良が施されており、シミュレーション速度および設計能力が最大10倍向上。異なる解析ワークフロー間をシームレスに移行することが可能になり、複雑なSI/PI解析のセットアップ時間を短縮できるようになった。

具体的にはシミュレーション・エンジンが再設計され、クラウド処理に対応する3Dソルバー「Clarity」の大規模分散アーキテクチャが取り入れられたほか、ユーザー・インターフェースも刷新され、「Clarity」やPCB設計ツール「Allegro® PCB Designer」、「Allegro Package Designer Plus」との連携も強化された。

Cadenceは「Sigrity X」をSI/PI解析におけるパラダイムシフトだと力説するが、MediaTek, ルネサス, Samsungなどの先行ユーザーも一様に「Sigrity X」の大幅な性能向上を称賛している。

2021.03.17

2021年3月9日、GlobalFoundriesは車載向けのチップ開発に関するBoschとの提携を発表した。

両社が協力して開発するのは車載ADAS向けのミリ波レーダーチップで、チップの製造にはGlobalFoundriesの22FDX RFプロセスを利用する。

GlobalFoundriesは高性能・低消費電力を実現する同社のFD-SOIプロセスを自動車向け半導体分野における強みとして展開しており、既に22nmのFD-SOIプロセスで3億5000万以上のチップ製造実績があるとしている。また、自社をミリ波テスト機能を備えた唯一の半導体ファウンドリとした上で、今回使用する22FDX RFプロセスは自動車レーダーに最適な半導体ソリューションだと主張する。

Boschの22FDXベースのミリ波レーダーSoCは、2021年の後半に市場投入される予定。独ドレスデンにあるファブ1と、米バーモント州バーリントンのファブ9にあるGlobalFoundriesのミリ波テストラボを利用してチップ製造が行われる。

Boschは半導体ベンダを介さず直接半導体ファウンドリとチップ開発を行うことで競合のTier-1サプライヤとの差別化を図る戦略を取っている。Boschは今年後半ドレスデンに独自の300mmウエハ・ファブを開設する計画を発表している。

プレスリリース

2021.03.16

2021年3月16日、パナソニックは、HD-PLC™4 規格に準拠したIPコアのライセンス供与の開始を発表した。

パナソニックが半導体IPのライセンス供与を行うのはIEEE 1901-2020 準拠の第4世代のHD-PLC IPコアで、最大1Gbpsの通信速度を実現する。同IPコアは、電力線通信だけでなく既設の様々なメタル線(制御線、同軸線など)を活用した通信も可能で、無線が届きにくい建物内など幅広い分野での利用が可能となる。

パナソニックは同IPコアのライセンスをソシオネクストに先行供与。ソシオネクストはIoT向けの半導体製品として同IPを用いた製品供給を行う予定。

2021.03.10

2021年3月9日、Synopsysは、京セラドキュメントソリューションズによる同社プロセッサIPの採用事例を発表した。

発表によると京セラは、高性能AI機能を組み込んだ複合機「TASKalfa 3554ciシリーズ」のSoC開発で、Synopsysの「DesignWare ARC EV6x Embedded Vision Processor IP」を採用。512ビット・ベクターDSPとCNNエンジンを搭載した同IPのソフトウェア開発には、専用環境「MetaWare EV Development Toolkit」を、SoCの開発にはFPGAベース・プロトタイピング・ソリューション「HAPS®」を活用し、SoCの一発完動に成功した。

複合機「TASKalfa 3554ciシリーズ」は、解像度の低い画像を元の解像度よりも高い解像度に変換し美しく印刷する機能や、書き文字を認識してその部分のみを強調して読みやすく印刷する機能など、AIベースの機能が備えられているという。

京セラでは今回の成果を受け、次のSoC開発プロジェクトでもARC EV71プロセッサIPとDNNオプションの組み合わせを検討しているという。

2021.03.10

2021年3月9日、RISC-Vベースのオープンソースコアを提供する非営利組織「OpenHW Group」と研究支援を目的としたカナダの非営利組織「Mitacs」は、RISC-Vプロセッサの共同研究開発プログラムを発表した。

OpenHW Groupは、RISC-Vベースのオープンソースコア「CORE-V」ファミリを提供する非営利組織で、「CORE-V」と合わせて関連するIPおよびソフトウェア・ツールの設計・開発のコラボレーション促進を行っている。現在50以上の企業・団体がメンバーとして加盟しており、日本からは唯一NECがメンバーとして活動に参画している。

Mitacsは、カナダ政府が出資する科学分野の研究支援を行う非営利組織でOpenHW Groupのメンバーでもある。

今回、OpenHW GroupとMitacsが発表したのは、オープンソース・ハードウェアの研究を行う「OpenHW Accelerate」と呼ぶ共同出資の複数年研究プログラムで2,250万ドルの予算が組まれている。

「OpenHW Accelerate」の最初のプロジェクトとして開始される「CORE-VVEC」は、RISC-Vベクトル・プロセッサのアーキテクチャ最適化に取り組む研究活動で、高スループットの多次元センサーデータ処理とエッジでのMLアクセラレーションをターゲットとしている。このプロジェクトは、カナダのCMCマイクロシステムズがスポンサーとなり、国際的な半導体およびソフトウェア・エンジニアリングの研究機関、Polytechnique MontréalとETHチューリッヒが3年間の共同研究として活動する。

「OpenHW Accelerate」プログラムと「CORE-VVEC」の詳細は、3月18日にOpenHW Group主催の

ウェビナーで発表される予定。

なお、OpenHW GroupとMitacsは、今後数か月以内に、産業界のスポンサーと学術機関を組み合わせた幾つかの新しい「OpenHW Accelerate」プロジェクトを発表する予定だという。

2021.03.10

2021年3月9日、IC Insightsのレポート:

IC Insightsは、2021年Q1の世界半導体市場の成長率を2020年Q4に対して2%増と予測している。予測通りの成長となると、Q4からQ1へにかけてのプラス成長という意味で10年ぶりの実績となる。その後、2021年Q2からQ4までフラットな形で市場が維持されると2021年の成長率は前年比12%増となる。

IC Insightsは、2021年Q2に3%増、Q3に8%増、Q4はフラットという新たな予測を示しており、その通りの成長となると2021年の成長率は前年比19%増となる。

しかし、調査会社の予測とはかなり水もので、IC Insightsは昨年4月時点で2020年の予測を3%のプラス成長から4%のマイナス成長に修正。同じく調査会社のGartnerもマイナス成長を予測していたが、結果的に2020年は前年比6.5%増という結果に終わった。

現在のところ今年の半導体市場は大きく伸びるというのが、業界関係者の共通した見立てとなっている。

2021.03.10

2021年3月9日、組込み型FPGAを手掛ける米Achronixは、同社の組込みFPGA IPの出荷数が1000万個に到達したことを発表した。

Achronixの提供する組込み型FPGA「Speedcore」は、FPGA機能をASIC/SoCに統合するもので、柔軟なアーキテクチャでFPGAロジック、メモリ、DSP処理機能の量を定義できる。スタンドアロンのFPGAを使用する場合と比較して、組込み型FPGAはデバイス・コストを最大90%、電力を最大75%削減すると同時に、インターフェイス帯域幅を10倍に増やせるとAchronixはうたっている。また組込み型FPGAは、機能変更、機能追加に柔軟に対応できるためASIC/SoCの製品ライフサイクルの延長という面でも大きなメリットをもたらす。Achronixによると同社の「Speedcore」は、AIワークロードをサポートする必要がある高性能データアクセラレーション・アプリケーションに採用されているという。

Achronixは元々Intelプロセスで製造するスタンドアロンのFPGAで事業を立ち上げた会社で、組込み型FPGAとスタンドアロンのFPGAの両製品を供給している。

組込み型FPGA「Speedcore」は、現在TSMCの16FFC、12FFC、N7プロセスをサポート。N5プロセス向けIPも開発中とのこと。

なおAchronixは、2021年1月にACE Convergence Acquisition Corp. (Nasdaq: ACEV)との合併契約を発表。合併後にNasdaqに上場する予定となっている。

2021.03.10

2021年3月9日、Accellera Systems Initiativeは、3月1日から4日までオンラインで開催していた「DVCon US 2021」のアワード受賞者と来場者数を発表した。

DVConは、電子回路の設計および検証技術に関するカンファレンスで今回で33回目の開催となる。例年カリフォルニア州サンノゼで開催されていたが、昨年からCOVID-19の影響によりオンラインでのバーチャル・イベントとして開催されている。

カンファレンスの主催者Accellera Systems Initiativeによると、今回のDVCon US 2021への参加者数は計1,329人。スポンサーとして20社が出展した。

カンファレンス参加者による投票で選ばれたベスト・ペーパーは以下の通り。

1位:Formal Verification Experiences: Spiral Refinement Methodology for Silicon Bug Hunt

Siemens EDA(Mentor Graphics)による発表

2位:Advanced UVM, Multi-Interface, Reactive Stimulus Techniques

Paradigm WorksおよびHMC Design Verificationによる発表

3位:Open-Source Framework for Co-Emulation Using PYNQ

Amiq Consultingによる発表

なお次回のDVCon US 2022は、2022年2月28日から3月3日、サンノゼでの通常開催が予定されている。

2021.03.08

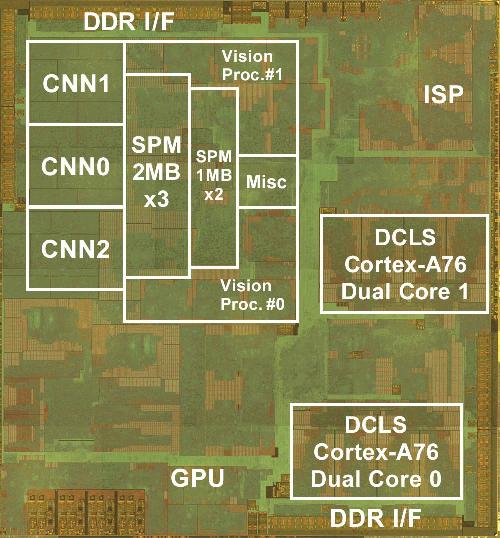

2021年2月17日、ルネサス エレクトロニクスは、同社が開発した自動運転向けのプロセッサ技術について発表した。

ルネサスが開発したプロセッサ技術は下記3つで、これら技術は既に昨年製品化されている車載用SoC「R-Car V3U」に適用済み。ルネサスはそれら技術の詳細について2月に開催されたISSCC(International Solid-State Circuits Conference)で発表した。

(1)60.4TOPSのディープラーニング性能と13.8TOPS/Wの電力効率を実現したハードウェア・アクセラレータ・コア

(2)偶発的に発生するハードウェア故障を高速に検出、制御する高度なセーフティメカニズム

(3)SoC上で混在する異なる安全性レベルのソフトウェアタスクを相互干渉なく動作させる機構

ルネサスによると開発したアクセラレータはCNN専用アクセラレータで、「R-Car V3U」には同アクセラレータを3個搭載。アクセラレータ専用のメモリを計6MB(1コアあたり2MB)搭載することでCNN処理における外付けDRAMとの転送データ量を9割以上削減。高いCNN処理性能と優れた電力効率を世界最高レベルで両立できたとしている。

また、ランダムなハードウェア故障を高速に検出、制御するセーフティ・メカニズムを搭載した「R-Car V3U」は、信号処理の大部分において機能安全規格ISO26262 ASIL Dのメトリクスを達成見込みでSoC単独の自己診断が可能。ソフトウェアタスク間の無干渉(FFI)支援機構は、SoC内のインターコネクトを流れる全データを監視し、動作する全てのタスク間の不正なアクセスを遮断することができるという。

※画像はルネサス社ホームページ上のデータ

2021.03.05

2021年3月3日、Synopsysは新製品「Euclide」のリリースを発表した。

Synopsysの発表によると「Euclide」は設計と検証の生産性を向上させる次世代のHDL統合開発環境という事。RTL設計者が利用するフロントエンドのHDLエディタとして、様々な便利機能を提供してくれるようだ。

主な機能の一つとして紹介されている「インタラクティブ解析/インクリメンタル解析機能」は、デザインおよびテストベンチをコーディングしながらオンザフライでインクリメンタル・コンパイル、エラボレーション、疑似シンセシス、ルールチェックを行う機能で、設計早期段階でコードのバグを発見・修復可能。SystemVerilogならびにUVM(Universal Verification Methodology)のコンプライアンス・チェックが可能だという。

また「自動補完機能/コンテント・アシスト機能」は、HDLのコーディング効率を上げコードの品質を高める機能で、シミュレータ「VCS」、デバッグ環境「Verdi」、エミュレーター「ZeBu」向けに最適なHDLコードをコーディングできる。「Euclide」にはその他にもリファレンス機能やコードの表示、ナビゲート機能など、HDLコード開発に関する豊富な機能を備えている。これら「Euclide」の機能は、Youtubeでトレーニング・ビデオが公開されているので、それを見るとイメージしやすいだろう。

2021.03.05

2021年3月4日、組込みソフトの開発環境を手掛けるIARSystemsは、同社の「Embedded Workbench® for RISC-V」が機能安全規格の認証を取得したことを発表した。

IAR Systemsによると「Embedded Workbench® for RISC-V」は、「IEC 61508」および「ISO 26262」の2つの機能安全規格の認証を取得。

この認証には、医療ソフトウェアおよび医療機器内のソフトウェア開発に関する国際規格「IEC 62304」、欧州鉄道規格「EN50128」、「EN50657」、家庭用電化製品向け規格「IEC60730」、機械制御システム向け規格「ISO 13849」、「IEC62061」も含まれているという。

「Embedded Workbench® for RISC-V」は、RV32/RV32E 32ビットRISC-Vコアおよび拡張命令をサポート。米SiFive、中国Nuclei System Technology、中国GigaDeviceなど各社のRISC-Vコアもサポートしている。