NEWS

2019.03.28

2019年3月26日:IC Insightsのレポート:

調査会社IC Insightsのレポートによると、2018年のファブレス半導体ベンダの総売上額は約1,094億ドルで、その68%は米国に本社を置く企業が占めている。(2010年時点での米国企業の売上シェアは69%)

売上シェア2位は台湾で16%、以下中国13%、欧州2%、日本1%と続く。この順位構成は2010年から変わっていない。

最も売上シェアを伸ばしているのは中国だが(2010年の5%から2018年は13%)、HiSilicon, ZTE, Datang(社内消費)を除くとシェアは7%。

日本企業として2018年ファブレス半導体ベンダ売上トップ50に入ったのはメガチップスだけで、2018年の売上は19%増の7億6000万ドル。

2018年の世界ファブレス半導体ベンダの売上は、前年比8%(83億ドル)増加。TOP50社のうち21社が2桁成長を記録。中国企業BitMain、ISSI、Allwinner、HiSilicon、そして米Nvidiaの5社は前年比25%以上の成長を記録した。マイニングファームのBitmainは前年比197%増、直接チップ販売を行なっていない同社の売上はTSMCからのチップ購入額。Bitmainはマイニング機器市場の84%を占めており、TSMCの中国向け売上の変動は同社の業績が大きく影響している。

2019.03.27

2019年3月25日、Electronics Weekley.comの記事:

コンサルティング会社Semiconductor Intelligenceによると、今年の世界半導体市場は前年比10%減のマイナス成長となる見通し。

価格の下落と需要の後退が進むメモリを除いても前年比2%減のマイナス成長になると同社は予測している。

Semiconductor Intelligenceによると、大手半導体ベンダの2019年Q1の業績はQualcommとInfineonを除いて軒並み減少する見通し。

特にメモリ大手のSamsung,Micron,SK Hynixは大幅に業績が悪化している。

今年に入って発表された各社各団体による2019年世界半導体市場の予測は以下の通り。

・Morgan Stanley 5%のマイナス成長

・VLSI Research 1%のマイナス成長

・Gartner 2.6%のプラス成長

・IC Insights 1.6%のプラス成長

・WSTS 3%のマイナス成長

・Semiconductor Intelligence 10%のマイナス成長

なお、2020年については現時点で以下のような予測が発表されている。

・VLSI Research 7%のプラス成長

・Gartner 8.1%のプラス成長

・IC Insights 1.9%のマイナス成長

・Semiconductor Intelligence 5-10%のプラス成長

2019.03.26

2019年3月21日、Synopsysは、同社のARCプロセッサ向けのembARC マシンラーニング推論(MLI)ソフトウェア・ライブラリの提供開始を発表した。

発表によるとembARC MLIソフトウェア・ライブラリは、ARCプロセッサへの各種ニューラルネットワークの実装を最適化するためのライブラリで無償で提供される。

embARC MLIソフトウェア・ライブラリがサポートするのは、低消費電力プロセッサ「ARC EMxD」および「ARC HS4xD」で、同ライブラリを用いる事で畳み込みニューラル・ネットワーク(CNN)ならびに再帰型ニューラル・ネットワーク(RNN)を使用する低消費電力IoTアプリケーションの実装を最適化できる。

Synopsysは同ライブラリの適用効果として以下を挙げている。

・消費電力とメモリー面積を抑制しつつ、LSTM、プーリング層、正規化線形関数などの活性化関数や各種推論実行手順を効率よく実装可能

・ARC EM9D上で実行するCIFAR-10などのベンチマークは、同クラスの他製品と比べて処理サイクル数を1/4にまで削減

・RNNやLSTMセルといった様々なニューラル・ネットワーク層の性能が3?5倍に向上、2次元畳み込み層の性能は最大16倍に向上

embARC MLIソフトウェア・ライブラリはARCユーザー向けのコミュニティWeb「embARC.org」より入手可能。

2019.03.22

2019年3月18日、Synopsysは新型のフィジカル検証ツール「IC Validator NXT」のリリースを発表した。

発表によると「IC Validator NXT」は大規模分散処理アーキテクチャにより、2,000個以上のCPUで分散処理を行うことが可能。Synopsysはフルチップのフィジカル検証サインオフを数時間で完了、最先端プロセス・ノードでのフィジカル検証サインオフにかかる期間を1/2に短縮できるとしている。また、新技術「Explorer DRC」によってSoC統合時のDRCの実行速度が5倍に高速化。同技術はDRC時のヒートマップ表示により、デバッグにかかる時間も大幅に削減できるという事だ。

Synopsysによると、既に複数のユーザーがクラウド上で「IC Validator NXT」を用いてフィジカル検証サインオフを行い成果を上げているという話。「IC Validator NXT」には、数秒以内でDRCのフィードバックを行う「Live DRC」という「Custom Compiler」との連携機能が備えられている。

2019.03.20

2019年3月13日、Synopsysは新型の論理合成ツール「Design Compiler NXT」の提供開始を発表した。

Synopsysによると「Design Compiler NXT」は、新しい最適化技術の利用により実行スピードならびに消費電力とタイミングの結果品質が大幅に向上。同ツールを先行して利用していた早期適用企業での実績として実行スピードが2倍、結果品質が10%向上したケースもあるという。

今回新たに以下のような最適化技術が「Design Compiler NXT」に搭載された。

・パワードリブンのマッピングならびに論理構築テクニック

・クロック/データ同時最適化

・結果品質を犠牲にすることの無い分散合成処理

なお、「Design Compiler NXT」は、IC Compiler II との間でライブラリや配置テクノロジの他に、RC 抽出、ネット・トポロジー、密度モデリングといったテクノロジを共有しており、5nm以降の最先端プロセス・ノードでも両ツール間の設計結果で緊密な相関性と結果品質を実現できるという。

2019.03.19

2019年3月15日、Baiduは、サンノゼで開催していたOpen Compute Project 2019グローバルサミットにて、Facebook, Microsoftと協力してOCP Accelerator Moduleの仕様定義に取り組むことを発表した。

OCP(Open Compute Project)は、2011年にFacebookが立ち上げたデータセンター向けのオープンソースのハードウェア開発プロジェクトで、OCP Foudationには、Facebook, Google, Microsoft, Intel, AMDなど計200社が参加している。

今回Baiduが仕様定義をアナウンスしたOCP Accelerator Module(OAM)は、AIアクセラレータの開発期間の短縮とその導入のスピードアップを目指して考案されたオープンなAIアクセラレータ・アーキテクチャで、AIアクセラレータ間の相互運用性の実現するもの。発表によるとBaidu, Facebook, Microsoftの3社は協力してOAMの仕様定義を主導し、OCPのメンバーである大手インターネット企業やAIアクセラレータの開発ベンダらがこれをサポートしていくという。

なおOpen Compute Project 2019グローバルサミット関連の話題としては、MicrosoftがAzureで使用しているデータ圧縮アルゴリズムとハードウェア(Verilog-RTLコード)をオープンソース化してOCPに寄託した事が報じられている。

2019.03.14

CEVAのDSPがDJIのフラッグシップ・ドローンに採用される、AI、コンピュータビジョン、長距離通信で利用

2019年3月12日、CEVAはドローン大手DJIによる採用事例を発表した。

発表によるとDJIはコンスーマ向けドローンの最上位機種「Mavic 2」にてCEVAのDSPを採用。

ディープラーニング、コンピュータビジョン、長距離通信と複数の用途で数種類のCEVAのDSPを利用しているという事だ。

DJIは以前から各種ドローンにCEVAのDSPを採用している。

2019.03.13

※追記あり

インターコネクトIPというビジネスを根付かせたとも言える、老舗のIPベンダ米SONICSが静かにその歴史に幕を閉じた。

詳細は明らかにされていないが、現在のSONICSのWebページを見ると事業の縮小がひっそりとアナウンスされている。

昨今、SoCのインターコネクト技術は、SoC設計の鍵を握るコア技術として大企業による囲い込みが進んでいる。2013年にはArteris社のインターコネクト技術とIP開発チームをQualcommが買収。昨年はIntelがインターコネクトIPのNetSpeed Systemsを買収した。この流れを踏まえると、SONICSもどこかの企業に買収された可能性が高い。だとすると一体どこが?

昨今の自動運転やAIを睨んだチップ開発競争の激化を考えると、AI用の独自チップの開発を進めているというGAFAMのどこかがSONICSを買収したと考えても不思議ではない。

※追記

米EETimesはSONICSを買収したのはFacebookであると報じている。

https://www.eetimes.com/document.asp?doc_id=1334429#

2019.03.13

2019年3月12日、Linux Foundationは、チップ設計に関連する高品質なオープンソース・コードをホストおよびキュレートする「CHIPS Allianceプロジェクト」の設立予定を発表した。

発表によるとCHIPS Allianceを支援する初期メンバーは、Esperanto Technologies、Google、SiFive、Western Digitalの4社。各社はいずれも、オープンソース・ハードウェアおよびRISC-Vアーキテクチャの推進・発展に賛同しており、CHIPS Allianceを通じてオープンソース・チップの設計環境、言い換えるとRISC-Vアーキテクチャの実装環境の整備に力を注ぐ予定。RISC-Vという命令セット・アーキテクチャそのものを整備・促進するRISC-V Foundationに対し、CHIPS Allianceはその実装を受け持つというスタンスとなる。

CHIPS Allianceによると既に下記2つの初期プロジェクトが動いており、今後はRISC-Vコア、設計ツール、検証メソドロジなどにフォーカスして今年の夏以降に活動が活発化される予定。

・Universal Verification Methodology (UVM)-Based Stream Generator Environment for RISC-V Cores

RISC-Vコア向けのUVMベース検証環境。Googleが開発中でCHIPS Allianceに提供される予定。

・SweRV Core

RISC-Vベースの32ビット、9ステージパイプラインのコア。Western Digitalが開発しており、コアと合わせてテストベンチ、ISSがCHIPS Allianceに提供される予定。

Western Digitalは、キャッシュ・コヒーレンス・プロトコル「OmniXtend」の仕様と実装コードも提供する予定。

2019.03.13

2019年3月12日、SEMIは半導体ファブへの設備投資の見通しを発表した。

発表によると今年の半導体ファブ(前工程)への設備投資額は前年比19%減の530億ドルと落ち込む見通し。しかし来年は前年比27%増と大きく成長し過去最高となる670億ドルに達すると予測されている。

メモリ需要の浮き沈みが設備投資にも大きく影響しており、2018年まではメモリ向けの設備投資が全投資額の約55%を占めていたが今年は45%に縮小。2020年には再び55%程度になると見られている。一方でファウンドリ向けの設備投資額は向こう2年間は約30%のシェアが安定的に維持される見通し。

2019.03.12

2019年3月11日、Alibaba, Cisco, Dell EMC, Facebook, Google, Hewlett Packard Enterprise, Huawei, Intel, Microsoftの9社は、データセンター向けの新たな高速通信用インタフェース規格「Compute Express Link (CXL)」の標準化活動の開始をアナウンスし、「CXL Specification 1.0」を公開した。

「CXL」規格は「CCIX」と同種のチップ間インターコネクト仕様で、プロセッサとハードウェア・アクセラレータ間の高速な相互接続とメモリー・コヒーレンシの向上を目指すもの。今回公開された「CXL Specification 1.0」は、PCI Express 5.0の技術をベースにIntelが中心となり開発したもので、下記の3つの主要なプロトコルを提供する。

1. I/O Protocol

2. Memory Protocol, initially allowing a host to share memory with an accelerator

3. Coherency Interface

先行している「CCIX」規格との違いや互換性などの詳細は不明だが、少なくとも「CXL」はPCI Express 4.0ベースの「CCIX」の次を狙う規格のようで、今のところ標準化団体「CXL Consortium」に名を連ねるチップベンダはIntelのみという状況から、その背景にはチップ・ベンダの政治的な争いも見え隠れする。(CCIXにはAMD, Arm, Mellanox, Qualcomm, Xilinxが加盟)

2019.03.12

2019年3月11日、NVIDIAはイスラエルのファブレス半導体ベンダMellanox Technologiesとの買収合意を発表した。

発表によるとNVIDIAはMellanoxの発行済み株式を1株当たり125ドルで現金で取得する予定。これは企業価値として約69億ドル相当。先週末金曜日の終値時点ではMellanoxの企業価値は約59億ドルだった。

MellanoxはネットワークスイッチやNICを手掛けるファブレスベンダで、HPC向けインターコネクト「InfiniBand」ソリューションで有名。NVIDIAによるとMellanoxのInfiniBandはスパコンTOP500のうち250以上が採用しているとの事。最新のスパコンランキングのツートップであるSummitおよびSierraはいずれもMellanoxのInfiniBandを利用している。

Mellanox買収の噂は当初はMicrosoft、その後Xilinx、そしてIntelと数々の社名が挙がっていたが、最終的にはNVIDIAがIntelに競り勝ち買収合意を取り付けた様子。両社の買収手続きは2019年末までに完了する予定。NVIDIAは売上の約3分の1がデータセンター向けで、今回の買収によりデータセンター向け事業をさらに強化する。

2019.03.09

2019年3月8日、Fudzillaの記事:

TSMCの2019年2月の売上は前年比22%減の19.7億ドルで22ヵ月ぶりの低水準。2月までの累計売上は前年比3.7%減となった。

TSMCは第1四半期の売上予測を73-74億ドルから70-71億ドルに下方修正した。

TSMCは元々市場の需要停滞から第1四半期の売上を前年比10%減程度と予測していたが、1月に発覚した欠陥フォトレジストの影響が更にTSMCの業績を悪化させた。

2019.03.08

今年の半導体売上ランキングはSamsungの大幅な減収でIntelが首位に返り咲く

2019年3月8日、IC Insightsのレポート:

2019年の半導体売上ランキングはIntelが首位に返り咲く。2017年からメモリの活況で首位の座を維持していたSamsungは、メモリ市場の急落によりIntelに首位の座を明け渡す。

IC Insightsの予測によると、2019年はメモリ市場が24%下落し、半導体市場全体の売上を7%引き下げる見通し。Samsungの半導体売上高の83%がメモリであることから、メモリ市場の低迷は今年の同社の半導体売上高全体を20%引き下げると予想される。

IC InsightsはSamsungと同様にSK Hynix, Micron, TOSHIBAについても今年の売上が20%以上減少すると予測。2017年の実績を割り込む可能性もあるという。

2019.03.06

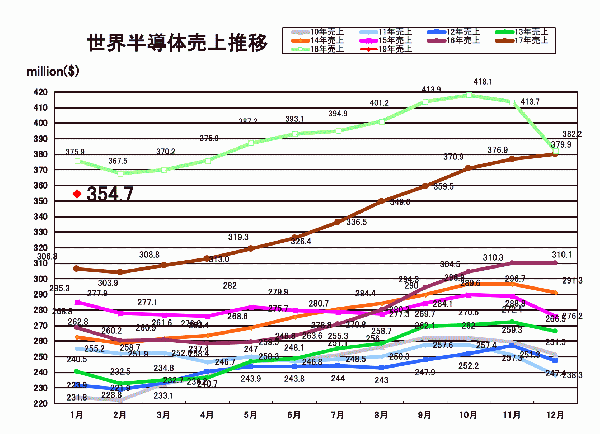

2019年3月4日、米SIA(Semiconductor Industry Association)は、2019年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2019年1月の世界半導体売上は前年同月比5.7%減、前月比7.2%減の354.7億ドルだった。売上が前年実績を下回るのは2年半振り。11月以降3ヶ月連続で売上減となった。

2019年1月の売上を地域別で見ると、全ての地域で12月の実績を下回り、欧州以外全ての地域で前年実績を割り込んだ。

最も売上が落ち込んでいるのは北米市場で、前月比13%減、前年比15.3%減となっている。

日本市場の1月の売上は前年比1.5%増、前月比4.7%減の31.6億ドル。売上を円ベースで換算すると前年比約3.2%減の約3442億円となる。

なお、WSTSが昨年11月に発表した秋季予測では2019年の成長率を2.6%のプラス成長と予測している。

※SIA

2019.03.05

2019年3月4日、Cadenceは新製品となるLPDDR5 IPのリリースを発表した。

発表された新製品の正式名は、「Cadence® Denali® Gen2 PHY IP for LPDDR5/4/4x」でTSMC 7nm FinFETプロセス向けの製品。LPDDR5はLPDDR4の倍のデータ転送速度を実現するメモリ規格で、今回LPDDR5と合わせてLPDDR4, LPDDR4xのPHY, コントローラ, 検証IPが用意された。

LPDDR5規格は今年2月にJEDECが公開したばかりだが、昨年からSamsungが先行して製品化を進めている。

2019.03.04

2019年2月19日、CadenceはGreen Hills Softwareとの協業について発表した。

発表によるとCadenceはGreen Hillsに対しGreen Hillsの所有持分の約16%に相当する1.5億米ドルを出資。合わせてCadenceのCEOであり著名な投資家としての顔を持つLip-Bu Tan氏がGreen Hillsの役員会のメンバーに就任した。両社は互いの強みを生かし、組み込みシステムのセーフティおよびセキュリティの推進に向けて戦略的に協業していくという。

Green Hillsのソリューションは国内では組み込みシステムの統合開発環境やリアルタイムOSなどが有名。CadenceによるとGreen Hillsの製品は、車載分野ではトヨタやフォードなどのOEM、tier-1顧客、航空宇宙および防衛分野ではボーイングやロッキード・マーティンなど、様々なアプリケーション分野において幅広く採用されているとのこと。Cadenceは今回のGreen Hillsとの協業により、推定30億米ドル規模の組み込みセーフティおよびセキュリティ市場において新たなビジネスの拡大を目指すという。

2019.03.04

2019年2月20日、SynopsysはSamsungファウンダリとの最先端プロセスに関する協業成果について発表した。

発表によるとSamsungは、Synopsysの配置配線ツール「IC Compiler II」を中心とした「Fusion Design Platform」を用いて、GAA(gate-all-around)FETと呼ばれる次世代トランジスタ構造のテストチップのテープアウトに成功した。最新の情報によるとSamsungは、3nmノードのGAAFETトランジスタの量産を2021年から開始する計画となっている。

SamusungはSynopsysと組むことで新たなGAAFETプロセスをターゲットとする配置配線およびパターニングのための設計プラットフォームを実現。各ツールの緊密な連携によって実現されるSynopsysのインプリメンテーション技術および最適化技術が、Samsungの最新プロセス・ノードの実用化に向けて大きく貢献したという。

2019.03.04

2019年2月27日、中国のAIチップベンチャーHorizon Roboticsは、資金調達Bラウンドで6億ドルの資金調達に成功したことを発表した。

発表によると今回の投資ラウンドを主導したのはSK Hynixと主要な自動車セクターのグループで、既存の投資家もこれに加わった。今回の投資に参加したかどうかは不明だが、Horizon Roboticsのパートナーには、AUDI、BOSCH、BYD、SAIC Motorなど自動車関連の主要企業が名を連ねている。ちなみにHorizon Roboticsは2017年に資金調達Aラウンドで1億ドルを調達しているが、この時はIntel Chinaがラウンドを主導した。

Horizon Roboticsはエッジ向けのAIプロセッサを手掛けるベンチャーでチップと合わせてコンピューティング・プラットフォームも開発している。同社が狙うのは自動運転とIoTで、すでに自動運転向けの「Journey」、IoT向けの「Sunrise」、2種類のAIプロセッサを製品化しており、それらプロセッサとハードウェア、ソフトウェアを組み合わせた自動運転向けのプラットフォーム「Matrix」とエッジAIコンピューティング向けのプラットフォーム「XForce」も提供している。「Matrix」はCES 2019 Inovation Awardを受賞しており、すでに自動車分野の主要企業に供給されているほか、「Sunrise」はXiaomiの「Mi AI Speaker」で採用されるなど既にビジネスの実績がある。

Horizon Roboticsは今回調達した資金を研究開発および製品開発に充て、来年には新世代のプロセッサをリリースする計画。

2019.03.04

2019年2月19日、AIチップを手掛けるシリコンバレーのベンチャーWave Computingは、「MIPS Openアドバイザリー・ボード」の設立を発表した。

MIPSは昨年12月に同社の保有するMIPS命令セットアーキテクチャのオープンソース化の計画を発表しており(関連ニュース)、今回の「MIPS Openアドバイザリー・ボード」の立ち上げは、MIPSオープンソース化に向けた第一歩となる。

Wave Computingによると「MIPS Openアドバイザリー・ボード」は、MIPSアーキテクチャをターゲットとしたエコシステムの標準化を目指す非営利団体「prpl Foundation」内のメンバー委員会として設置される。「prpl Foundation」はImmagination Technologiesの主導で組織された団体で、MIPSコア運用のためのオープンソースのソフトウェア・フレームワークやAPIなどを整備している。当面「prpl Foundation」は、「MIPS Openアドバイザリー・ボード」のインキュベーション組織として機能し、将来的には「MIPS Openアドバイザリー・ボード」の独立化が検討される見通し。

「MIPS Openアドバイザリー・ボード」では、MIPSアーキテクチャのオープンソース化に向けたライセンス契約の形態やメンバーシップの要件、コミュニティのガバナンス構造、MIPS Open Certified™製品の基準などの定義が進められる予定で、Wave Computingおよび「prpl Foundation」は、現在同アドバイザリー・ボードのメンバーを募集している。

2019.03.01

2019年2月27日、Cadenceはレーダー/ライダー、通信向けDSPコアの新製品「Tensilica ConnX B20」を発表した。

CadenceのDSPコア「Tensilica ConnX」ファミリは元々は通信向けのDSPとして展開していた製品で、その後需要の高まりを受けレーダー/ライダー向け処理にも対応するDSPとして製品が拡張された経緯がある。

Cadenceによると新製品「Tensilica ConnX B20」は、ISA(命令セットアーキテクチャー)の強化、クロック速度の向上により、市場で普及している前世代製品「Tensilica ConnX BBE32EP DSP」と比較して、通信処理チェーンの各処理を最大30倍、レーダー/ライダーの処理チェーンの各処理を最大10倍高速に処理する事が可能。他のConnX DSPファミリーとソフトウェアの互換性があり、基本スペックは以下の通りとなっている。

・512ビットのベクター幅で最大128 MACの処理性能

・各サイクル1024ビットのデータをロード可能

・16nmプロセスで1.4GHzを超える動作周波数を実現

・演算性能

−ネイティブで複素数に対応する32ビットの固定小数点演算

−ネイティブで複素数に対応する32ビットの浮動小数点演算(拡張オプション)

−単精度/半精度のベクター浮動小数点(VFPU)演算

Tensilica ConnX B20のブロック図(Cadence web上のデータ)

なお、Cadenceは「Tensilica ConnX B20」と合わせて、256ビットのベクター幅で最大64MACの処理性能を備える「Tensilica ConnX B10」も発表している。いずれの製品も2019年Q2に一般リリースされる予定。

2019.03.01

2019年2月27日、IC Insightsのレポート:

IC Insightsによると、2009-2018年の10年間で閉鎖または転用された半導体ウエハ工場は計97。

その大半が200mm以下のウエハ工場で、地域別にみると最も多いのは日本で計36の工場が閉鎖・転用された。

2018年には3つの工場が閉鎖・転用されたが、そのうち2つはルネサスの工場だった。

ウエハ工場のコスト上昇を考えると半導体ベンダのファブレス化は今後も進み、今後数年間でさらにいくつかの工場が閉鎖される見通しで、ルネサスは今後も大津、宇部の2工場を閉鎖・転用する計画がある。

ウエハ工場の閉鎖・転用が進み、新たな工場が立ち上がらない状況をみると、日本の半導体設備投資のシェアが僅か5%である事は不思議ではない。

2019.02.27

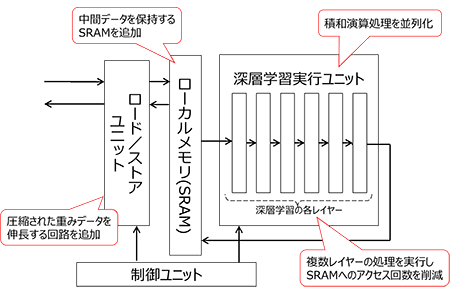

2019年2月26日、東芝デバイス&ストレージ株式会社は新たに開発した車載向け画像認識SoCについて、米国サンフランシスコで開催中の「ISSCC(International Solid-State Circuits Conference) 2019」で発表した。

発表によると今回東芝が開発した画像認識SoCにはディープニューラルネットワーク・アクセラレータが搭載されており、これまでのSoC「Visconti 4」と比較して処理速度は約10倍、電力効率は約4倍を達成。東芝が発表した論文タイトルからすると、新開発の画像認識SoCの演算性能は20.5TOPS、チップ面積当たりの演算性能は217.3GOPS/mm2となるようだ。(Visconti 4の演算性能は1.9TOPS)

東芝の説明によると開発したDNNアクセラレータは、256個の積和演算ユニットを搭載したプロセッサを4つ保持しており、積和演算プロセスの並列化により演算性能を向上。さらに電力効率を向上させる手立てとして、以下のようなローパワー策を講じた。

・中間データを保持するローカルメモリ(SRAM)を演算実行ユニットの近くに配置し、そのSRAMに収まるように深層学習の推論処理を分割することでDRAMへのアクセス回数を削減

・重みデータを事前に圧縮して保存し、読み込み時用のデータ伸長回路を追加することで、重みデータの読み込みに使用するデータ量を削減

・推論処理の各レイヤーをパイプライン接続し1回のSRAM参照で複数レイヤーの処理を実行

東芝は今回開発したSoCの精度や消費電力を更にブラッシュアップし、車載向け画像認識AIプロセッサ「Visconti 5」として2019年9月にサンプル出荷の予定。同SoCは自動車の機能安全規格ISO 26262にも対応しているという。

2019.02.26

2019年2月25日、エッジ向けAIプロセッサを手掛けるベンチャー米Syntiantは、同社初となるAIプロセッサ製品「Syntiant™ NDP100™」および「Syntiant NDP101™」を発表した。

Syntiantの開発する「NDP(Neural Decision Processor)は、独自のアナログ・ニューラルネットワーク技術とフラッシュメモリを利用したメモリ・セントリック・アーキテクチャにより、超ローパワーで電力効率の高いAI処理を実現するのが特徴。Syntiantによると「NDP100」は稼動時の消費電力がわずか200μW以下で「NDP100/101」は、他のプロセッサよりも1桁から2桁高い電力効率で常時オンの音声認識を実現可能。同IPを用いる事で、補聴器からラップトップ、スマートスピーカーまでほぼ全てのバッテリ駆動機器に常時オンの音声インタフェースを追加できるとしている。

なお、ユーザーはSyntiantの用意する「TDK(training development kit)」を用いる事で、ディープニューラルネットワークをNDPへダイレクトに実装する事が可能。TDKは、TensorFlowなどの業界標準の機械学習フレームワークをサポートしている。

Syntiantは昨年2度の資金調達に成功しIntel, Microsoft, Amazon, Motorolaなどから数千万ドルを調達。NDPを用いた製品開発でInfineon Technologiesと契約を結んでいる。

2019.02.22

2019年2月20日、Synopsysは、2019会計年度第1四半期(18年11-19年1月)の四半期決算を報告した。

発表によるとSynopsysの2019会計年度Q1の売上は、前年同時期比約14.1%増、前Q4比約3.2%増の8億2040万ドルで同社の四半期売上記録を更新した。四半期売上記録の更新はこれで5四半期連続。営業利益は前年の370万ドルの赤字から1億5350万ドルの黒字へと大きく伸ばした。(※GAAP基準による会計結果)

Synopsysの2019会計年度Q2(19年2月-4月)の売上を8億1000万-5000万ドルと予測している。

2019.02.22

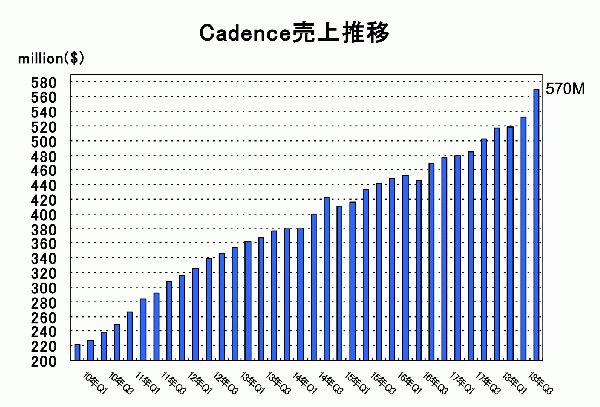

2019年2月20日、Cadenceは、2018会計年度第4四半期(2018年10-12月)の売上を報告した。

Cadenceの2018年Q4売上は、前年比約13.5%増、前期Q3比約7.1%増の5億7000万ドルで9四半期連続で四半期売上記録を更新した。営業利益は前年比約2%減の9800万ドルだった。(※GAAP基準による会計結果、2018年と2017年は会計ルールが異なる)

新しい収益算出ルールに基づいたCadenceの2018会計年度の売上は、前年比約10%増の21億3800万ドル、営業利益は前年比約1%減の3億4600万ドルだった。(※GAAP基準による会計結果、2018年と2017年は会計ルールが異なる)

Cadenceが年間売上を20億ドルの大台に乗せたのは今回が初。9四半期連続での四半期売上記録の更新が示すように、Cadenceの業績は右肩上がりで好調を維持しており、2019会計年度は22億7000万〜23億1000万ドルの売上を見込んでいる。

2019.02.21

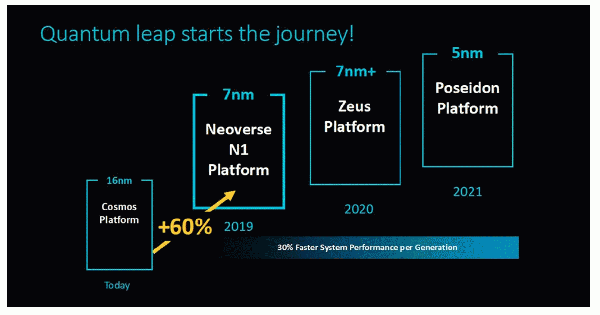

2019年2月20日、ArmはNeoverseファミリーの新コア2品種「N1」および「E1」を発表した。

発表によると「Arm Neoverse N1」コアは、7nmプロセス向けに最適化されたコアで、主要なクラウド処理においてCortex-A72の2.5倍の演算性能を実現。4コアから128コアまでスケーラブルに拡張可能でサーバー向けSoCを主なターゲットとしている。

もう一つの「Arm Neoverse E1」コアは、5G時代のネットワーク・インフラを見据えたスループット重視のコアで、Cortex-A53と比較して2.7倍以上のスループット性能、2.4倍以上のスループット効率、そして2倍以上の演算性能を実現。ベース・ステーションから高性能ルーターまでスケーラブルに高速データ転送ニーズに対応する。

Armは2021年まで毎年新しい世代のコアをリリースする計画で、世代毎に30%の性能向上を目指している。今回発表された「Neoverse」コアは既存の「Cosmos」コアよりも60%以上の性能向上を実現しているという。

画像はArm社Web上のデータ

2019.02.19

2019年2月18日、仮想通貨マイニング大手のBitmainは、新型のマイニングASIC「BM1397」を発表した。

発表によるとBitmainの新製品「BM1397」は、TSMCの7nm FinFETプロセスで製造される同社2世代目の7nmチップで、Proof of Work (PoW)でSHA256を利用するBitcoin(BTC)やBitcoin Cash(BCH)のマイニングに利用できる。Bitmainによると「BM1397」は初代7nmチップの「BM1391」よりも電力効率が28.6%向上しているという。

仮想通貨のマイニングは対電力コストとの戦いで、性能とともに電力効率をいかに向上させるかがマイニングチップ開発の鍵となっている。詳細は明らかにされていないが、Bitmainは今回の「BM1391」の開発にあたりチップの設計メソドロジを改善したとしている。

2019.02.13

2019年1月30日、クラウド・ストレージ・ソリューションを手掛けるイスラエルのベンチャーPliops社は、資金調達Bラウンドで計3000万ドルを調達した事を発表した。

Pliopsへの出資をリードしたのは新たに投資家に加わったSoftbank Ventures Asiaで、既存の投資家であるIntel, Western Digital, Xilinxらもこれに続いた。

今回の3000万ドルを合わせて同社の累計調達額は計4000万ドル。新たに調達した資金はクラウドストレージおよびデータベース・アプリケーション向けの「ストレージ・プロセッサー技術」の開発加速に充てる。

PliopsはSamsungや東芝でSSDコントローラを開発していたメンバーが2017年に立ち上げた会社で、イスラエル、アメリカ、中国に拠点を持つ。

同社のコア技術「ストレージ・プロセッサ」に関する詳細は未だ公表されていないが、プレスリリースでは「MySQLやCassandraのようなクラウドデータベースを、分離されたFlashに展開することで、計算負荷を90%、ネットワークトラフィックを20倍、レイテンシを50倍、アプリケーションのスループットを10倍以上向上する」と説明。データセンターにおける高速かつ低消費電力なデータアクセスを実現するソリューションのようだ。

Pliopsは2019年中ごろに同社のソリューションの詳細を発表する予定。

2019.02.13

2019年2月12日、DIGITIMESの記事:

業界筋によるとTSMCは3月末からEUVを用いた第二世代の7nmプロセスでチップの量産を開始する予定。これにより7nmチップの売上比率は全体の9%(2018年)から25%まで高まる見通し。

半導体製造装置大手のASMLは2019年にEUVシステムを計30セット出荷する計画で、うち18セットはTSMCが予約している。

TSMCは2019年Q2から計画している5nmプロセスノードのリスク生産も順調に進めている。

2019.02.08

2019年2月7日、IC Insightsのレポート:

中国の半導体生産額は2018-2023年にかけて平均成長率15%以上で伸び2023年は480億ドルに到達する。同時期の中国半導体市場の平均成長率は8%で2023年は2290億ドルに達する。

中国は国内市場が拡大し生産額も伸びるが、半導体自給率は2023年で20%程度と政府目標(2020年までに40%、2025年までに70%)には遠く及ばない。今後も外資系企業による生産が中国市場の大部分を占める。世界市場で見ると中国の半導体生産額のシェアは10%にも満たない。

2019.02.08

2019年2月7日、デンソーの子会社であるファブレスIPベンダNSITEXEは、北米のAIチップスタートアップquadric.ioへの出資を発表した。

quadric.ioについてはCEOの名前以外はWeb上にも殆ど情報が無いが、NSITEXEの発表によると同社は産業機器向けの「エッジプロセッシングユニット(EPU)」の開発技術を持つとのこと。EPUは、低遅延、低消費電力のエッジ向けプロセッシング・ユニットという事らしい。

今回NSITEXEは、quadric.io社に出資を行うことでEPUに車載向け仕様を織り込んだIPの開発を加速させる計画。同IPは同社が北米のAIチップベンチャーThinCIと共同で開発している「データフロープロセッサー(DFP)」と組み合わせて自動運転向けに利用するという。

2019.02.06

2019年2月4日、市場調査会社Gartnerは2018年の半導体消費企業ランキングを発表した。

発表によるとHuaweiが前年比45%増でSamsung, Appleに次ぐ3位に浮上。その他新たにXiaomiがTop10にランクインし、Top10中4社が中国企業となった。

2019.02.05

2019年2月5日、SynopsysはAIチップベンチャー中国FABU Technologyによる同社IPの採用事例を発表した。

FABU TechnologyはADAS、AIチップおよび自動運転トラックを手掛ける2017年設立のベンチャーで中国浙江省の杭州市に本拠を置く。創業者であるCEOのXiaofei He氏はAI,機械学習の専門家で、中国版Uberと呼ばれる中国ライドシェアサービス最大手「滴滴出行」のシニアVPを務めていた。

発表によるとFABU Technologyは、AI機能を備える車載向けSoCの開発でSynopsysのIPを採用した。採用したのは下記の4品種。

・DesignWare® Interface IP

・DesignWare® Security IP

・DesignWare® ARC® EM Safety Island Processor IP

・DesignWare® Embedded Memory Test and Repair IP

FABUが開発したSoCは、ADASならびに自動走行車に必要となる物体/走行レーン認識、信号機認識、車両位置特定、動態解析、状況認識の処理を行うインテリジェントなチップ。

FABUはSynopsysのIPを採用することで、所望の機能・品質を実現すると同時にSoCレベルでの機能安全性の査定にかかる期間を短縮することができたとしている。

なお、FABUが今回開発したSoCの詳細は明らかにされていないが、同社は自社の自動運転トラック向けに開発したSoCを外販しているようだ。

2019.02.05

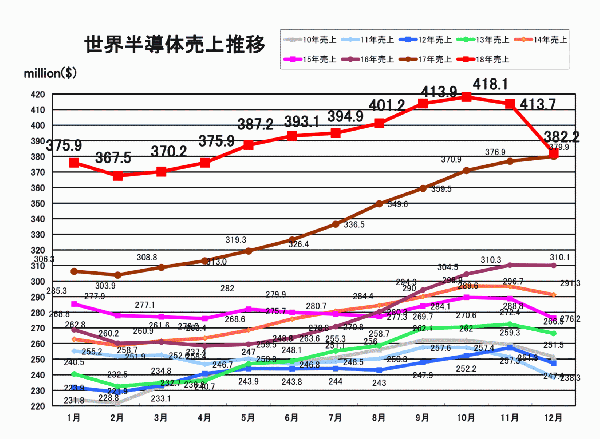

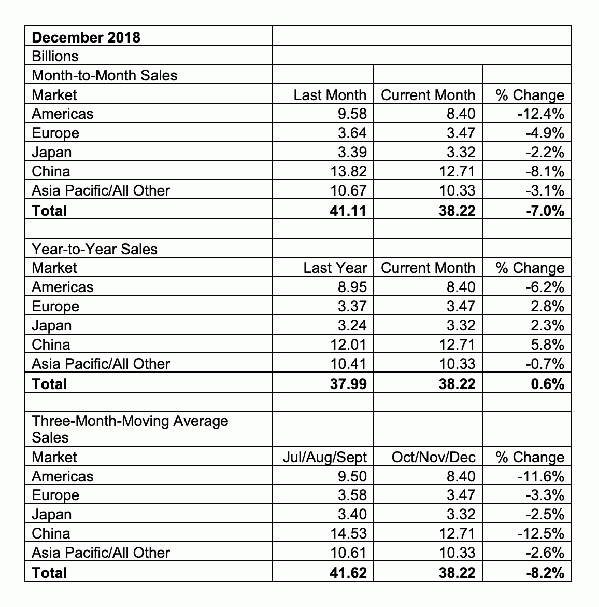

2019年2月4日、米SIA(Semiconductor Industry Association)は、2018年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年12月の世界半導体売上は前年同月比0.7%増、前月比7%減の382.2億ドルだった。11月に5ヶ月連続していた単月売上の更新記録がストップしたが、12月は更に11月の実績を下回り2ヶ月連続の売上減となった。これは2015年の6月以来の出来事となる。

SIAの統計によると、最終的に2018年の世界半導体売上は前年比13.6%増の4688億ドルで過去最高。

製品別カテゴリで見るとメモリの売上が最も多く前年比27.4%増の1850億ドル。DRAMの売上は前年比36.4%増とNANDフラッシュよりも大きく伸びた。

地域別に見ると年間売上高は、中国(20.5%)、アメリカ(16.4%)、ヨーロッパ(12.1%)、日本(9.2%)、アジアその他地域(6.1%)と全手の地域で前年実績を上回った。

12月の単月売上ではアメリカとアジアその他地域が前年実績を下回った。

日本市場の12月の売上は前年比2.3%増、前月比2.2%減の33.2億ドル。売上を円ベースで換算すると前年比約2.1%増の約3737億円となる。

なお、WSTSが昨年11月に発表した秋季予測では2018年の売上合計額は4700億ドル超となる見通しだったが、結果的には12月の売上が予想以上に落ち込み4700億ドルを割り込んだ。

WSTSは2019年の成長率を2.6%のプラス成長と予測している。

※SIA

2019.02.01

2019年1月30日、SEMIは2018年のシリコンウエハの市場統計を発表した。

発表によると2018年のシリコンウエハの出荷数は前年比8%増の127億3200万平方インチで過去最高を記録。売上額は前年比31%増の114億ドルで2008年以降、初の100億ドル突破となった。

ウエハ単価の向上により2018年の収益は増加したが、まだ過去最高を記録した2007年の売上を超えるには至っていない。

2019.01.31

2019年1月30日、Reuterの記事:

Intelはイスラエルのファブレス半導体ベンダMellanox Technologiesの買収に向けて、現金と株式でおよそ55-60億ドルのオファーを出した様子。

60億ドルのオファーは、ナスダックでのメラノックスの直近の終値に対する35パーセントのプレミアムに相当する。

Mellanoxは昨年10月時点で少なくとも2社から買収のオファーを受けており、売却を検討するための財務アドバイザーを雇った。

MellanoxはNIC、スイッチなどを手掛けるファブレス半導体ベンダで、同社のInfiniband製品はHPC分野で実績がある。直近のスパコンランキング1位、2位のスパコンはMellanoxのInfiniBandを使用している。

Mellanoxの買収については、これまでBroadcomやXilinxなどの名が挙がっていたがIntelの名が挙がるのはこれが初めて。

2019.01.31

2019年1月30日、Digitimesの記事:

中国のファウンドリ大手SMICは2019年上半期に14nmの量産開始を計画。

最初の顧客は携帯電話セクターとなる見通し。

SMICは14nmプロセスの歩留まりを95%まで向上。元TSMC及びSamsungの高名な研究者を迎え入れた事でSMICのFinFETプロセス開発は大きく前進した。

またSMICは政府の支援を受け10nm及び7nm FinFETプロセスの開発も加速している。

2019.01.30

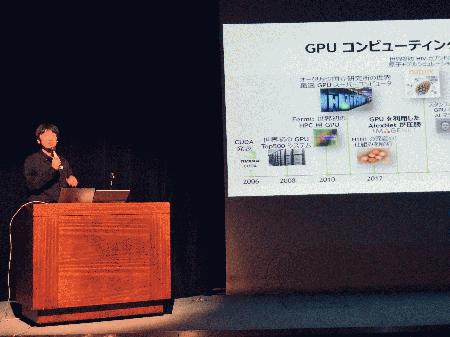

昨年12月に日本EDAベンチャー連絡会のイベント「JEVeC DAY 2018」が川崎市産業振興会館で開催された。

JEVeCは国内のEDA関連各社が組織する非営利団体で日本のEDAの発展を活動目的に掲げている。

JEVeCは例年独自のイベントを開催しているが、「JEVeC DAY 2018」は例年以上の大規模イベントとして開催され150名以上の参加者を集めた。

キーノートではArmとNVIDIAがAIをキーワードに両社最新の取り組みとソリューションを紹介。

セミナーの中心はシステムセッションと称した上流設計、システム視点の講演と実装セッションと称したバックエンド設計、ボード設計などの講演で、その間にSystemVerilogのチュートリアルが行われ、産業タイムズ泉谷氏による特別招待講演がセミナーを締めくくった。

※キーノートで登壇したNVIDIAの佐々木邦暢氏

様々な企業が加盟し幅広いネットワークを持つJEVeCのイベントだけあって、「JEVeC DAY 2018」は非常にバラエティに富んだ講演と人が集まる場として賑わっていた。

是非来年も同様のイベント開催に期待したい。

なお、「JEVeC DAY 2018」の一部の講演資料はJEVeCホームページよりダウンロード可能となっている。

2019.01.23

2019年1月14日、IPベンダCEVAは同社のIPを搭載した機器の出荷数が100億台に到達したことを発表した。

CEVAは同社のIP採用企業として下記の企業名を挙げている。

Alibaba, Amazon, Apple, Canon, China Mobile, Dell, DJI, Fujifilm, Google, GoPro, Hikvision, HP, Huawei, JD.com, LG, Logitech, Meizu, Microsoft, Nest, Nikon, Nokia, Panasonic, Reliance Jio, Samsung, Siemens, Sony, TomTom, Toshiba, Xiaomi, Vivo, ZTE.

2019.01.23

2019年1月21日、SoC組み込み型のFPGAコアを手掛けるFlex Logix Technologiesは、中国の通信大手Datangの子会社であるMorningCore Technologyによる採用事例を発表した。

今回MorningCoreが採用したのはTSMC 12nm FFCプロセス向けの組み込み型FPGAコア「EFLX 4K」。同FPGAコアは4入力LUTを4000個搭載して約1mm2。用途に応じてスケーラブルに構成可能で最大7x7アレイ約20万LUTまで拡張できる。FPGAコアはRTLで提供され専用のコンパイラでインプリメントする。通信システムではプロトコルやアルゴリズムのカスタマイズ、リアルタイム更新などで同FPGAコアを活用できる。

2019.01.21

2019年1月18日、NECは同社が開発した「NanoBridge-FPGA(NB-FPGA)」の宇宙での実証実験を実施することを発表した。

「NB-FPGA」は、NECがNEDOプロジェクトの成果を活用して開発した「ナノブリッジ」と呼ぶ原子スイッチで回路情報を保持するFPGAで、メモリの代わりに金属原子の「ナノブリッジ」を使うことで高い放射線耐性、小型化、低消費電力化を実現する。NECによると「NB-FPGA」は、同等の処理能力を持つ最先端FPGAと比較して消費電力を10分の1、チップサイズを3分の1に抑えられ、放射線耐性の面では素子自身のエラー発生率を従来の1/100以下に抑えられるという。

これまで書き換え可能でかつ高い放射線耐性を実現するというFPGAは市場に存在していない。

今回、JAXAが1月18日にイプシロンロケット4号機で打ち上げた小型衛星「小型実証衛星1号機(RAPIS-1)」のカメラモジュールに「NB-FPGA」を搭載。JAXAとNECが共同で宇宙空間での「NB-FPGA」の動作・信頼性に関する実証実験を行うという。

2019.01.18

2019年1月16日、Xilinxは、Baiduによる同社FPGAの採用事例を発表した。

Baiduは自社のデータセンターでXilinxのFPGAを活用しているが、今回発表されたのはBaiduの新ソリューション「EdgeBoard」におけるZynqの採用事例。

「EdgeBoard」はBaiduが顧客に提供するエッジAIシステムのプラットフォームとして利用される小型ボードで、XilinxのZynq UltraScale+ MPSoCをベースとしている。

Baiduの「EdgeBoard」はターミナル・コンピューティング・アクセラレーション・ソリューションとして、様々なマシンビジョン・アルゴリズムモデルの実装、高性能推論の実現をターゲットとしている。

2019.01.17

2019年1月16日、京都マイクロコンピュータ(KMC)は、同社のJTAGデバッガ「PARTNER-Jet2」が日本のIPベンダNSITEXEのテストボードの開発環境に対応したことを発表した。

デンソーの100%子会社であるNSITEXEは、米AIスタートアップのThinCI社と共同で次世代半導体 IP「Data Flow Processor(DFP)」を開発しており、昨年12月にDFPを搭載したテストチップの開発完了を発表していた。

今回、KMCのJTAGデバッガ「PARTNER-Jet2」はDFPを搭載したNSITEXEのテストチップ・テストボードの開発環境として対応した。NSITEXEはDFPの市場投入に向け、試作チップの開発初期段階からKMCとデバッグ・トレース環境の検討と検証を行ってきたという。KMCの「PARTNER-Jet2」はARMやSHに対応するJTAGエミュレータとして実績があり、IntelのCPUやARM最新の64bit v8アーキテクチャにも対応している。

今回の発表は1/16から東京ビッグサイトで開催されている第11回オートモーティブワールドに合わせて行われたものである。

2019.01.17

2019年1月11日、メーリングリストに登録していたAIチップベンチャーGraphcore社からメールニュースが届いた。

メールニュースのトピックスは大きく3つ。

1.2018年12月に2億ドルの追加資金調達に成功

このニュースはTwitter(https://twitter.com/EDAExpress)でも一報を報じたが、Bosch, Dell, Samsungなど既存の投資家に加えBMW, Microsoftもラウンドに参加し、Graphcoreは計2億ドルの追加資金を調達。同社の累計調達額は3億ドルを超えた。同社は独自のAIプロセッサ「IPU-Processor」をベースに既にビジネスで収益を出し始めており、既存の投資家の評価も高い様子。新たに出資したBMWの投資担当者は、データセンターから自動運転車、音声アシスタントまで幅広く利用できる「IPU」の柔軟性の高さを指摘している。なお、Deep Mind社の創業者Demis Hassabis氏やニューラル・ネットワークの大御所Geoff Hinton氏などAI業界の有名どころもGraphcoreに出資しているようだ。

2.ラック型システム「IPU-POD」を発表、32ラック計4,096個の「IPU」で最大0.5エクサFLOPSの演算性能(FP16/32混合精度)

2018年12月にカナダで開催されたNeurIPS 2018にてラック型システム「IPU-POD」を発表した。

「IPU-POD」には「IPU-Processor」を4個搭載した「IPU-Machine」を32枚挿せる。この「IPU-POD」を32台繋げると計4,096個の「IPU-Processor」で最大0.5エクサFLOPSの演算性能(FP16/32混合精度)を実現できる。

※「IPU-Processor」, 「IPU-Machine」の構成の詳細はGraphcore社Webサイト参照(登録すると最新の製品プレゼン資料を入手できる)

超並列化された1000個以上のプロセッシング・ユニットと多量の「In Processor memory(SRAM)」を密結合させたアーキテクチャを持つ「IPU-Processor」は、マシンラーニング・フレームワークで作成した計算モデルのターゲットとして開発されたグラフ・プロセッサで、Graphcoreの提供するグラフ・プログラミング・フレームワーク「Poplar」を用いることでマシンラーニング・モデルのグラフを作成・最適化し、「IPU-Processor」上で実行できる。「Poplar」は、マシンラーニング・モデルのグラフを「IPU-Processor」上のプロセッシング・ユニットにマッピングし、プロセッシング・ユニット間の通信を制御する。

3.人材募集

Graphcoreは英国ブリストルと米国シリコンバレーにオフィスがあり、社員数は200名以上。現在ソフトウェアおよびハードウェアエンジニア、AI研究者などを募集している。

同社は2018年Silicon Review誌の選ぶ最も優れた職場の1つに選出されたという。

Graphcoreの「IPU-Processor」はマシンラーニングの学習/推論両方に適用可能で、いずれにおいても既存のソリューションの10-100倍の性能を発揮するとしている。

同社の創業者Nigel Toon氏は、Alteraに13年間勤務した後に3GセルラーモデムチップのIcera社を創業。同社を2011年にNVIDIAに売却。その後半導体ベンチャー2社のCEOを経てGraphcoreを設立している。

2019.01.17

2019年1月4日、IC Insightsのレポート:

IC Insightsのレポートによると、世界の大手半導体サプライヤは過去10年間で市場シェアを大幅に拡大。

2018年の世界半導体市場では上位5社が47%を占め、10年前と比較して14ポイント増加。上位50社では市場の89%を占め、10年前から7ポイント増加した。

2018年半導体上位50社の成長率は前年比66%増で、最も成長率が高かったのはNanyaの+56%、最も低かったのは富士通の-10%。昨年売上が減少したのは半導体企業上位50社のうち3社のみで、2桁の売上減を記録したのは富士通だけだった。

2019.01.16

2019年1月15日、インターコネクトIPを手掛けるAlteris IPは、同社のインターコネクトIP「FlexNoC」が中国IT大手Baiduに採用されたことを発表した。

Baiduは独自開発のAIチップ「Kunlun」向けにArterisのインターコネクトIPをライセンス。同チップはデータセンターや自動運転車などでの運用が想定されている。

2019.01.16

2019年1月8日、Everspin Technologiesは、昨年12月より量産に向けて28nm 1Gb STT-MRAMのサンプル出荷を開始したことを発表した。

Everspinは既に256MbのSTT-MRAMを量産しているが1Gb STT-MRAMの製品化は世界初。2019年下半期から量産を開始する計画。

EverspinのMRAMはSSDの高速化などで利用されている。

2019.01.16

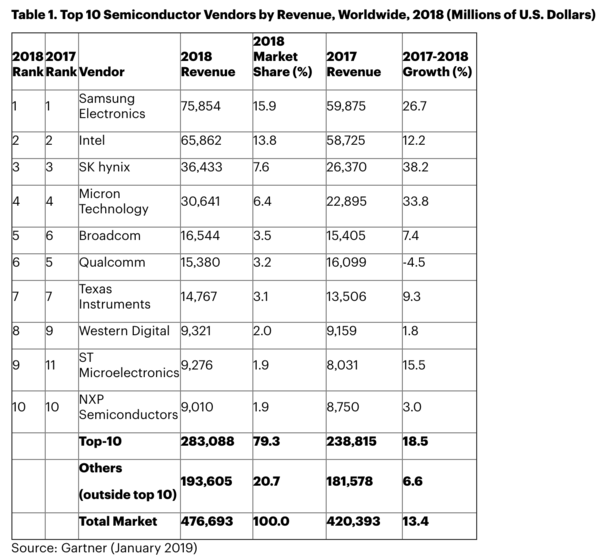

2019年1月7日、市場調査会社Gartnerは、2018年世界半導体市場統計を発表した。

Gartnerによると2018年の世界半導体市場の売上は前年比13.4%増の4767億ドル。メモリの売上成長率は2017年に満たなかったが、メモリの売上が依然売上増の原動力になっており、全売上に締める割合は昨年の31%から34.8%に上昇した。

市場の上位25社による売上は昨年より16.3%増加し全市場の79.3%を占めた。

TOP4は昨年と変わらず上からSamsung, Intel, SK Hynics, Micronの順。5位は昨年6位のBroadcomがQualcommと入れ替わった。

前年比の成長率が最も高かったのはSK Hynicsで前年比38.2%増、次いでMicronが33.8%増だった。

Gartnerの担当者はメモリの減速やASSPの低迷などを挙げ2019年は過去2年とは全く異なる市場になるとコメントしている。

2019.01.15

2018年12月13日、高位合成ツールを手掛ける米Bluespecは、オープンソースのRISC-Vプロセッサの第2弾「Flute」ファミリのリリースを発表した。

Bluespecの新製品「Flute」は、昨年8月に同社がリリースしたオープンソースのRISC-Vプロセッサ「Piccolo」(3段パイプライン)を補完する5段パイプラインのコンフィギュラブル・プロセッサで、IoT向けのカスタム・プロセッサとしての活用を想定。ベアメタルの「RV32IMAコア」とスーパーバイザレベル「RV64IMAコア」の2種類の合成可能なオープンソースのVerilogコードが提供されている。将来的には浮動小数点と圧縮命令(RV32GC/RV64GC)が追加され、LinuxとFreeRTOSがサポートされる計画となっている。「Flute」は XilinxのUltraScale/UltraScale+搭載ボードで実証済みで動作周波数は100MHz、LUT数は5000以下。 Bluespecの発表にはインドのHPC/AI企業Calligo Technologiesが「Flute」のユーザーとしてコメントしている。

Bluespecは元々は高位合成ツールを手掛けるEDAベンダとして活動していたが、最近はRISC-VベースのIPコアとその開発環境の提供にビジネスの主軸を移しているようだ。