NEWS

2009.01.23

パシフィコ横浜で開催中のElectronics Design and Solution Fair 2009に出展していたサイバネットシステムのブースレポート。

サイバネットは、昨年5月より代理店販売を開始した米Bluespec社のESL合成ツール「Bluespec Compiler」を展示。

「Bluespec Compiler」は、SystemVerilogベースの独自言語Bluespec SystemVerilogで記述された抽象度の高い記述から、SystemC TLMよりも更に細分化された「処理の単位」をベースに回路を合成。制御系、データパス系いずれの回路も合成可能でテストベンチも自動生成可能。Denali社が自社IPの開発でBluespecを採用している。

「Bluespec Compiler」は、SystemVerilogベースの独自言語Bluespec SystemVerilogで記述された抽象度の高い記述から、SystemC TLMよりも更に細分化された「処理の単位」をベースに回路を合成。制御系、データパス系いずれの回路も合成可能でテストベンチも自動生成可能。Denali社が自社IPの開発でBluespecを採用している。

既に数社の国内大手電気メーカーがBluespecの本格評価を開始しているという話で、C言語設計に限界を感じてBluespecを検討する顧客、C言語ベースの動作合成では合成できない部分でBluespecの使用を検討する顧客、Bluespecの設計思想が気に入って検討する顧客と、評価顧客のモチベーションは様々との事。今年中には採用事例を発表できるのではないかという話だった。

BluespecのESL合成ツール「Bluespec Compiler」は昨年11月に新バージョンをリリースしており、SCE-MIライブラリをサポート。合成結果をより容易にエミュレータに接続できるようになった。今後はトランザクタ回りの強化を予定しているほか、合成するハードウェア用デバイスドライバの出力機能も開発が計画されているという。

BluespecのESL合成ツール「Bluespec Compiler」は昨年11月に新バージョンをリリースしており、SCE-MIライブラリをサポート。合成結果をより容易にエミュレータに接続できるようになった。今後はトランザクタ回りの強化を予定しているほか、合成するハードウェア用デバイスドライバの出力機能も開発が計画されているという。

※サイバネットシステム株式会社

※Bluespec社

2009.01.22

2009年1月21日、ケイデンスは、STマイクロエレクトロニクスが同社の新型デジタルインプリメント環境「Encounter(R) Digital Implementation System」を採用した事を発表した。

プレスリリース文

発表によるとSTマイクロは、世界中の設計拠点で高性能SoC設計向けに「Encounter(R) Digital Implementation System」を65および40ナノメーター設計フローで採用。さらに、STマイクロとケイデンスは、低消費電力、ミックスシグナル、および先進的なsystem-in-package (SiP)設計機能をターゲットとしたSTマイクロの最先端のセル・ライブラリをベースとした次世代の32ナノメーター設計プラットフォームについても協業中。STマイクロでは、Encounter製品の使用を大幅に増やし、55、40、32nmフローでも「Encounter(R) Digital Implementation System」を採用しているという。

「Encounter(R) Digital Implementation System」は、昨年12月に発表された新型のデジタルインプリメント環境で、旧来の「SoC Encounter」の改良版。ツール内部のデータ構造やメモリアーキテクチャに手が加えられたほか、RTLからGDS-IIまでの設計工程全般で処理のパラレル化を実現しており、より大規模なデザインを高い予測性の下でより早く設計できる。

※日本ケイデンス・デザイン・システムズ社

※STマイクロエレクトロニクス

2009.01.22

2009年1月21日、シーケンシャル等価性検証ツール「SLEC」を手掛ける、米Calypto Design Systems社は、英ARC社による消費電力最適化ツール「PowerPro CG」の成功事例を発表した。

プレスリリース文

発表によるとARCはカリプトと協同でビデオ・コーディング・プラットフォーム「ARC AV 401」の消費電力削減に挑戦。カリプトの消費電力最適化ツール「PowerPro CG」を用いてビデオ・コーデック部の最適化を行ったところ、200Mhzで動作するプラッフォトーム構成において約15%の電力削減を実現。「ARC AV 401」は、既に低電力化されたプラットフォームであったにも関わらず、更なる消費電力の削減に成功した。

「PowerPro CG」は、複数のクロック・サイクルをまたいで回路の動作を解析、ゲーティング可能な論理を特定し、元のRTL コードに対してシーケンシャルなイネーブル論理を挿入。可能な限りクロック・ゲーティングを行うことで、消費電力の削減を実現するツールで、これまでに顧客のデザインで最大60%の電力削減を実現した実績もあるという。

※カリプト・デザイン・システムズ株式会社

※ARC社

2009.01.22

2009年1月21日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automation社は、アルプス電気が同社の回路シミュレータ「Analog FastSPICE」とデバイスノイズ解析ツール「Noise Analysis Option」を採用した事を発表した。

プレスリリース文

発表によるとアルプス電気は、自社先端電子デバイスのキャラクタライゼーションとパフォーマンスシミュレーション向けに「Analog FastSPICE」と「Noise Analysis Option」を採用。設計フローのアップグレードに取り組む中で次世代の設計ツールを探していたという。

Berkeley Design Automationは、今回アルプス電気が採用した「Analog FastSPICE」、「Noise Analysis Option」のほかに、周期解析ツール「RF FastSPICE」、PLLアナライザ「PLL Noise Analyzer」を提供している。

※Berkeley Design Automation社

※アルプス電気株式会社

2009.01.21

2009年1月21日、ケイデンスは、同社の動作合成ツール「C-to-Silicon Compiler」がFPGA向けの合成をサポートした事を発表した。

プレスリリース文

ケイデンスによると、「C-to-Silicon Compiler」がサポートするのはAltera/Xilinxの2社のFPGAで、FPGAをターゲットとした動作合成を実現。制御回路とデータパスの混在デザインの合成やデザインの変更箇所だけを再合成するインクリメンタル合成など、「C-to-Silicon Compiler」の特徴的な機能をFPGA設計にそのまま利用できる。

昨年7月に満を持してリリースされた「C-to-Silicon Compiler」は、ASIC設計向けのツールとしてForte社の「Cynthesizer」やNEC情報システムズの「Cyber Work Bench」が競合と目されていたが、今回FPGAをサポートしたことでターゲットユーザー層は更に拡大され、動作合成ツールのトップシェアを誇りFPGAユーザーの支持が高いメンターの「Catapult Synthesis」とも真っ向からぶつかる事になる。

※日本ケイデンス・デザイン・システムズ社

2009.01.21

2009年1月21日、ケイデンスは、同社のLowPowerソリューションでフリースケール・セミコンダクタ・ジャパンがパワー・マネジメント・チップのテープアウトに成功した事を発表した。

プレスリリース文

発表によるとフリースケールは、様々なパワーモードを管理する携帯デジタルオーディオ/ビデオ製品向けのパワー・マネジメント・チップの設計にてケイデンスのLowPowerソリューションを活用。具体的には低消費電力設計にあたり、「Incisive Enterprise simulator」、「Encounter RTL Compiler」、「Encounter Digital Imprementation System」を使用した。

フリースケールは、Powerフォーマット「CPF」対応の設計フローを通じてMVS(多電源供給)手法やパワー・シャットオフ手法で設計した結果、チップの消費電力を大幅に削減する事に成功し、設計期間を20%短縮することが出来たという。

※CPF:Common Power Format

※日本ケイデンス・デザイン・システムズ社

※フリースケール・セミコンダクタ・ジャパン

2009.01.21

2009年1月20日、OCPパフォーマンス・アナライザ、制御レジスタ管理ツールなどを手掛けるアイルランドの新興ベンダDuolog Technologiesは、米Beach Solutionsの技術と製品を買収した事を発表した。

プレスリリース文

Duolog TechnologiesとBeach Solutionsは、制御レジスタの管理・生成を自動化するツールで競合していた関係で、それぞれ「BITWISE」(Duolog)、「EASI-Tools」(Beach Solutions)という製品を提供。Duologは日本国内の販売チャネルを持っていないが、Beach Solutionsはイノテックを代理店に製品を供給していた。

Duologは、SoCのI/O仕様からRTLを自動生成するというツール「SPINER」を昨年リリースし、現在のところOCPパフォーマンス・アナライザと合わせて大きく3つの製品を展開中。今年は1500万ドルの売上を目指しているということで、今回の買収により製品強化と合わせて日本市場の足場を固めるという狙いがあるようだ。

※Duolog Technologies社

2009.01.20

2009年1月20日、ハードウェアベースの検証環境を手掛ける仏EVE社は、ルネサステクノロジが同社のZeBuエミュレータの最上位機種「ZeBu-XXL」を採用した事を発表した。

プレスリリース文

発表によるとルネサスは、第3世代携帯電話向けSoCの開発で「ZeBu-XXL」を採用。同社は以前から「ZeBu-XL」を使用しているユーザーで、今回、最大1億ASICゲートに対応可能な大規模デザイン対応の「ZeBu-XXL」に乗り換えた。

ルネサスでは、最終的なシステムの性能はソフトウェアを流さないと分からないという点から、SoCの協調検証用にEVEのエミュレータ「ZeBu-XL」をしてきた経緯があり、大規模デザインへの対応だけでなく、ZeBuシリーズの特徴でもある市販エミュレータでは困難なトランザクタを用いた外部モデルとの連動機能を高く評価している。

発表にコメントを寄せているルネサス テクノロジ システムソリューション第二事業部 モバイルSOC第一部 部長の服部俊洋氏は、以前、EVE社のセミナーで周波数2.5Mhzで「ZeBu-XL」を動かす事に成功したと語っていたが、トランザクションモード実行時には最高速度が20MHzにも達するという「ZeBu-XXL」の性能を今回の事例でどこまで引き出したか聞いてみたい。

※日本イヴ株式会社

※株式会社ルネサステクノロジ

2009.01.20

2009年1月19日、ESLツール大手のコーウェアは、リコーがCoWare ESL 2.0ソリューションを採用した事を発表した。

プレスリリース文

発表によるとリコーは、オフィス・オートメーション機器向けの次世代ワイヤレス通信SoC設計において、SoCプラットフォーム・アーキテクチャ設計とSoC完成前のソフトウェアの開発用にCoWare ESL 2.0ソリューションを採用。

具体的には、「CoWare Platform Architect」、「CoWare Virtual Platform」、「CoWare IP Model Library」を導入し、マルチコア・ハードウェアプラットフォーム・アーキテクチャの設計検証と複雑なマルチコア・プラットフォーム向け組込みアプリケーション・ソフトウェアの開発、統合およびテストを実施した。

リコーは、「CoWare ESL 2.0ソリューション」を導入した事で、従来の設計手法とFPGAプロトタイピングを使用した前回の結果と比較して、オペレーティング・システムのポーティング時間とブート・ローダ・ソフトウェアの開発期間を90%削減することに成功したという。

※コーウェア株式会社

※株式会社リコー

2009.01.20

2009年1月20日、メンター・グラフィックスは、国内EDAベンダ大手のジーダットがメンター・グラフィックスのパートナー・プログラム「OpenDoor®」に参加したことを発表した。

プレスリリース文

発表によると、今回のジーダットのパートナー・プログラムへの参加を受け、両社はジーダットのカスタムデザインプラットフォーム「α-SX」 とメンター物理検証環境「Calibre®」プラットフォームの統合を推進。2009年6月の統合を目指す。

両製品の統合が完了すれば、「α-SX」ユーザは「α-SX」からシームレスに「Calibre nmDRC」による検証の実行、解析レポートの確認、違反箇所のデバッグを実現できるようになる。

発表にあたり、日本電気株式会社、コンピュータ事業部 CAD技術部長、嵯峨 幸治氏が歓迎のコメントを寄せている。

※メンター・グラフィックス・ジャパン株式会社

※株式会社ジーダット

2009.01.20

2009年1月19日、ハードウェアベースの検証環境を手掛ける仏EVE社は、同社のZeBuエミュレータ向けの新機能「zFAST (ZeBu Fast Synthesis)」を発表した。

プレスリリース文

新たにZeBuエミュレータ向けのソフトウェア環境に搭載される「zFAST (ZeBu Fast Synthesis)」は、大規模デザインに対応可能な高速な合成機能で、業界最高クラスのFPGA合成より数倍高速にデザインのマッピングを実現。同種のツールと比較してエリアの僅かな増加だけで大型デザインをマッッピング可能で、複数のPC上で並列処理により、従来手法で数時間を要していた大規模デザインの合成を僅か数分で完了できる。

言語は、VHDL、Verilog、SystemVerilogをサポートしており、合成によって信号名が勝手に変更されてしまうようなことはなく、ZeBuがRTLの信号名でVCD/FSDB/VPDに波形ファイルを生成することが出来る様にRTLの信号を保持する事が可能。トップダウン合成と合わせてモジュール毎のボトムアップ合成もサポートしている。

新たな合成機能「zFAST」の発表にあたり、EVE-USA社長兼ワールドワイド・マーケティングVPのラウロ・リザッティ氏は、「全システムの検証に関して言えば、FPGAベースのエミュレータだけが成功するでしょう。」、「大規模デザインをFPGAにマッピングを行おうとすると多くの商用FPGA合成ツールでは扱いきれません。」と自信満々のコメントを寄せている。

zFASTは、ZeBuの追加機能としてすでに出荷中で、初回ライセンスは50,000ドル、追加ライセンスは15,000ドルで提供される。

※EVE社

2009.01.20

2009年1月19日、フォーマル検証ツールを手掛ける、米Jasper Design Automation社は、業界初となるデザインの動作からRTLの解析・デバッグを行う新ツール「ActiveDesign」を発表した。

プレスリリース文

Jasperの発表した新ツール「ActiveDesign」は、「Behavioral Indexing」と呼ぶ業界初の新技術を用いた検証ツールで、デザインの動作検証における劇的なブレイクスルーを目指すもの。具体的には、「Behavioral Indexing」技術によりデザインの動作を繰り返し抽出・索引化し、「Activated Design」と呼ぶ実行可能なデータベースにRTLと共に保存。RTLの実装過程で同データベースを用いる事で、機能動作の確認や索引化、意図しない相互作用の検出など設計者のセルフテストの品質と効率を向上させることができる。

これにより、設計者がデザインを実装している間に第三者でもそのデザインの動きを理解できるようになり、検証期間の短縮やデザインの再利用、デザインの情報移管の加速などが可能となるほか、設計者はデザインを検証チームに渡す前に、テストベンチを作らずにデザインの品質を上げる事ができるようになる。

「ActiveDesign」は、SystemVerilog、Verilog、VHDLのRTLを入力可能で、テストベンチやシミュレータ無しでフォーマル技術によってデザイン動作の波形表示を生成可能。ユーザーは所望の形に直接波形を修正する事ができるだけでなく、「関連度解析」機能を利用すれば自動的にデザインの変更が機能に与える影響をレポートしてくれるという。

新製品「ActiveDesign」は、2009年3月に正式リリースの予定で、今週開催されるEDSFair2009にて、日本代理店CyberTec株式会社のブースで初披露される。

※「ActiveDesign」の関連記事を当サイトで掲載中

※CyberTec株式会社

※Jasper Design Automation社

2009.01.20

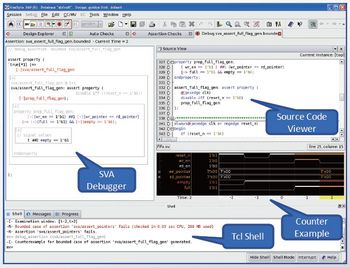

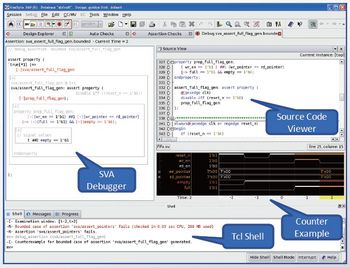

2009年1月19日、フォーマル検証ツールを手掛ける独OneSpin Solutionsは、フォーマル検証の統合環境「360 MV」製品ファミリーの拡張を発表した。

OneSpinの「360 MV」製品ファミリーは、日本上陸当初は2つの製品で構成されていたが、現在は下記の5つの連携する製品で構成される包括的なフォーマル検証環境。少ないプロパティ記述で高速な検証を実行できる点やプロパティを作成するメソドロジを用意している点が特徴で、プロパティの再利用性が高い高度なフォーマル検証を簡単な手順で実行できるツールとして欧州市場では強固な顧客を確保している。

発表によると、今回の製品拡張でステップバイステップの構造化されたアサーションベース検証アプローチが導入され、ユーザーは専門知識とプロジェクトのニーズに適したレベルに応じてツールを利用可能に。すなわち、検証エキスパートに限らずフォーマル検証の初心者でもアサーションベース検証で効果を出せる環境を用意した。

具体的には、3段階の「標準」フォーマルABVと、オペレーションをベースとしたOneSpinの改良ABV手法の3段階のエントリーレベルを用意しており、設計初期段階のコードクリーンアップのための自動チェックから、最高の検証品質を保証する検証まで広範囲にフォーマル検証をカバー。新たなデバッガも用意され、より高品質な検証をより効率的に実現できるようになった。

同新製品ファミリーは、今週開催のEDSFair2009にて初披露される予定。

■「360 MV」製品ファミリー ラインナップ

?360 MV Inspect™ (自動チェック)

コードが最初に利用可能となった段階で すぐにRTLエラーを検出でき、以降のデバッグ工数を削減できます。数千のチェックを数分で実行し、フォーマル検証の経験やアサーション言語の知識を必要としません。

?360 MV Check™ (インプリメンテーション意図の検証)

マイクロアーキテクチャまたはインプリメンテーションの側面を表したアサーションを使って、設計者はテストベンチが利用可能となる数週間または数ヶ月前にインプリメンテーションのバグを見つけ出すことができ、早期の品質向上と以降のデバッグ工数削減を可能にします。

?360 MV Verify™ (機能仕様と設計に含まれるオペレーション検証)

業界最高のキャパシティおよびパフォーマンスと、設計のオペレーションに対する独自の体系的な検証により、深く、複雑なエラーをシミュレーションや他のフォーマルツールよりも格段に効率的に見つけだします。 また、新しい証明ベースのデバッガにより、複雑なSVAに対して自動的にエラー箇所を特定します。360 MV Verifyは、高カバレッジのモジュール/サブシステムレベルテストベンチに対する必要性を削減、または解消し、OneSpin独自の、オペレーションベースのフォーマルABVに対するエントリポイントとしての役割を果たします。

?360 MV Assure™ (自動ギャップ検出を使った検証)

まだ検証されていない入力シナリオを自動的に特定し、設計に含まれるオペレーションの体系的な検証を強化します。デバッグおよび診断環境により、これらの検証ギャップをクローズするSystemVerilogアサーションの開発を助け、仕様/インプリメンテーションの徹底的な協調検証を確実にします。

?360 MV Certify™ (ギャップフリー検証)

OneSpinの旗艦製品であり今日他のどの検証アプローチでも保証できない検証品質を提供します。検証プランニング、検証の実行、自動ギャップ検知を統合した閉ループプロセスであるOneSpinのGapFreeVerification™ により、可能な限り最高の検証品質を達成します。360 MV CertifyはギャップのないSystemVerilogアサーションの開発を支援します。仕様に準拠した設計の完全な機能のリファレンスモデルを構築し、RTLコードがリファレンスモデルと機能的に等価であることを証明します。

※OneSpin Solutions社

2009.01.20

2009年1月19日、設計初期段階でのアーキテクチャ探索を実現するESLツール「CoFluent Studio」を手掛ける仏CoFluent社は、拡大する日本市場での顧客サポート体制を強化する為、昨年開設した日本事務所を、2009年中に100%保有の株式会社として法人化する計画を発表した。

プレスリリース文

コフルエントは、昨年の日本事務所開設以降、順調に日本国内での受注を伸ばしており、その顧客はディジタルマルチメディアやコンスーマ分野に限らず、オートモーティブ関連にも拡大。高精度な仮想環境を構築する前に、よりスピーディかつ容易にシステムのパフォーマンス/動作を可視化したいというニーズにマッチし、「CoFluent Studio」はSoCのシステム・アーキテクトからソフトウェア開発者まで様々な用途での実用が進んでいるという。

※コフルエントデザイン社

2009.01.19

2009年1月19日、ケイデンスは、VDEC(東京大学大規模集積システム設計教育研究センター)が日本国内の主要大学、および高等専門学校でのデジタル設計向け研究・教育プログラムで使用するために、ケイデンスの最先端デジタル設計向けツールを採用したことを発表した。

プレスリリース文

発表によるとVDECは、ケイデンスの論理合成ツール「Encounter RTL Compiler」とデジタルインプリメント環境「Encoutner Digital Implementation System」を研究・教育プログラムでの使用に採用。すでに採用済みのVirtuosoアナログ設計環境と統合し、セル設計、カスタムIC設計、SoC設計に及ぶ総合的な設計環境を、学生、および研究者に提供する。

発表に寄せられたVDECセンター長の浅田邦博教授のコメントによると、VDECでは既に今回採用したRTL CompilerとEncoutner Digital Implementation Systemを使用して試作チップのテープアウトを完了し、現在65nmの試作チップのプロジェクトが進行中だという。

※日本ケイデンス・デザイン・システムズ社

※VDEC:東京大学大規模集積システム設計教育研究センター

2009.01.19

2009年1月16日、株式会社半導体理工学研究センター(STARC)は、TLモデリングガイド第2版(OSCI TLM2.0対応)のリリースを発表した。

プレスリリース文

今回STARCがリリースした「TLモデリングガイド第2版」は、昨年1月にリリースした「TLモデリングガイド」の改訂版で、その内容を今年7月にリリースされたOSCIのSystemC-TLM2.0に対応させたもの。

同モデリングガイドは、EDAツールに依存しない再利用性、相互運用性の高いトランザクションレベルの設計の実現を目指し、抽象レベル、モデル構造、通信APIの3つの標準化を行ない、これに沿ったモデルの例題記述やモデルの設計手順を記載している。

市場のニーズに後押しされ、SystemC-TLMに対応したEDAツールが色々と流通するようになってきたが、その実用化に向けてはTLM2.0のリリースとモデリングの標準化を求める声が大きかった。昨年7月のTLM2.0のリリースを受けて僅か半年足らずで実施された今回のSTARCの改訂は、システムレベルの設計手法を普及するという意味で大きな功績と言える。

尚、STARCは今週開催するEDSFair2009にて同モデリングガイドを紹介する予定。書籍はSTARCホームページ上でも販売する予定。

※株式会社半導体理工学研究センター

2009.01.19

2009年1月16日、株式会社半導体理工学研究センター(STARC)は、RTLでの機能検証に対するガイドを開発。同ガイドを「IP機能検証ガイド?機能検証仕様策定編?」として書籍販売することを発表した。

プレスリリース文

発表によるとSTARCは、STARCメンバ会社の検証専門家の協力を得てEDAツールによる自動処理化が困難な検証の準備過程に焦点を当ててIP機能検証ガイドを策定。これまでSTARCメンバ会社へ限定的に同ガイドをリリースしていたが、今回、同機能検証手法のさらなる普及促進を目的に書籍化=一般的な配布に踏み切った。

IP機能検証ガイド「機能検証仕様策定編」の内容としては、IP品質向上をターゲットとしたシミュレーションベースの機能検証(ダイナミック検証)での活用を想定し、機能検証戦略策定から機能検証仕様書の策定までのプロセスにおけるノウハウや検証の推奨フロー、推奨手法などをガイド項目としてまとめており、機能検証項目とテストベンチの関連を明確にし、テストベンチの詳細機能要求仕様として検討すべき内容をガイド化。熟練の検証エンジニアの知見をベースとしているが、経験やスキルに依存しない機能検証の実現を目指す形となっているという。

尚、STARCは今週開催するEDSFair2009にて同ガイドを紹介する予定。書籍はSTARCホームページ上でも販売する予定で、ガイドの利用促進のための入門編(クイックガイドPDFファイル)のダウンロードサービスも開始する。

※株式会社半導体理工学研究センター

2009.01.18

2009年1月15日、仮想システム・シミュレーターを手掛ける米VaST Systems Technology社は、NECエレクトロニクス・アメリカが、自動車関連顧客に同社の仮想開発ソリューションを提供する事に合意した事を発表した。

プレスリリース文

発表によるとNECエレUSAは、北米市場における自動車顧客への営業活動の一環として自社の車載向け32ビットMCU製品と合わせてVaST社のツールを提供。同ツールを提供する事で、顧客のハードウェアプロトタイピングとソフトウェア開発のコスト低減/効率化を実現し、製品の付加価値を高めるという狙い。

VaST社とNECエレUSAは2007年より協業を進めており、VaST社は既に自社シミュレーター用の仮想モデルとして複数のNECV850シリーズのモデルを提供している。

VaST社のシミュレータ「CoMET」は、高速かつ高精度なシミュレーション能力を売りにコンスーマ機器や車載ECUなどのソフトウェア開発で利用されているツール。VaSTは、ルネサステクノロジとも車載向けマイコン関連でパートナーシップを結んでいる。

※NECエレクトロニクスUSA

※VaST Systems Technology社

2009.01.16

2008年1月15日、エレクトロニクス分野の国際学会「DesignCon」の主催団体IEC(International Engineering Consortium)は、DesignCon 2009の公式ホームページにて今年の「DesignVision Award」のファイナリストを発表した。

「DesignVision Award」は、毎年DesignConにて表彰が行われているIEC主催の権威ある賞で、市場にインパクトを与えた優れた製品、サービス、アプリケーションを表彰するもの。今年も計8部門に分けて各部門の受賞候補が発表された。

EDAツール関連のファイナリストとしては、ChipVisionの動作合成ツール「PowerOPT」、Mentorの配置配線ツール「Olympus-SoC」、Xilinxの設計環境「ISE」、Sequence Design の消費電力解析ツール「PowerArtist」、EVEのエミュレーション環境「ZeBu-Personal」がノミネートされた。

EVEとSequenceは、製品は違うが昨年に続いてのファイナリスト選出。

各部門の受賞製品は、DesignCon 2009会期中の2月3日に発表される予定。

■DesignCon2009 DesignVision Awardファイナリスト一覧

・IC Design Tools

-ChipVision Design Systems for PowerOpt™

-Mentor Graphics for the Olympus-SoC Parallel Timing Analysis and Optimization

-Xilinx for Integrated Software Environment (ISE™) 10.1

・Design Verification Tools

-Agilent Technologies for MIPI D-PHY Analysis/Stimulus Solution (N4851A)

-EVE for ZeBu-PersonalQualiSystems for TestShell

-Sequence Design for PowerArtist

・Interconnect Technologies and Components

-FCI for ZipLine™ Connector System

-Molex Incorporated for the Impact Backplane Connector System

-Tyco Electronics for the Micro ACTION PIN PCB Interconnect

-Xilinx for the Virtex®-5 FXT and TXT FPGAs for PCI Express® version 2.0

・PCB Design Tools and Technologies

-Mentor Graphics for the Mentor Graphics RF Design Solution with Agilent

-PCB Matrix for the Symbol Wizard

-Simberian Inc. for the Simbeor 2008

・Semiconductor Components and ICs

-International Rectifier for the IR3720 and IR3721

-National Semiconductor for the ADC12EU050

-Xilinx for the Xilinx® Virtex®-5 TXT FPGA Platform

・Semiconductor IP

-Cadence Design Systems for the ChipEstimate.com IP Ecosystem

-IPextreme for CoReUse

-Virage Logic Corporation for the STAR Memory System 4.0

・System Modeling and Simulation Tools

-National Semiconductor WEBENCH® Sensor Designer

-Virtutech for Simics Hybrid

-Signal Integrity Software (SiSoft) for the Quantum Channel Designer

・Test and Measurement Equipment

-Agilent Technologies for the MIPI D-PHY Analysis/Stimulus Solution (N4851A)

-Cascade Microtech for the EDGE™ Flicker Noise Measurement System

-SyntheSys Research, Inc. for the DPP 12500A-4T

※DesignCon2009

2009.01.16

2009年1月16日、ケイデンスは、同社のSDC生成・検証ツール「Encounter Conformal Constraint Designer」がSTARCのSTARCAD-CEL設計フローに認定された事を発表した。

プレスリリース文

「STARCAD-CEL」は、STARCが開発する65nmプロセス以降の先端プロセスをターゲットとする設計メソドロジ。ケイデンスのインプリメントツールを中心とした「PRIDE」フローとシノプシスのインプリメントツールを中心とした「Eagle」フローがある。

今回STARCは、Encounter Conformal Constraint Designerに対して100を超える評価項目に基づいてテストを実施。バグの混入を防ぎ多大な工数を要するSDCの生成とチェック、修正を自動化するEncounter Conformal Constraint Designerをチップ・レベルのコンストレイントを構築できるツールとしてSTARCAD-CELフローに採用した。

※STARC:株式会社半導体理工学研究センター

※日本ケイデンス・デザイン・システムズ社

2009.01.16

2009年1月16日、検証IPを手掛ける国内ベンチャー、アクティブテクノロジーは、同社初の製品となる検証IPの発売を発表した。

プレスリリース文

アクティブテクノロジーは、2006年5月に設立された検証ソリューション専門のベンチャーで、社長の大島氏は日立製作所の設計者からEDA業界へ転向。Axis Systems、Verisity Designと検証系EDAベンダでの仕事を経てアクティブテクノロジーを立ち上げた。

今回アクティブテクノロジーが発売する検証IP「AHB@VIP」は、SystemVerilog/OVMベースの検証IPでSystemVerilogをサポートしているシミュレータであれば環境を問わず利用可能。「AHB@VIP」を利用すれば、AHBバスのランダム検証環境を容易に構築できるようになるという。

製品の販売は2009年1月20日より開始予定で、価格はマンスリーライセンスで25万円から。

※アクティブテクノロジー株式会社

2009.01.15

2009年1月15日、メンター・グラフィックスは、富士通と富士通研究所がOVMベースの次世代機能検証環境を整備するために、メンターの検証プラットフォーム「Questa」を採用した事を発表した。

※OVM:Open Verification Methodology

プレスリリース文(メンター・グラフィックス社のWebサイト参照)

発表によると富士通と富士通研究所は、高性能並列計算機システムの主要な要素を形成することが可能な、複雑かつ複数クロックドメインのインターコネクト用チップの検証を目的にSystemVerilogと同言語を用いた検証メソドロジOVMを採用。機能検証環境の構築にあたりメンターの検証プラットフォーム「Questa」を選択した。

今回のような大規模かつ複雑なSoCの検証にOVM が使われた事例は世界でも例が無く、メンターと組んでOVMベースの検証環境を構築した理由として富士通/次世代テクニカルコンピューティング開発本部長の井上愛一郎氏は、「先進の検証技術そして非常に高いカバレッジが必要だった」とコメント。ベンダ非依存の形で検証環境を構築できたことも成果として大きかったという。

両社が構築した検証環境で特徴的なのは、以前から両社が取り組んでいるUMLからの仕様書を起点として検証を目指している点。同環境は、複数SoCに対してUMLで記述された設計仕様書を解析することで、体系的かつ網羅的にユースケースを抽出し、検証シナリオを形成することが可能だという。

尚、同事例の詳細については、来週開催されるEDSFair2009での特設ステージセッション5(1/23:16:15?17:15)「検証メソドロジ入門から超並列計算機向けインターコネクトへの適用事例まで ?仏作って魂を入れる検証?」にて触れられる予定で、検証メソドロジの必要性やテストシナリオの重要性など、検証戦略のイロハについて実例をベースとした話を聞く事ができる。

※富士通株式会社

※株式会社富士通研究所

※メンター・グラフィックス・ジャパン株式会社

2009.01.14

2009年1月13日、ハードウェアベースの協調検証ソリューションを手掛けるEVEは、2008年売上が前年比30%増を達成したことを発表した。

※プレスリリース文は間もなく同社サイトで公開されるでしょう。

発表によるとEVEは昨年、顧客40社と共にトランザクションベース検証のリーダーとしての地位を強化。経済情勢が世界的に悪化する中で、その実績を(恐らく売上額と思われるが)エミュレーション市場2位まで上げた。

EVEは昨年1年間で新製品「ZeBu-Personal」のリリース、トランザクタ自動生成ツール「Zemi-3」のリリース、検証IP(ライブラリ)の拡張、ソフトウェア環境の強化、デバッグ機能の追加など多数の製品革新を進めており、2008年の売上増は、研究開発への投資が新技術を生み出し新技術が売上を伸ばすという好循環の結果と言える。

※日本イヴ株式会社

2009.01.13

2009年1月13日、バックエンド設計向けの多目的表示プラットフォーム「LAVIS」を手掛ける、日本のEDAベンダTOOL社は、「LAVIS」の最新版、「LAVIS Ver.8.1」のリリースを発表した。

プレスリリース文

毎年EDSFairや米国のDAC開催のタイミングに合わせてツールのバージョンアップを発表している同社だが、今回のバージョンアップでは既存の等電位追跡機能が強化され、接続箇所におけるビア数のチェックなどDFMを意識したデザインチェッカーとしての機能が実装されたほか、簡易編集機能にて新たにOASISフォーマットをサポート。オブジェクトの移動や編集、追加や削除、アレイの展開、ポリゴンやパス、およびテキストの追加など、業界標準となりつつあるOASISフォーマットの簡易編集も可能となった。

また、DensityMap表示機能の強化や、VSB12パターンのファイルオープン時間の短縮、メモリ消費の抑制、他社EDAベンダーツールとの連携強化など、レイアウトエディタとしての基本機能に関しても更に機能強化を実施。更なる性能向上を実現しているという。

尚、同社は来週開催予定のEDSFair2009にて、下記2セッションの出展社セミナーを開催予定。

・LAVISファンになろう !---設計の全工程で使える視覚検証ツールを体感する

・LAVIS名人になろう !---単なる視覚検証に留まらない最新機能を極める

※TOOL株式会社

2009.01.13

2009年1月12日、ケイデンスは、富士通マイクロエレクトロニクスが同社のローパワーソリューションを活用し、65nm モバイルWiMAXの設計を成功させた事を発表した。

プレスリリース文

発表によると、富士通マイクロエレクトロニクスは、富士通のリファレンスデザインフロー3.0を用いて65nm モバイルWiMAXのデザインをテープアウト。同フローにはPower記述フォーマット「CPF」をベースとしたケイデンスのローパワー技術が取り入れられており、富士通マイクロエレクトロニクスはそれら技術によってリーク電流を88%、全体的な消費電力を36%も削減する事に成功。インプリメント環境「Encounter」の自動パワーシャットオフ機能やPLI不要でパワーシャットオフをシミュレーションできる「Incisive」の検証機能などが活用されたという。

※CPF:Common Power Format

尚、ケイデンスが中心となって組織しているCPFベース低電力設計の推進組織PFI(Power Forward Initiative)では、Low Power設計のためのメソドロジ・ガイドおよび事例集を発行しており、日本ケイデンスのサイトから日本語版をダウンロードできる。

※日本ケイデンス・デザイン・システムズ社

2009.01.12

2009年1月12日、米EDA Consortiumは、2008年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

プレスリリース文

発表によると、2008年Q3(7月?9月)の世界のEDA売上総額は、前年比10.9%減の12億5860万ドル(約1121億円、$=89.12yen換算)。Q2売上と比較すると2.8%減という結果に終わった。

EDA業界の売上は、Q1で前年比1.2%減と3年ぶりに前年割れを記録して以来、Q2で前年比3.7%減、Q3で10.9%減と確実に業績悪化が拡大しており、Q4でも前年比2ケタ減が確実と見られている。

売上減少の要因は、市場の冷え込みが北米だけでなく欧州、日本へと波及したことにあり、Q2では前年比2ケタ増を記録していた両市場も今期は12.9%減(欧州)、15.3%減(日本)と大幅現に反転。アジアその他の地域も含め世界全体で前年比減を記録した。

製品分野別の売上でみると、サービス分野の売上が前年比25%増と大きくアップしたが、主力のCAE分野とIC Physical Design & Verification分野がQ2に続き2ケタ減と壊滅的な状況になりつつある。業界の雇用人員数は、Q2に続いて前年比3.4%増の28176名と増加している 。

2008年Q3の分野別の売上と昨年同時期との比較は以下の通り。

※$=89.12yen換算(Q1レポート時のレートは$=107.13yenだった)

■CAE分野 4億6540万ドル(約415億円)17.6%Down

■IC Physical Design & Verification分野 2億9870万ドル(約266億円)22.3%Down

■IP分野 2億6780万ドル(約239億円)1.8%Up

■サービス分野 1億3090万ドル(約117億円)25%Up

■PCB/MCM分野 1億480万ドル(約132億円)2.5%Up

2008年Q3地域別の売上と昨年同時期との比較は以下の通り。

■北米 5億5550万ドル(約495億円)11%Down

■ヨーロッパ 2億4770万ドル(約221億円)12.9%Down

■日本 2億5480万ドル(約228億円)15.3%Down

■アジアその他地域 2億50万ドル(約179億円)0.9%Down

※EDAC(EDA Consortium)

2009.01.09

2009年1月9日、WindowsベースのPCBおよびFPGA設計環境を手掛ける、豪アルティウム リミテッドは、エレクトロニクス製品設計環境「Altium Designer」の最新版Winter 09において、CADstar用インポートウィザードをサポートした事を発表した。

プレスリリース文

アルティウムによると、今回サポートしたCADstar用インポートウィザードは、図研のPCB設計環境CADSTARの設計データを「Altium Designer」上で利用する為のもので、Altium Designerの設計変換ウィザードから利用。設計変換ウィザードでは、CADSTARのほかにAllegro、OrCAD、DXDesigner、PADSによる設計ファイルも読み込むことができる。

※アルティウム・ジャパン株式会社

2009.01.08

2009年1月9日、ケイデンスは、同社の社長兼CEO(最高経営責任者)にリップ・ブー・タン(Lip-Bu Tan)が就任した事を発表した。

プレスリリース文

ケイデンスによると、タン氏は米国マサチューセッツ工科大学において、原子工学の修士課程を修め、米国サンフランシスコ大学において経営学修士を取得。2004年よりケイデンスの取締役会の一員となり、取締役として「Finance and Technology Committees」のメンバーを務めてきた。

昨年10月の旧経営陣の退任後は、複数の幹部で構成するケイデンスの暫定経営組織のメンバーと、ケイデンスの取締役会の暫定副会長として業務に従事しており、その手腕を買われ今回の社長件CEO就任へと至った。

タン氏は、社長兼CEO就任後も引き続き取締役会のメンバーとして活動を継続。同氏は、1987年にタン自身が創立したベンチャー・キャピタルであるWalden Internationalの会長という顔も持つ。

※タン氏プロフィール

※日本ケイデンス・デザイン・システムズ社

※Walden International社

2009.01.08

2009年1月7日、パワー・インテグリティ解析ツールを手掛ける、米Apache Design Solutions社は、新製品「RedHawk-NX」を発表した。

プレスリリース文

発表によると、新製品「RedHawk-NX」には「hierarchical dynamic power analysis」と呼ぶ業界初の解析技術が実装されているほか、マルチコアもサポート。次世代のダイナミック・パワーインティグリティ解析ツールとして、5億ゲート規模のデザインを取り扱う事が可能だという。

同社は研究開発への投資を続け、2002年に「RedHawk-SD」、2005年に「RedHawk-EV」、そして今回の「RedHawk-NX」と3年おきに新世代のダイナミック・パワーインティグリティ解析ツールをリリースし、半導体各社の先進的なニーズに応え続けており、それが23四半期連続の売上増達成という結果に繋がっている。

※Apache Design Solutions

2009.01.07

2009年1月5日、ESLツール大手のコーウェアは、ストレージ、セキュリティ、ネットワーク分野のソリューションを手掛ける米Hifn社が同社の「ESL 2.0ソリューション」を採用したことを発表した。

プレスリリース文

Hifn社はネットワークやストレージ向けのプロセッサを提供しており、その開発プロセスの改善を狙いコーウェアのESL技術を採用。具体的にはコーウェアの仮想開発環境「CoWare Platform Architect」を用いる事で、開発プロセスの初期段階におけるハードとソフトの協調設計の実現を目指すという。

コーウェアの「ESL 2.0ソリューション」は、単なる開発ツールの提供だけではなく、SystemCをベースとしたデザイン・メソドロジが包含されており、ESL技術によって開発コストの削減を目指す企業に受け入れられている。

※コーウェア株式会社

※Hifn社

2009.01.05

2009年1月5日、バックエンド設計向けの多目的表示プラットフォームを手掛ける、日本のEDAベンダTOOL社は、同社のOASISデータハンドリングツール「OASIS-Utility」を富士通マイクロエレクトロニクスが採用した事を発表した。

プレスリリース文

TOOLの提供する「OASIS-Utility」は、既存のレイアウトデータフォーマット「GDS」から次世代レイアウトデータフォーマット「OASIS」への移行作業を効率化するすための支援ツールで、同最新版では、指定された検査条件にもとづき、値の範囲や図形の形状といった検査をセルの階層展開を行いながら高速に実行することが可能。また、OASISデータに含まれる様々な情報を単にDUMP出力するだけでなく、階層構造やセルの一覧、図形サマリなどの情報も個別に出力できる。

富士通マイクロエレクトロニクスは、OASISデータ受け入れのためのインフラ整備を加速させるためにTOOLの「OASIS-Utility」の採用を決定。同ツールを用いる事でこれまでボトルネックとなっていたOASISデータの受け入れ検査を高速に処理できるようになるという。

※TOOL株式会社

※富士通マイクロエレクトロニクス株式会社

2008.12.22

プレスリリース:

http://www.altium.com/files/corp/media/pdfs/20081212AltiumDeliversAltiumDesignerWinter09_JP.pdf

「Altium Designer Winter 09」では、基板設計作業中にプリント基板をリアルタイムに3次元表示するグラフィック・エンジンのアップグレード、インタラクティブ配線エンジンの改良、設計ファイルのバージョン管理強化など計40の新機能を投入。また、「Altium Designer」とは独立したFPGAをテストするためのダッシュボードも新たに用意され、FPGAの内部機能のテストやモニタリングも可能となった。

今回のバージョンアップでは、PCB設計を中心に更にユーザビリティが高められ、PCB/FPGA開発のTAT短縮に貢献。

価格は、年間ライセンスで基本セット:717000円、拡張セット:1955000円で提供される。

※アルティウム・ジャパン株式会社

http://www.altium.co.jp/

2008.12.22

プレスリリース:http://www.cadence.co.jp/news/h20-12-12.html

発表によると、「Virtuoso Accelerated Parallel Simulator」は、既存の「Virtuoso Spectre Circuit Simulator」の精度を保ちながら、マルチスレッド処理によりシミュレーション速度を大幅に向上。新たなシミュレーションエンジンは、単一スレッドでも「Virtuoso Spectre Circuit Simulator」以上のパフォーマンスを発揮できる。

発表に寄せられた先行ユーザーのコメントによると、「Virtuoso Accelerated Parallel Simulator」を用いる事で既存SPICEよりも10倍/20倍の生産性を実現できているという。

※日本ケイデンス・デザイン・システムズ社

http://www.cadence.co.jp/news/h20-12-12.html

2008.12.12

プレスリリース:

http://www.cadence.com/cadence/newsroom/press_releases/Pages/pr.aspx?xml=121008_Q308earnings(英文)

発表によると、ケイデンスの2008年Q3の売上は前年同時期より42%減の2億3200万ドル。(約220億円 $=95.1yen換算)収支は赤字となり1億6900万ドル(約160億円)の損益を計上した。また、ケイデンスはQ3の売上報告と合わせてQ1およびQ2の収支報告を訂正。2008年1月?6月の合計損益額を約4600万ドルとした。

※金額は全てGAAP基準による会計結果

尚、ケイデンスはQ4の売上を2億1500万?2500万ドルと予測。このままいくと同社の2008会計年度の合計売上額は、前年比約37%減の10億3000万ドル程度となる。

※日本ケイデンス・デザイン・システムズ社

http://www.cadence.co.jp

2008.12.12

プレスリリース:

http://www.aldec.co.jp/news/news_12_01_2008.htm(アダプタボード:12月1日)

http://www.aldec.co.jp/news/news_12_08_2008.htm(LINTツール:12月8日)

アルデックによると今回新製品として発表したプロトタイピング・アダプタボードは、Actel社の大規模アンチヒューズFPGA「RTAX4000S」のプロトタイピング向けのアダプタボードで、ActelのフラッシュFPGA「ProASICR3 A3PE3000」を2個搭載。書き換え可能、再利用可能(取り外し可能)というメリットを提供し、航空宇宙産業で多く使用されている「RTAX4000S」のプロトタイピング検証の効率化、低コスト化を実現する。

LINTツール「ALINT」は、新バージョンの「ALINT 2008.10」にてVHDL/Verilogの混在HDLファイルのチェックをサポート。既存のVerilogコードのLINTチェックに加えVHDLコードについてもチェックが可能となった。その他、チェック対象ルールの設定やチェック結果表示等についても機能拡張が行われた。

「ALINT」はLINTツールとして、STARCの「RTL設計スタイルガイド」VerilogHDL編第2版およびVHDL編初版に準拠したLINTチェックが可能で、アルデック社が策定したルールを利用したチェックやユーザー独自のルール設定によるチェックも可能。現在キャンペーン中でALINTに関するアンケートに答えると特別価格でALINTを購入できるほか、抽選で「RTL設計スタイルガイド」VerilogHDL編第2版またはVHDL編初版が当たる。

※アルデック・ジャパン株式会社

http://www.aldec.co.jp

※アクテルジャパン株式会社

http://www.actel.com/intl/japan/

2008.12.09

プレスリリース:http://www.cadence.co.jp/news/h20-12-5.html(英文)

今回新たに検証IPラインナップに加わったのは、業界初となるモバイル機器向けプロセッサ・インターフェース標準「MIPI」準拠の検証IPで、MIPI標準をベースとした設計の検証を加速するために開発されたもの。(※MIPI:Mobile Industry Processor Interface)

ケイデンスは、MIPI標準化団体の標準化ワーキング・グループのメンバーとして今回の検証IPの開発を進め、カメラ用Serial Interface、 ディスプレイ用Serial Interface、 UniPro(SM)、 SLIMbus(SM)、 DigRF(SM) v4 、MIPIフィジカル・レイヤに対応した6種類の検証IPを用意。それぞれの検証IPは検証メソドロジ「OVM」にも対応しており、ユーザーはOVMの提供する検証環境を利用しながら自動的にMIPIプロトコルへの準拠をチェックできるようになる。

※MIPI

http://www.mipi.org

※日本ケイデンス・デザイン・システムズ社

http://www.cadence.co.jp

2008.12.09

プレスリリース:

http://www.mentor.com/company/news/systemverilog_base_class_library(メンター)

http://www.cadence.co.jp/news/h20-12-5-2.html(ケイデンス)

今回両社が発表したOVMソリューションは、VMMユーザーに向けてOVMへの移行をサポートするためのもので、メンター/ケイデンスそれぞれ異なるクラスライブラリを提供。いずれも既存VMMコードのOVM環境下での利用を実現している。

メンター:OVM/VMM Interoperability library

ケイデンス:VMM to OVM migration library

両社のクラスライブラリは、検証IPの標準規格や認識手法の策定を進めている「Accellera VIP Technical Subcommittee」のまとめた、SystemVerilog base class libraryとのインターペラビリティに関する要求事項に準じており、既にOVM公式ホームページ上で公開されている。

※OVM World

http://www.ovmworld.org

※メンター・グラフィックス・ジャパン株式会社

http://www.mentorg.co.jp

※日本ケイデンス・デザイン・システムズ社

http://www.cadence.co.jp

2008.12.09

プレスリリース:http://synopsys.mediaroom.com/index.php?s=43&item=633

発表によるとSTARCは、2009年第1四半期にリリース予定のSTARCAD-CELv3.0での採用に向けて「IC Compiler」の新技術「Zroute」と「Clock Mesh」を評価。評価の結果、早い段階でルーティングの速度向上(3.5倍以上)とビア数の削減(20%以上)を確認。クロックスキューの低減とばらつきへの対応力も推定できたという。

この評価結果を受けてSTARCは「IC Compiler」の新技術「Zroute」と「Clock Mesh」をSTARCAD-CELv3.0にて採用する方向。STARCAD-CELは、先端プロセス向けの推奨設計フローとしてSTARCが提唱しているメソドロジで、シノプシスのツールを中心とした「Eagleフロー」とケイデンスのツールを中心とした「PRIDEフロー」の2つのフローがある。

※STARC:株式会社半導体理工学センター

http://www.starc.jp

※日本シノプシス株式会社

http://www.synopsys.co.jp

2008.12.08

プレスリリース:http://investor.magma-da.com/releasedetail.cfm?ReleaseID=352483(英文)

発表によると、マグマの2008年8月?10月の売上は、前年同時期より32%減の3650万ドル。($=92.84円換算で約33億円)。売上額としては前四半期終了時に発表したフォーキャストを上回ったが、純損益が2590万ドル(約24億円)と昨年同時期の4倍以上に拡大。同社の株価はついに2ドルを割り込んだ。

※GAAP基準による会計結果

尚、マグマは次の四半期の売上を2800?2900万ドルと予測。2009会計年度の年間売上額については、当初の1億5800?6000万ドルという予測を1億4400万?4600万ドルへと下方修正した。

※マグマ・デザイン・オートメーション株式会社

http://www.magma-da.co.jp

2008.12.05

プレスリリース:http://investors.viragelogic.com/releasedetail.cfm?ReleaseID=351979

発表によるとVirage Logicは、12月2日にLogicVisionに対し、全株式を一株当り$1.05?で現金で買い取る事を提案。同買取価格は、12月1日のLogicVision株価の終値の倍以上に相当しており、総額約1000万ドルとなる。

LogicVision側は今回の提案について、取締役会で協議の上回答するとしている。

※Virage Logic社

http://www.viragelogic.com

※LogicVision社

http://www.logicvision.com

2008.12.05

プレスリリース:http://synopsys.mediaroom.com/index.php?s=43&item=632(英文)

発表によると、シノプシスの2008年8月?10月の売上は、前年同時期より11.9%増の3億5280万ドル($=92.45yen換算で約326億円)、2008会計年度の売上合計は13億3700万ドルとなり、世界的な経済不況の中にもかかわらず対前年比10.3%の売上増という好結果に終わった。

※GAAP基準による会計結果

シノプシスと昨年度業界首位のケイデンスとでは、決算月に2ヶ月の開きがあるが、このままいくと2008年のEDA業界売上首位の座はシノプシスが獲得しそうだ。

※日本シノプシス株式会社

http://www.synopsys.co.jp

2008.12.04

プレスリリース:http://eve-japan.co.jp/company/article_120208.html

EVEによると「EVEユニバーシティ・コネクション・プログラム」は、大学などの教育機関を対象に自社のハードウェアベースの協調検証ソリューションを提供し、論理検証関連の教育や研究をサポートするもので、世界中の教育機関の連携を目指している。

本プログラムの対象となるのは、ハードウェア・アシスト検証技術や複雑な論理検証に関わる研究に取り組んでいるあらゆる教育機関で、当プログラムに許可された大学は、複雑なデザインを検証する研究、実習、ツールおよびメソドロジの教育など幅広いプロジェクト向けにEVEのハードウェア・アシスト検証プラットフォームを利用できる。

EDAソフトウェアとしては、アカデミック版製品の供給や教育プログラムなどは割と一般的であるが、ハードウェアベースの検証環境を教育機関向けに提供するというのは珍しいケースと言える。

※日本イヴ株式会社

http://eve-japan.co.jp

2008.12.03

2008年12月2日、シノプシスは、 ASICプロトタイピング・ソリューションを手掛ける、独ProDesign社のCHIPit事業部を買収することを発表した。

プレスリリース:http://www.synopsys.co.jp/pressrelease/2008/20081201.html

シノプシスは買収に関する条件は公表していないが、CHIPit事業部の買収は2008年11月?2009年1月に完了する予定。CHIPit事業部の人材、技術、製品はシノプシスの傘下に収まる。

ProDesignのASICプロトタイピングシステム「CHIPit」は、欧州の大手企業を中心にワールドワイドで採用されているヒット商品で、2年前の時点でSTマイクロ、フィリップス、ソニーなど採用企業数は50社を超え、売上げ前年比倍増を達成していた。

シノプシスは昨年シンプリシティを買収し、旧HARDI社のASICプロトタイピングシステム「HAPS」を手に入れているが、今回のCHIPitの買収により、検証プラットフォーム「Confirma」のハードウェア・ベース検証ソリューションを更に拡張する。

尚、ProDesign社の「CHIPit」は、これまでプロトタイピング・ジャパン社が日本代理店として販売していた。

※日本シノプシス株式会社

http://www.synopsys.co.jp

※ProDesign社

http://www.uchipit.com/ce/index.htm

2008.11.28

2008年11月24日、SystemCのアサーション・ベース検証環境を手掛ける、米JEDA Technologies社は、SystemC 「TLM-2.0 Compliance Checker」のリリースを発表した。

プレスリリース:http://www.jedatechnologies.net/base/?q=node/213(英文)

JEDAによると発表された「TLM-2.0 Compliance Checker」は、先月発表されたばかりの「JEDA Validation Tools Suite」の一部として提供されるもので、TLM2.0のモデル開発者やTLM2.0ベースの仮想環境ユーザーを対象にモデルの品質向上と検証の効率化を実現する。

最近は、シノプシスが「DesignWare System-Level Library」を提供するなど、TLMモデルの設計利用が広がりつつあり、各社から供給されるモデルや独自開発したモデルのインターオペラビリティをチェックする上でJEDAの環境が役に立つ。

※JEDA Technologies社

http://www.jedatechnologies.net

※株式会社エッチ・ディー・ラボ(JEDA社代理店)

http://www.hdlab.co.jp

2008.11.27

2008年11月24日、マグマと超低消費電力FPGAのSiliconBlueは、両社のパートナーシップ契約を発表した。

プレスリリース:http://www.magma-da.co.jp/press/2008112401.html

発表によると今回のパートナー契約により、マグマはSiliconBlueの超低消費電力FPGA「iCE65」アーキテクチャに対応したフィジカル・シンセシス、配置技術を提供。これら技術は、SiliconBlue社の専用開発環境「iCEcube」ツールフローに完全に統合され、設計者にコンセプトからビットストリームまでシームレスなFPGA設計環境を提供する。

「iCEcube」は、SiliconBlue社のWebサイトからダウンロード可能。標準制約フォーマット、VerilogやVHDLに対応しており、65nm以下のプロセス・ノードでSiliconBlue社の最先端NVCM (不揮発性コンフィギュレーション・メモリ)技術を利用できる。

尚、SiliconBlueのコンスーマ向け超低消費電力FPGAは今年6月の製品発表以降、3ヶ月以内という短期間で70以上の契約、ツール導入を果たしているという。(日本国内ではトーメンエレクトロニクス社が代理店として販売)

※マグマ・デザイン・オートメーション株式会社

http://www.magma-da.co.jp

※SiliconBlue社

http://www.siliconbluetech.com

※トーメンエレクトロニクス

http://www.tomen-ele.co.jp

2008.11.26

2008年11月21日、PCB設計向けの支援ツールを手掛けるNEC情報システムズは、同社製品「DEMITASNX」のバージョンアップを発表した。

プレスリリース:http://www.nec-nis.co.jp/topics/news/news_081121.html

「DEMITASNX」は、プリント基板上のノイズを抑制する設計支援ツールで、独自のノウハウに基づいたデザインルール・チェックを行うことで、プリント基板上のノイズ(EMI)の原因を試作前に除去することができる。

今回発表された新バージョンでは、従来のネット(デバイス間の結線)単位でのエラー表示に加え、修正すべきエラーの優先度を一覧表示する機能を追加。更にEMIチェック精度の向上、レポート機能の追加など機能強化を図るとともに、EMCエンジニアなど詳細なEMCチェックを必要とするヘビーユーザーを対象に高機能製品パッケージ「EMC Expert版」を新たに用意した。

NEC情報システムズは、今後2年間で5億円の売上を目指しているという。

※株式会社NEC情報システムズ

http://www.nec-nis.co.jp

2008.11.26

2008年11月21日、シノプシスは、45nm以降のプロセス・テクノロジをターゲットとした新たなComposite Current Source (CCS)ベースカーブ・モデリング・テクノロジを発表した。

プレスリリース:http://www.synopsys.co.jp/pressrelease/2008/20081119.html

シノプシスによると今回発表したCCSモデリング・テクノロジにより、デジタル・セル・ライブラリのファイルサイズを最高で1/4に削減でき、またそれによりツールの実行時間とメモリ使用量を大幅に改善可能。同技術は、65nm以前のプロセス・ノードに比べて10倍にも増加しているというライブラリのファイルサイズの問題解決に貢献し、結果としてEDAツールの実行時間を60%向上できるという。

※日本シノプシス株式会社

http://www.synopsys.co.jp

2008.11.25

2008年11月20日、アルテラは、同社の「HardCopy II ASIC」がTektronixの最新オシロスコープに採用された事を発表した。

プレスリリース:http://www.altera.co.jp/corporate/news_room/releases/products/nr-tektronix.html

発表によるとTektronixは、発表したばかりのミックスド・シグナル・オシロスコープ「MSO2000シリーズ」およびデジタル・フォスファ・オシロスコープ「DPO2000シリーズ」において、スタンダード・セルASICの代替としてアルテラのストラクチャードASIC「HardCopy II」を採用。これにより、業界最高レベルの価格性能比を実現すると同時に製品の開発期間を20%短縮。製品価格の設定にもインパクトを与えたという。

HardCopy ASICシリーズは、FPGAによるプロトタイプから量産への移行を短期間・低リスク・低コストで実現するスタンダード・セルASICに代わるソリューションで、ASICゲート換算で1300万以上のASICゲート、20Mビットのメモリ、36個の高速トランシーバ・チャネル、および550MHz以上のシステム性能を提供。アルテラの提供する開発環境「Quartus II 」があれば、1つのRTLデザイン、1セットのIPコアからFPGAとASICの両方を実装できる。

※日本アルテラ株式会社

http://www.altera.co.jp

※日本テクトロニクス株式会社

http://www.tek.com/ja

「Bluespec Compiler」は、SystemVerilogベースの独自言語Bluespec SystemVerilogで記述された抽象度の高い記述から、SystemC TLMよりも更に細分化された「処理の単位」をベースに回路を合成。制御系、データパス系いずれの回路も合成可能でテストベンチも自動生成可能。Denali社が自社IPの開発でBluespecを採用している。

「Bluespec Compiler」は、SystemVerilogベースの独自言語Bluespec SystemVerilogで記述された抽象度の高い記述から、SystemC TLMよりも更に細分化された「処理の単位」をベースに回路を合成。制御系、データパス系いずれの回路も合成可能でテストベンチも自動生成可能。Denali社が自社IPの開発でBluespecを採用している。 BluespecのESL合成ツール「Bluespec Compiler」は昨年11月に新バージョンをリリースしており、SCE-MIライブラリをサポート。合成結果をより容易にエミュレータに接続できるようになった。今後はトランザクタ回りの強化を予定しているほか、合成するハードウェア用デバイスドライバの出力機能も開発が計画されているという。

BluespecのESL合成ツール「Bluespec Compiler」は昨年11月に新バージョンをリリースしており、SCE-MIライブラリをサポート。合成結果をより容易にエミュレータに接続できるようになった。今後はトランザクタ回りの強化を予定しているほか、合成するハードウェア用デバイスドライバの出力機能も開発が計画されているという。