NEWS

2009.02.19

2009年2月18日、WindowsベースのPCBおよびFPGA設計環境を手掛ける、豪アルティウム リミテッドは、同社製品の開発ボード「NanoBoard」用のオプション・ドータボードの追加ラインナップを発表した。

プレスリリース文

今回アルティウムが用意したのはXilinx Virtex-4 SXを搭載したドータボードで、ボード上にはアプリケーションから利用できるオンボードメモリやボードの識別データを記録しておくための1-Wireメモリデバイスも搭載されている。

「NanoBoard」は、PCB/FPGA/組込みソフトの統合開発ツール「Altium Designer」とプラグインで接続できる「Altium Designer」専用の開発ボードで、顧客のニーズに合わせて搭載するFPGAを選べるのが特徴。Xilinx,Alteraをはじめ各社のFPGAドータボードをオプションとして用意しており、プラットフォームとなる「NanoBoard」にワンタッチで装着できる。

Xilinx製FPGAでは、今回新たに用意されたVirtex-4 SXのほかに、Virtex-4 LX、Spartan-3、Spartan-3A、Spartan-3ANなどを搭載したドータボードがオプション品として用意されている。

※アルティウムジャパン株式会社

2009.02.19

2009年2月18日、シノプシスは、2009会計年度第1四半期(08年11月-09年1月)の売上を報告した。

プレスリリース文

発表によると、シノプシスの2009会計年度Q1の売上は、前年同時期より7.7%増の3億3980万ドル。前四半期の売上には及ばなかったが、業界大手が軒並み売上を落としている中、前年比プラスの結果を今期も維持した。

尚、営業利益は5240万ドルで、前年比13%増となっている。

シノプシスは、次期Q2(09年2月-4月)の売上額を3億3200万‐4000万ドルと予測しており、予測通りに売上が推移すればQ2も前年比プラスの結果を残す事になる。

※日本シノプシス株式会社

※日本シノプシス株式会社

2009.02.19

2009年2月18日、フォーマル検証ツールを手掛ける、米Jasper Design Automation社は、第4ラウンドの資金調達でベンチャーキャピタルから700万ドルを調達した事を発表した。

プレスリリース文

発表によると今回のJasperへの出資をリードしたのは、日本人が代表を務めるシリコンバレーのベンチャーキャピタルZenShin Capital社で、既存のベンチャーキャピタル5社がこれに続いた。(Accel Partners, Cambrian Ventures, Foundation Capital, InnovationsKapital, Northzone Ventures)

ZenShin Capital代表の森健(もりたけし)氏のコメントによると、Jasperは厳しい経済状況の中、2008年の実績として顧客のライセンス更新100%を達成。売上も前年を上回る結果を残しているという。

Jasperは先頃フォーマル技術を活用した新製品「ActiveDesign」を発表したばかりで、3月より製品販売を展開する予定となっている。

関連記事:

米Jasper、業界初デザイン動作からRTLの解析・デバッグを行う新ツールを発表

※「ActiveDesign」の関連記事を当サイトで掲載中

※Jasper Design Automation社

※CyberTec株式会社(Jasper製品日本代理店)

2009.02.18

2009年2月17日、設計初期段階でのアーキテクチャ探索を実現するESLツール「CoFluent Studio」を手掛ける仏CoFluent社は、同社の2008年の営業実績として顧客数を前年比2倍に増やした事を発表した。

コフルエントによると、同社は仮想システムシミュレーション技術を用いたアーキテクチャ探索ツール「CoFluent Studio」の提供により、その顧客数を拡大。業界のアナリストGart Smith氏の2008年ESL市場トレンドレポートにて、シノプシス、メンターらと合わせてArchitect Workbench and ESL Design and Entry market segments,のトップ3にランキングされるまでにその存在感を確立した。

尚、コフルエントの売上の半分はスマートフォン関連の顧客によるもので、かの有名なBlackBerryの開発にも「CoFluent Studio」が利用されているとの事。顧客の中には特許出願のために、技術の確認環境として「CoFluent Studio」を活用している例もあるという。

※コフルエントデザイン社

2009.02.18

2009年2月2日、マグマは、同社のフィジカル・ベリフィケーションツール「Quartz DRC」と「Quartz LVS」のバージョンアップを発表した。

プレスリリース文

発表によるとマグマは、複数マシンによる分散処理などにより「Quartz DRC」と「Quartz LVS」のランタイムを大幅に削減することに成功。更にサードパーティのフィジカル・ベリフィケーションツール(恐らくメンターの物理検証ツール「Calibre」)のファイルをインポートする機能を追加し、他社製品からの置き換えの敷居を下げた。

「Quartz DRC」と「Quartz LVS」は、他社のインプリメントツールとの互換も保持しているが、当然ながら自社のインプリメント環境「Talus」とシームレスに連携できるため、マグマのインプリメントツールを利用する顧客にとっては、「Quartz DRC」と「Quartz LVS」を使えば、物理検証ツールからの不要なデータ変換を省いた効率的な統合インプリ/検証環境を構築できるというメリットが生まれる。

マグマのユーザであるデザイン・コンサルティング会社Fastrack Design社では、Talusベースのデザインフローで、「Quartz DRC/LVS」の新バージョンが従来の検証ツールと比較して約3倍ランタイムが改善されていることを確認したという。

※マグマ・デザイン・オートメーション株式会社

2009.02.17

2009年2月16日、SoC/組込みシステム向けのデザインサービスを手掛けるインドのCircuitSutraTechnologies社は、英GreenSocsとSystemCデザインサービスで提携した事を発表した。

CircuitSutraは、2005年設立のインドのベンチャーで、主にSoC/組込みシステム向けのソフトウェア開発サービスを提供中。設立当初からSystemCのモデリングを手掛けており、世界各国の顧客にモデリングサービスを提供した実績がある。

CircuitSutraとGreenSocsとは、協力して顧客にSystemCのモデリングサービスを実施した事があり、その成功経験をビジネスとして他の顧客に展開すべく、今回正式にSystemCデザインサービスにおける提携を発表した。

両社の手掛けるデザインサービスは、SystemC TLMのモデリングを中心に仮想プラットフォームの構築など、GreenSocsがオープンソースで公開している各種SystemCモデルをベースとしたものとなる。

※CircuitSutra Technologies社

※GreenSocs社

2009.02.15

2009年2月11日、シノプシスは、VMM準拠の検証IPを提供する「DesignWare Verification IP Alliance program」の始動を発表した。

プレスリリース文

シノプシスの発表によると「DesignWare Verification IP Alliance program」は、VMM準拠の検証IPをより広範囲に設計者に提供するためのプログラムで、検証IPベンダのネットワークを構築しVMM準拠の検証IPのラインナップを拡充するもの。プログラムに参加した企業から提供される検証IPは、シノプシスのガイドラインやVMM評価ツールを用いて開発され、一定の品質とユーザビリティが保証された形で最終的に「DesignWare Verification IP Alliance program」を通じてユーザーに提供される。

今回のプログラム始動に伴い、インドのデザインサービス会社eInfochipsと、ルーマニアの検証サービス会社NoBugの2社がプログラムメンバーとして参画。両社とも「Synopsys VMM Catalyst Program」のメンバーでその実績からプログラムへの加入が認められた。

現在、同プログラムを通じてHDMIの検証IPを入手できる。

※DesignWare Verification IP Alliance program

※日本シノプシス株式会社

2009.02.14

2009年2月12日、シノプシスは、同社のスタティック・タイミング解析ツール「PrimeTime」の機能強化を発表した。

プレスリリース文

シノプシスの発表によると今回の「PrimeTime」の機能強化は大きく2つ。

一つはマルチコア・プロセッシング対応で、マルチコアCPUを搭載したマシンでの処理が可能に。もう一つはランタイムの改善でシノプシスによるとこれら2つの機能強化により処理速度は最大2倍に向上。その効果は半導体ベンダにて100万-5000万ゲートのデザインで確認済だという。

※日本シノプシス株式会社

2009.02.13

2009年2月12日、メンター・グラフィックスは、同社のインテリジェント・テストベンチ自動化ツール「inFact」が検証メソドロジOVMをフルサポートした事を発表した。

プレスリリース文

発表によると今回の「inFact」のOVMサポートにより、OVM準拠の検証コンポーネントおよびシーケンスと「inFact」がのプラグ&プレイで連携することが可能に。具体的には「inFact」のシーケンスをユーザが開発したOVMシーケンスを補完したり、置き換えることが可能となり、インテリジェントすなわち賢く検証シナリオやテストベンチを自動生成する「inFact」の機能によって既存のOVM環境を強化することができる。

「inFact」は、機能仕様ルールから重複の無いテストパターンを自動生成する機能を有しており、バグの無いテストパターンを手間無く効率的に自動生成作成する事が可能。テスト項目と検証対象の機能仕様をルールとしてツールに与えると、目的とするテスト項目に則した冗長性の無い全てのテストパターンを自動生成し、機能カバレッジの向上に貢献する。

昨年7月には、テスト・シーケンスを重複することなく大規模シミュレーションを複数のCPUに分散するための分散処理のマネンジメント機能「Simulation Distribution Manager」が追加されている。

※メンター・グラフィックス・ジャパン株式会社

2009.02.12

2009年2月12日、国内のEDAベンチャー、ギガヘルツテクノロジーは、パワーインテグリティ解析ツール「PDN Designer」の発売を開始したと発表した。

発表によると「PDN Designer」は、設計フローの上流の回路設計のフェーズで使用可能なPI解析ツールで、仮想電源プレーン形状、電源スペックを与えることで、ターゲットとするべき電源インピーダンスを算出させることが可能。この条件を満たすべきデカップリングキャパシタの容量と個数の概算値を算出し、最適化を図る事ができる。

解析手法としてはChip/PKGを簡易モデルとして入力出来るようになっており、また電源プレーンの形状からモデル算出が出来る機能があり、Chip/PKG/PCBの組合せ解析を実施し解析品質を向上させている。

また、本ツールは、自社開発のSPICEを内臓しており、従来より約100倍以上高速な解析を行うことが可能。S-Parameterモデルにも対応しており柔軟性も高く、直感的なわかりやすいユーザーフレンドリーな操作性で、これまでパワーインテグリティが考慮できなかった設計者にも最適。

尚、同製品はサイバネットシステムによる代理店販売が決定しており、本日開催されるサイバネットシステム主催の「EDA Forum 2009」でも紹介される予定。

ギガヘルツテクノロジーは、2005年設立のベンチャー企業で、自社開発の高速SPICEのOEM提供や、解析サービスなどを行っている。

※ギガヘルツテクノロジー株式会社

※サイバネットシステム株式会社

2009.02.12

2009年2月10日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automation社は、新製品「Analog FastSPICE Nano™ (AFS Nano)」を発表した。

プレスリリース文

発表によると新製品「AFS Nano」は、ブロック単位のアナログ・シミュレーションをターゲットとしたSPICEシミュレーターで、そのキャパシティは最高5000素子。最高100万素子まで対応する同社の「Analog FastSPICE」と比べるとデザインの規模は制限されるが、その価格は年間ライセンスで1900米ドルと破格。正確なSPICE精度を保証し、その処理速度は「Analog FastSPICE」と同様に市場の従来製品より5-10倍高速だという。

同社の「Analog FastSPICE」は、2006年の発売以降、既に50社以上の顧客を持ち、アナログ、ミックスドシグナル、RF設計の分野で旋風を巻き起こしている。

※Berkeley Design Automation社

2009.02.12

2009年2月11日、EDAの業界団体米EDA Consortiumは、ケイデンスのCEO兼社長のLip-Bu Tan氏を同団体の運営役員(Board of Director)に指名した事を発表した。

プレスリリース文

EDAコンソーシアムは、これまでBoard of Directorの一員だったAgility社のCEO Dave Burow氏の辞任を受け、その後任に今年1月にケイデンスのCEO兼社長に就任したLip-Bu Tan氏を指名。同氏が2010年までのボードメンバーとしてEDAコンソーシアムの運営に加わる事になった。

現在、EDAコンソーシアムのボードメンバーは、チェアマンを務めるメンターのCEO Walden C. Rhines氏以下、下記業界関係者が名を連ねている。

Aart de Geus(CEO of Synopsys)

Kathryn Kranen(CEO of Jasper Design Automation)

John Bourgoin(CEO of MIPS Technologies)

John Kibarian(CEO and co-founder of PDF Solutions)

Rajeev Madhavan(chairman & CEO of Magma Design Automation)

Chris Rowen(founder & CTO of Tensilica)

Sanjay Srivastava(president and CEO of Denali Software)

関連記事:

ケイデンスの新社長兼CEOにリップ・ブー・タン氏が就任

※EDAC(EDA Consortium)

2009.02.11

2009年2月10日、SystemC入力の動作合成ツールを手掛けるForte Design Systemsは、2008年売上が過去最高を記録した事を発表した。

プレスリリース文

発表によると、フォルテの2008年度の売上は年間を通じて好成績を残し、売上額は過去最高を達成。08年10月?12月のQ4に関しては世界的に経済状況が混乱する中、前年比30%増という結果を残した。

フォルテは売上増加の要因の一つとして、大手企業による複数年契約の獲得を公表。既存顧客である東芝情報システムやNXPがライセンスを複数年契約で更新したという。

フォルテの動作合成ツール「Cynthesizer」の次期バージョンは、SystemC2.2のサポートや「インタフェース・ジェネレータ」機能の強化、合成用IPのラインナップなどを予定している。

関連記事:

【EDSFレポート】フォルテは売上順調、今後は動作合成回りの設計容易化を目指す

フォルテ・デザイン・システムズ株式会社

2009.02.11

2009年2月10日、検証IPを中心とした検証ソリューションを手掛ける米Avery Design Systemsは、同社の検証IP「USB-Xactor」がUSB 3.0をサポートした事を発表した。

プレスリリース文

発表によると今回USB 3.0をサポートしたAveryの検証IP「USB-Xactor」は、Bus Functional Models (BFM)、protocol checkers、directed and random compliance test suites、reference verification frameworksから成る検証ソリューションで、SystemVerilogベースの検証メソドロジVMMとOVMに対応している。

Averyは PCI Express,、Serial ATA、Parallel ATAなどの検証IPを供給してきた実績があり、USBの検証IPも以前から提供している。また、分散処理によるRTLシミュレーションの高速化システムなども提供している。

USB 3.0の検証IPは、デナリソフトウェアがいち早く市場に投入し、すぐにシノプシスが追随。ケイデンスもリリースする計画で、かなりHOT。検証IPの普及がこれら製品の供給を後押ししていると言える。

ちなみに日本国内にAvery製品の販売代理店は無い。

※Avery Design Systems社

2009.02.10

2009年2月10日、ESLツール大手のコーウェアと高速メモリ・アーキテクチャのライセンス企業Rambusは、Rambus社のXDRメモリ・アーキテクチャ対応の包括的なESL設計環境を発表した。

プレスリリース文

発表によると両社の協業により、コーウェアがRambusのXDRメモリ・サブシステムの各種SystemCモデルを提供。それらSystemCモデルはXDRメモリ・サブシステムの様々な構造設定に対応しており、コーウェアの仮想環境「CoWare Platform Architect」上で使用することで、最終アプリケーション、デザインのコンフィグレーション、デバイス・タイプなどの様々なオプションに対して、完全なシステム性能解析が可能。ハードならびにソフトウェアの設計生産性を大幅に向上できる。

コーウェアから提供されるトランザクション・レベル・モデルには、XDRメモリ・コントローラ、メモリ・コントローラ・インターフェイス (PHY)、3.2Gbpsから4.8Gbpsの速度を実現するXDR DRAMデバイスが搭載されている。

※コーウェア株式会社

※Rambus社

2009.02.10

2009年2月10日、ケイデンスは、シャープのシステムデバイス事業部がケイデンスのエミュレータ・アクセラレータ「Incisive Palladium III」を採用したことを発表した。

プレスリリース文

ケイデンスの発表によるとシャープは、システム設計・検証フロー向けに「Palladium III」を採用。従来のFPGAを使用したプロトタイプとブレッドボードによる手法よりも検証環境を迅速かつ容易に構築し、システム設計品質の向上を実現した。

ケイデンスは「Palladium III」を用いたシャープの成功例の説明として以下の5点を挙げている。

・FPGAプロトタイピング/ブレッドボードよりもコンパイル時間とシステムの立ち上げ期間を短縮

・ブレッドボードの開発工数とデザインの分割マッピング(複数FPGAへの)の工数が不要

・外部接続アダプタ「SpeedBridge」を用いる事で検証インタフェースの立ち上げを簡素化

・Incisiveコンパイラを使用して検証時間を短縮

・ハードおよぶソフトのデバッグにデバッグ機能「FullVision」を活用

※日本ケイデンス・デザイン・システムズ社

2009.02.10

2009年2月9日、シノプシスは、ラピッド・プロトタイピング環境「Confirma」の機能拡張を発表した。

プレスリリース文

シノプシスのラピッド・プロトタイピング環境「Confirma」は、昨年買収したシンプシシティ社のASIC検証ソリューションをベースとしたもので、プロトタイピング・ボード「HAPS」、FPGAへのインプリメント用のRTLパーテショニングツール「Certify」、TotalRecallテクノロジを搭載したFPGAデバッグツール「Identify Pro」によって構成されている。今回のシノプシスの発表はこれら既存の「Confirma」に、昨年ProDesign社から買収した「CHIPit」製品が加わったというもの。

シノプシス本社マーケティング及び事業開発部門のTom Borgstrom氏によると、シノプシスがターゲットとするハードウェアベース検証の市場は、いわゆるエミュレータと呼ばれる高額な大規模システムを除いたFPGAベースのプロトタイプボードを中心とした成長市場で、その理由として速さ、安さ、手軽さ(容易な利用)を指摘。「CHIPit」製品は、既存のプロトタイピング・ボード「HAPS」と同じFPGAベースのボードを主体としたものであるが、充実したソフトウェア環境を用いてエミュレータライクにデザインを検証したい場合は「CHIPit」、手間覚悟で実チップ並みのスピードを実現したい場合は「HAPS」と使い分けが可能だという。

「CHIPit」と「HAPS」は様々な違いがあるが、根本的な違いはボード上のFPGAの接続方法で、スイッチデバイスで複数FPGAを接続する「CHIPit」に対して「HAPS」は直接続。当然、「HAPS」の方が速度が出るがデザインのインプリは「CHIPit」の方がプッシュボタン式でイージー。「HAPS」は生身のボードであるため開発用の製品実機と接続して利用可能だが、「CHIPit」はそれが出来ない分、SCE-MIインタフェースや論理シミュレータとのブリッジ、C/C++/TCL APIなど他環境との接続インタフェースが用意されている。

「CHIPit」と「HAPS」は様々な違いがあるが、根本的な違いはボード上のFPGAの接続方法で、スイッチデバイスで複数FPGAを接続する「CHIPit」に対して「HAPS」は直接続。当然、「HAPS」の方が速度が出るがデザインのインプリは「CHIPit」の方がプッシュボタン式でイージー。「HAPS」は生身のボードであるため開発用の製品実機と接続して利用可能だが、「CHIPit」はそれが出来ない分、SCE-MIインタフェースや論理シミュレータとのブリッジ、C/C++/TCL APIなど他環境との接続インタフェースが用意されている。

60種以上用意されている拡張ボードは両製品に対して共通利用可能。現在「CHIPit」と「HAPS」は、2つの異なる製品として提供されているが、将来的にはソフトウェア環境も含めて統合されていく予定だという。

関連記事:

関連記事:

【EDSFレポート】シノプシス、ハードベースツールを拡充し検証環境は万全の体制

シノプシス、独ProDesign社プロトタイプボード「CHIPit」事業部を買収へ

※日本シノプシス株式会社

2009.02.09

2009年2月5日、アナログ/ミックスドシグナル設計統合環境およびMEMS向け設計環境を手掛ける、Tanner Research社のEDA事業部Tanner EDAは、業界20周年を迎えその実績を発表した。

発表によると同社は、創業以来年間平均20%の成長をとげ、直近9年間においては8期の黒字。これまで、同社のアナログ/ミックスドシグナル設計統合環境およびMEMS向け設計環境の販売実績は、計67カ国、4000顧客、25000ライセンスに達しているという。

同社のソフトウェア製品の特徴は「PCベースの設計環境」という点で、設計環境がUNIXワークステーションからPCへと移り変わる流れに上手く乗りビジネスを成功させている。代表的な製品は、回路図入力エディタ「S-Edit」 、アナログシミュレータ「T-Spice」、レイアウトエディタ「L-Edit」、物理検証エンジン「L-Edit DRC/Extract/LVS」など。

※タナーリーサーチジャパン株式会社

2009.02.09

2009年2月5日、無償の仮想HWプラットフォームを提供する英Imperasは、SystemC TLM 2.0ベースのCPUモデルの公開を発表した。

プレスリリース文

発表によると、ImperasがSystemC TLM 2.0で開発した組込みソフト開発用のCPUモデルは、Imperasの提供する命令セットシミュレータ「OVPSim」上で最高1000MIPSという高速で動作。これまで提供していたARM、MIPS、ARC、Tensilica、OpenCoreの各種CPUモデルの全てについてTLM 2.0版を用意しており、これらモデルはシミュレータと合わせて無償の仮想HWプラットフォーム「OVP:Open Virtual Platforms」としてオープンソースで提供される。

Imperasによると、2008年3月に仮想HWプラットフォームを公開してから「OVP」のソフトウェアやデモ、プレゼンのダウンロード数は約10,000件。シミュレーターは500以上のダウンロードを記録。これまでImperasの環境は「OVP」で閉じらた仮想環境であったが、今回、OVPsimシミュレーターとネイティブOSCI TLM-2.0のインターフェースが用意された事でその利用価値は大幅に拡大すると言える。

尚、Imperasは、無償で仮想プラットフォームを提供し、それを用いたソフトウェア開発用のツールを販売するというビジネスを展開している。

※OVPサイト

※Imperas社

2009.02.08

1月23日 EDS Fairの特設ステージにおいて、若手エンジニアや元エンジニア向けのセッション「今さら聞けない高位合成 -一から学ぶ高位合成-」が開催された。

会場は立ち見も多く見られるほどの満員盛況ぶりで、シャープ株式会社 電子デバイス事業本部の山田 晃久 氏は、C言語設計のためのアーキテクチャ探索を始めとする高位合成の基本技術を始め、従来のRTL設計と抽象度を上げた動作レベル設計との違いまでをポイントをうまくまとめながら説明してくれた。

次に、高位合成ツールによる設計適応事例の紹介があり、同社の液晶テレビに搭載されたフレームレート変換機能付きLSIの設計において、回路全体の90%(約2000万ゲート)に高位合成ツール「Bach」を用い、アルゴリズムがフィックスしてからテープアウトまでを約2ヶ月で完了し、リスピンなしで量産ができたという成功事例を披露した。

この適応事例の成功のポイントとしては、アルゴリズム開発と、レイアウトまでを含めたRTL検証が並行してできたことだという。

さらに山田氏は、今後の課題として以下の4つをあげて高位合成による設計への期待とした。

さらに山田氏は、今後の課題として以下の4つをあげて高位合成による設計への期待とした。

・タイミング収束 -高位合成時の見積り精度

・静的検証 -動作レベルとRTLの等価性検証

・ECO(Engineering Change Order)への対応 -抽象度と解析容易性のトレードオフ

・記述スタイルの確立

最後に、C言語による高位合成設計における3つの留意点をあげ発表を締め括った。

1.「全ての回路をCで設計するのが良いとは限らない。 得意なところでの適応が必要」

2.「良いツールがあれば、良い回路ができるわけではない。人手は必要。」

3.「Cを使えば高速検証ができるわけではない。抽象度を高く記述することが必要」

1980年代後半に登場した論理合成ツールは、1990年代に普及し始め2000年代には大半の回路設計に使われるようになった。同様に、1990年前後、研究レベルから商用ツールとして登場してきた高位合成ツールは、2000年後半になって、ようやく実設計への適応が多々聞かれるようになり、今後の実用レベルでの普及が期待されるステージになってきたと言えよう。

= EDA EXPRESS 特別レポーター =

2009.02.08

Electronics Design and Solution Fair 2009に出展していたALTOS社、シリコン・フロントライン・テクノロジ社のブースレポート。

新興ベンダエリアに出展していたセルキャラクタライズの注目ベンダALTOS Design Automation社と、新世代RC抽出ツールを提供するシリコン・フロントライン・テクノロジ社は、いずれも米国カリフォルニアを拠点とする企業で、丸紅情報システムズが国内代理店として製品を提供している。

ALTOSは既にSSTA用セル・キャラクタライゼーションのツールとして足場を築いているが、今回投入した新製品はエンベデッド・メモリのキャラクタライズを行うLibrateMXと、ライブラリのバリデーションを行うLibrateLV。

LibrateMXはメモリコア全体の中からワーストケース・パス、クリティカル・パスを自動的に切り出しそのパスについてダイナミック・パターンで精度の高いシミュレーションを実行するというアプローチで精度の高いキャラクタライズを行う。

メモリセル全体を漠然とFast SPICEでシミュレーションしても精度誤差は10%もある。LibrateMXは効率的、高速に精度の高いキャラクタライズが行える。

シリコン・フロントライン・テクノロジ社はレイアウト抽出ツールの会社。3つの製品ラインがある。R3Dは、パワーMOS混載チップ用高精度・高速抽出/解析ツール、F3Dは、大規模・超高速 次世代3D寄生素子抽出ツール。 そして新製品のH3Dは、F3Dの階層対応版でより高速化が図れるという。欧米5社で採用されており、日本でも評価が行われている。

※ALTOS DESIGN AUTOMATION社

※シリコン・フロントライン・テクノロジ株式会社

= レポーター 山田佳子 =

レポータープロフィール:

EDAツールのアプリケーション・エンジニアとして業界の成長とともにフロントエンドからバックエンドまで幅広い設計技術を経験。

好奇心と情熱に突き動かされるまま、様々な活動を展開中。

わくわくする技術とビジネスを語り合いながら飲めれば幸せ。

2009.02.07

Electronics Design and Solution Fair 2009に出展していたコ・フルエント デザインのブースレポート。

コ・フルエントは昨年に続きESLツール「CoFluent Studio」を展示。同製品は、組込みソフトやISSモデル、ハードIPを必要とせずに、抽象化されたモデルを用いてシステムの性能解析を行うESLツール。ポジションとしては、コーウェアやVaSTの提供する精度の高い仮想環境の更に上に位置するツールで、仕様レベルの情報から「早い段階でシステムの性能を大まかに見極めたい」というニーズにマッチしている。

コ・フルエント日本オフィス マネージャーの山下氏によると、日本での本格営業を開始したこの1年間で大手数社への導入を実現。コンスーマ機器を開発しているユーザーに加えて、車載システムの開発へ適用を考えている顧客もいるという。

コ・フルエント日本オフィス マネージャーの山下氏によると、日本での本格営業を開始したこの1年間で大手数社への導入を実現。コンスーマ機器を開発しているユーザーに加えて、車載システムの開発へ適用を考えている顧客もいるという。

「CoFluent Studio」は、仏ナント大学における長年の研究成果をベースとした製品で、既に製品のコア機能は固まっており現在は周辺のインタフェースの整備を進めている最中。今年のDACで発表する予定の新バージョンはEclipseベースとなる予定で、MATLAB Mファイルのインポートや他社ESLツールとの連携、ソフトウェアの実装用コード生成機能の追加なども計画されていると聞いた。

尚、山下氏の話では「CoFluent Studio」のユーザーは殆どがもとからのSystemCユーザーで、世界的には一気に顧客数が倍増。ノキア、TIといった大手大口顧客が4社あり、スマートフォン「BlackBerry」で有名なRIM社(Research In Motion)も同社製品のユーザーだという。

尚、山下氏の話では「CoFluent Studio」のユーザーは殆どがもとからのSystemCユーザーで、世界的には一気に顧客数が倍増。ノキア、TIといった大手大口顧客が4社あり、スマートフォン「BlackBerry」で有名なRIM社(Research In Motion)も同社製品のユーザーだという。

※コ・フルエントデザイン社

2009.02.07

Electronics Design and Solution Fair 2009に出展していたデナリソフトウェアのブースレポート。

デナリの今回の展示の目玉は、昨年11月に業界に先駆けて製品化した「USB 3.0」の検証IP「PureSpec」。といっても、ブース正面に大きなグラフィックを掲げていた以外、ブース内に同USB3.0仕様をサポートした「PureSpec」の展示は見当たらず、ブース内ももっぱら顧客とのミーティングに忙しい様子。

聞くところによると「USB 3.0」のサポートは相当なインパクトがあったようで、国内ユーザーからも引き合いが多数。1月23日に行われた同社の出展社セミナー「USB3.0デザインのコンプライアンス・チェックの進め方」へは、定員30名を超える聴講者が訪れ立ち見もあふれる盛況ぶりだったという。

聞くところによると「USB 3.0」のサポートは相当なインパクトがあったようで、国内ユーザーからも引き合いが多数。1月23日に行われた同社の出展社セミナー「USB3.0デザインのコンプライアンス・チェックの進め方」へは、定員30名を超える聴講者が訪れ立ち見もあふれる盛況ぶりだったという。

マーケティングの鈴木氏によると、検証IPというもの自体が設計現場でも定着し、もはや「買うのが当たり前」といっても過言ではないほど利用者が増えてきている状況。デナリの検証IP「PureSpec」は長年の実績もさることながら、検証メソドロジやシミュレータ、設計言語に依存しないニュートラルな立場の製品としてユーザーの支持を得ているとの事だった。

確かにVHDLやe言語などの資産を活用しているユーザーにとっては、言語やメソドロジに非依存な検証IPは重宝されると感じた。

関連記事:デナリの検証IP「PureSpec」が早くもUSB3.0仕様をサポート

関連記事:デナリの検証IP「PureSpec」が早くもUSB3.0仕様をサポート

※デナリソフトウェア株式会社

2009.02.07

2009年2月5日、マグマとLogicVisionは、マグマのATPG技術をLogicVisionにライセンスする事を発表した。

プレスリリース文

発表によるとLogicVisionは、BISTツールを補完するATPGソリューションを開発するためにマグマとの間でATPG技術のライセンス供与について合意。現在、マグマのATPG技術を用いたATPGツールおよびATPG圧縮ツールを開発中で、マルチスレッド技術を用いたATPGツールは今年の秋にはリリースされる予定。処理能力の高さとマグマのインプリメントフローとの親和性が高いフィジカル考慮のテスト生成がウリとなる。

マグマは2007年にATPGツール「Talus ATPG」とATPG圧縮ツール「Talus ATPG-X」を発売したが、2008年後半以降の経済状況の悪化に伴い組織の再編成を検討。「選択と集中」という戦略の中でATPGソリューションについては同社製品ラインナップから消えていた。

今回の件は、ATPG技術資産を有効に処理したいマグマと、自社のDFT製品ポートフォリオを拡張したいLogicVisionの利害がうまく一致した結果と言えるだろう。

関連記事:

マグマがリストラ敢行?組織再編成の実行を発表

LogicVision売上報告、2008年Q4は前年比微増の300万ドル

※マグマ・デザイン・オートメーション株式会社

※LogicVision社

2009.02.07

2009年2月5日、マグマは同社のリストラ策を発表した。

プレスリリース文

マグマは、同社従業員数の17%削減と従業員の給与削減を決定。現在900名いる従業員は750名程度に減らされ、北米とヨーロッパのセールス&サポートオフィスを1ヶ所ずつ閉鎖する予定で、これらリストラ策は今年の4月までに実施される。既に役員報酬は20%カットされているが、従業員の給与見直しと人員削減により同社の2010会計年度の経費は約2000万ドル削減されるという。

関連記事:

マグマがリストラ敢行?組織再編成の実行を発表

※マグマ・デザイン・オートメーション株式会社

2009.02.06

2009年2月5日、英ARMは2008年Q4(10-12月)の売上を報告した。

プレスリリース文

発表によると、ARMの2008年Q4(10-12月)の売上は、前年同時期比15%増の1億4940万ドル。前期Q3で更新した1四半期の最高売上額の記録を塗り替えた。

2008年通期の売上合計は前年比6%増の5億4620万ドルで、過去最高を達成。不況の中、ロイヤリティ収入の増加によって同社の業績は伸び続けている。

しかし、さすがのARMも来期2009年度の売上額を4億6000万ドル程度と悲観的な予測をしている。

※アーム株式会社

※アーム株式会社

2009.02.05

2008年2月2日、第19回米EDN誌「INNOVATION AWARDS」のファイナリストが発表された。

発表内容

「EDN Innovation Awards」は、EDA業界内でも認知度の高い権威ある賞で、エレクトロニクス業界における優れた製品および技術を表彰するもの。毎年2月にEDN誌の記者によって選出されたファイナリストが発表され、その後3月にEDN読者のオンライン投票結果によって受賞者が決定される。

ファイナリストは部門毎に各4製品・技術がノミネートされるが、今年は昨年よりも8部門多い計28部門、112製品・技術がファイナリストに選出されている。

昨年のEDA関連部門は、「Digital IC Design Tools」部門と「PCB、FPGA、and Custom IC Tools」部門の2つだけであったが、今年は倍の4部門に拡張されそれぞれ下記製品がファイナリストに選ばれている。メンターの配置配線ツール「Olympus-SOC」とシーケンスの消費電力最適化ツール「PowerArtist」は先頃「DesignCon」の「Design Vision Award」を受賞したばかりだが、今回のEDN「INNOVATION AWARDS」にもノミネート。惜しくも「Design Vision Award」では負けたが、ChipVision社の動作合成ツール「PowerOPT」は今回もノミネートされている。

EDN読者によるオンライン投票は2月27日まで行われ、アワード受賞者は3月30日にサンノゼで発表される予定。

◆Design Analysis部門ノミネート製品

・Incisive Palladium DPA (dynamic-power analysis) (Cadence Design Systems)

・JasperGold formal-verification tool (Jasper Design Automation)

・Olympus-SOC timing analyzer (Mentor Graphics)

・PowerArtist RTL tool (Sequence Design)

◆Design Creation and IP部門ノミネート製品

・C-to-silicon compiler (Cadence Design Systems)

・Intelli DDR3 memory interface (Virage Logic)

・PowerOpt RTL tool (ChipVision Design Systems)

・Zroute chip-level router with integral DFM analysis (Synopsys)

◆PCB, FPGA, and Mixed-signal/RF ICs 部門ノミネート製品

・Integrated Software Environment (ISE) 10.1 (Xilinx)

・RF Design Solution (Mentor Graphics and Agilent Technologies)

・Simics Hybrid Simulation solution (Virtutech)

・Titan platform (Magma Design Automation)

◆System-level Synthesis部門ノミネート製品

・Matlab/Simulink synthesis technology (Altera)

・Simscape (The MathWorks)

・Webench power designer (National Semiconductor)

・Webench sensor designer (National Semiconductor)

関連記事:

メンターとシーケンスのEDAツールが「2009 Design Vision Award」を受賞

DesignCon、今年のDesignVision Awardsのファイナリストが出揃う

※米EDN誌

2009.02.05

2009年2月4日、ケイデンスは2008年Q4(10-12月)の売上を報告した。

プレスリリース文

発表によると、ケイデンスの2008年Q4(10-12月)の売上は、前年同時期比50%減の2億2700万ドル。前期Q3に続いて収支は赤字となり、16億4000万ドルの損益を計上した。(2007年Q4は1億2000万ドルの黒字)

ケイデンスの2008年売上合計は前年比36%減の10億400万ドル、2007年の収支合計は18億5000万ドルの赤字という結果になった。

※金額は全てGAAP基準による会計結果

尚、ケイデンスは2009年Q1(1-3月)の売上を2億-2億1000万ドルと予測。この数字はサブプライムの影響が出始めた2008年Q1売上の70%相当となる。

※日本ケイデンス・デザイン・システムズ社

※日本ケイデンス・デザイン・システムズ社

2009.02.05

2009年2月3日、メモリIPの大手、米Virage Logicは、同社の「ASAPメモリIPアーキテクチャ」がシャープに採用されたことを発表した。

プレスリリース文

シャープは、以前からビラージロジックとパートナー関係にあり、今回更に関係を強化・拡張。ハンドヘルド民生機器を対象としたCIS(CMOSイメージセンサー)プロセス向けに、最新CMOSイメージセンサーデバイス向けに最適化されたビラージロジックの「ASAPメモリIPアーキテクチャ」を採用した。

シャープは、小型化でセンサーモジュール業界をリードする立場を維持するために、小型で費用効果の高い設計で高性能機能を実現する必要があり、実績のあるビラージとの関係を拡張した。

※Virage Logic社

2009.02.04

2009年2月4日、メンター・グラフィックスは、PCB電源プレーン構造の高精度解析環境「HyperLynx® PI(Power Integrity)」を発表した。

プレスリリース文

発表によるとメンターは、高性能/高集積度/多ピンICに対応した電源分配システムの設計において回路設計者とレイアウト設計者が緊密に協力して作業する必要性に応えるべく、新製品「HyperLynx® PI」を開発。同社既存のシグナル・インテグリティの解析・検証用製品「HyperLynx」と「HyperLynx® PI」を組み合わせることで、適切な電源分配システムを設計できると同時に、設計期間と試作の繰り返し、製造コストを削減できる。

具体的には、「HyperLynx® PI」を用いる事で電源やグランドプレーンの構造とデカップリング・キャパシタの必要数、および位置を判断することができ、過度に保守的な設計による製品コストの増大を回避可能。設計技術者は電源供給ネットワークに対するコスト効果の高いルールを作成し、"What-if"解析で重要な問題を設計サイクルの早期に解決し、高価な"試作/テスト"を回避することができるという。

※メンター・グラフィックス・ジャパン株式会社

2009.02.04

Electronics Design and Solution Fair 2009にて行われた図研の出展社セミナー「動作合成ツールの必然性と可能性」のレポート。

「動作合成ツールの必然性と可能性」 NEC中央研究所 EDA開発センター 研究部長 若林一敏氏

(※若林氏は体調不良により欠席、代理の方による講演となった。)

内製ツールとして、15年の実設計適用の実績があるCyberWorkBench(CWB)は、動作合成のみならず、形式検証やSW/HW強調検証の工程までをシームレスに扱う統合SoC開発プラットフォームとして、全てをC言語で実行するというAll-in-Cのコンセプトを謳っている。

CWBでは、動作合成の得意分野である?演算処理系に加え、?今後の需要が高まるだろう制御フローインテンシブ(演算とシーケンスが複雑に絡み合った回路)、さらには動作合成には向かないといわれていた?制御系ままでもC言語のみで設計が可能。ある適応例では、仕様設計からハード評価まで、RTLベース設計では14ヶ月の期間に対して、Cベース設計は8.5ヶ月、バグも低減、ソフト設計も平行して進められたため、工数削減が実現し、開発全体で数千万円ものコスト減となったという。

実際、NECでは、累積で4,000億円を超える商用チップで適応済みで、最近の事例では、2007年のSONY業務用カムコーダに搭載されたNECエレクトロニクス社の高性能リコンフィギャラブル・コアであるSTPエンジンの統合開発環境にCyberの技術が利用された。

実際、NECでは、累積で4,000億円を超える商用チップで適応済みで、最近の事例では、2007年のSONY業務用カムコーダに搭載されたNECエレクトロニクス社の高性能リコンフィギャラブル・コアであるSTPエンジンの統合開発環境にCyberの技術が利用された。

2009年Q1の新バージョンでは、アーキテクチャーの自動探索による様々なRTLのバリエーション出力・ループや関数の自動並列化、ビット幅自動調整機能強化、ネスト・ループや連続ループを1本のループパイプライン化するなどの機能が追加される予定。

※NECシステムテクノロジー株式会社

※株式会社図研

= EDA EXPRESS 特別レポーター =

2009.02.04

Electronics Design and Solution Fair 2009に出展していた図研/NECシステムテクノロジーのブースレポート。

NECシステムテクノロジーは、同社のC言語設計環境「Cyber Work Bench」の代理店である図研との共同出展。ブースでは「Cyber Work Bench」による最近の3つの設計事例を展示していた。

SONYの業務用CAMコーダ「PMW-EX1」に採用された、NECエレクトロニクス製ブリッジ・チップ「XBridge」を設計した事例は昨年のET2008でも紹介されたが、「XBridge」内のCPUコア「STPエンジン」の開発用にCyberを適用。「STPエンジン」は以前「DRP」と呼ばれていた動的再構成可能な独自のCプログラマブル・コアで、その専用開発環境の中にCyberの合成エンジンが組み込まれている。同環境はチップと合わせてNECエレクトロニクスから顧客に提供されているが、Cアルゴリズムから動作合成しマッピングするという技術はFPGAなどにも転用可能との事。

ドコモ製の3G携帯で使われているNECエレクトロニクス製の携帯向けLSI「Medity M1/M2」の事例では、同チップの大半のモジュールを「Cyber Work Bench」で合成。また、1月14日に発表されたばかりの同じくNECエレクトロニク製のSTB向けLSI「EMMA 3SL/LP」、「EMMA 3SL/L」の設計にも「Cyber Work Bench」を適用。同チップのうりであるSD放送対応に特化したH.264処理の部分を「Cyber Work Bench」で合成したという。

ドコモ製の3G携帯で使われているNECエレクトロニクス製の携帯向けLSI「Medity M1/M2」の事例では、同チップの大半のモジュールを「Cyber Work Bench」で合成。また、1月14日に発表されたばかりの同じくNECエレクトロニク製のSTB向けLSI「EMMA 3SL/LP」、「EMMA 3SL/L」の設計にも「Cyber Work Bench」を適用。同チップのうりであるSD放送対応に特化したH.264処理の部分を「Cyber Work Bench」で合成したという。

話を聞いたNECシステムテクノロジーの斉藤氏によると、「Cyber Work Bench」のLSI適用事例は既に数十品種に及んでいるとの事。来年初頭には新バージョンのリリースも予定していると聞いた。

話を聞いたNECシステムテクノロジーの斉藤氏によると、「Cyber Work Bench」のLSI適用事例は既に数十品種に及んでいるとの事。来年初頭には新バージョンのリリースも予定していると聞いた。

尚、同ブース内での図研の展示コーナーでは、同社のC言語設計サービスに関する展示をしており、ネットワークカメラ向けのJPEG評価ボードの設計例を紹介していた。

話によると同社のC言語設計サービスでは、実際に「Cyber Work Bench」を使っているとの事で、これまでの実績では人手によるRTL設計と比較して約2/3程度の工数で設計を完了。Cyber用のガイドラインなども用意して本格的にC言語設計サービスを展開しているという。

※NECシステムテクノロジー株式会社

※NECシステムテクノロジー株式会社

※株式会社図研

2009.02.04

Electronics Design and Solution Fair 2009に出展していたサイバーテックのブースレポート。

サイバーテックは、EDSFair開催前に発表されたばかりの米Jasper Design Automation社の新製品「ActiveDesign 」を展示していた。

サイバーテックの杉浦氏によると、新製品「ActiveDesign 」は設計者によるセルフテストの効率化を目指す製品で、フォーマル技術を活用してテストプランの作成や機能テストなどの設計支援を行う環境。もともとJasperが提供していた検証戦略のプランニングツール「GamePlan」がベースとなっており、それにフォーマル検証ツール「JasperGold」のビジュアライズ機能を追加し改良を加えた製品で、RTLコードを読み込みんでデータベース化する技術と、データベース化したデザインを解析する技術、解析結果をグラフィカルに表示する技術が盛り込まれている。

見せてもらったデモでは、RTLコードを読み込んで自動的にステートマシンの動きを解析し解析結果を波形表示。何を確認したかという確認項目とその波形を得れるので、それらを実行可能な仕様書やテストプランとして利用する事ができるほか当然、波形を見ながらコードをデバッグすることも可能。ステートマシンの動作解析だけでなくRTLコードに対し様々な機能チェックを行う事が可能で、何を確認するか?というチェック項目は、ユーザーがリストアップする事もできるし、ツールに自動抽出させることも出来るという。

尚、「ActiveDesign 」は単体製品として提供される製品で、既に北米では大手顧客が3社ほどついているとの話。同製品にはアサーション機能は含まれていないが、フォーマル検証ツール「JasperGold」と組み合わせて運用可能。フォーマル検証技術を用いて、デザインの過程でデザイン品質の向上を目指すというのが、この製品の最大の特徴と言える。

尚、「ActiveDesign 」は単体製品として提供される製品で、既に北米では大手顧客が3社ほどついているとの話。同製品にはアサーション機能は含まれていないが、フォーマル検証ツール「JasperGold」と組み合わせて運用可能。フォーマル検証技術を用いて、デザインの過程でデザイン品質の向上を目指すというのが、この製品の最大の特徴と言える。

サイバーテックのブースではフォーマル検証技術に関する冊子を配っていた。

※CyberTec株式会社(Jasper社代理店)

※CyberTec株式会社(Jasper社代理店)

※Jasper Design Automation社

2009.02.04

2009年2月3日、サンタクララで開催中のエレクトロニクス分野の国際学会「DesignCon」にて、今年の「Design Vision Award」の受賞者が発表された。

発表内容

今年のIC Design Tools部門の受賞製品は、メンター・グラフィックスの配置配線ツール「Olympus-SoC Parallel Timing Analysis and Optimization」。ChipVisionの動作合成ツール、XilinxのISEと競り勝って見事受賞。

Design Verification Tools部門の受賞製品は、シーケンスデザインの消費電力最適化ツール「Power Artist」で、こちらはAgilentとEVEに競り勝って受賞した。

各部門の受賞製品は以下の通りで、Semiconductor IP部門ではケイデンスのIP検索サイト「ChipEstimate.com IP Ecosystem」が受賞している。

■IC Design Tools 部門

Mentor Graphics for the Olympus-SoC Parallel Timing Analysis and Optimization

■Design Verification Tools 部門

Sequence Design for PowerArtist

■Interconnect Technologies and Components 部門

Molex Incorporated for the Impact Backplane Connector System

■PCB Design Tools and Technologies 部門

PCB Matrix for the Symbol Wizard

■Semiconductor Components and ICs 部門

Xilinx for the Xilinx® Virtex®-5 TXT FPGA Platform

■Semiconductor IP 部門

Cadence Design Systems for the ChipEstimate.com IP Ecosystem

■System Modeling and Simulation Tools 部門

Signal Integrity Software (SiSoft) for the Quantum Channel Designer

■Test and Measurement Equipment 部門

SyntheSys Research, Inc. for the DPP 12500A-4T

関連記事:

DesignCon、今年のDesignVision Awardsのファイナリストが出揃う

※DesignCon2009

2009.01.28

2009年1月27日、次世代配置配線ツール「Aprisa」を手掛けるATopTechは、同社の2008年の実績を発表した。

発表によると同社の2008年売り上げ実績は前年比250%を達成。顧客によるテープアウト数は前年比8倍に増加した。これらの実績は同社の新たな顧客8社からのオーダーによるもので、これまでの発表からするとその中にはBroadcom、シャープ、リコーらが含まれていると思われる。

尚、テープアウト実績の中には、同社初となる40nmデザインの成功も含まれており、2009年第1四半期に更に幾つかの40nmデザインのテープアウトを予定しているとの事。

配置配線ツール「Aprisa」は、処理速度の速さ、少メモリ、マルチスレッド化とマルチコア化の両方に対応したMCMM機能、容易な階層設計対応などが特徴。旧Avant!社R&Dチームが開発したツールでレイアウトツール分野に新風を巻き起こしている。

※ATopTech社

2009.01.28

2009年1月27日、リコンフィギュラブル・プロセッサを手掛けるテンシリカは、富士通マイクロエレクトロニクスが、顧客向けの民生用携帯機器向けデバイスの設計に、テンシリカのダイヤモンド・スタンダード330HiFiオーディオDSPを採用したことを発表した。

プレスリリース文

富士通マイクロエレクトロニクス IP開発統括部長 国安良男氏のコメントによると、今回同社がテンシリカのダイヤモンド・スタンダード330HiFiを音声処理用DSPとして選択したのは、エンドユーザーである同社の顧客がテンシリカの製品を高く評価しているため。低消費電力性、使用可能なオーディオソフトウェアの豊富なラインナップが評価されているという。

※テンシリカ株式会社

※富士通マイクロエレクトロニクス株式会社

2009.01.28

2009年1月27日、1.5GHz動作の高速FPGAを手掛けるアクロニクスは、自社FPGA向けの開発環境に関するメンター・グラフィックスとの契約を発表した。

プレスリリース文

発表によるとアクロニクスはメンターと論理合成環境「Precision Synthesis」のサポートを拡充する複数年契約を締結。2006年に自社のFPGA開発環境にメンターの「Precision Synthesis」を統合する契約を結んでいたが、今回はその契約を更に拡充するもの。アクロスは今後複数年にわたり、メンターの論理合成ツールを自社の開発スイートの一部として顧客に提供する。

アクロニクスは、最大1.5GHzの速度を誇るFPGA「Speedsterファミリ」のほかに耐放射線FPGAを提供中。今回の契約はこれら両製品に加え、将来的な製品もサポートの対象として含まれているという。

※アクロニクス社

※メンター・グラフィックス・ジャパン株式会社

2009.01.28

2009年1月23日、DRAM大手の独キマンダは、会社の再建を目的にドイツミュンヘンの地方裁判所に事業再生手続きを申請した事を発表した。

プレスリリース文

キマンダはDRAMの価格下落と金融危機に伴う資金調達難により財務状況が悪化。昨年10月からリストラ計画を進めており、昨年12月にはドイツのザクセン州、親会社のインフィニオン、ポルトガルの投資銀行から3億2500万ユーロの金融支援を受ける発表がなされていたが、期日までに最終合意に至らず現会計年度で必要な資金不足が生じてしまった。

キマンダは事業の再生に向け米国バージニア州リッチモンドにある200mm製造施設、ドレスデンにあるコンポーネントおよびモジュールのバックエンド製造施設を段階的に閉鎖。独ミュンヘンと中国西安における製品開発を統合し、人員や管理費の削減を進めている。同社は売上17.9億ユーロ(2008年会計年度)の業界第5位で、従業員は全世界で12200人。技術提携している日本のエルピーダの株価は、今回のキマンダの破綻を受けて一時急反発した。

※キマンダ社

2009.01.28

2009年1月22日、メモリIP大手の米Virage Logicは、同社のリストラ策を発表した。

プレスリリース文

発表によるとビラージロジックは全米4ヶ所ある研究所のうち、ニュージャージーとミネソタの研究所を閉鎖。合わせて営業人員の削減も行い、社員数を約13%削減する。営業人員の削減により営業力の低下が予想されるが、同社は前四半期にに発表した各国の市場をカバーする新たな代理店5社との連携によって低コストで営業を進めていくという。

※ビラージロジック社

2009.01.27

Electronics Design and Solution Fair 2009に出展していた日本イヴのブースレポート。

イヴは、FPGAベースのエミュレーション環境「ZeBu」シリーズを展示。ブース前にはメイド姿のコンパニオンが立ち、トレードマークの紫色の大型紙袋と合わせて会場でかなり目立っていた。

目立っている理由は他にもある。先日発表があった通り、イヴはこの業界苦境の中、売上げ前年比30%増を達成。M&Aが進んだ関係もあるが、エミュレーション市場では売上2位にまで上り詰めた。それだけではない、昨年リリースしたトランザクタ自動生成ツール「Zemi-3」に続いて、今度は新たな合成エンジン「zFAST (ZeBu Fast Synthesis)」をリリースと続々新製品・新機能を投入。つまり勢いがある。

目立っている理由は他にもある。先日発表があった通り、イヴはこの業界苦境の中、売上げ前年比30%増を達成。M&Aが進んだ関係もあるが、エミュレーション市場では売上2位にまで上り詰めた。それだけではない、昨年リリースしたトランザクタ自動生成ツール「Zemi-3」に続いて、今度は新たな合成エンジン「zFAST (ZeBu Fast Synthesis)」をリリースと続々新製品・新機能を投入。つまり勢いがある。

日本イヴ社長の岩上氏によると、先日発表したルネサステクノロジ以外にも大手4社が携帯電話向けSoCの開発で「ZeBU」を使用。MFP(マルチ・ファンクション・プリンタ)の世界でも大手がこぞって「ZeBu」を使用しており、その波はCAMコーダの開発分野へと広がっているとの事。ZeBuの最上位機種「ZeBu-XXL」の導入も順調に進んでいるという。

快進撃の理由を岩上氏に聞くと、製品コスト、ソフトウェア環境、サポート体制の3点を指摘。他社エミュレータよりも安く場合によっては時間ライセンスで導入できるコスト面での優位性はユーザーにとって大きなメリットとした上で、競合の追随を許さないソフトウェア環境(コンパイラ技術、トランザクタなど)のパフォーマンスとサポート体制にも自信があると語っていた。

快進撃の理由を岩上氏に聞くと、製品コスト、ソフトウェア環境、サポート体制の3点を指摘。他社エミュレータよりも安く場合によっては時間ライセンスで導入できるコスト面での優位性はユーザーにとって大きなメリットとした上で、競合の追随を許さないソフトウェア環境(コンパイラ技術、トランザクタなど)のパフォーマンスとサポート体制にも自信があると語っていた。

ちなみに、イブのR&D部隊は総勢50人近くで、その大半がソフトウェア環境の開発に従事。殆どのユーザーがイヴが検証IPとして提供しているトランザクタ(USB, PCI Express, AXI/AHB など)を利用しているとの事。また、日本国内のサポートは同分野で業界最多の9名のエンジニアが張り付いているという。

尚、次回のDACではまた新製品を披露する予定。その前に国内で無償の技術セミナーも開催すると聞いた。(3月18日:品川)

尚、次回のDACではまた新製品を披露する予定。その前に国内で無償の技術セミナーも開催すると聞いた。(3月18日:品川)

関連記事:

EVE、2008年売上が前年比30%増を達成‐エミュレーション市場2位に

EVE、大規模デザインを高速にFPGAにマッピング可能な新合成エンジンを発表

※日本イヴ株式会社

2009.01.27

Electronics Design and Solution Fair 2009に出展していたTOOLのブースレポート。

TOOLは、1月13日にリリースしたばかりのレイアウト表示プラットフォーム「LAVIS Ver.8.1」を展示。

新しい「LAVIS」では、デザインチェッカーとしても「LAVIS」を使いたいというユーザーニーズに応え、従来から搭載されている等電位追跡機能を強化。具体的には、ノードの分岐箇所を確認できる「Show Branch」コマンドやGDSデータへのプロービングも可能なビア落ち箇所のチェック機能、ダブルビアのチェック機能、アナログ設計でも利用できる精度の抵抗値計算機能、等電位追跡の結果をグラフィカル的に際立たせる機能などが追加され、「LAVIS」で可能なデザインチェックの幅とユーザビリティが更に広がった。

マーケティングの長谷部氏によると、今回のバージョンアップで追加された各種等電位追跡機能は全て標準機能として「LAVIS」に装備されるもので、ユーザーは無償で利用することが可能。事前に潰せるレイアウトの不具合は、重たいサインオフ検証前に手軽に「LAVIS」でチェックするのが効果的との事だった。

マーケティングの長谷部氏によると、今回のバージョンアップで追加された各種等電位追跡機能は全て標準機能として「LAVIS」に装備されるもので、ユーザーは無償で利用することが可能。事前に潰せるレイアウトの不具合は、重たいサインオフ検証前に手軽に「LAVIS」でチェックするのが効果的との事だった。

また、今回のバージョンアップでは、OASISデータの簡易編集機能も追加。TOOL社長の本垰氏によると、プロセスの微細化に伴いOPC以降の設計工程においてはGDS-IIではもはや限界にきており、世界的に大手半導体ベンダは、GDS-IIからOASISへと移行傾向が加速しているとの事。今回の編集機能追加はOASIS周りのニーズを意識しての対応で、OASISへの変換ツールは色々あるが、ビューワとしてOASISが読み込め更に編集が可能なツールは恐らく世界でも「LAVIS」だけと語っていた。

また、今回のバージョンアップでは、OASISデータの簡易編集機能も追加。TOOL社長の本垰氏によると、プロセスの微細化に伴いOPC以降の設計工程においてはGDS-IIではもはや限界にきており、世界的に大手半導体ベンダは、GDS-IIからOASISへと移行傾向が加速しているとの事。今回の編集機能追加はOASIS周りのニーズを意識しての対応で、OASISへの変換ツールは色々あるが、ビューワとしてOASISが読み込め更に編集が可能なツールは恐らく世界でも「LAVIS」だけと語っていた。

ちなみに、OASIS関連にて同社の「OASIS-Utility」について聞いたところ、同製品は昔から販売しているがここ最近また引き合いが増えているとの事。先日、富士通マイクロエレクトロニクスの採用を発表していたが、既に十数社の納入実績があるという。

関連記事:

TOOLのOASISデータハンドリングツールを富士通マイクロエレクトロニクスが採用

尚、ビジネスはUS市場での「LAVIS」の販売が好調で売上は上々。今後は2月にサンノゼで開催されるリソグラフィ関連の学会「SPIE」に出展、その次は4月にPhotomask Japanに出展、そして7月にDAC出展を予定。DACでは「LAVIS」の等電位追跡機能のパフォーマンスアップとサードパーティツールとの連携強化が報告できるだろうと聞いた。

※TOOL株式会社

2009.01.27

Electronics Design and Solution Fair 2009に出展していたエッチ・ディー・ラボのブースレポート。

エッチ・ディー・ラボは、自社の設計コンサルティング、教育サービスと合わせてEDA事業部の取り扱う米JEDA Technologies社と米Certess社の製品を展示。

JEDAは、アサーション、カバレッジ、ランダムの3つの検証ソリューションを特徴とするツールベンダで、既にOCP(オープンコアプロトコル)については、一通りのソリューションを提供済み。現在はSystemC関連のツール開発を進めており、昨年11月に「SystemC TLM-2.0 Compliance Checker」をリリースした。

JEDAは、アサーション、カバレッジ、ランダムの3つの検証ソリューションを特徴とするツールベンダで、既にOCP(オープンコアプロトコル)については、一通りのソリューションを提供済み。現在はSystemC関連のツール開発を進めており、昨年11月に「SystemC TLM-2.0 Compliance Checker」をリリースした。

エッチ・ディー・ラボでJEDA製品を担当しているAEの若槻氏によると、JEDAはこれまでアサーション・ライブラリは提供していなかったが、ツール(ライブラリ)として提供する方針に変更。既に提供済のOCPチェッカーに続く第二弾として、「SystemC TLM-2.0 Compliance Checker」を開発した。説明によると使い方は簡単で、SystemC記述TOP階層のソケット部分(イニシエータとターゲットの間)に挿入するだけ。ルールはOSCIのマニュアルを基に作られており、この種のツールでは以外と不可能なルールの個別ON/OFFが可能。ルール違反が検出されると、メッセージでOSCIマニュアルの当該ルールを指し示してくれるという気の利いた機能も付いているという。

JEDAはこの「SystemC TLM-2.0 Compliance Checker」の開発にあたりアサーションエンジンを改良。設計者よりも早くEDAベンダがIP開発用途にこのツールに飛びついたという噂もある。

JEDAはこの「SystemC TLM-2.0 Compliance Checker」の開発にあたりアサーションエンジンを改良。設計者よりも早くEDAベンダがIP開発用途にこのツールに飛びついたという噂もある。

今後の予定としては、TLM2.0準拠のテストパターンを自動生成するSystemCランダムテストソリューションが間もなくリリースされるほか、STARCの開発した「TLモデリングガイド第2版」準拠のチェッカーも開発すると聞いた。

※このTLモデリングガイド準拠のチェッカー開発は1月26日にプレス向けに発表されている。

プレスリリース文

関連記事:

関連記事:

JEDAがSystemC TLM-2.0 Compliance Checkerをリリース

STARC、TLモデリングガイド第2版(OSCI TLM2.0対応)をリリース

※JEDA Technologies社

※株式会社エッチ・ディー・ラボ

2009.01.26

Electronics Design and Solution Fair 2009に出展していたSynforaのブースレポート。

Synforaは、1月20日にバージョンアップを発表した動作合成ツール「PICO Extreme」と「PICO Extreme FPGA」を展示。

「PICO Extreme」は、ヒューレットパッカード社研究所での長年の研究技術に基づいたC言語入力の動作合成ツールで、アンタイムドCアルゴリズムから効率の高いRTLを生成する最適化コンパイラと高度な並列化処理、アーキテクチャ・テンプレートを使った構造的設計アプローチ等により、大規模で複雑なアルゴリズムから、品質の高いハードウエアを実現。PICOは、Program In Chip Outの意で、従来の高位合成ツールで多かったブロック分割による合成ではなく、一括合成を特徴とする。

「PICO Extreme」は、ヒューレットパッカード社研究所での長年の研究技術に基づいたC言語入力の動作合成ツールで、アンタイムドCアルゴリズムから効率の高いRTLを生成する最適化コンパイラと高度な並列化処理、アーキテクチャ・テンプレートを使った構造的設計アプローチ等により、大規模で複雑なアルゴリズムから、品質の高いハードウエアを実現。PICOは、Program In Chip Outの意で、従来の高位合成ツールで多かったブロック分割による合成ではなく、一括合成を特徴とする。

「PICO Extreme」の新バージョンではスケジューリングのアルゴリズムが改良されたほか、ループ文の解析と処理に工夫が加えられ、5-20%の面積削減と10-30%のパフォーマンス改善を実現。また、新機能としてスループットのボトルネックを解析する機能や可視化・レポート機能、レポートからのフィードバック機能などが追加された。

Synforaの創設者でもあるCTOのVinod Kathail氏によると、PICOはインド バンガロールのR&D部隊を中心に開発されており、ワールドワイドでは、TIやSTマイクロ、Broadcomなどが主要顧客。日本でも最近導入が進んでおり、同社の2008年売上は前年比2.5倍を達成。日本代理店としてセラスターに加えプロトタイピング・ジャパンとも契約を交わした。

Synforaの創設者でもあるCTOのVinod Kathail氏によると、PICOはインド バンガロールのR&D部隊を中心に開発されており、ワールドワイドでは、TIやSTマイクロ、Broadcomなどが主要顧客。日本でも最近導入が進んでおり、同社の2008年売上は前年比2.5倍を達成。日本代理店としてセラスターに加えプロトタイピング・ジャパンとも契約を交わした。

聞くところによると、「PICO Extreme」のユーザーはその大半がハードウェア設計者。実績としては、高性能ビデオ圧縮アルゴリズム設計において、100万ゲートの回路を一括合成しマニュアル設計と同等のパフォーマンスを実現した例、ビデオアルゴリズム設計にて、1/4の設計リソースで面積は同等、パフォーマンスは30%向上、消費電力を22%削減した例もあるという。(全て対マニュアル設計比)

※Synfora社

※Synfora社

※セラスター株式会社

※プロトタイピング・ジャパン株式会社

2009.01.26

Electronics Design and Solution Fair 2009に出展していたSTARCのブースレポート。

STARCは、STARCAD-CEL、STARCAD-Clouseauといった開発中の次世代設計フローと合わせて、もう一つの活動の柱である標準化活動の成果を展示。

EDSFair開催直前の1月16日に発表した「TLモデリングガイド第2版」は、トランザクションレベルの設計資産の再利用性と相互運用性の向上を目指し、抽象レベル、モデル構造、通信APIの標準化を行ない、その設計手順を示したもので、昨年リリースした初版の内容をOSCI TLM2.0に対応させたもの。

EDSFair開催直前の1月16日に発表した「TLモデリングガイド第2版」は、トランザクションレベルの設計資産の再利用性と相互運用性の向上を目指し、抽象レベル、モデル構造、通信APIの標準化を行ない、その設計手順を示したもので、昨年リリースした初版の内容をOSCI TLM2.0に対応させたもの。

STARC企画部 部長代理の古井氏によると、昨年リリース以降、TLモデリングガイドのダウンロード数は1000件を突破。この数は、STARC幹事会社(大手電機メーカー)以外のユーザーによるダウンロード数という事で、相当な反響があったことが伺える。

「TLモデリングガイド第2版」は、STARCサイトですぐに購入することが可能。価格は¥4620(税込)で送料はSTARCが負担してくれる。

古井氏に聞いたところ、STARCでは本モデリングガイドの普及を目指し、エッチ・ディー・ラボ社の協力を得て今年中にトレーニング講座を開設する予定。また、初版リリース時に多数寄せられた「ソースコードを提供して欲しい」という設計者のリクエストに応え、リファレンスモデル(ソースコード)の提供も計画しているという。

もう一つ、STARCの標準化活動の成果として展示していたのが「IP機能検証ガイド」。

もう一つ、STARCの標準化活動の成果として展示していたのが「IP機能検証ガイド」。

こちらも1月16日にリリースが発表されたばかりのガイドブックで、タイトル通りIPの機能検証基準の標準化を目指すもの。構成としては、機能検証仕様策定編、テストベンチ開発編(開発中)、テストベンチ適用編(開発予定)の3部構成となっており、今回出版されたのは「機能検証仕様策定編」。

興味のある人には、無償で配布されている「クイックガイド」で内容構成を確認することをお勧めするが、すぐに欲しいという人はオンライン購入が可能。価格は¥6300(税込)でこちらもSTARCが送料を負担してくれる。

「IP機能検証ガイド―機能検証仕様策定編」は、IPの設計を依頼する側と請け負う側の共通インタフェースとして、判断基準となる検査項目をまとめたもので、STARC及びSTARCメンバー会社の検証エキスパートが約2年の歳月を費やして作成。実際にPCI ExpressやUSB2.0、AMBAバス、UARTなどの機能検証仕様を作成し実証した結果を元に編集されているとの事で、今まで誰も手をつけなかった膨大な作業をまとめあげた成果は大きい。(ドキュメント量も非常に多い)

今後の予定としては、3月末にテストベンチ開発編を出版予定で、そちらは検証メソドロジVMM/OVMの双方に対応したものになるという。

今後の予定としては、3月末にテストベンチ開発編を出版予定で、そちらは検証メソドロジVMM/OVMの双方に対応したものになるという。

※STARC:株式会社半導体理工学研究センター

2009.01.26

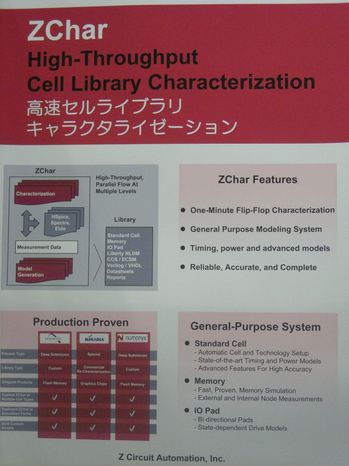

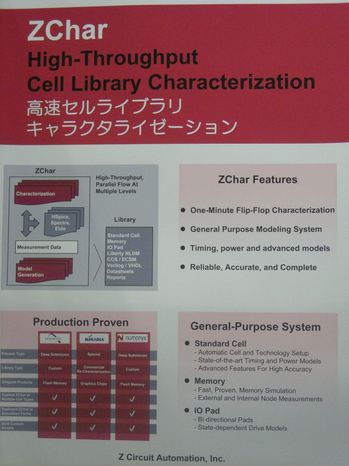

Electronics Design and Solution Fair 2009に出展していたZ Circuitのブースレポート。

Z CircuitはEDSFair初出展の米国ベンチャー。新興ベンダエリアに出展していた。

同社の設立は2000年で北米市場では既に製品の供給実績有り。これまでの実績を受けていざ日本進出という事で、現在某商社と代理店交渉中。

同社の製品はキャラクタライゼーションツール「ZChar」とライブラリ検証・解析ツール「Library Analyzer」の2製品。「ZChar」は、独自のSPICEエンジンを用いる他社ツールとは違い、各社の汎用SPICEを利用可能。SPICEの並列化によって利用効率を上げ高速なキャラクタライゼーションを実現する。SPICE環境を問わない間口の広さと1分以内でフリップフロップ・モデルを生成できるという高速処理がうけているという。

もう一つの「Library Analyzer」は、複雑化するセルライブラリのチェックを行う為のツールで、作成したライブラリのチェック、供給されたライブラリの受け入れチェック、ライブラリの出荷チェックなどのニーズを想定しており、独自ルールによるチェックも可能。ライブラリのバージョン差異などもチェックできる。

もう一つの「Library Analyzer」は、複雑化するセルライブラリのチェックを行う為のツールで、作成したライブラリのチェック、供給されたライブラリの受け入れチェック、ライブラリの出荷チェックなどのニーズを想定しており、独自ルールによるチェックも可能。ライブラリのバージョン差異などもチェックできる。

※Z Circuit社

※Z Circuit社

2009.01.25

Electronics Design and Solution Fair 2009に出展していたシーケンス・デザインのブースレポート。

シーケンスは昨年のDACで発表した新製品「Power Artist」を国内初展示。同製品は、RTLコードを読み込み消費電力を解析し、解析した結果を元にツールに登録されたクロック関連、メモリ関連、データパス関連のルールに応じてデザインの消費電力を最適化する。

ジャパンの石川氏によると、既に日本国内でも「Power Artist」を複数顧客が導入済み。現在は、ユーザビリティの更なる向上、消費電力最適化のための新ルールの追加、最適化処理の自動化に取り組んでおり、DACに向けてバージョンアップを計画中との事。

日本国内では大手が殆ど採用しているRC抽出ツール「Columbus-AMS」の売上比重が大きいが、ワールドワイドでは「PowerTheater」、「Power Artist」といった消費電力解析/最適化ツールが同社売上の中心となっていると聞いた。

日本国内では大手が殆ど採用しているRC抽出ツール「Columbus-AMS」の売上比重が大きいが、ワールドワイドでは「PowerTheater」、「Power Artist」といった消費電力解析/最適化ツールが同社売上の中心となっていると聞いた。

関連記事:

関連記事:

【DACレポート22】Sequence、新製品のRTLパワー最適化ツール「Power Artist」を発表

※シーケンスデザイン株式会社

2009.01.25

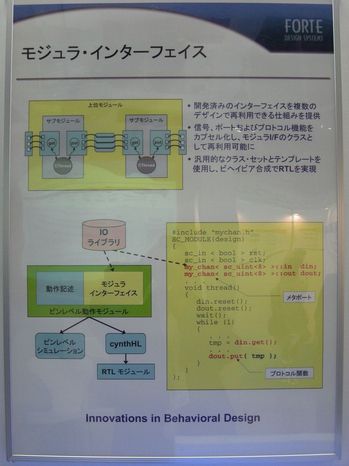

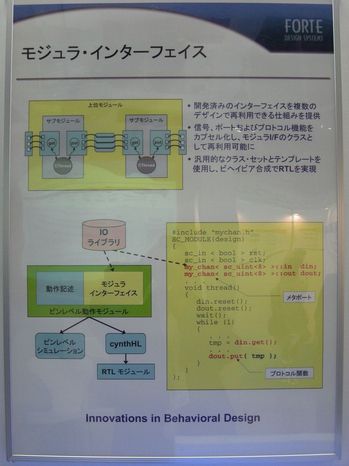

Electronics Design and Solution Fair 2009に出展していたフォルテ・デザイン・システムズのブースレポート。

フォルテはSystemCからの動作合成ツール「Cynthesizer」を展示。「Cynthesizer」は、市販の動作合成ツールとしては最も息の長い製品で、ジャパンの山田社長曰く「中身の合成機能は相当成熟したものになった。」という事で、フォルテは、今後動作合成回りの設計容易化に注力していく計画。

今後のロードマップとしては、DACに向けて新バージョン3.6を開発中。既に顧客による先行評価が進んでいる新バージョンでは、SystemC2.2のサポートやインタフェースIPを自動生成する「インタフェース・ジェネレータ」機能のフルセットサポート、特定アプリケーション向けの合成用IPの装備などを予定しているという。

今後のロードマップとしては、DACに向けて新バージョン3.6を開発中。既に顧客による先行評価が進んでいる新バージョンでは、SystemC2.2のサポートやインタフェースIPを自動生成する「インタフェース・ジェネレータ」機能のフルセットサポート、特定アプリケーション向けの合成用IPの装備などを予定しているという。

シニアAEの桜井氏によると、合成用IPは、画像処理系のデータ・バッファリングなど設計において手間のかかる部分のテンプレート化を計画しており、これらはSystemCの動作IPとして提供される予定。また、「モジュラ・インタフェース」として提供しているインタフェースIPのラインナップも強化される計画で、同IPを使えば複雑なインタフェースを理解しなくても関数を呼ぶだけで設計が可能に。既にこういった「モジュラ・インタフェース」を社内で作っているユーザーもいるらしく、動作合成ユーザーの動向としては、間違いなく動作レベルIPの活用が進むと聞いた。

シニアAEの桜井氏によると、合成用IPは、画像処理系のデータ・バッファリングなど設計において手間のかかる部分のテンプレート化を計画しており、これらはSystemCの動作IPとして提供される予定。また、「モジュラ・インタフェース」として提供しているインタフェースIPのラインナップも強化される計画で、同IPを使えば複雑なインタフェースを理解しなくても関数を呼ぶだけで設計が可能に。既にこういった「モジュラ・インタフェース」を社内で作っているユーザーもいるらしく、動作合成ユーザーの動向としては、間違いなく動作レベルIPの活用が進むと聞いた。

関連記事:

富士通マイクロエレクトロニクス、ASICリファレンスフローにフォルテの動作合成ツール「Cynthesizer」を採用

カリプトとフォルテのSystemCデザインフローが数百万ゲートのSoC設計を成功させる

※フォルテ・デザイン・システムズ株式会社

2009.01.24

Electronics Design and Solution Fair 2009に出展していたシステム・ジェイディーのブースレポート。

システムJDでは昨年に引き続きテストパターン変換ツール「STILAccess」を展示。同製品はテストパターン記述言語「STIL」の構文を解析するライブラリで、STIL関連プログラムの開発を効率化するもの。

システムJDの伊達社長に聞いたところ、国内大手半導体ベンダによる「STILAccess」の採用が決定し、この2月から本格導入の予定。半導体メーカーの内製ツール一部として、メーカー独自のハード的なテスト指標を考慮したSTIL変換を実現するという。

システムJDの伊達社長に聞いたところ、国内大手半導体ベンダによる「STILAccess」の採用が決定し、この2月から本格導入の予定。半導体メーカーの内製ツール一部として、メーカー独自のハード的なテスト指標を考慮したSTIL変換を実現するという。

システムJDは、自社のテスト設計ショリューションを半導体メーカーの要望に応じてカスタム提供しており、今回導入したメーカーに対しては「STILAccess」と合わせて汎用品が存在しない「STIL言語専用エディタ」を開発して納入。このエディタは、今後製品化して販売する計画と聞いた。

システムJDは、自社のテスト設計ショリューションを半導体メーカーの要望に応じてカスタム提供しており、今回導入したメーカーに対しては「STILAccess」と合わせて汎用品が存在しない「STIL言語専用エディタ」を開発して納入。このエディタは、今後製品化して販売する計画と聞いた。

伊達氏によると、ビジネスは順調で、現在は九州大学らと動的再構成デバイスをターゲットとしたテストシステムの開発にも取り組んでいるとの事だった。

※株式会社システム・ジェイディー

2009.01.24

Electronics Design and Solution Fair 2009に出展していた礎デザインオートメーションのブースレポート。

礎DAはCコードの最適化ツール「FP-Fixer」を展示。同製品は、Cコード中の浮動小数点変数を固定小数点変数に自動的に変換するツールで、

2007年にET2007 LSIオブザイヤー優秀賞、東京都ベンチャー技術大賞優秀賞、2008年中小企業優秀新技術・新製品大賞奨励賞を受賞している。

「FP-Fixer」は、Cアルゴリズムをハードウェア化するハードウェア設計者のニーズを主なターゲットとしているが、ここ最近はソフトウェアのパフォーマンス向上を目的としたユーザーが増加中。車載ソフトの最適化などでも利用している顧客がいるとの事。現在、動作合成ツール「Cyber Work Bench」を取り扱う図研が代理店として同製品を販売しているが、Cyberに限らず動作合成ツールとの組み合わせた利用を検討する顧客も多いという。

「FP-Fixer」は、Cアルゴリズムをハードウェア化するハードウェア設計者のニーズを主なターゲットとしているが、ここ最近はソフトウェアのパフォーマンス向上を目的としたユーザーが増加中。車載ソフトの最適化などでも利用している顧客がいるとの事。現在、動作合成ツール「Cyber Work Bench」を取り扱う図研が代理店として同製品を販売しているが、Cyberに限らず動作合成ツールとの組み合わせた利用を検討する顧客も多いという。

2月末を目処にリリース予定の次期バージョンでは、ツールのパフォーマンスアップが図られると同時に、細かな新機能も実装される予定と聞いた。

尚、礎DAではツール販売の他にSystemCモデル開発やSystemC言語トレーニングもサービスとして提供中。2月からは、SystemC TLM2.0の新セミナーも定期開催するという。

関連記事:

富士通九州ネットワークテクノロジーズが礎DAの浮動小数点自動変換ツールを採用

※株式会社礎デザインオートメーション

※株式会社礎デザインオートメーション

2009.01.24

2009年1月22日、メンター・グラフィックスは、ESLツールを手掛ける米Agility Design SolutionからC言語設計スイートを買収した事を発表した。

プレスリリース文

発表によるとメンターが今回Agilityから買収したのは、旧Celoxca製品といった方が日本では馴染みのあるHendel-Cベースの動作合成ツール「DK Design Suite」、画像/ビデオ処理向けIP「PixelStreams」、FPGA評価ボード「RCシリーズ」の3製品からなるC言語設計環境で、その取引額は未公表。メンターは、これら製品をAgilityの既存顧客へ継続販売すると同時に、自社の動作合成ツール「Catapult C Synthessis」へのアップグレードのパスも用意する。

Agilityは財務状況の悪化により事業継続が困難となり、昨年Celoxica社から買収したCeloxca社のESL事業をメンターに売却。旧Catalytic社製品であるMATLAB高速化ソリューション他、Agilityの残りの資産は、1月28日に最低入札額275000ドルで競売にかけられる予定となっている。

メンターは、1月21日にSystemCフロントエンド環境「Vista」と動作合成「Catapult C Synthesis」を組み合わせた新しいTLM-2.0設計フロー「Scalable Design Methodology」を発表したばかりだが、Agilityのソリューションを手に入れた事でESL分野における同社の製品ポートフォリオは更に拡張される。

関連記事:

米Catalytic、英CeloxicaのESL事業を300万ドル(約3.3億円)で買収(2008年1月7日)

【EDSFレポート】CeloxicaとCatalyticが合併して新会社Agilityとしてスタート(2008年1月24日)

コーウェア・ジャパンが米Agility社の「MATLAB-to-C製品」の取り扱いを開始(2008年5月14)

※Agility Design Solution社

※メンター・グラフィックス・ジャパン株式会社