NEWS

2010.03.19

2010年3月18日、メンター・グラフィックスは、PCB設計ソリューションのValor Computerized Systemsの買収完了を発表した。

プレスリリース文

メンターは、バロール社にメンター株約560万株と現金3250万ドルを支払ったとしており、今回の買収は金額にして計約5000万ドル。

バロール社は、プリント基板開発・製造向けのソリューションとして、レイアウトツール、DFMツール、生産管理ツールなどを提供しており、これらソリューションがメンターに加わることにより、「PADS」、「Board Station」をはじめとするメンターのPCBソリューションはより強力なものとなる。

バロール社はイスラエルに本社を置き、フランクフルト証券取引所に上場、世界各地に拠点を持つグローバル企業。昨年10月に買収計画が発表された段階では、買収総額約8200万ドルとされていた。

※メンター・グラフィックス・ジャパン株式会社

※Valor Computerized Systems社

2010.03.18

2010年3月8日、システムレベルからのパワー/熱解析ソリューションを手掛ける、仏DOCEA Powerは、ワイヤレス半導体大手のSTエリクソンが同社製品「ACEplorer」を採用した事を発表した。

プレスリリース文

DOCEAの発表によると、STエリクソンは複雑な次世代3Gマルチメディア・プラットフォームのパワーおよびサーマル・ビヘイビアのモデル化に向けて「ACEplorer」を採用。パワーの見積りおよび管理において、表計算ソフトベースの従来手法から「ACEplorer」を用いた新手法へ乗り換えた。

「ACEplorer」はシステムレベルでパワー仕様をモデル化しパワーの見積もりを行う事が可能。パワーモデルを管理しながら下流のインプリメントに応用する役目も果たす。消費電力と熱解析のほかに、IRドロップや熱暴走といった問題にも対処できる。

Web上の情報を見る限り、同社の日本販売チャネルは存在していない。

※DOCEA Power社

2010.03.17

2010年3月15日、カスタム設計環境とHDLデバッグ環境を手掛けるSpringSoftは、アナログ/ミックスド・シグナル設計向けの2つの新製品を発表した。

プレスリリース文

SpringSoftが発表した新製品は、自動配置ツール「Laker Custom Row Placer」と自動配線ツール「Laker Custom Digital Router」の2製品。いずれも同社のカスタムIC設計環境「Laker」上でダイレクトに稼動するツールで、「Laker」上でデジタル・ブロックの配置・配線を実現するもの。

カスタム・デジタルブロックを含むカスタムIC設計では、これまではデジタル部分が少なかったこともあり、デジタル・ブロックの配置、配線は人手作業で進められる事が殆どだったが、デジタル部分が増えるにつれ自動化のニーズが高まっていた。自動化自体は、市販のデジタル配置配線ツールを利用すれば実現できるが、設計データをエクスポートする必要があり、ユーザーにとっては単一環境で全ての作業が完結できた方が当然嬉しい。

「Laker Custom Row Placer」は、2倍の高さのセルを含むスタンダード・セル、カスタム・セルの自動配置を可能としており、スタッキングやシェアリング、行分離や重複削除などの機能もあるほか、「Laker」と統合された包括的な編集機能を提供。もう一つの自動配線ツール「Laker Custom Digital Router」がそのまま使用できるデータを出力できる。

「Laker Custom Digital Router」は、グリッドベースおよびシェイプベース双方の配線が可能なハイブリッド・ラウターで、その対象を50K以下のセルに限定。OpenAccessデータベースにも対応しており、LEF/DEFのインポート/エクスポートが可能なほか、ポスト配線DRC機能、ビア/ダブルビア挿入、CMPなどDFM機能も装備されている。最初のリリースでは40nmルールをサポートし、将来的には28nmルールもサポートする予定だという。

「Laker Custom Digital Router」は、グリッドベースおよびシェイプベース双方の配線が可能なハイブリッド・ラウターで、その対象を50K以下のセルに限定。OpenAccessデータベースにも対応しており、LEF/DEFのインポート/エクスポートが可能なほか、ポスト配線DRC機能、ビア/ダブルビア挿入、CMPなどDFM機能も装備されている。最初のリリースでは40nmルールをサポートし、将来的には28nmルールもサポートする予定だという。

SpringSoftによると、カスタムIC設計環境における「Laker」の世界的なシェアは15%程度。アジア圏でのユーザー数が順調に伸びており、日本市場を含めアジアを核としたシェアの拡大に期待を寄せている。

SpringSoftによると、カスタムIC設計環境における「Laker」の世界的なシェアは15%程度。アジア圏でのユーザー数が順調に伸びており、日本市場を含めアジアを核としたシェアの拡大に期待を寄せている。

尚、「Laker Custom Row Placer」および「Laker Custom Digital Router」の正式リリースは2010年Q2の予定。ライセンスは3年間TBLで「Laker Custom Row Placer」は1年あたり35000ドル、「Laker Custom Digital Router」は1年あたり65000ドルとなっている。

※株式会社スプリングソフト

2010.03.11

2010年3月10日、メンター・グラフィックスは、同社の提供する検証ライブラリ「MVC」が先頃発表されたARM AMBA 4仕様をサポートした事を発表した。

プレスリリース文

メンターのMVC(Multi-view Verification Components)は、検証メソドロジOVM準拠の検証コンポーネント・ライブラリで、検証IPとして検証環境の構築に用いられる。同ライブラリは、システムレベル、TLMレベル、RTLレベルの各検証に対応した単一の検証IPで、これを利用すればテストベンチの作成工数を削減可能。同社のシミュレーター「Questa」を用いた検証環境を短期間で構築でき、各設計抽象度において一貫したカバレッジの高い機能検証を実現できる。

今回のMVCによるAMBA 4仕様サポートにより、設計者はAXI4、AXI4-Lite、AXI4-Stream用の検証IPが利用可能となり、これらインタコネクト・プロトコルを用いたデザインの機能検証を迅速に実施できるようになる。

ARMのAMBA 4仕様は今月3/8に仕様が発表されたばかりのAMBA 3の拡張インタコネクト・プロトコル仕様で、FPGA実装向けの拡張が主な拡張として挙げられている。

※メンター・グラフィックス・ジャパン株式会社

※アーム株式会社

2010.03.11

2010年3月10日、マグマは、静的タイミング解析とモンテカルロ・シミュレーションの新製品2製品を発表した。

プレスリリース文(STA)

プレスリリース文(Monte Carlo)

発表されたSTA(静的タイミング解析ツール)は「Tekton」という製品名で、既存のSTAよりも高速、高精度、大容量をうたい、シングルCPUで高速なマルチシナリオ解析が実現できるとしている。また、マルチスレッド機能によって最大24台のCPUでリニアに近いスケーリングも可能。同社の寄生抽出ツール「Quick Cap」の次世代版「QCP」との組み合わせによって、高速・高精度なタイミング解析を実現しているという。

もう一つの新製品「FineSim Fast Monte Carlo」は、独自の統計技術と「dynamic error-controlled algorithms」により、従来のモンテカルロ・シミュレーションよりも高速・高精度な統計解析が可能。マグマの並列技術を用いることで最大100倍の高速処理を実現出来るという。

尚、「FineSim Fast Monte Carlo」は既にリリースされており、同社の回路シミュレーター「FineSim SPICE」、「FineSim Pro」と合わせて利用可能。「Tekton」は今年6月に正式リリースされる予定となっている。

※マグマ・デザイン・オートメーション株式会社

2010.03.10

2010年3月8日、ESLソリューションを手掛ける米Carbon Design Systems社は、ARMのGPU「Mali」の仮想モデルを発表した。

プレスリリース文

今回カーボンがリリースしたのは、ARMの提供する「Mali-200」および「Mali-400MP」、2種類のGPUの仮想モデル。これらモデルは、ARMのRTLコードからコンパイルされており100%の精度を保証。インタフェースはSystemC TLM 2.0仕様に準拠しており、TLM LT(loosely timed)レベルならびにCAレベル(Cycle Accurate)の仮想シミュレーションに活用できるという。

※カーボン・デザインシステムズ・ジャパン株式会社

2010.03.10

2010年3月9日、ベルギーの研究機関IMECとシノプシスは、シリコン貫通ビア技術の開発における両社のコラボレーションを発表した。

プレスリリース文

発表によるとIMECは、3次元積層ICを実現するコア技術「TSV:シリコン貫通ビア」のモデル化にシノプシスのTCADを活用。シリコン貫通ビアの信頼性と性能向上に役立てるという。

「3D TSV」などと呼ばれる半導体の積層技術は、チップ・パッケージの小型化、信号経路の違いによる性能向上、消費電力の削減などのメリットが期待されており、それを実現するTSV(シリコン貫通ビア)の研究開発は各方面で活発に進められている。

チップの積層手段としては、ダイ間をワイヤー・ボンディングで接続するMCP(マルチ・チップ・パッケージ)という手法もあるが、ワイヤーを不要とするTSVの方がチップの積層効果が高いとされている。

シノプシスは、TCAD技術を有する企業を過去2社買収しており、現在「Sentaurus」というファミリ名でTCAD製品を展開している。TCAD分野ではシノプシスとシルバコが2大勢力となっている。

※日本シノプシス合同会社

※IMEC

2010.03.10

2010年3月8日、システムレベル記述言語「SystemC」の標準化団体であるOSCI(Open SystemC Initiative)は、アナログ/ミックスシグナル設計向けのSystemC AMS1.0のリリースを発表した。

プレスリリース文

AMS1.0は、アナログ/ミックスシグナル設計向けの標準言語としてSystemCを拡張して設計されたもので、システムレベルでのアナログ/ミックスシグナル設計を実現すべく、新たなクラスライブラリが用意されている。

リリースされたSystemC AMS1.0は、OSCIホームページからダウンロード可能。

SystemC AMS1.0は、Verilog-AMSとMatlab/Simulinkにまたがる抽象領域をカバーするとされている。

※OSCI

2010.03.09

2010年3月2日、米SynTest Technologies社の日本支社シンテスト・ジャパンは、同社の故障シミュレータ「TurboFault」がSTIL形式のテストデータをサポートした事を発表した。

シンテスト・ジャパンによると、今回、東芝マイクロエレクトロニクス(株)が販売しているSTIL対応の設計・テスト環境構築ツール「STILDirector」の一部機能を用いる事で「TurboFault」のSTILサポートを実現。

具体的には、「STILDirector」を「TurboFault」のSTILリーダーとして使用することにより、論理シミュレータ、LSIテスタ等で使用するテストデータをそのまま「TurboFault」で読み込む事が可能に。「STILDirector」と「TurboFault」の組み合わせ利用によって、あらゆるディジタル回路のSTILデータを効率良く故障シミュレーション可能となる。

※シンテスト・ジャパン

※東芝マイクロエレクトロニクス株式会社

2010.03.08

2010年3月5日、SystemC言語からの高位合成ツールを手がける米Forte Design Systems社は、たデータパス合成ツール「CellMath Designer」および演算器IP「CellMath IP」の最新版のリリースを発表した。

プレスリリース文

「CellMath Designer」および「CellMath IP」は、データパス集約型のデザインブロックにおけるパフォーマンス向上、面積削減、消費電力削減を狙うもので、フォルテが昨年9月に買収を発表したAlithmatica社が開発した製品。

買収後数カ月の速さで実現された今回のバージョンアップでは、「CellMath Designer」の更なる自動化、合成するRTLコードの最適化、マルチプレクサ合成機能の拡張などが実施されたという。

「CellMath Designer」は既に国内にもユーザーが存在しており、昨年11に開催されたフォルテのユーザー交流会では、株式会社デジタルメディアプロフェッショナルの大渕氏がユーザーとして事例を講演。同社のグラフィックIP開発にて浮動小数点演算器生成ツールとして「CellMath Designer」および「CellMath IP」を採用したところ、コア面積の削減に成功。SystemCモデルとの合わせ込みも不要となり、検証が楽になったという。

「CellMath Designer」の米国販売価格は年12万ドルから。

※関連ニュース

高位合成ツール米フォルテがデータパス合成ツールの米Arithmaticaを買収

※フォルテ・デザイン・システムズ社

2010.03.08

2010年3月4日、メンター・グラフィックスは、2010会計年度第4四半期(2009年11月-2010年1月)の売上を報告した。

プレスリリース文

発表によると、メンターの09年11月-10年1月の売上は、前年比約2%減の2億3710万ドル。例年通りQ4に当たる今四半期は年間を通じて最高の売上額を叩き出し、上位10件の契約更新額の平均は25%増を達成したが、Q1から続いていた売上前年比増は一休止となった。

メンターの2010会計年度(09年2月-10年1月)の売上合計は8億270万ドルで前年比2%増。この数字は、ケイデンスの2010会計年度(09年10-12月)売上合計8億5100万ドルに次ぐ業界第三位。メンターは、2011会計年度は更なる業績向上を見越しており、売上で5%増を予測している。

※メンター・グラフィックス・ジャパン株式会社

※メンター・グラフィックス・ジャパン株式会社

2010.03.04

2010年3月3日、フォーマル検証を中心とした検証ソリューションを手掛ける、米Real Intent社は、同社のCDC検証ツール「Meridian CDC」の最新バージョン 3.0を発表した。

プレスリリース文

リアルインテントによると、今回発表された「Meridian CDC 3.0」では、リセット関連をはじめ新たなチェック・カテゴリが用意され、より広範囲な解析が可能となったほか、検証環境の自動セットアップ機能やデバッグ機能、デザイン制約生成機能などがエンハンスされた。

※Real Intent社

2010.03.04

2010年3月1日、ESLツール大手のコーウェアは、同社の仮想環境「Platform Architect」および「Virtual Platform」向けの新たなシステム解析ツールを発表した。

プレスリリース文

http://www.coware.co.jp/news/2010/2010.3.1.html

コーウェアによると、新たなシステム解析ツールはオープンソースIDE「Eclipse」をベースとしたもので、仮想環境上で実行したソフトウェア及びハードウェアの挙動を解析し、その結果を強力な表示機能によってグラフィカルに示す。

・ソフトウェアの解析

-マルチコア上で動作するソフトウェアの状態と履歴

-各プロセスなどの結果

-ハードウェア・プラットフォームとのやり取り

-キャッシュの状態

-ファンクションのトレースおよびカバレッジ

-OSを認識した解析

-その他

・ハードウェアの解析

-プロトコルを認識したトランザクション・レベルのトレース

-インタコネクトの構造全体および内部バス解析 (カウント、待ち時間、スループット)

-バスおよびメモリ・リソースの利用率および競合解析

-アプリケーション・タスク・グラフ・リソースの利用率および競合解析

-その他

尚、今回発表したシステム解析ツールは、ユーザーがカスタマイズ可能なフレームワークが用意されており、ニーズに応じて機能を追加する事が出来るという。

・フレームワークの主な構成要素:

-SystemC標準言語に準拠したモデルに実装するためのオープンAPI

-ソースコードを変更することなく実行時にデータを収集するモニタの自動挿入

-静的解析を効率的に保存するための実行時データ削減

-TLMのトレース結果および解析結果の高速かつ応答性の高い表示を可能にする階層型データベース

-トレース結果および解析結果を複数のレベルで表示可能なグラフィカル・チャート・ビュー

-ユーザが制御可能な情報や結果のフィルタリングと表示

-シミュレーションの制御やカスタム解析ビューを作成するために便利なTclスクリプト用API

新たなシステム解析ツールは、既にリリースされているCoWare Platform Architect、CoWare Virtual Platformの新バージョン2010.1で利用できる。

※コーウェア株式会社

2010.03.02

2010年3月1日、カスタム設計環境とHDLデバッグ環境を手掛けるSpringSoftは、同社の検証環境品質測定ツール「Certitude」を国内ファブレス半導体ベンダのメガチップスが採用した事を発表した。

プレスリリース文

メガチップス社、取締役執行役員 第1LSI事業部長、古都 哲生氏のコメント:

「Certitudeはわずか1時間で、コード・カバレッジ製品では検出できなかった検証環境の問題を特定しました。使いやすく、簡単に当社の既存フローに統合することができるため、今後もCertitudeを使用し、さらなる検証効率の向上を図って行きたいと考えています。」

「Certitude」は、SpringSoftが2009年に買収したCertess社の開発した製品で、デザインを直接検証する訳ではなく、「Functional qualification」という手法を用いて、検証環境の品質・信頼性そのものを客観的に評価する。元々はCertess社が検証コンサルティングを行う過程で内製した製品で、既に東芝やSTマイクロ、Juniper Networksなど大手の採用が報じられている。

※スプリングソフト株式会社

2010.03.02

2010年2月25日、マグマは2010会計年度第3四半期(2009年11月-2010年1月)の売上を報告した。

プレスリリース文

発表によるとマグマの2009年11月-2010年1月売上は、3ヶ月前の予測を上回る前年同時期比約1%増の3100万ドル。前四半期は黒字を達成していたが、再び260万ドルの損益を計上した。※GAAP基準による会計結果

マグマのCEO兼チェアマンRajeev Madhavan氏のコメントによると、予測を上回る売上結果には満足している様子。フィジカル検証ツール、回路シミュレーター、アナログ/ミックスドシグナル設計ツールなどが好調だという。

マグマは次期2010年Q4(2010年2月-4月)の売上を3250-3300万ドルと予測している。

マグマは次期2010年Q4(2010年2月-4月)の売上を3250-3300万ドルと予測している。

※マグマ・デザイン・オートメーション株式会社

2010.02.26

---PR---

■ベリフィケーションテクノロジーより、プライベートセミナー開催のお知らせ

お客様各位

平素は、格別のお引き立てを賜り、厚く御礼申し上げます。

ベリフィケーションテクノロジーでは、かねてよりUSB3.0へのアプローチを 進めておりました。

この度、東京コンファレンスセンターで開催されるプライベートセミナーにて、 USB3.0開発支援製品「VITIS」、アーキテクチャ検討ツール「VisualSim」、弊社が提唱する「仕様書へのアサーション導入」をご紹介させて頂きます。

ご多忙の折とは存じますが、皆様のご来場を心よりお待ちしております。

--------------------------------------------------------------------------

記

【開催概要】

会 場 : 東京コンファレンスセンター品川 4F-406

http://www.tokyo-cc.co.jp/access.html

開催日 : 2010年3月12日(金)

時 間 : 14:00?17:30 (13:30受付開始)

定 員 : 100名

参加料 : 無料

(当日はご名刺を2枚ご準備頂きます様、お願い申し上げます。)

【セミナー概要】 展示ブース解説

○テーマ : 検証を成功に導く3つの「V」 ?USB3.0へのアプローチ?

◆ ご挨拶 14:00

ベリフィケーションテクノロジー株式会社

代表取締役 竹内 秀人

◆「Mirabilis社 VisualSim のご紹介」 14:10-15:00

高速シリアルI/Fにおいて、現在最も注目されていますUSB3.0導入時、

現状のシステム構成、CPUやBUS、メモリのスペックがどの程度変更する

必要があるかを検証し、性能やパワーバランスのとれた最適なシステム

仕様をVisualSimを使用して短期間で決定する例を紹介致します。

実際にUSBを含んだシステムの簡易モデルを使用しデモをご覧頂きます。

◆「USB3.0/2.0プロトコル層ソフトウェアの研究成果報告

?"低消費電力化/高速化/コストダウン"の実現?」

15:15-16:05

USB3.0/2.0プロトコル層ソフトウェアの研究成果を、実際の計測データを

用いて報告します。

・USB3.0プロトコル紹介/高速化のコツ/実機エミュレーション技術

/低消費電力化評価方法

・安価、高速、低消費電力なUSB2.0プロトコルからGigaEther

プロトコルへの変換

・関連製品URL:http://www.vtech-inc.co.jp/product/vitis-em.html

・「平成21年度 戦略的基盤技術高度化支援事業」経済産業省採択

研究テーマ

◆「仕様書へのアサーション導入」 16:20-17:00

システム開発の現場において従来から「仕様書は重要である」と認識がある

にも関わらず、未だに上流工程での不具合・不整合の混入が改善されていな

いのが現状です。Vtechでは、長年の第三者検証のノウハウをもとに、今必要

とされる仕様書についてご提案致します。これはSystemVerilogアサーション

を導入した仕様書の提案であり、プロジェクト高品質化に直結し、最終的な

TAT短縮への効果を示す有効な手段と考えます。

----------------------------------------------------------------------------

下記サイトより申し込み頂けます。

http://www.vtech-inc.co.jp/seminar.html

また必要事項をご記入の上、sales@vtech-inc.co.jp にご返信頂いて結構です。

・会社名:

・氏 名:

・部 署:

・住 所:

・TEL:

・FAX:

・E-mail:

--------------------------------------------------------------------------

*********プライバシーポリシーについて***********************

ベリフィケーションテクノロジーでは、お客様の個人情報を弊社の

プライバシーポリシーに基づいて取り扱いさせていただいております。

個人情報につきましては第三者への譲渡は一切ございません。

http://www.vtech-inc.co.jp/privacy.html

―――――――――――――――――――――――――――――――――――

【セミナーに関するお問合わせ先】

TEL:045-470-8310 FAX:045-470-8319

担当:土屋 m_tsuchiya@vtech-inc.co.jp

池田 m_ikeda@vtech-inc.co.jp

―――――――――――――――――――――――――――――――――――

―――――――――――――――――――――――――――――――――――

ベリフィケーションテクノロジー株式会社(Vtech)

営業部 土屋 政勝 080-5178-8311

E-mail:m_tsuchiya@vtech-inc.co.jp Web:http://www.vtech-inc.co.jp

(本社)

〒222-0033 横浜市港北区新横浜2-3-8 KDX新横浜ビル4F

TEL:045-470-8310 FAX:045-470-8319

(関西検証センター)

〒542-0082 大阪市中央区島之内1-17-12長堀橋第25松屋ビル7F

TEL:06-6120-6662 FAX:06-6120-6663

(福岡検証センター)

〒814-0001 福岡市早良区百道浜3-8-33 福岡システムLSI総合開発センター703

TEL:092-985-1369 FAX:092-980-1031

――――――――――――――――――――――――――――――――――――

2010.02.26

2010年2月23日、I/Oレイヤ生成、レジスタ管理などチップ・インテグレーションに関するソリューションを展開しているアイルランドの新興ベンダDuolog Technologiesは、同社のシステム設計ツール「Socrates」によるOVM検証環境の自動生成機能を発表した。

※OVM:Open Verification Methodology

プレスリリース文

発表によるとDuologは、複雑なSoC,ASIC,FPGAのチップ・インテグレーション・プラットフォームとして売り出している同社の「Socrates」に、新たに検証メソドロジOVMベースの検証環境を自動生成する機能を搭載。同機能は、メンターの提供する「OVM register package」バージョン1.0を用いたOVM検証環境を自動生成するもので、これを利用することでユーザーは検証環境の構築ではなく検証そのものに集中できる。

Duologは、昨年競合のBeach Solutionsを買収して以降、製品のラインナップを変更し、現在は「Socrates」という製品名の下で、I/Oファブリック生成(Spinner)、制御レジスタ管理(Bitwise)、チップ・アセンブリ(Weaver)と3種類の異なる製品を展開しているが、XML IP-XACTファイルをインタフェースとしてツールに情報を取り込み、何かを自動生成するという部分は、今回のOVM検証環境の自動生成機能も含めて共通しているようだ。

今回発表したOVM検証環境の自動生成機能に関する詳細は、現在サンノゼで開催中のDVCon2010にて発表されるという。

※Duolog Technologies

※イノテック株式会社(Duolog製品代理店)

2010.02.25

2010年2月22日、市場調査会社の米Global Industry Analystsは、EDA市場の成長を予測するレポートを発表した。

プレスリリース文

発表によるとGIA社は、2015年までにEDAの市場規模が98億5000万ドルに達すると予測。市場が成長する要因として、ブロードバンドおよび無線通信分野の成長、モバイル端末および携帯電話分野の成長、通信キャリアのインフラ整備や自動車分野の更なる半導体使用などを挙げ、現在市場をリードしている米国ではなく、発展途上にある国がEDA市場成長の原動力になると予測している。

既に大手3社をはじめ、様々なEDAベンダが北米、欧州、日本に次ぐ新たな市場開拓に乗り出しているが、世界EDA市場はこの10年間その市場規模に大きな変化は無く、概ね5000億円前後を維持している。市場によほどの変化が起こらぬ限り、この先5年間で市場規模が倍になるような急成長は難しいというのが一般的な見方だろう。

※Global Industry Analysts

2010.02.25

2010年2月21日、フォーマル検証ツールを手掛ける米Jasper Design Automation社は、LPDDR1、LPDDR2およびDDR3 SDRAM向けのフォーマル検証用「Proof kit」のリリースを発表した。

プレスリリース文

JasperがリリースしたProof kitは、JEDECの標準規格に則ったインタフェエース・プロトコルを検証するためのプロパティ・セットで、SystemVerilogで記述されたプロパティとJasperGoldで利用可能な検証プランが含まれている。

これらキットは、低電力ニーズによって需要が拡大しているLPDDRのユーザーをターゲットとしたもので、Jasperでは今後も同種のキットを増やしていく計画だという。

尚、LPDDR1、LPDDR2およびDDR3 SDRAMの各「Proof kit」は、「Jasper Formal Testplanner」の一部として提供されるもので、「Jasper Formal Testplanner」のユーザーは追加費用を負担することなく同キットを利用できる。

※Jasper Design Automation社

2010.02.25

2010年2月10日、フォーマル検証ツールを手掛ける米Averant社は、同社のフォーマル検証ツール「Solidify」のバージョンアップを発表した。

プレスリリース文

発表によると「Solidify」の最新バージョン5.2は、新たに単一マシンによるマルチコア処理をサポートし、8コア搭載の最新のワークステーションで7倍近い処理の高速化を実現。また、プロパティ記述もテストベンチも必要としない「自動チェック」機能と前バージョン5.1で追加された新機能「SEC(sequential equivalency checking)」がエンハンスされ、それぞれ処理速度、キャパシティ、堅牢性が改善された。

※Averant社

2010.02.25

2010年2月22日、フォーマル検証ツールを手掛ける独OneSpin Solutionsは、同社のアサーションベース検証ツール「360 MV」とPlatform Computing社の分散処理ソリューションの統合を発表した。

プレスリリース文

発表によるとワンスピンは、分散コンピューティング管理ソフトの大手Platform Computing社のハイパフォーマンス・コンピューティング環境向けワークロード管理ソリューション「LSFインフラストラクチャ」と自社のフォーマル検証ツール「360 MV」を統合し、複数マシンを用いたアサーションベース検証の分散処理を実現。

この改良された「360 MV」ソリューションを利用する事で、ユーザーは検証ニーズに応じて任意のクラスタ・サイズにスケーラブルに対応する事が可能。検証ジョブのスケジューリングをマシン・リソースに合わせて調整することができるほか、「LSF」のモニタリングツールを用いてプロパティ・タスクを追跡し、その進捗を「360 MV」のGUIにレポート出力することが可能だという。

※OneSpin Solutions社

2010.02.24

2010年2月22日、カスタム設計環境とHDLデバッグ環境を手掛けるSpringSoftは、同社のカスタム設計環境「Laker」のバージョンアップを発表した。

プレスリリース文

発表によると「Laker」の最新バージョンは、OpenAccessデータベースをサポート。これにより、OpenAccessデータベースをサポートする他社ツールとのインターオペラビリティが高まり、設計データを変換することなく他のツール環境に移管する事が可能に。他社ツールとの連携も容易となる。

「Laker」は、TSMC社のインターオペラブル・プロセス・デザインキット(iPDK)をはじめ、あらゆるインターフェイス、ライブラリ、デザインキットをサポートしている。

※SpringSoft社

2010.02.23

2010年2月18日、第20回米EDN誌「INNOVATION AWARDS」のファイナリストが発表された。

発表内容

「EDN Innovation Awards」は、エレクトロニクス業界における優れた製品および技術を表彰するもの。毎年2月にEDN誌の記者によって選出されたファイナリストが発表され、その後3月にEDN読者のオンライン投票結果によって受賞者が決定される。

今年は全32部門、計133の製品・技術がノミネートされており、EDA関連部門としては、下記3部門計13品がファイナリストにノミネートされた。

■EDA: Back-End Tools

・Encounter Digital Implementation System, Cadence Design Systems

・In-design DFM with Encounter Digital Implementation System, Cadence Design Systems

・Quartus II Version 9.1 FPGA-design tool, Altera

・Totem-SE full-chip power and substrate noise-analysis solution, Apache Design Solutions

■EDA: Front-End Analysis and Synthesis Tools

・ActiveDesign formal design system, Jasper Design Automation

・IC Validator in-design physical-verification solution, Synopsys

・PowerPro MG memory-power optimizer, Calypto Design Systems

・RealTime Designer RTL synthesis tool, Oasys Design Systems

・RootCause analyzer formal diagnosis tool, OneSpin Solutions

■EDA: Front-End Simulation and Database Tools

・BOM Manager Version 4 bill-of-materials-management tool, SiliconExpert Technologies

・MVSIM voltage-aware cosimulator, Synopsys

・Virtuoso Accelerated Parallel Simulator, Cadence Design Systems

・ZeBu-Server emulation system, EVE

尚、EDA部門以外でもシノプシスの開発チームとメンターの製品が下記部門でノミネートされている。

■Innovator of the Year

・Synopsys DesignWare SuperSpeed USB 3.0 IP engineering team

■Design, debug, and production test, yield analysis

・Tessent YieldInsight yield-analysis tool, Mentor Graphics

EDN読者によるオンライン投票は3月19日まで行われ、アワード受賞者は4月26日に発表される予定。

※米EDN誌

2010.02.23

2010年2月22日、システムレベル記述言語「SystemC」の標準化団体であるOSCI(Open SystemC Initiative)は、「CCI:Configuration, Control & Inspection」の構成要件のパブリック・レビュー開始をアナウンスした。

プレスリリース文

「CCI」は、SystemCモデルのインターオペラビリティ(相互運用性)向上を目的に標準化が計画されているEDAツール向けの標準API仕様で、2008年からOSCI内にCCI-WGが組織され、標準化に向けた活動が進められている。

今回発表されたのは、「CCI」の構成要件仕様と呼べる「configuration requirements specification」のパブリック・レビューで、期間は4月2日まで。ドキュメントはOSCIのWebサイトからダウンロードできる。

SystemCはESL用途に普及が進んでいるものの、利用するツールによりモデルの作成仕様が異なる場合があり、作成したモデル資産の再利用やツール・チェーンの構築といった観点から、モデルとツール間のインターオペラビリティの向上が望まれている。

※OSCI公式ページ

2010.02.23

2010年2月17日、シノプシスは、2010会計年度第1四半期(09年11月-10年1月)の売上を報告した。

プレスリリース文

発表によると、シノプシスの2010会計年度Q1の売上は、前年同時期より約2.8%減の3億3020万ドル。売上としては前四半期に続き前年割れとなったが、収支は1億3280万ドルの黒字でこの数字は前年同時期の約2.5倍にあたる。

シノプシスは、次期2010年Q2(10年2月-4月)の売上額を3億3100-3900万ドルと予測している。

※日本シノプシス合同会社

※日本シノプシス合同会社

2010.02.17

2010年2月16日、メンター・グラフィックスは、フリースケールから「Virtual Garage」製品ラインを買収したと発表した。

プレスリリース文

「Virtual Garage」は、車載電子システム開発向けのツールスイートで、車載電子システムのパフォーマンス要件を検討する「V-Architect」と、CANネットワークシステム設計向けの「CANDIFF」、大きく2種類の製品がある。

メンターによると今回買収した「Virtual Garage」の技術は、同社が既に保有している車載電子システムおよびハーネス設計環境「CHS」と補完関係にあるという。

メンターは、昨年4月に新製品としてAUTOSARベースの車載システム設計環境「Volcano™ Vehicle Systems Architect」を発表するなど、ここ最近、自動車分野に向けたソリューションにも注力している様子が伺える。

※関連ニュース:

メンター、自動車向けの新製品としてAUTOSAR統合設計環境「VSA」を発表

※メンター・グラフィックス・ジャパン株式会社

2010.02.16

2010年2月10日、シノプシスは、ヤマハが同社の最新グラフィックスチップの設計に「Design Compiler Graphical」のRTL論理合成ソリューションを採用したことを発表した。

プレスリリース文

発表によるとヤマハは、これまで論理合成の段階で配線密集度を予測することができず、論理設計-フィジカル設計間の設計のやり直し発生に苦慮していたが、今回、シノプシスの「Design Compiler Graphical」を採用し、同ツールの配線密集最適化テクノロジを活用することで、最新の画像処理SoCの厳しいタイミング目標を達成。設計期間も大幅に短縮することに成功した。

ヤマハは、こうした成果を踏まえ、シノプシスをEDAツールのメイン・サプライヤーとして選定し、EDAツールのライセンス契約を拡大したという。

※日本シノプシス合同会社

2010.02.16

2010年2月8日、カスタム設計環境とHDLデバッグ環境を手掛けるSpringSoftは、同社の自動デバッグ・システム「Verdi」に、パワーを考慮するデバッグ・モジュールを新たに追加したことを発表した。

プレスリリース文

SpringSoftによると、新たなパワー考慮のデバッグ機能は、低消費電力化設計のための制約フォーマット「UPF」および「CPF」をサポートしており、デザインにおけるパワー・インテントを理解し、予期しないデザイン動作が論理によるものか、パワー関連問題によるものかを判断する事が可能。パワー関連のエラー原因の視覚化、トレーシング、解析を自動化することができる。

※UPF:United Power Format

※CPF:Common Power Format

RTLレベルで利用できるパワー考慮のデバッグ環境は今のところ「Verdi」のみで、既にベータバージョンが大手半導体企業数社で使用されているという。

※SpringSoft社

2010.02.10

システムレベルのシミュレーション技術を核とした、バーチャル・プロトタイピング市場の上位3社がこの1週間で相次いで買収(買収合意含む)された。

2010年2月3日、シノプシスがVaST Systems Technology社を買収

2010年2月5日、ウインドリバーがVirtutech社を買収

2010年2月9日、シノプシスがCoWare社を買収へ

シノプシスが買収を発表したVaSTとCoWareの2社は、古くは協調シミュレーターと呼ばれていた頃からソリューションを提供しているバーチャル・プロトタイピングの老舗で、同市場シェアの半分以上は両者で占められていると言われている。

VaST社は、早くから「ソフトウェア開発」をターゲットとしたソリューションとしてシミュレーター「CoMET/METeor」を売り出し、複写機、デジカメ、自動車といった分野を中心に顧客を獲得。シミュレーションの速さや日本製マイコンモデルのラインナップで顧客の支持を集めていた。

一方のCoWareは、「SoCアーキテクチャ設計」をターゲットとしたハードウェア設計向けのシミュレーターとして「N2C」を売り出し、C言語設計創成期に多数の顧客を獲得。その後、SystemC言語ベースのシミュレーター「Platform Architect/Virtual Platoform」にリニューアルし、携帯電話、複写機、デジタル家電、といった分野でARMユーザーを中心に「ソフトウェア開発」ニーズも含めて顧客を増やしていた。

ウインドリバー(インテル)が買収したVirtutechは、AMDと共同開発した経緯を持つOS/ミドルウェア開発をターゲットとしたシミュレーター「Smics」を売り出し、OSベンダなどの顧客を獲得。元々はx86アーキテクチャ向けのソリューションという立ち位置であったが、その後、ターゲットとするCPUを増やしソリューションを拡大していた。

Virtutechは、ハードウェア/SoC開発向けにケイデンスと連携した活動も見せていたが、今回発表されたウインドリバーによる買収によって、いわゆる一般的なESL市場からは姿を消し、インテル/ウインドリバーのユーザー向けのソリューションとして残る形が予想される。

VaSTとCoWareについては、既に多数の顧客が存在している事から、シノプシスが以前買収したハードウェア・プロトタイピングの「HAPS(旧シンプリシティ製品)」と「CHIPit」のように、製品名を残し、両ソリューションを従来通りの形で存続していくと思われる。

シノプシスは、バーチャル・プロトタイピング用のシミュレーターとして、旧Virtio社製品「Innovator」を既に買収により保有していたが、今回、同分野の上位2社を一気に買収することでバーチャル・プロトタイピング市場をほぼ独占。これまで手薄だったESLソリューションが一気に強化される。シノプシスの包括的なソリューションにより、ゆくゆくはバーチャル・プロトタイピングからの実装も夢ではなくなりそうだ。

※VaST Systems Technology社

※CoWare社

※Virtutech社

※日本シノプシス合同会社

※ウインドリバー株式会社

2010.02.05

2010年2月3日、ビラージロジックは2010会計年度第1四半期(09年10月-12月)の売上を報告した。

プレスリリース文

ビラージロジックの2009年10-12月の売上は、前年同時期より約92%増、前Q4より約65%増の2170万ドルという好結果となった。2009会計年度は全ての四半期で前年割れを記録していたが、2010会計年度は幸先の良いスタートを切った。(※GAAP基準による会計結果)

ビラージによると、Q1売上はライセンスの売上が前期よりも55%増、ロイヤリティ収入が前期よりも114%増という内容。ARC社の買収による売上増と顧客の半導体ファウンドリのIP利用が増加した結果、記録的な売上増へと繋がった。

ビラージは、次期Q2(10年1-3月)の売上についても引き続き好調が続き、前年比大幅増の2350-2400万ドルに達すると予測している。

※ビラージロジック株式会社

※ビラージロジック株式会社

2010.02.04

2010年2月3日、ケイデンスは2009年Q4(10-12月)の売上を報告した。

プレスリリース文

ケイデンスの2010年Q4(10-12月)の売上は、前年同時期比約3%減、直前のQ3と比較して約2%増の2億2000万ドル。2009年度通年(1月-12月)の売上合計は、前年比約20%減の8億5100万ドルという結果となった。(※GAAP基準による会計結果)

ケイデンスは2009年全ての四半期で売上が前年割れとなったが、経営の建て直しが順調に進んでいる様子で、Q1からQ4にかけて少しずつ売上を回復させており、今期Q4は久しぶりに収支を黒字に戻している。

尚、ケイデンスは次期2010年Q1の売上を2億1000-2000万ドルと予測。2010年通年の売上総額は2009年を上回る8億6500万-9億ドルに達すると予測している。

※日本ケイデンス・デザイン・システムズ社

※日本ケイデンス・デザイン・システムズ社

2010.02.04

2010年2月3日、アームは、2009会計年度第4四半期(2009年10-12月)の売上を報告した。

プレスリリース文

http://www.jp.arm.com/pressroom/10/100203.html

アームの2009会計年度Q4 (2009年10-12月) の売上は、前年比5%減、前Q3比14%増の

1億4000万ドル。2009年通期(2009年1-12月)の売上は、前年比10%減の4億8950万ドルという結果となった。

アームのCEOは、業界全体の売上が約20%減少している中、シェアの拡大により売上の減少を10%に留め、営業利益率30%を維持できたとコメント。2010年は未だ不透明としながらも、業界全体の展望と同様に業績は改善する方向とみている。

アーム2009年Q4トピックス(抜粋)

アーム2009年Q4トピックス(抜粋)

・携帯電話の高機能化に伴い、1台当たりのチップ数平均2.4を達成

・車載機器、マイクロコントローラ、プリンタ、スマートカードなど、幅広いアプリケーションでプロセッサのライセンス契約19件を締結

・サムスン社が次世代のコンシューマ機器向けにARMのMaliグラフィックス・プロセッサのライセンスを取得

※アーム株式会社

2010.02.03

Electronics Design and Solution Fair 2009に出展していた、DSMソリューションズのブースレポート。

DSMソリューションズは、参考出展として仏DOCEA Power社のパワー/熱解析ツール「ACEplorer」を展示していた。

DSMソリューションズは、参考出展として仏DOCEA Power社のパワー/熱解析ツール「ACEplorer」を展示していた。

「ACEplorer」は、デザイン初期段階のシステムレベルで低消費電力アーキテクチャーを探求するツールで、ユーザーの入力したデザインデータからXMLフォーマットのパワーモデルを生成し、同モデルを用いたシミュレーションでパワーおよびサーマル・ビヘイビアの解析/見積りを行う。デザインのシステム構成はIP-Xactフォーマットで入力可能で、解析結果からパワー制約ファイル「UPF」を自動生成する事が可能。生成したUPFはRTL以降のインプリメント工程で利用することができる。

※UPF:Unified Power Format

「ACEplorer」は直接的に消費電力を削減するツールではなく、システムレベルでパワー仕様を見積もり、その情報を下流設計へと渡すという、パワー解析およびパワー管理ツールという位置付け。同ツールを利用することで、IRドロップや熱暴走といった下流設計で起こりうる問題に早めに手を打つ事ができるという。

DOCEA Power社は2006年設立のEDAベンチャーで、仏モアランを拠点としている。同社が世に送り出した初めての製品が「ACEplorer」で、未だ日本国内にユーザーはいないが、海外では既に「ACEplorer」を製品開発に適用している顧客がいると聞いた。

※DOCEA Power社

※DSMソリューションズ株式会社

2010.02.03

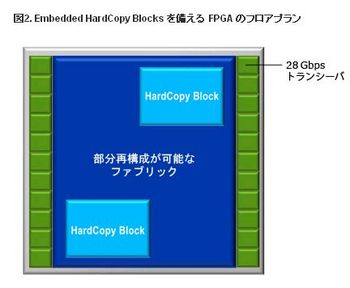

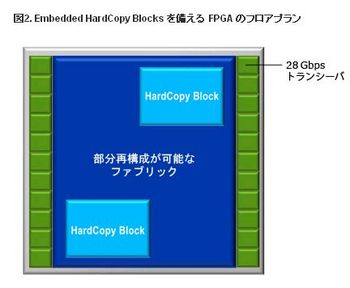

2010年2月2日、アルテラは、開発中の28nmFPGAで使用される3つの新技術を発表した。

プレスリリース文

発表された新機能は以下の3つ。

・Embedded HardCopy Blocks

Embedded HardCopy Blocks は、アルテラのストラクチャードASIC「HardCopy ASIC」の機能を活用したカスタマイズ可能なハードIPブロックで、アプリケーション・スペシフィックな機能、トランシーバ・プロトコル、ユーザー独自に所有するカスタムIPなどの実装を迅速かつ低コスト、低消費電力で実現するもの。標準的なファンクションやロジック比率の高いファンクションを最適化したIPブロックとしてFPGA内に取り込むイメージとなる。

・パーシャル・リコンフィギュレーション(部分再構成)

パーシャル・リコンフィギュレーション機能は、文字通りFPGAを動作させたまま、一部分だけを再コンフィギュレーションする技術。この技術を使えば、FPGAと外部メモリで複数のアプリケーションを実現できるようになり、FPGAには必要な機能のみを実装することで、FPGAサイズ、消費電力、ボード面積の削減が可能となる。システムを中断する事無く、リモート操作でシステムを拡張できる点も大きなメリットとなる。

・28Gbps エンベデッド・トランシーバ

現在提供している11.3Gbps エンベデッド・トランシーバの更に上をいく28Gbps エンベデッド・トランシーバを用意。このトランシーバにより、デザインの機能を維持しつつ、外部コンポーネント、I/O数、消費電力、コストを削減することが可能。400Gシステムなどの次世代デザインを、コストの高い外部コンポーネントを追加することなく、ワンチップ上に実装することも可能となる。

アルテラは、同じデザインを40nmFPGAから28nmFPGAに移行し、これら新技術を適用することで、面積、消費電力、トランシーバのチャネル数ともに、4分の1程度まで削減可能としている。

※日本アルテラ株式会社

※日本アルテラ株式会社

2010.02.02

2010年2月1日、LSI設計分野の国際学会「DesignCon 2010」がサンタクララで開幕した。

DesignCon 2010公式ホームページ

今年はキーノート、チュートリアル、フォーラム、パネルディスカッションなど計100以上のセッションが予定されており、展示会場ではEDAベンダを中心とした計117社が設計ソリューションを展示する。

恒例となっている「DesignVision Award」は、現地時間2月2日に発表される予定で、今年も計8部門に分けて各部門の受賞候補が発表されている。「DesignVision Award」は市場にインパクトを与えた優れた製品、サービス、アプリケーションを表彰するもので、毎年「DesignCon」で発表されている。

■DesignCon2010 DesignVision Awardファイナリスト一覧

Category 1: IC Design Tools

-Cadence Design Systems for the Encounter Digital Implementation System

-Altera Corporation for the Quartus II Software version 9.1

-Xilinx for the Xilinx ISE Design Suite 11

Category 2: Design Verification Tools

-Agilent Technologies for the ADS DDR3 Compliance Design Kit

-DFT Microsystems for the DV1600 SerDes Validation Tester

-Synopsys for the VCS 2009.09

Category 3: Interconnect Technologies and Components

-Samtec for BullsEyeTM

-Molex Incorporated for the EdgeLine CoEdge Connector

-FCI for the High Performance High Density TwinMezzTM

Category 4: PCB Design Tools and Technologies

-Altium Limited for the Altium Designer

-Rogers Corporation for the RO4000® LoProTM Series Laminate

-Simberian Inc. for the Simbeor 2008.01

Category 5: Semiconductor Components and ICs

-PMC-Sierra for the HyPHY 10G & 20G

-Maxim Integrated Products for the MAX2078

-SiBEAM for SiBEAM's Second-Generation SB9220/SB9210 HRTX and SB9221/SB9211 Wir -elessHD HRRX Chipsets

Category 6: Semiconductor IP

-Cadence Design Systems for the Chipestimate.com Semiconductor IP Customer Testimonials

-Coreworks for the CWda60 - Sideworks Dolby Digital Professional Encoder IP

-Rambus for the Rambus and Kingston Threaded Module

Category 7: System Modeling and Simulation Equipment

-Sigrity for the Channel Designer

-Mentor Graphics for the HyperLynx PI

-E-System Design for SPHINX

Category 8: Test and Measurement Equipment

-Agilent Technologies for the Agilent J-BERT N4903B

-SyntheSys Research for the BERTScope Si 25000C & BERTScope CR 25000A

-LeCroy Corporation for the WaveMaster 830Zi

2010.02.02

Electronics Design and Solution Fair 2009で開催された、10周年特別企画:「各社のNo.1設計者が語る"私の設計"」の聴講レポート。

同企画の詳細はこちらのEDSFair2010公式ページをご参照下さい。

簡単に言うと、各社エキスパートのエンジニアが「設計とは何か?」を語り、これからの世代へ「先輩からの一言」を伝えるというものです。会場となった特設ステージは立ち見の出る満席状態でした。

講演のトップバッターを務めたのは、パナソニック株式会社の道正 志郎 氏(本社R&D部門 戦略半導体開発センター ハードウェア設計エキスパート)。司会の東京工業大学の松澤 昭 教授(理工学研究科 電子物理工学専攻 工学博士)とは元上司と部下という間柄。

講演のトップバッターを務めたのは、パナソニック株式会社の道正 志郎 氏(本社R&D部門 戦略半導体開発センター ハードウェア設計エキスパート)。司会の東京工業大学の松澤 昭 教授(理工学研究科 電子物理工学専攻 工学博士)とは元上司と部下という間柄。

講演によると、道正氏はバブル真っ只中の平成元年に松下電器に入社。当時は日本の半導体が全盛の時代で、出張はビジネスクラス、殆どのEDAツールは内製で「ソルボーン」というワークステーションまで作っていた。そんな中、道正氏はCMOSアナログと出会う。専門家が少なく、差別化された分野を担当できた事が結果的にラッキーだったと道正氏。当時はあまり忙しくなく勉強する時間が取れた事、アナログ設計は自動化されずに人間に頼る必要があった事なども、道正氏がアナログ設計にのめり込んでいく要因だったようだ。

幾つかの設計を経て、PHS用アナ/デジ混載LSIの設計を担当した際に、道正氏はシミュレーションツールが無かったため、s変数とz変数の伝達関数表示プログラムなどツールの自作を開始した。道正氏は今でもPLLのジッタ解析ツールなどツールの自作を続けており、Excelベースの自作ツールを用いてかなりのアナログ回路が設計可能との事。逆に設計の名人ほどSPICEシミュレーションをせず、理論計算だけで済ませてしまうという事実があるという。

その後道正氏は、上司(松澤教授)の指示で松下電器の設計研修所でPLL回路の講師を担当。未だ回路設計の経験も無いのに講師を担当するという無理難題が自らの成長に役立った。以降、キャリア・アップへの投資を自ら積極的に進めており、人前で話をする「講演」の機会は一番勉強となるため、決して断らないのがポリシーだという。

アナログ設計の面白さについては、「人間の工夫が計算機の最適化を上回る」と表現し、革命的とも言える技術が発明できる点を指摘。不可能と思える要求仕様を克服し、如何に「美しい回路」を設計するかが自分に限らずアナログ設計者の夢であるとした。また道正氏は、設計とは突き詰めると「探求:必要な情報を集めて課題を見つける」、「発想:今までと違うアイデア、工夫、組み合わせ」、「実現:形、仕様、パラメータなど決定」、の3つのプロセスに分かれるが、一番重要なのは「課題を見つけること」と指摘。うまく課題を見つければ人生の目標になることもあるが、課題を見つけるためには視点を画一化しない多様性が必要とした。

アナログ設計の面白さについては、「人間の工夫が計算機の最適化を上回る」と表現し、革命的とも言える技術が発明できる点を指摘。不可能と思える要求仕様を克服し、如何に「美しい回路」を設計するかが自分に限らずアナログ設計者の夢であるとした。また道正氏は、設計とは突き詰めると「探求:必要な情報を集めて課題を見つける」、「発想:今までと違うアイデア、工夫、組み合わせ」、「実現:形、仕様、パラメータなど決定」、の3つのプロセスに分かれるが、一番重要なのは「課題を見つけること」と指摘。うまく課題を見つければ人生の目標になることもあるが、課題を見つけるためには視点を画一化しない多様性が必要とした。

LSIの未来については、今までの常識・次元を変えるイノベーションが必要とした上で、「変化していない事を疑おう」と強調。例として、バラつかないプロセスが生まれれば、コーナー解析は非常に簡単。20年来変わらぬ設計手法を変える事が出来れば、プロセス・設計ともに工数が大幅に削減でき、消費電力もコストも削減できると指摘した。

また道正氏は最後に、「LSIは人間が造りだした究極の(大量生産)の産物」であり、使い捨てを助長しているのでは?と疑問を投げかけ、そういった負の課題への対処案として、「電化製品にも生物的特長を取り入れ、愛される電化製品を作ろう」とユニークなアイデアを披露して講演を終えた。

尚、同講演企画の最優秀スピーカーとして選ばれたのは道司氏。会場の聴講者の方々も納得の様子でした。

2010.02.01

Electronics Design and Solution Fair 2009に出展していた、EVEのブースレポート。

EVEのブースでは、昨年7月に発表した新型エミュレーター「ZeBu-Server」を大々的に展示。「ZeBu-Server」は、最大10億ASICゲートのデザイン検証に対応可能なエミュレーターで、同社エミュレーター製品として6世代目の製品となる。

EVEのブースでは、昨年7月に発表した新型エミュレーター「ZeBu-Server」を大々的に展示。「ZeBu-Server」は、最大10億ASICゲートのデザイン検証に対応可能なエミュレーターで、同社エミュレーター製品として6世代目の製品となる。

「ZeBu-Server」はデザイン容量もさることながら、コンパイル時間および検証速度の更なる高速化が実現されており、1億ゲートのデザインを約1時間でコンパイル可能。4000万ゲートのデザインを約10Mhzの速度でエミュレーション可能で、5台のマシンを用いた並列処理で5Mトランザクタ/秒を達成した実績もある。

EVE副社長のLauro Rizzatti氏によると、「ZeBu-Server」は、昨年7月の発表以降この半年間で既に3社のユーザーを獲得しており、うち1社は日本のユーザー。ワールドワイドでトップ10に入る大手電機・半導体メーカーによる製品評価が6件進行中との事。

ビジネス面については、2008年は市場の急激な変化で大きなダメージを受けたが、2009年で売上を元の水準に戻すことに成功。2010年は更なる売上増を目指すと聞いた。Lauro Rizzatti氏によると日本市場での同社の売上は堅調で、多くのEDAベンダが日本市場で苦戦を強いられる中、2009年の売上は良い結果を残したという。

「ZeBu-Server」は、デザイン1ゲート当たりの検証コストが僅か「2セント」と、コスト面での優位性に加え、筐体自体が小さく消費電力も少ないことから、Green&Low Costなエミュレーション・ソリューションという打ち出しも行っている。

※日本イブ株式会社

※日本イブ株式会社

2010.01.31

2010年1月27日、オープンコアプロトコル(OCP)の普及団体OCP-IPは、同団体の会員に提供しているSystemC TLMキットのバージョンアップを発表した。

OCP-IPが会員向けに無料提供している「SystemC TLMキット」は、OCP準拠のTLMベースの通信モデル、インタフェースモデルを作るためのキットで、昨年4月にOCP-IPがOSCI TLM2.0対応版をリリース。今回バージョンアップされたキットでは、最新のOSCI TLM 2.0.1をサポートしている。

OCP-IPから現在提供される最新の「SystemC TLMキット」は、OCP2.1および2.2仕様をサポートするもので、昨年11月に発表されたOCP3.0仕様をサポートしている訳ではない。

尚、OCP-IPの「SystemC TLMキット」は、非OCP会員でもモニターの無いバージョンを無償利用できる。

※OCP-IP(Open Core Protocol International Partnership)

2010.01.31

Electronics Design and Solution Fair 2009に出展していた、Synforaのブースレポート。

Synforaは新興ベンダエリアでの出展。CTOのVinod Kathail氏も来日にしていた。

Synforaは新興ベンダエリアでの出展。CTOのVinod Kathail氏も来日にしていた。

同社の大きなトピックスは、EDSFair2010にて発表した高位合成ツール「PICO」のC++サポート拡張と、昨年発表した新製品「PICO Extreme Power」の初披露。

Synforaによると、今回のC++サポートの拡張により演算子のオーバーロードがサポートされたほか、ホストインタフェース、メモリ・マッピングの強化、ループ構文やポインタのサポート範囲の拡張などなどが実現された。

また、「PICO Extreme」および「PICO Extreme FPGA」の最新のバージョンでは、QOR改善も進められ、合成する回路の面積を最大で8%削減。ザイリンクのDSPユニット向けのマッピング機能も強化されたという。

今回ブースで紹介していた新製品「PICO Extreme Power」は、システムレベルの消費電力最適化を実現する高位合成ツールで、高位合成ツール「PICO Extreme」にダイナミックなPower最適化を実現するマルチレベルでのクロックゲーティング機能が追加されたもの。このツールを使えば、CアルゴリズからRTLを合成する過程でダイナミックな消費電力を最適化することが可能。これまでの事例では、ビデオアプリケーションの合成でダイナミックな消費電力を半減させた事もあると聞いた。

(※図はPICO Extreme Powerによる最適化例)

※Synfora社

2010.01.31

2010年1月29日、アルテラは、2009会計年度第4四半期(2009年10-12月)の売上を報告した。

プレスリリース文

アルテラの2009会計年度Q4 (2009年10-12月) の売上は、前年比12%増、前Q3比27%増の

3億6500万ドル。この数字は過去2年間で最高となるもので、純利益は前年比の倍に近い1億297万ドルと好調な結果を残した。アルテラは、全ての市場、全ての製品セグメントにおいて売上実績が前年を上回ったとしている。

2009年度通期の売上高の合計は、前年比13%減の11億9541万ドル。Q4は良い結果を残し売上回復の兆しを見せたものの、全体としてはQ1-Q3のマイナスが響いた。経営面では、2009年度を終えてアルテラの現金および短期投資額は、前年実績の12億ドルから15億ドルに増加した。

アルテラは、2010年度においても、40nm製品におけるリーダーシップが新たな成長ドライバーになるとみている。

※日本アルテラ株式会社

※日本アルテラ株式会社

2010.01.30

2010年1月29日、STARC(株式会社半導体理工学研究センター)とケイデンスは、STARCが開発したEDAツール評価用データベースを活用したリグレッション・テスト環境の構築を発表した。

プレスリリース文

発表によるとSTARCとケイデンスは、STARCメンバー企業で使用するEDAツールの信頼性評価を目的に、STARCが開発したEDAツール評価用の「QAデータベース」を用いたEDAツールのリグレッション・テスト環境を構築した。

同プロジェクトは、先日STARCが発表したアトレンタ社との品質向上プロフラムと同種のもので、既に実施されたリグレッション・テストによって下記ケイデンスのEDAツールがSTARCのQAデータベースに認証されている。

・Conformal® Constraint Designer

・Encounter® Timing System

・Encounter Digital Implementation Systemが持つStatistical Static Timing Analysis機能

・Encounter RTL Compiler

STARCメンバー企業の設計者は、リグレッション・テスト結果のレポートを活用することで、EDAツールの信頼性評価に関わる工数を削減。認証ツールを用いた信頼性の高い設計フローを迅速に構築することができる。

STARCコメント:

西口 信行 氏(執行役員、開発第1部長):

「STARCの最も重要な役割の一つは、メンバー企業が使用する半導体設計ソフトウェアの品質と精度の検証を支援することです。今回のケイデンスとの協業は、STARCとメンバー企業が開発したテスト・データを使用してソフトウェアの品質検証を行い、STARCのメンバー企業の要求事項に最大限合致することが確認できるため、我々の使命を果たすことができます。」

※STARC(株式会社半導体理工学研究センター)

※日本ケイデンス・デザイン・システムズ社

2010.01.29

Electronics Design and Solution Fair 2009に出展していた、サイバネットシステムのブースレポート。

サイバネットは、代理店として販売している米Bluespec社のESL合成ツール「Bluespec SystemVerilog」を展示。同ツールの販促活動の一環として企画した「Bluespecデザインコンテスト」をアナウンスしていた。

※デザインコンテスト案内ページ

同コンテストは、お題となる「ソート回路」の設計を「Bluespec SystemVerilog」で行い、その回路性能や工夫点を競い合うというもので、学生、社会人問わず個人でエントリー可能。もちろん「Bluespec SystemVerilog」の無償ライセンスが貸与され、優秀作品には、アップルの「iPad」をはじめとした賞品が贈られる。応募期間は3月1日から5月31日まで。

同コンテストは、お題となる「ソート回路」の設計を「Bluespec SystemVerilog」で行い、その回路性能や工夫点を競い合うというもので、学生、社会人問わず個人でエントリー可能。もちろん「Bluespec SystemVerilog」の無償ライセンスが貸与され、優秀作品には、アップルの「iPad」をはじめとした賞品が贈られる。応募期間は3月1日から5月31日まで。

「Bluespec SystemVerilog」は、最新バージョンの2009.11にて新たに「Paclib」と呼ぶデータパス回路向けのビルディング・ブロックをサポート。ツールのエンハンスと合わせて、昨年のDACで発表していたFPGAエミュレーションをターゲットとしたソリューションにも注力しているとの事。

話によると、Bluespecはこの1年間で複数の日本顧客を獲得。ワールドワイドの顧客数は12以上で、2009年売上は前年比約30%増を達成したという。

※サイバネットシステム株式会社(Bluespec国内代理店)

※Bluespec社

2010.01.28

2010年1月28日、SystemC関連の技術セミナー「SystemC Japan」のメンバー企業がSystemCの更なる普及を目指してSystemCのホームページを立ち上げた。※SystemC Japanオフィシャルサイト

・SystemC Japanのメンバー企業

株式会社エッチ・ディー・ラボ

日本ケイデンス・デザイン・システムズ社

コーウェア株式会社

フォルテ・デザイン・システムズ株式会社

カリプト・デザイン・システムズ株式会社

コフルエントデザイン社

株式会社EDAエクスプレス

エッチ・ディー・ラボの長谷川氏は、「SystemCは現在、アーキティクチャー探索、早期ソフトウエア開発、動作合成、アルゴリズム検討の世界で広く使われています。その一方、SystemCは難しいと言った声も多くSystemCは専門家の言語ととらえている方も多いようです。本サイトでは、「ここまでできるSystemC」をテーマにSystemCをもっと簡単に利用して頂く目的で開設いたします。」と述べている。

このホームページでは、SystemCの普及を促進する為に入門的なドキュメントや、実践的な記述例が数多く置かれている。また、SystemCに関する様々な資料を集約し、掲示板を通し、設計者に情報交換の場を提供しており、SystemCに関するノウハウや情報の拠点になることを目指している。

尚、SystemC Japanメンバー企業は今年も技術セミナーの開催を計画中。ホームページを通じた技術交流と合わせて、従来通りセミナーを通じた技術交流も継続していく。

※SystemC Japanオフィシャルサイト

2010.01.27

2010年1月26日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automation社と、トランジスタレベルの統計的ばらつき解析ソリューションを手掛けるカナダのSolido Design Automation社は、両社のコラボレーションによるナノメータICのばらつき解析フローを発表した。

プレスリリース文

発表によると両社は、ある大手ファブレス半導体メーカーからのニーズに応じて、Solidoのばらつき解析ツール「Variation Designer」の解析エンジンとして、BerkeleyのSPICEシミュレーター「Analog FastSPICE Platform」を利用するソリューションを開発。

「Analog FastSPICE Platform」 と「Variation Designer」の組み合わせにより、設計者は高速なばらつき解析と修正機能を手に入れる事が可能になるという。

※Berkeley Design Automation社

※Solid Design Automation

2010.01.27

2010年1月27日、ケイデンスは、ルネサステクノロジが同社のカスタムIC設計環境「Virtuoso」の最新バージョンを国内外のデザインセンターで標準採用した事を発表した。

プレスリリース文

ルネサステクノロジは、以前からアナログ/ミックスシグナル設計向けにケイデンスの「Virtuoso」を採用しているが、「Virtuoso」の最新バージョンであるIC6.1のコンストレイント・ドリブンな設計および検証機能に更なるTAT削減効果を期待。今回、国内外のデザインセンターへ標準配備する事を決定した。

ルネサステクノロジは「Virtuoso」の持つ下記の機能/利点を評価しており、品質を犠牲にすることなく設計期間を最大30%削減できると期待している。

・コンストレイント・ドリブンなメソドロジ

-設計の意図を確実に維持するために費やされる時間を短縮

-容易なIPの再利用

・歩留まり最適化、寄生を考慮した設計モード

・コンストレイント・テンプレート機能を含む先進的な自動化機能

※日本ケイデンス・デザイン・システムズ社

2010.01.27

2010年1月27日、STARC(株式会社半導体理工学研究センター)とアトレンタは、STARCが開発したEDAツール評価用データベースを活用したツール品質向上プログラムの始動を発表した。

プレスリリース文

発表によるとSTARCは、EDAツールの改版時の不具合を早期発見する事を目的に、テストケースと呼ぶ評価仕様書や評価モチーフで構成されるEDAツール評価用の「QAデータベース」を開発し、アトレンタに提供。アトレンタはこの「QAデータベース」を用いたツールの品質向上(評価)プログラムを開始し合わせて評価実施結果をSTARCにレポートする仕組みを作った。

実際にアトレンタが同社のRTL解析ツール「SpyGlass」の改版時に同プログラムを実施したところ、以前見られていたツール改版時のリグレッションが一切無くなったという。

評価実施結果のレポートには、不具合の有無や不具合の内容、不具合の改修予定などの情報とQAデータベースに対応した仕様変更情報なども含まれており、それらを確認する事で設計者は、ツールを設計現場に適用するかどうかの判断を円滑に行う事が可能となり、これまで工数を割いていたツールの確認作業を削減できようになる。

アトレンタは今回の品質向上プログラムについて、ツールの不具合を減らすだけでなく、QAレポートの共有によりユーザー・サポートが容易になったとコメント。

STARCは今回の成果を受け、評価機能の追加や適用EDAツールの拡大を進め、ツール品質の維持やツールの評価・サポートコストの削減に役立てていく予定。

※STARC(株式会社半導体理工学研究センター)

※アトレンタ株式会社

2010.01.27

2010年1月26日、ハードウェアベースの検証ソリューションを手掛ける仏EVE社は、韓国LGエレクトロニクスが同社のエミュレーション・システム「ZeBu-XXL」を採用した事を発表した。

プレスリリース文

発表によるとLGエレクトロニクスは、高性能コンスーマ製品の開発向けに徹底的な評価を行い「ZeBu-XXL」の採用を決定。既にLGエレクトロニクスでは、「ZeBu-XXL」を用いることでシミュレーターでは発見出来なかった根深いバグを複数発見した実績がある。

LGエレクトロニクスによると、「ZeBu-XXL」によるトランザクションレベルのコ・エミュレーションは、1000万ASIC相当のデザインで5Mhzの速度を実現。これまでシミュレーターで2日を要していた検証をトランザクションレベルのコ・エミュレーション8分で処理できるという。

※日本イヴ株式会社

2010.01.27

2010年1月26日、SystemC言語からの高位合成ツールを手がける米Forte Design Systems社は、国内ファブレス半導体ベンダのメガチップスが同社の「Cynthesizer」を採用した事を発表した。

プレスリリース文

発表によると、メガチップスは高位合成ツールの検討にあたり、データパス系回路および制御系回路と異なるデザインで複数の高位合成ツールを評価。その結果、最も優れたRTLコードを生成し、かつ設計資産の再利用が可能なフォルテの「Cynthesizer」の採用を決定した。

メガチップスは、ゲーム機「Wii」、「DS」など任天堂へのLSI供給で有名。デジカメ向けの画像処理LSIや地デジ向けLSIなども手掛けている。今回同社が高位合成ツールの導入を検討したモチベーションは、「LSIアーキテクチャの容易なトレードオフ」にあったようだ。

※フォルテ・デザイン・システムズ社

2010.01.27

2010年1月26日、ケイデンスは、三菱電機が同社のOVM SystemVerilogソリューションを採用し、検証期間の短縮とASIC製品の品質向上を達成したと発表した。

プレスリリース文

発表によると三菱電機は、ケイデンスのOVM SystemVerilogモジュール・ベース・ソリューションを採用する事で、ASICのシリーズ開発において検証コンポーネントの40%が再利用可能となり、新たな検証環境の構築期間を30%短縮。検証環境を部品化することで、製品仕様の拡張に対する更新箇所の反映が容易になり検証環境の構築作業を低減できたとしている。

OVMは利用するツール環境を問わないオープンソースのSystemVerilog検証メソドロジとして、利用者を増やしているが、当然ながら利用するツール環境や検証IPなどにより構築される検証環境は様々で、各EDAベンダはシミュレーターにおける機能の違いや検証IPの提供などで、独自のOVMベース検証ソリューションを打ち出している。

ケイデンスはシミュレーション環境「Incisive Enterprise Simulator」を核としたOVMベース検証ソリューションを展開しているが、検証IP「Cadence® Incisive® Verification IP (VIP)」のラインナップ拡大にも力を注いでおり、数十種類ある検証IPを全て利用可能な単一ライセンスも提供している。

※日本ケイデンス・デザイン・システムズ社

2010.01.26

2010年1月26日、ケイデンスは、NECエレクトロニクスが同社のソリューションを用いて40nmプロセスの設計環境を構築した事を発表した。

プレスリリース文

発表によるとNECエレクトニクスは、ケイデンスのインプリメントツール「Encounter Digital Implementation System」、「Encounter Timing System」、論理合成ツール「Encounter RTL Compiler」を核に40nmプロセス向けの設計環境を構築。既に、同環境を用いて40nm低消費電力プロセスのASICを10件以上設計しており、既に幾つかのデザインはテープアウトし量産を開始している。

NECエレクトロニクスは、「Encounter Digital Implementation System」のマルチスレッド処理機能、「Encounter RTL Compiler」の合成技術を活用したネットリストの最適化機能、統合されたDFM最適化とサインオフ解析機能を使用することにより、2000万ゲート以上の大規模デザインを効率化したという。

※日本ケイデンス・デザイン・システムズ社