NEWS

2010.06.28

第47回DAC(Design Automation Conference)に出展していたVennsa Technologies社のブース・レポート。

Vennsaは、DAC初出展のカナダのベンチャー。※詳細は下記ニュース記事参照。

https://www.eda-express.com/2010/04/dacvennsa-technologies.html

Vennsaは、RTLのデバッグを対象とした検証ツール「OnPoint」を展示。「OnPoint」はフォーマル検証ツールの検出したエラーの情報を読み込み、エラーの原因と推測される箇所を自動的に特定してくれるツールで、ツールの示唆した上位10候補をチェックすれば、ほぼバグは特定できるという優れもの。

これまで「OnPoint」はフォーマル検証ツールのみを対象としていたが、DAC前に発表した最新バージョンでは、シミュレーションにおけるエラーの原因特定にも対応。市販論理シミュレーターのエラー情報からもバグ原因候補の特定が可能となった。また、特定したバグ候補に対して、どのようにしてバグを修正すれば良いか指南してくれるオプション機能も新たに備えられたという。

Vennsa社のCTOSean Safarpour氏によると、同社のセールスは北米市場より先に日本市場で展開しており、既に日本企業の顧客を獲得済み。その理由はフォーマル検証のユーザーとしてスキルが高く、ツールの良さを一番実感してもらえるからとの事。シミュレーションにも対応した事で、今後、北米市場での売り込みにも力を入れるが、引き続き日本市場は同社の最重要市場としてセールス及びサポートに力を注いでいくと聞いた。

※下の画像の人物はVennsa社のCTOSean Safarpour氏

※Vennsa Technologies社

※Vennsa Technologies社

2010.06.28

第47回DAC(Design Automation Conference)に出展していたCalypto Design Systems社のブース・レポート。

Calyptoのブースでは、6月11日にリリースした「PowerPro」の新バージョン4.0と「SLEC」5.0を展示していた。いつも感じる事だが、同社のブースは意外と大きい。

「PowerPro」の新バージョン4.0では、メモリ向けの「PowerProMG」に新たに「アドバイザ機能」を追加。同機能は、RTL記述のどの部分を書き換えればより低電力化が可能かを指南してくれるもので、プッシュボタンでアドバイスを確認可能。これまではあくまでもRTLに記述されている信号だけが最適化の対象であったが、アドバイスに従ってRTLの記述を修正すればより低電力の可能性が広がる。同機能は、既に「PowerPro CG」では実装されていたが、今回「PowerProMG」にも対応させた形だ。

また、「PowerProMG」バージョン4.0では、新たにSystemVerilogをサポートしたほか、ユーザー側で回路の動作モード毎に電力最適化を行う事が可能となった。Calyptoの山本修作氏(Japan Technical Account Manager & Business Development)によると、一般的なロジック回路の設計と違い、メモリ設計の場合はクロック・ゲーティングを駆使しているケースが少なく、その分「PowerProMG」の適用効果が高いという話。また、設計したメモリのRTLをゴールデンとして、メモリのポータビリティを保ちながらターゲットに応じて「PowerProMG」でメモリの最適化を行う顧客も増えているという。

「SLEC」5.0では、シーケンシャル・アナリシス・エンジンを改良し、新たに「LoopInduction機能」を追加。「SLEC」は高位合成前後の機能等価性をチェックできるが、その主な対象となる信号処理系の回路には、「深いループ」が存在する事が多く、チェックに当たっては制限や複雑なツール設定が必要とされていた。今回追加された「LoopInduction機能」は、これまで困難だったデザインの取り扱いを容易にするもので、プッシュ・ボタン式に高位合成前後のコードの機能等価性を検証可能。これまでのようにデザインにおける「ループ」を気にせず等価性をチェックできるようになる。「LoopInduction機能」の追加は「SLEC」にとって非常に大きな進化。高位合成ユーザーに与えるインパクトも大きい。

「SLEC」5.0では、シーケンシャル・アナリシス・エンジンを改良し、新たに「LoopInduction機能」を追加。「SLEC」は高位合成前後の機能等価性をチェックできるが、その主な対象となる信号処理系の回路には、「深いループ」が存在する事が多く、チェックに当たっては制限や複雑なツール設定が必要とされていた。今回追加された「LoopInduction機能」は、これまで困難だったデザインの取り扱いを容易にするもので、プッシュ・ボタン式に高位合成前後のコードの機能等価性を検証可能。これまでのようにデザインにおける「ループ」を気にせず等価性をチェックできるようになる。「LoopInduction機能」の追加は「SLEC」にとって非常に大きな進化。高位合成ユーザーに与えるインパクトも大きい。

尚、「LoopInduction機能」は、高位合成ツール側からの情報を必要としているため、Calyptoでは現在ケイデンスの高位合成との連携を先行して進めていると聞いた。

※カリプト・デザイン・システムズ株式会社

2010.06.25

第47回DAC(Design Automation Conference)に出展していたAMIQ社のブース・レポート。

AMIQ Consultingは、2003年設立の機能検証を主体とした、ルーマニアのコンサルティング会社で、創立メンバーにはケイデンスに買収された元Vericityのメンバーらが含まれている。

同社が検証サービス用の内製ツールとして開発した「DVT」は、e言語とSystemVerilogをサポートする検証エンジニア向けのフロントエンド環境でEclipseをベースとしている。「DVT」のエディタには、シンタックス・チェック、リント・チェック、クラス・トレース等の機能が統合されていて、コードのリビジョン管理も可能。一般的な市販シミュレーターと連携させて運用する事が可能で、検証メソドロジOVM、VMMをサポートしている。

※下の画像は「DVT」のエディタGUI画面

DACでは、「DVT」が新たに検証メソドロジ「UVM」をサポートした事を発表。合わせて「DVT」に新たに実装した「OVM to UVM Migration Wizard」を展示していた。同ウィザードを利用すると自動的にファイルのリネームやスクリプトのアップデートなどを実行し、OVMのプロジェクト・ファイルをUVM形式に変更してくれるという。

DACでは、「DVT」が新たに検証メソドロジ「UVM」をサポートした事を発表。合わせて「DVT」に新たに実装した「OVM to UVM Migration Wizard」を展示していた。同ウィザードを利用すると自動的にファイルのリネームやスクリプトのアップデートなどを実行し、OVMのプロジェクト・ファイルをUVM形式に変更してくれるという。

話によると既に北米市場では複数の顧客を獲得しており、安価な環境なため複数ライセンスの一括販売に成功している。日本国内では未だユーザーは存在していないが、既に製品評価を進めている企業があるとの事。日本では株式会社シンコムが販売代理店を務めている。

※下の画像の人物は「DVT」開発マネージャーの Adrian Simionescu氏

※AMIQ社

※AMIQ社

※株式会社シンコム(代理店)

2010.06.25

第47回DAC(Design Automation Conference)に出展していたZOCALOのブース・レポート。

ZOCALOは、今回初出展となる2006年設立のEDAベンチャーでTexasのAustinが本拠地。

FPGAプロトタイピング向けのRTLパーテショニング・ツールを手掛けていたSpeedGate社(2000年にメンターが買収)のメンバーがファウンダーとして名を連ねている。

今回同社が展示していたのは、ABV(アサーション・ベース検証)の普及を狙ったアサーション生成ツール「Zazz」。「Zazz」はSystemVerilogとVerilogの全てのバージョンをサポートしており、エンジニアによるアサーションの作成を自動的に補助。HDLで記述したデザインをツールに入力すると、解析エンジンがデザイン内のシグナル数をチェックし、その重要度を解析しアサーション候補としてランキング表示する。

ユーザーは示されたアサーション候補を指定するだけで自動的にSVAアサーションを生成する事が可能で、基本的にSVAの知識は必要ない。また、作成済のアサーションの品質チェックやアサーションのカバレッジ・チェックも可能で、アサーションをチェックするためのテストベンチを自動生成する機能もあり、GUIベースで複雑なアサーションを自動生成する事もできる。

※下の画像はGUIベースでアサーション作成を行う「Zazz Visual SVA」のGUI画面

「Zazz」は、「Zazz Bird Dog」、「Zazz Metrics」、「Zazz Visual SVA」、「Zazz Assertion Library Support」と大きく4つのツール・コンポーネントで構成されている。

「Zazz」は、「Zazz Bird Dog」、「Zazz Metrics」、「Zazz Visual SVA」、「Zazz Assertion Library Support」と大きく4つのツール・コンポーネントで構成されている。

ZOCALOのテクニカル・ディレクター Lgor Goldman氏によると、まだ製品をリリースしたばかりだが、既に北米市場でベータ・カスタマーを3社獲得。日本への製品供給ルートは無いが、今回のDACでは複数の日本人エンジニアがブースに訪れたという。

Lgor Goldman氏曰く、「Zazz」は他社のアサーション生成ツールと違い、設計の初期段階から容易に利用できるのが特徴で、テストベンチを用意する必要も無いし、ツールに対する複雑な設定もSVAの習得も一切不要との事。自動と言いながら半自動の他社ツールと違い、我々の製品は真の自動アサーション生成ツールだとアピールしていた。

尚、同社はEDA業界ご意見番Gary Smith氏も「DAC見ておけリスト」でピックアップしていた。

※下の画像の人物がLgor Goldman氏

※ZOCALO社

※ZOCALO社

2010.06.24

第47回DAC(Design Automation Conference)に出展していたアトレンタのブース・レポート。

アトレンタは、DAC2日目の6/15に新製品「SpyGlass-Physical」を発表した。

「SpyGlass-Physical」は、RTLの段階でレイアウト上、問題となりそうな箇所を解析するソリューションで、「いけてない」RTLを事前に修正することで、レイアウト工程からRTLへの手戻り削減を狙うもの。「SpyGlass-Physical」は、従来のSpyGlass製品同様、ルールベースのチェックで問題箇所を指摘するため、重要なのはそのルール作り。アトレンタは日本の半導体ベンダの協力も得て、実例ベースのデータから、レイアウト上問題が発生する可能性の高い「危険なRTL記述」10ケースをルール化したとしている。

「SpyGlass-Physical」は、レイアウト上の問題を完全に取り除く事を目指すツールではないが、実際の開発現場で起こるレイアウト側からRTL設計側への修正依頼を減らし、両者のやり取りを円滑化させる効果も期待できる。

※下の画像はアトレンタ社のブースの様子

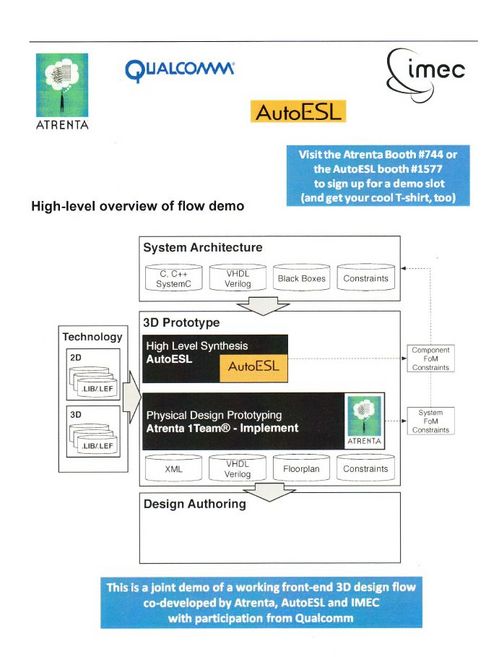

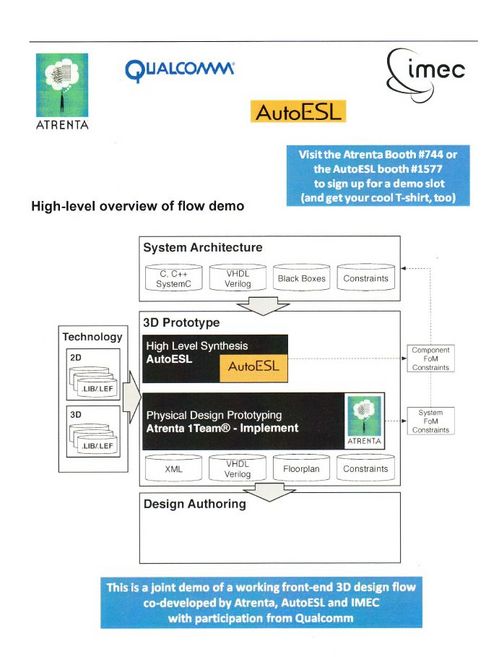

また、今回のアトレンタの展示で興味を惹いたのは、3D-IC設計関連でのAutoESLとのコラボレーション・フロー。ブース内プレゼンで紹介していた同フローは、ベルギーIMECのTSV(スルー・シリコン・ビア)の研究をベースに、Qualcommがユーザーとして参加しているプロジェクトで開発されたもの。TSV技術を効果的に利用するためには、2次元のレイアウトの設計フェーズよりも、より上位の設計フェーズで3次元的な検討が必要というコンセプトがベースとなっており、AtrentaとAutoESLが両社の製品を用いた3D Prototypeフローを構築した。

また、今回のアトレンタの展示で興味を惹いたのは、3D-IC設計関連でのAutoESLとのコラボレーション・フロー。ブース内プレゼンで紹介していた同フローは、ベルギーIMECのTSV(スルー・シリコン・ビア)の研究をベースに、Qualcommがユーザーとして参加しているプロジェクトで開発されたもの。TSV技術を効果的に利用するためには、2次元のレイアウトの設計フェーズよりも、より上位の設計フェーズで3次元的な検討が必要というコンセプトがベースとなっており、AtrentaとAutoESLが両社の製品を用いた3D Prototypeフローを構築した。

フローとしては、AutoESLの高位合成ツールによって様々なアーキテクチャの回路を自動生成し、それら回路のフィジカル・プロトタイプをAtrentaの「1Team-Imprement」で実行。その結果からTSVによるデザインへのインパクト、熱分布、メカニカル・ストレスなどを解析し、何処に、どのようにTSVを使うか? その様々なオプションを探求する。

未だ実験レベルのフローという事だが、上流手法での解析の有効性は確認済みという事で引き続きAtrenta、AutoESL、IMECの3社で研究を進めていくという。

※下の画像はアトレンタ社の資料より 3Dフローの概要

※アトレンタ株式会社

2010.06.24

第47回DAC(Design Automation Conference)に出展していたメンター・グラフィックスのブース・レポート。

メンターのブースでは、バックエンド系のソリューションとして、新製品となる寄生RC抽出ツール「Calibre xACT 3D」と配置配線およびレイアウト検証統合環境「Calibre InRoute」2品をアピール。

DAC直前の6/11に発表された「Calibre xACT 3D」は、メンターが新たに開発したレイアウトデータからのRC抽出ツール。製品名の「3D」とは、Field Solverを用いたMaxwell方程式での電磁界シミュレーションを指しており、文字通り「Calibre xACT 3D」にはField Solverが内蔵されている。

一般的にField Solverを用いたRC抽出ツールは、高精度ながら処理が非常に重く、用途が限られていたが、「Calibre xACT 3D」はその常識を覆すツールで、従来手法ではタイミング不一致の問題が顕著化する32/28nm以降のプロセスをターゲットに、Field Solverを用いた高速・高精度なRC抽出を実現。シミュレーション精度は誤差3%以内、従来製品よりも1ケタ高速な処理性能を有するという。高速化の秘密は内蔵するField Solverのエンジンによるところが大きく、同エンジンは買収したPextra社の開発した技術を利用。同エンジンはSTARCでも評価されお墨付きを得ていたが、既に台湾UMCでは「Calibre xACT 3D」をリファレンス・サインオフ抽出ツールの1つとして採用したという。

※下の画像はメンター・グラフィックス社の資料より 「Calibre xACT 3D」は精度と速さを両立

もう一つの「Calibre InRoute」は、今年の連休明けに発表された新製品で、メンターの配置配線ツール「Olympus-SoC」上で「Carible」が走るという両製品の統合環境。

もう一つの「Calibre InRoute」は、今年の連休明けに発表された新製品で、メンターの配置配線ツール「Olympus-SoC」上で「Carible」が走るという両製品の統合環境。

これまでも「Olympus-SoC」と「Carible」は密接な連携によって、比較的シームレスなP&Rとレイアウト検証のフローを実現していたが、あくまでも別ツールとしての連携に留まっていた。今回発表された「Calibre InRoute」は、「Olympus-SoC」上に「Carible」が移植された新製品で、「Calibre InRoute」上にはプルダウン・メニューの一つとしてDRCチェック機能が備えられており、DRCルールを予め読み込んでおく事で、P&Rを進めながらその場でDRCを実行する事が可能。余計なデータのハンドリングを一切省いた形で単一環境の中でP&RとDRCを同時実行でき、レアなエラーを見つけ次第すぐに自動ECOを行い、エラーの一発修正を実現する。

※下の画像はメンター・グラフィックス社の資料より 「Calibre InRoute」のイメージ図

メンターは、既に「Calibre」製品ファミリを中心に半導体ファウンドリ大手のTSMCと密接なパートナー関係を築き上げており、TSMC最新のAMSリファレンス・フロー1.0に対するサポートを表明しているが、その一方で今回のDACでは、GLOBALFOUNDRIESとのパートナーシップも発表。両社は28nm以下のプロセスをターゲットとした、Calibreベースの物理検証リファレンス・フローを共同開発しているという。

メンターは、既に「Calibre」製品ファミリを中心に半導体ファウンドリ大手のTSMCと密接なパートナー関係を築き上げており、TSMC最新のAMSリファレンス・フロー1.0に対するサポートを表明しているが、その一方で今回のDACでは、GLOBALFOUNDRIESとのパートナーシップも発表。両社は28nm以下のプロセスをターゲットとした、Calibreベースの物理検証リファレンス・フローを共同開発しているという。

※メンター・グラフィックス社の上流設計ソリューションに関しては、別記事でレポートさせて頂きます。

※メンター・グラフィックス・ジャパン株式会社

2010.06.23

カリフォルニア州アナハイムで開催された、第47回DAC(Design Automation Conference)のレポート。

一昨年に続きアナハイム開催となった今年のDAC。不況の影響がやはり大きいのか、来場者は遂に6000名レベルに。(カンファレンス、展示会、その他来場者全ての合計)

一昨年に続きアナハイム開催となった今年のDAC。不況の影響がやはり大きいのか、来場者は遂に6000名レベルに。(カンファレンス、展示会、その他来場者全ての合計)

来場者減と並行して展示会に出展する企業数も年々確実に減少しており、今回は計174社が出展、うち初出展24社という内訳だった。

カンファレンスでは、148の論文発表、9つのSpecial Session、35のTechnical Session、6つのWorkshopが行われ、論文発表数だけは昨年の計117を上回った。Best Paperには、カーネギーメロン大のXin Li氏が発表した「Bayesian Virtual Probe: Minimizing Variation Characterization Cost for Nanoscale IC Technologies via Bayesian Inference」が選ばれた。全体的にカンファレンスでは、アジア系(特に中国系)の発表者数がかなり増えた印象だった。

カンファレンスでは、148の論文発表、9つのSpecial Session、35のTechnical Session、6つのWorkshopが行われ、論文発表数だけは昨年の計117を上回った。Best Paperには、カーネギーメロン大のXin Li氏が発表した「Bayesian Virtual Probe: Minimizing Variation Characterization Cost for Nanoscale IC Technologies via Bayesian Inference」が選ばれた。全体的にカンファレンスでは、アジア系(特に中国系)の発表者数がかなり増えた印象だった。

今回の47DACで印象に残ったのは、大手半導体ファウンドリの影響力とESLブーム。

半導体ファウンドリ最大手のTSMCに続いて、今年はGLOBALFOUNDRIESが初出展。GLOBALFOUNDRIESはスポンサーとして上から2番目の「Gold Exhibiter」として、会場内計4ヶ所にブースを構え、バックエンド系を中心に20社近いパートナーEDAベンダとの共同展示を実施。同社のCEO Douglas Grose氏は、基調講演のトップ・バッターを務め、チップ開発の革新には、EDAベンダ、IPベンダ、設計サービス会社とのエコシステムが必要不可欠とし、電機メーカーに対し製造パートナーとの関係の再定義を呼びかけた。

TSMCは、DAC開催前の6/8に新たな2つのリファレンス・フローを発表。一つは刷新を重ねているデジタル・インプリメントの「リファレンス・フロー11.0」で、もう一つはアナログ/ミックスド・シグナル設計向けの「AMSリファレンス・フロー1.0」。この発表が出るや否やCiranova、Synopsys、Apache、Solid、Magma、Mentor、SiloconFrontline、Pyxis、EdXact、Fotre、CadenceなどEDA各社(順不同)は、こぞって同フローに自社製品が採用された事を発表し、それら発表の多さが逆にTSMCの存在感と影響力を浮き彫りにした。

また驚かせたのは、今回のTSMC「リファレンス・フロー11.0」に初めてESLツールが加わった事で、TSMCはPPA(パワー、性能、面積)の向上に向けてバーチャル・プラットフォーム、高位合成、ESL to RTL検証などを導入。TSMCのエンジニアリング・マネージャーのAshok Mehta氏によると、PPAの中でも特にパワー最適化に関してESLツールに期待しているという事で、現時点でSynopsysのバーチャル・プラットフォームやTLM検証ソリューション、Cadence、Mentor、Forteの高位合成、CarbonのESLモデル生成ツールなどが採用されて入ることが明らかになっている。また、同フローには、ArterisのSoCインターコネクトIPも含まれている。

TSMCのリファレンス・フローにも現れているように、ESLはEDAソリューションの中で一つの大きなブームと言えるカテゴリとなっており、今回の47DACでも話題の中心に。未だESL手法そのものを採用していない企業も多いようだが、採用している企業はかなり積極的にESLツールを運用しているようで、Mentor主催のESL Symposiumでの情報によると、2003?2008年の5年間におけるEDAカテゴリ別売上成長率は、首位がDFM(13.3%増)で2位がESL(12.5%増)という話。多数開催されていたESL関連セッションを聴いた限りでは、中でも高位合成(HLS)の利用は確実に広がっている様子で、未だデファクトと言えるHLSは無いが、SynopsysがSynfora買収でHLS市場に再参入した事で、大手3社+老舗HLSベンダによる市場争奪戦は更に激化すると思われる。

TSMCのリファレンス・フローにも現れているように、ESLはEDAソリューションの中で一つの大きなブームと言えるカテゴリとなっており、今回の47DACでも話題の中心に。未だESL手法そのものを採用していない企業も多いようだが、採用している企業はかなり積極的にESLツールを運用しているようで、Mentor主催のESL Symposiumでの情報によると、2003?2008年の5年間におけるEDAカテゴリ別売上成長率は、首位がDFM(13.3%増)で2位がESL(12.5%増)という話。多数開催されていたESL関連セッションを聴いた限りでは、中でも高位合成(HLS)の利用は確実に広がっている様子で、未だデファクトと言えるHLSは無いが、SynopsysがSynfora買収でHLS市場に再参入した事で、大手3社+老舗HLSベンダによる市場争奪戦は更に激化すると思われる。

また、かのESL推進論者Gary Smith氏は、DAC初日のパネル・セッションで今年もESLの重要性を強調。チップの開発コストを引き下げる一つの解としてESLツールの有効性を指摘し、ForteのCynthesizer、CadenceのCtoS、MentorのVista、BluespecのESLツール、Synopsysのバーチャル・プロトタイプ環境などを注目のESLツールとして紹介していた。

※47DAC公式ページ

※47DAC公式ページ

2010.06.11

2010年6月10日、シノプシスは、高位合成ツールベンダSynforaの買収を発表した。

プレスリリース文

買収金額など詳細は明らかにされていないが、シノプシスによるSynforaの買収は完了。

シノプシスは自社のESLソリューションにSynforaの高位合成技術を取り込む事になる。

シノプシスは、Synforaの持つC/C++からの高位合成技術はFPGAプロトタイピング・ソリューションの強化にも繋がるとしており、Synforaの合成からSynplifyを用いたFPGAインプリメントのパスを示している。

シノプシスは買収したシンプリシティのDSP合成ツール「Synplify DSP」の合成技術をベースに開発した高位合成ツール「Synphony」を持っているが、この製品はMatlabのMコードからRTLを自動合成するもの。今回のSynforaの買収によってシノプシスは、Matlabからの合成に加えてC/C++からの合成技術も獲得する事になり、既にC言語からの高位合成ツールを提供しているケイデンス、メンター、フォルテと対峙する事になる。

※日本シノプシス合同会社

2010.06.11

2010年6月10日、シノプシスは、ビラージロジックの買収を発表した。

プレスリリース文

発表によるとビラージロジックが合意した買収価格は3億1500万ドル。ビラージロジックの2009会計年度の売上は約4740万ドルで、直近の2010会計年度Q3(1?3月)の売上は2520万ドルだった。

シノプシスは、今回のビラージロジックの買収により、同社のDesignWare IPポートフォリオの拡張を実現。メモリIPやプロセッサ・コア(旧ARC社)などビラージロジックのIP資産を獲得する。

シノプシスは、今年2月にバーチャル・プロトタイプのVaST社とCoWare社を買収。一部報道によるとSPICEのベンチャーGemini Design Automation社も買収していた。

※日本シノプシス合同会社

2010.06.10

2010年6月10日、ESL合成ツールを手掛けるBluespec社の日本代理店を務めるサイバネットシステムは、富士通がBluespecのESL合成ツールを採用した事を発表した。

プレスリリース文

サイバネットによると、富士通は独立行政法人新エネルギー・産業技術総合開発機構(NEDO)から委託されている「メニーコア・プロセッサ技術の先導研究」において、サーバー向けプロセッサのハードウェア・アーキテクチャの探索・設計にBluespecのESL合成ツールを利用した。

同設計事例の詳細は、7月13日に開催予定の「Bluespec User Group Meeting 2010」にて発表される予定となっている。

富士通 高村 守幸氏 (エンタプライズサーバ本部長付)のコメント:

「32 コア、48 コア、64 コアといったメニーコア・プロセッサのプロセッサ相互結合網を開発する場合、その通信パターンの組み合わせや回路規模はコア数に対応して指数関数的に増加するため、従来のRTL を用いる手法には限界を感じていました。SystemC のような検証用の記述言語を用いて高抽象度の記述から実装までを自動化しても、要求するレイテンシやシリコンサイズの見通しを得ることは困難です。そのような中で、Bluespec は「ほどよい」抽象度を我々に提供してくれました。さらに、メニーコア・プロセッサに限らず民生機器・産業機器用コンピュータのLSI 開発においても、Bluespec の恩恵が期待されます。」

BluespecのESL合成ツール「Bluespec SystemVerilog」は、SystemVerilogベースの独自の拡張言語を入力とするESL合成ツールで、抽象レベルの高い記述からRTLを自動合成するという意味では高位合成ツールに近いが、その思想・設計理念は我が道を行くもので、市場に数ある高位合成ツールとは一線を画す製品となっている。

数年前まで高位合成ツールは「制御回路の合成に不向き」というのが一般的な見方であったが、BluespecのESL合成ツールはいち早くこの固定概念を覆したツールで、制御系の回路もデータパス系の回路も容易に合成できるほか、テストベンチの自動生成機能なども備えている。今年3月にはパナソニックがシステムLSIの上流設計・検証に向けたBluespecの導入を発表しており、C/SystemC系の高位合成とは違った独自路線で着実に実績を重ねている。

※サイバネットシステム株式会社

※Bluespec社

2010.06.09

2010年6月7日、フォーマル検証ツールを手掛ける独OneSpin Solutionsは、同社のアサーションベース検証ツール「360 MV」が4ステートX解析およびX検証をサポートしたことを発表した。

プレスリリース文

ワンスピンによると、今回バージョンアップの機能強化により、未知、未定義または「ドントケア」の信号値(X)とそれら(X)のデザイン内への伝播を網羅的に解析することが可能となり、データの破損やコントロールパスの分断に繋がる(X)の完全な可視化および(X)の伝播の完全なトレースを実現できるという。

同社VP Product MarketingのMichael Siege氏は、「合成前に設計のXに対するロバスト性を確認することができるため、後段のゲートレベルシミュレーションでの手間を削減することができます。」と語っている。

ワンスピンは発表した「360 MV」の新機能(4ステートX解析およびX検証)を来るDAC2010にて公開の予定。

※OneSpin Solutions社

2010.06.09

2010年6月1日、設計初期段階でのアーキテクチャ探索を実現するESLツール「CoFluent Studio」を手掛ける、仏CoFluent社は、「CoFluent Studio」の新機能を発表した。

プレスリリース文

発表によると、CoFluentは予てからロードマップで示していた組込みCコード生成機能を「CoFluent Studio」に実装。UML,SysMLまたは独自グラフィカル言語やMatlab,ANCI-Cなど、多彩な言語からパフォマーンス・シミュレーション用のSystemCを自動生成する「CoFluent Studio」に新たなアウトプットが用意される。

同新機能は、「Cofluent Studio」最新バージョン3.2.1にオプション機能として用意されるもので、正式なリリースは今年のQ3予定。生成されるCコードは、IEEE標準のAPI「POSIX:Portable Operating System Interface」を備えているため、汎用的なLinuxやRTOS上に実装可能。他のAPI向けにカスタマイズする事も容易だという。

これまで「CoFluent Stuio」は、あくまでもシステムレベルのパフォーマンス解析/アーキテクチャ探求ツールという位置付けであったが、今回の組込みCコード生成機能により、組込みソフトウェアの開発ツールとしてターゲット市場を広げる事になる。

※CoFluent Design

2010.06.09

パワー/熱解析の仏DOCEAが製品強化、資金調達、コラボレーションを発表

2010年5月26日、6月2日、6月8日、システムレベルからのパワー/熱解析ソリューションを手掛ける、仏DOCEA Powerは、立て続けに3つのプレス発表を行った。

プレスリリース文(製品バージョンアップ)

プレスリリース文(資金調達)

プレスリリース文(コラボレーション)

発表によるとDOCEAは、パワーの見積りおよび管理を実現する「ACEplorer」とモデリング環境「AcePowerModeler」をそれぞれ機能強化。

新たにハード開発/ソフト開発双方においてパワーモデルが開発出来るようになり、プロジェクト全体を通じて開発したパワーモデルを共有できるプロジェクト管理機能が備わったほか、バーチャル・プラットフォームからVCDファイルを通じてタイム・アキュレートなシナリオをインポート出来るようになり、ソフト開発の初期段階で消費電力を見積もれるようになった。

また、モデリング環境「AcePowerModeler」においては、システムレベルでのパワーモデリング機能の他に、より下位のシミュレーション結果やキャラクタライゼーション・データからパワーモデルを生成できるようになった。これらは、既存資産を用いた設計に対応するためのソリューションとなる。

これら新機能は来るDAC2010にて披露される。

また、DOCEAは、ベンチャー・キャピタルより150万ドルの資金調達に成功したほか、同じフランス勢でESLツールを提供するCoFluent社とシステムレベルのパワー・アーキテクチャ探求に関するコラボレーションを発表。詳細は明らかにされていないが、両社の製品「ACEplorer」と「CoFLuent Studio」が相互運用可能になるようだ。

※DOCEA Power社

2010.06.09

2010年5月25日、新世代RC抽出ツールを手掛ける、Silicon Frontlineは、台湾UMCが同社の3Dフルチップ寄生抽出ツールをリファレンス・ツールとして採用した事を発表した。

プレスリリース文

発表によるとUMCは、Silicon Frontlineの「F3D (Fast 3D)」を同社の40/65nmプロセス向け寄生データ抽出用のリファレンス・ツールとして採用。同製品は昨年5月の市場投入以降、半導体上位25社のうち8社が採用。既に200以上のデザインに利用された実績があるという。

※Silicon Frontline社

2010.06.09

2010年5月19日、フォーマル検証を中心とした検証ソリューションを手掛ける、米Real Intent社は、新製品「Meridian DFT」を発表した。

プレスリリース文

新製品「Meridian™ DFT」は、同社の「Meridian」プロダクトファミリーの新製品で、DFT考慮のRTL設計を実現するもの。同ツールを利用すれば、論理合成前後のRTLに対して、テスタビリティとDFT関連のインプリメンテーションエラーをチェックできる。

具体的には、DFTトレードオフに対して what-if 解析を行い、stuck-at および at-speed tests の ATPGカバレッジを算出。同社のフォーマル検証技術や構造解析、シミュレーション技術がベースとなっており、市販のATPGツールとも連携できるという。

リアルインテントは、来るDAC2010にて新製品「Meridian™ DFT」をお披露目予定。

※リアルインテント社

2010.06.03

2010年6月2日、ハードウェアベースの検証ソリューションを手掛ける仏EVE社は、同社の論理エミュレーション・システム「ZeBu」がOSCI TLM-2.0 をサポートした事を発表した。

プレスリリース文

発表によるとEVEは、「ZeBu」のTLM-2.0トランザクタ・アダプタを用意する事でSystemCモデルの運用を実現。EVEは、これによりSystemCベースの仮想環境とのインテグレーションが可能となり、SystemCとRTLを組み合わせた「高性能ハイブリッド仮想プラットフォーム」が実現できるとしている。

EVEのTLM-2.0トランザクタ・アダプタは、他のEVEのトランザクタIPやZEMI-3で作成されたトランザクタと相互運用可能。OSCI TLM-2.0標準互換で複数のターゲットおよびイニシエータ、ブロッキング/ノン・ブロッキングのトランスポート・インタフェースをサポートしており、モデリング抽象度としては、Loosely Timed (LT)、Loosely Timed Temporal Decoupled (LTD)、Approximately-Timed (AT)に対応しているという。

今回の発表にはシノプシスからもコメントが寄せられている。

Synopsys社 システムレベル・ソリューション・プロダクト・マーケティング担当ディレクター Frank Schirrmeister氏:

「仮想プロトタイプで得られる効率的なデバッグと解析能力によって、開発サイクルの極めて初期の段階からソフトウェア開発者が作業を開始できるようになります。EVE社のZeBuのような高速なRTLエミュレーション環境と弊社がサポートする標準ベースのSystemC TLM-2.0とのインテグレーションによって、Synopsys仮想プロトタイプ製品は、ハードウェア/ソフトウェア協調検証に向けたシステムレベルの可視性の恩恵を拡げられます。」

※日本イヴ株式会社

2010.06.02

2010年6月1日、カスタム設計環境とHDLデバッグ環境を手掛けるSpringSoftは、同社のカスタムIC設計環境「Laker」がTSMCに採用されたことを発表した。

プレスリリース文

発表によるとTSMCは、ミックスドシグナル、メモリ、I/Oデザイン向けに「Laker」を採用。複雑なカスタム回路のレイアウト時間削減を狙う。

当然ながらSpringSoftのカスタムIC設計環境「Laker」は、TSMCのオープンPDK「iPDK」をサポートしており、SpringSoftはその仕様策定にも関わっている。

TSMC社、デザイン・メソドロジおよびサービス・マーケティング担当副ディレクタ、Tom Quan氏のコメント:

「 当社のICデザイン・チームは、今日の非常に厳しいカスタムチップ開発、設計可能性の最前線に立っています。このような多種多様かつ複雑な設計に対応するために、当社は絶えず、設計の障壁を克服する上で役立つLakerレイアウト・システムのようなツールやメソドロジを採用し、当社の設計環境の調整に心を砕いています。」

※株式会社スプリングソフト

2010.06.01

2010年5月25日、ケイデンスとIBMは先端IPの共同開発を発表した。

プレスリリース文

発表によると両社は、32nmでのsilicon-on-insulator (SOI)技術を使用して、DDR PHY、メモリ・コントローラ、PCI Express、EthernetなどのプロトコルIPを開発。その狙いは益々複雑化するネットワークおよび通信分野向けのSoCの統合設計にあり、両社の開発するIPを利用すれば、設計サイドのIPの認定・統合費用を軽減できるという。

今回の両社の協業は先日ケイデンスが発表したEDA360ビジョンを踏襲するもので、その中核をなすIP統合設計環境「Cadence Open Integration Platform」によって実現される。

※日本ケイデンス・デザイン・システムズ社

2010.06.01

SystemC関連の技術セミナーとして世界最大の規模を誇る「SystemC Japan」。

今年はOSCIが主催となり、例年よりも規模を拡大して開催致します。

開催5回目となる今年の「SystemC Japan 2010」では、SystemCユーザーによる設計事例の発表を計6件予定。OSCIによる最新のSystemC動向報告が予定されているほか、恒例のレセプション・パーティーも実施。レセプション・パーティーはセミナー参加者どたなたでも参加可能で、本セミナーのスポンサー企業のソリューション展示をご覧頂けます。

LSI設計における一つの大きなトレンド「ESL設計」を支える業界標準言語「SystemC」。その技術動向や設計における適用例など、「SystemC」の今を知りたい方は是非この機会にセミナーへ足をお運び下さい。

※セミナー開催案内ページ

■セミナー開催概要

会期:2010年7月2日(金)

10:00-17:35(セミナー)、17:50-19:30(パーティー)

会場:新横浜国際ホテル 南館 〒 222-0033 横浜市港北区新横浜 3-18-1

セミナー会場:2F チャーチル、レセプション会場:3F クリスティ

※会場へのアクセス→http://www.khgrp.co.jp/shinyoko/access/index.php

参加:無料(事前登録制) 定員300名 先着順

※当セミナーのお申し込みにあたっては、「お申し込みにともなう個人情報の取扱い」に同意いただく必要がございます

主催: Open SystemC Initiative (OSCI)

メインスポンサー:

日本ケイデンス・デザイン・システムズ社

フォルテ・デザイン・システムズ株式会社

メンター・グラフィックス・ジャパン株式会社

日本シノプシス合同会社

協賛:

アーム株式会社

カリプト・デザイン・システムズ株式会社

コ・フルエント デザイン社

日本イヴ株式会社

株式会社エッチ・ディー・ラボ

日本電気株式会社

株式会社プライムゲート

■セミナー内容

◆10:00-10:30 「OSCI and IEEE Update」

OSCI Treasurer, P1666 Chair&Cadence Group Director

Stan Krolikoski

◆10:30-10:45 「日本におけるSystemCの標準化活動(予定)」

JEITA SystemC Working Group (講演予定)

◆10:45-11:25 「動作合成とバーチャル・プラットフォームの統合に向けて」

株式会社リコー 電子デバイスカンパニー 画像LSI開発センター 設計技術室

シニアスペシャリスト

塚本 泰隆

◆11:25-11:50 「シノプシスが提供する仮想化技術を用いたトータル・ソリューションの紹介」

日本シノプシス合同会社 FCAEグループマネージャ

内田 憲法

◆11:50-12:40 昼食休憩

◆12:40-13:20 「ルネサスエレクトロニクスにおける高位設計適用事例」

ルネサスエレクトロニクス株式会社 FE設計技術開発部

FE設計技術開発第二課 主任技師

野中 義弘

◆13:20-13:45 「ケイデンスのTLM設計・検証ソリューション」

日本ケイデンス・デザイン・システムズ社 マーケティング本部 ディレクター

後藤 謙治

◆13:45-14:25 ※講演調整中(SystemCユーザー設計事例)

◆14:25-15:05 「CoFluent Studioによるハードウェア構成検討」

(アルゴリズムプロファイリング機能とアーキテクチャマッピングの利用)」

日本システムウエア株式会社 プロダクトソリューション事業本部

デバイスソリューション事業部 マネージャー

齊藤 勇吉

◆15:05-15:25 休憩

◆15:25-15:50 「ESL設計メソドロジによる高抽象度最適HW設計と検証手法」

メンター・グラフィックス・ジャパン株式会社

Design Creation and Synthesis Division Business Development Manager

牧野 潔

◆15:50-16:30 「経産省委託研究 画像・動画処理用C 言語のLSI 化の支援システム開発事例」

株式会社プライムゲート 代表取締役社長

梅田 芳直

◆16:30-16:55 「TLMレベルからの動作合成による実現化手法」

フォルテ・デザイン・システムズ株式会社

シニアアプリケーション エンジニア

桜井 至

◆16:55-17:35 「ソニーで成功しているSystemC設計フロー」

ソニー株式会社 CPDG半導体事業本部設計基盤技術部門

システムデザインソリューション部 主任技師

蛯原 均

ソニー株式会社 半導体事業本部 設計基盤技術部門 統括課長

旦木 秀和

◆17:50-19:30 レセプション・パーティー(事前登録制、参加無料、立食パーティー)

スポンサー11社のSystemCソリューションを展示

※セミナー参加者どなたでも参加可能

※19:00より恒例のプレゼント抽選会を行います

※セミナー内容詳細はこちら↓

http://www.systemcjapan.com/SystemCJapan2010/aboutseminar.html

※セミナーお申し込みはこちら↓

http://www.systemcjapan.com/SystemCJapan2010/privacy.html

■■お問い合わせ

SystemC Japan 2010に関するお問い合わせは、下記窓口までお願い致します。

SystemC Japan 2010運営事務局 EDAエクスプレス info@eda-express.com

2010.06.01

2010年5月27日、プロトタイピング・ソリューションを手掛ける、プロトタイピング・ジャパンは、FPGAベースのプロトタイピング・プラットフォームを提供する米BEEcube社と国内代理店契約を締結し、販売を開始したと発表した。

プレスリリース文

BEEcube社の提供するFPGAベースのプロトタイピング・プラットフォーム「BEE3」は、同社とマイクロソフトリサーチ、UCバークレイ大学が共同開発した第3世代のシステムで、その起源はUCバークレーが開発した「BEE(Berkeley Emulation Engine)」にある。

「BEE3」は、ザイリンクスのFPGA「Virtex-5」をベースにした大容量プラットフォームで、1モジュールに4個のFPGAを搭載。用途に応じてフレキシブルに複数モジュール構成に拡張可能で、1モジュール当り消費電力400W以下で4兆回/秒の整数演算を実現する。

特長としては、USB、イーサネット、PCI Express経由して複数のホストコンピュータとのインタフェース及びリモートコントロールが可能な点、MATLAB及びネィティブCAPIと直接統合が可能な点などがあるが、ユニークなのは、MathWorks社のSimulinkフレームワーク上に構築できるシステムレベル・ハードウェア/ソフトウェア協調検証環境「BEEcube Platform Studio(BPS)」を用いる事で、特定のハードウェア・インタフェースや対応するソフトウェア・ドライバを自動生成可能。これにより、例えば複雑なDSPアルゴリズムのプロトタイピングなどが数日で実行可能となる。

また、拡張モジュールとして、アナログ/デジタルコンバータ、HDビデオインタフェースなども用意されている。

BEEcube社は、2010年6月2日よりつくばで開催される、第24回ACM ICS(InternationalConference on Supercomputing)のBronzeスポンサーとして出展予定。6月14日より米アナハイムで開催予定のDAC(Design Automation Conference)にも出展する。

プロトタイピング・ジャパンは、BEEcube社の「BEE3」以外にも、Terasic社のASICプロトタイピングボード「DE4」など複数のプロトタイピング用製品を提供しているが、「BEE3」は同社の製品ラインナップの中心的な製品になると予想される。

※プロトタイピング・ジャパン株式会社

2010.05.31

2010年5月28日、メンター・グラフィックスは、2011会計年度第1四半期(2010年2月-4月)の売上を報告した。

プレスリリース文

発表によると、メンターのQ1(2-4月)売上は、前年比約9%減の1億8060万ドル。前年同時期は、世界不況の中で久しぶりに前年比プラスを記録した四半期だったが、今期は前2010年Q4(11-1月)に続いて前年実績割れとなった。

しかしメンターのCEO Walden C. Rhines氏のコメントによると、例年、年度後半に集中する契約更新の受注は好調で、顧客上位10社の契約更新は前四半期に続いて25%増を達成しているという。

メンターは次期2011会計年度Q2(10年5月-7月)の売上を前年同水準の約1億8000万ドルと予測。2011会計年度全体としては2010年を上回る8億7000万ドルと予測している。

※メンター・グラフィックス・ジャパン株式会社

※メンター・グラフィックス・ジャパン株式会社

2010.05.28

2010年5月27日、マグマは2010会計年度第4四半期(2010年2月-4月)の売上を報告した。

プレスリリース文

発表によるとマグマの2010年Q4(2010年2月4月)売上は、前年同時期比約1.5%減の3360万ドル。2010会計年度の売上合計は、2009会計年度売上合計1億4700万ドルに対して約16%減の1億2310万ドルという結果となった。

売上額だけでみるとマグマの業績が鈍っているように見えるが、財務的には大きく改善されており、2010年Q4の損益は70万ドル(前年比約93%減)、2010年通年の収支は損益330万ドル(前年比97%減)となっている。※GAAP基準による会計結果

マグマは、2011会計年度(2010年5月-11年4月)の売上を1億3000-3300万ドルと予測している。

※マグマ・デザイン・オートメーション株式会社

※マグマ・デザイン・オートメーション株式会社

2010.05.27

2010年5月25日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automation社は、同社の「Analog FastSPICE」の新機能「AFS Multi-Core Parallel (AFS MCP) 動作モード」を発表した。

プレスリリース文

BerkeleyDAによると新機能「AFS MCP」は、最大8コアのシェアードメモリシステム上で、コーナー、スイープ、Monte Carloの繰り返し計算を平行して別個のコアで自動的に実行

する事が可能。シングルコア上で稼働する「Analog Fast SPICE」と比較して8コアで6倍の高速処理が可能で、精度は同一。従来の市販SPICEと比べると25?50倍以上のパフォーマンスを実現できる。

BerkeleyDAは、「AFS MCP」のパフォーマンスを利用すれば、多数のマシンとシミュレーション・ライセンスを必要とするアナログ/RFブロックのキャラクタライズ作業をSPICE 精度で大幅に高速化出来るとしており、1?2本のBDA Tokenライセンスの追加によって、数十のシミュレーションライセンスを使ったサーバーファームをスタンドアロンのマルチコアマシン1台に置き換えることができるとしている。

※Berkeley Design Automation社

2010.05.27

2010年5月26日、メンター・グラフィックスは、マルチコア向け組込みLinuxの提供で米NetLogic Microsystemsと提携した事を発表した。

プレスリリース文

NetLogic Microsystemsはネットワーク専用プロセッサを手かげる半導体ベンダで、今回の提携により、メンターから提供される組込みLinuxソリューションを自社のマルチコア、マルチスレッド・プロセッサのアプリケーション開発に活かす。

メンターは、昨年7月にAndroidおよびLinux関連の組込みソリューションを手掛けるEmbedded Alley社を買収し、AndroidやLinuxといったオープンソース製品と自社の組込みOS「Nucleus」を組み合わせた開発ソリューションを展開。組込みソフトウェア分野への取り組みに力を注いでいる。

尚、メンターとNetLogic Microsystemsの両社は、マルチコア・システム開発のアライアンス「eNsemble Multi-Core Alliance」の設立メンバーとして名を連ねている。

※eNsemble Multi-Core Alliance

※メンター・グラフィックス・ジャパン株式会社

2010.05.27

2010年5月26日、マグマは、ARMがフィジカルIP製品開発向けにマグマのキャラクタライズツール「SiliconSmart」を採用した事を発表した。

プレスリリース文

発表によると、ARMはマグマの「SiliconSmart」を利用することで、フィジカルIP開発におけるスタンダード・セルとI/Oのキャラクタライゼーションおよびモデリングの精度向上を図った。

マグマの「SiliconSmart」は、ライブラリ・キャラクタライズ・ツールの業界標準となっている。

ARM社、デザイン・オートメーション/フィジカルIP部門担当副社長、Brent Dichter氏のコメント:

「当社のプロセスに最適化された高精度かつ高密度なスタンダードセル・ライブラリと多目的かつ専門的なI/Oによって実現した、高品質かつこのフィジカルIPソリューションは、当社のお客様に、厳しい設計条件を満たすことができる高い品質と柔軟性をご提供します。当社のお客様の条件はますます高くなっており、SiliconSmartは当社のスタンダード・セル、I/O製品を迅速にキャラクタライズするために必要な自動化/性能/信頼性を構築する上で役立っています。」

※マグマ・デザイン・オートメーション株式会社

2010.05.27

2010年5月、STARC(?半導体理工学研究センター)は、「TLM入門セミナー」の開催をアナウンスした。

関連ページ

http://www.starc.jp/tlmg/smn/semiguide-j.html

STARCの「TLMセミナー」は、TLM技術の利用普及を目的としたセミナーで、STARCが販売する「TLモデリングガイド」をベースにTLMの基礎を解説するもの。約3時間半のセミナーで下記内容の講義が行われる。

■ 第1章 TLMとは

1. APIを使用するモデリング手法

2. 実行可能な仕様

3. SystemCとTLM

4. 並列プロセス

5. 抽象度

6. 抽象レベルの明確な定義

7. LTとAT

■ 第2章 システム開発の現状とTLMのメリット

1. システム開発の現状

2. 仕様および実装上の問題点

3. TL設計の導入

4. TLMによる設計検証フロー

5. ソフトウエア早期開発-実践例

6. アーキテクチャー設計での成功例

7. パフォーマンス解析

8. 広がるTLMの世界

■ 第3章 ソケットとペイロード

1. ソケット(LT/AT共通)

2. ソケット(種類)

3. ソケット(標準ソケット)

4. 汎用ペイロード

5. 汎用ペイロード (アトリビュートの種類)

6. 汎用ペイロード (アトリビュート・アクセス用のメンバ関数)

7. 汎用ペイロード (データポインタ)

8. 汎用ペイロード (データ長)

9. 汎用ペイロード (データ転送例 : unsigned char -> unsigned char)

10. 汎用ペイロード (バイトイネーブル)

11. 汎用ペイロード (ストリーミング幅)

12. 汎用ペイロード (応答ステータス)

■ 第4章 ターゲットモデルの記述方法

1. バブルソートのアルゴリズム

2. バブルソートの全体像

3. モデル作成の流れ

4. ハードを意識した記述への変更

5. リソースの検討

6. レジスタとアクセス関数の定義

7. Cソースコードの修正

8. C++への変更

9. TLMモデルの記述方法

10. イニシエータ記述例

11. ターゲット記述例

12. 遅延の記述方法

13. 同期LT

14. タイミングアノテーション

15. テンポラルデカップリング

第一回目の開催は6月18日、大阪で開催される展示会「Embedded Technology WEST2010」に合わせて行われる予定で、秋口には関東でも開催を計画中。参加費はなんと無料である。

※株式会社半導体理工学研究センター

2010.05.27

2010年5月26日、マスクデータ処理ソリューションを手掛ける、仏XYALIS社は、2つの新ツールを発表した。

プレスリリース文

発表によるとXYALISが開発したのは、先端プロセスをサポートするマスク・セットの自動生成ツールとマルチ・プロジェクト・ウエハー向けの配置エンジンで、いずれもマスク設計におけるコスト削減を狙うもの。

マスク・セットの自動生成ツールはマルチ・チップ・マスクを含めあらゆる種類のマスク生成に対応しており、数分間でマスク・セットを自動生成する事が可能。人手を介さず人的エラーの混入も防止できる。

マルチ・プロジェクト・ウエハー向けの配置エンジンは、製造コストや生産量、パッケージングの情報などの生産条件を考慮し、最も費用対効果の高い配置を実現。同社の提供するマルチ・プロジェクト・ウエハーのアッセンブリ・ツールに搭載される。

XYALISはこれら2つの新ソリューションを来る47thDACで披露する予定。

※XYALIS社

2010.05.21

LSI設計のエンジニアリング支援ツールを手掛ける日本のベンチャー、マイクロアークは、設計データの配置配線リスクを診断するクラウドサービス「ChipNavi(チップナビ:http://chipnavi.com/)」の試験運用を開始した。

参考ページ

マイクロアークによると「ChipNavi」は、ネットリストと最小限のライブラリ(LEF、Liberty)を基にインプリメントにおけるリスク要因を診断するもので、具体的には、クラウド環境上に用意された簡易フィジカルプロトタイピングツールを用いて、ユーザー自ら作成した評価データから配置配線イメージを作成。その結果からタイミング制約、配線難易度、テストカバレッジなど、フィジカル・インプリメントに関するリスクファクターを評価し、診断表として各評価項目についての診断コメント(問題点や次に取るべき対応策など)レポートする。

クラウド環境の利用にあたっては、Googleアプリケーションと同じセキュリティ、プライバシー、データ保護ポリシーが適用されており、利用者はGoogleアカウントを用いてサービスを利用可能。当然ながら、利用者のネットリストやライブラリなどの情報がクラウド環境に直接アップロードされる事は無い。

「ChipNavi」のユニークなところは、Webベースのクラウド環境を利用している事もさることながら、ネットリスト、LEF、Libertyのみで短時間で配置配線イメージを入手し、チップ面積を算出できる点で、サービスの利用にあたりフィジカル・インプリメンテーションに関する細かい知識は一切不要。接続関係の矛盾やモジュールの不存在が生じている未完成のネットリストであっても評価できる。

マイクロアークのビジネスモデルは、「ChipNavi」による診断サービスを無償提供する事で物理設計における設計現場の早期リスク認識に貢献し、認識したリスク・課題の解消に向けて、より詳細なデザイン検討が可能なデスクトップ型のツール「MaEPL」を有償提供するという形をとる。

ちなみにマイクロアークでは、「MaEPL」に関しても一部機能制限付の無償版をWeb上で配布しており、全機能が利用可能なライセンス版は30日間限定で無償評価できる。

※マイクロアーク株式会社

2010.05.20

2010年5月11日、EDA関連の標準化推進機関米Si2(Silicon Integration Initiative)は、「OpenPDK Coalition」を発足。その創設メンバーを発表した。

プレスリリース文

「OpenPDK Coalition」の創設メンバーは、下記計10社で、22nmプロセス以降の各テクノロジ・ノードに対応する、EDAツールおよびファウンドリ非依存のオープンなPDK(process design kit)標準の策定を目指す。

・AnaGlobe Technology

・Cadence Design Systems

・IBM

・Intel Corporation

・Mentor Graphics

・NXP

・Pulsic

・SpringSoft

・STMicroelectronics

・Synopsys

オープンなPDKの普及推進では、IPL(Interoperable PDK Library)Allianceという企業連合も存在しており、独自に策定したオープンなPDK仕様「IPL 1.0」を公開しているが、そのベースとなっているのはSi2のPDK規格で、あくまでも業界横断的なPDKの「標準化」を目指すSi2の活動に対して、IPL Allianceの活動はファウンドリ最大手のTSMCを中心とした企業連合と見て取れる。

※Silicon Integration Initiative

2010.05.20

2010年5月19日、シノプシスは、2010会計年度第2四半期(10年2月-4月)の売上を報告した。

プレスリリース文

発表によると、シノプシスの2010会計年度Q2の売上は、前年同時期の3億3680万ドルより130万ドル増の3億3810万ドル。収支は3950万ドルの黒字だった。前期、前々期と2四半期連続で前年割れを記録していたが、今期は前年と同水準を維持した。(※GAAP基準による会計結果)

シノプシスは、次期2010年Q3(10年5月-7月)の売上額を3億3000-3800万ドルと予測している。

※シノプシス株価推移

※シノプシス株価推移

※日本シノプシス合同会社

2010.05.18

2010年5月11日、マグマは、同社のアナログ設計環境「Titan」が、90nmプロセスをターゲットとしたオープンPDKのリファレンス「IPL 1.0」をサポートした事を発表した。

プレスリリース文

「IPL 1.0」は、IPL(Interoperable PDK Libraries) Allianceによって策定されたオープンなPDK仕様で、EDAツールを問わずに利用できるプロセス・デザイン・キットの普及を目的に作られたもの。

今回マグマは、IPL Allianceと協力して「Titan」を評価。「Titan」が「IPL 1.0」の互換性および精度条件を満たしているという認証を受けた。これにより、「IPL 1.0」準拠のiPDKであれば一定の品質基準の下で安心して「Titan」上で利用できる。

発表によるとマグマは、iPDKの導入・開発で先行するTSMCと既に65nm iPDKに対する「Titan」の認証で協力中。「Titan」は65nm/45nmプロセスをターゲットとする「IPL 2.0」もサポートしているようだ。

※マグマ・デザイン・オートメーション株式会社

2010.05.18

2010年5月10日、マグマは、同社の提供する業界標準キャラクタライゼーション・ツール「SiliconSmart」の新機能「SiliconSmart ACE」メモリ・キャラクタライゼーションを発表した。

プレスリリース文

マグマによると、「SiliconSmart ACE」メモリ・キャラクタライゼーションは、メモリ向けのキャラクタライズ機能で、同社の「SiliconSmart」に超高速SPICE「FineSim Pro」シミュレータと特許のメモリ回路向け最適化技術を組み込む事によって実現されている。

この新機能を利用することで、メモリ・インスタンスのタイミング/パワー/ノイズのキャラクタライゼーションを高速かつ高精度に行うことが可能。一般的にスタンダード・セルよりも複雑とされるメモリのキャラクタライゼーションを容易に実行できるという。

※マグマ・デザイン・オートメーション株式会社

2010.05.17

2010年5月17日、ケイデンスは、設計および検証IPソリューションを手掛けるデナリソフトウエアの買収を発表した。

プレスリリース文

発表によるとケイデンスとデナリは、ケイデンスがおよそ3億1500万ドルでデナリを買収し、両社を合併することで合意。今回の買収は現金で行われるようで、デナリは、合併合意時点で4500万ドルの現金を保有。ケイデンス今回の買収を先頃発表した経営戦略「EDA360」に則したものとしており、デナリの買収によって2011年度の一株当たり利益が増加すると予想している。

デナリは、メモリおよび各種標準インタフェースの設計/検証IPの提供で業界をリードしてきた企業で、業界売上トップ10に入る中堅ベンダとして、業界大手を相手にIPソリューション分野で凌ぎを削っていた。ケイデンスがデナリを買収することで、IP分野における業界大手の競争が更に加速され、市場規模もより早いペースで拡大する事が予想される。

※日本ケイデンス・デザイン・システムズ社

※デナリソフトウエア株式会社

2010.05.07

2010年5月6日、メンター・グラフィックスは、同社のエミュレーター「Veloce」が検証メソドロジOVM(Open Verification Methodology)をフルサポートした事を発表した。

プレスリリース文

発表によるとメンターは、「Veloce」向けに開発したトランザクション・ベース・シミュレーションの高速化ツール「TestBench XPress」を用いる事で、OVM準拠のシミュレーション・テストベンチを「Veloce」上で再利用する手法を実現。設計者は、シミュレーション用に用意したOVMテストベンチを手を加える事無くそのまま「Veloce」で利用できるようになる。

OVMはテストベンチの再利用という面でも大きな利用メリットが有り、機能検証工程の大半を占めるテストベンチの作成工数を削減する事ができる。このOVMの利点と「Veloce」の高速化能力が結びつく事で、エミュレーターを用いた検証効率が格段に向上するのは言うまでも無く、設計者はシミュレーション用に作成したOVMテストベンチを用いて、最大でシミュレーターの400倍のスピードでトランザクション・ベース・シミュレーションを実行可能。5時間のビデオ・フレームのシミュレーションが「Veloce」上で30秒で完了するという。

OVMベースの検証手法は、メンター、ケイデンスの両社が先頭に立って推し進めており、国内でも利用事例の発表が増えつつある。教科書としては、昨年7月にメンターのMark Glasser氏による著書「OVM Cookbook」が出版されているが、メンターの立ち上げたオンライン・アカデミー「Verification Academy」に行けば、同書のPDF版や無償のOVMキットなどを入手できる。

※Verification Academy

※メンター・グラフィックス・ジャパン株式会社

2010.05.06

2010年5月6日、新興EDAベンダの米NextOp社は、同社初のEDA製品「BugScope」のリリースを発表した。

プレスリリース文

NextOpによると「BugScope」は、RTLのデザインとテストベンチから機能検証用のアサーションと機能カバレッジのプロパティを自動生成するツールで、SVA,PSLおよび合成可能なVerilog記述として出力。生成されたアサーションとプロパティは、既存の検証フロー上(サードパーティのシミュレーター、エミュレーター、フォーマル検証ツール)で利用する事ができる。

NextOpは、「BugScope」を利用する事で機能検証上の作業として一つの障壁であったアサーションおよびプロパティを記述する手間を省くと同時に、検証品質も向上できるとしており、「BugScope」を用いたアサーション・ベース検証によって既存の検証手法の限界を克服出来ると主張。実際に、早くもAltera, Entropic, Nvidia,の大手半導体3社が「BugScope」を導入済みという事で、各社の検証メソドロジの中に「BugScope」が取り込まれているという。

NextOpは、「BugScope」を利用する事で機能検証上の作業として一つの障壁であったアサーションおよびプロパティを記述する手間を省くと同時に、検証品質も向上できるとしており、「BugScope」を用いたアサーション・ベース検証によって既存の検証手法の限界を克服出来ると主張。実際に、早くもAltera, Entropic, Nvidia,の大手半導体3社が「BugScope」を導入済みという事で、各社の検証メソドロジの中に「BugScope」が取り込まれているという。

尚、NextOpのコア・メンバーは中国系エンジニアで、CEOのDr. Yunshan Zhu氏は元シノプシスAdvanced Technology Groupのメンバー。CTOのDr. Yuan Luは、元ブロードコムのエンタープライズ・スイッチング部門Principle Scientistという肩書きを持つ。共同創設者には、フォルテのCTOであるDr.John Sanguinetti氏、元Simplex創設者のDr. David Overhauser氏、カーネギーメロン大学のDr. Randy Bryant氏、Dr. Edmund Clarke氏らが名を連ねている。

NextOp社は昨年のDACにデモスイートのみの形で出展。当時は未だステルスモードで製品の詳細は明らかにしていなかったが、同社のブースには日本企業のエンジニアも多数出入りしており、NextOpの名は密かに話題となっていた。

※NextOp社

2010.05.06

2010年5月4日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automation社は、台湾の半導体メーカーSunplus Technologyが同社の回路シミュレーター「Analog FastSPICE」を中心とする「Analog FastSPICEプラットフォーム」採用した事を発表した。

プレスリリース文

バークレーの発表によると、コンシューマエレクトロニクス向け半導体ベンダSunplus Technologyは、アナログおよびミックスシグナルIC の設計検証およびデバイスノイズ解析向けに「Analog FastSPICEプラットフォーム」を導入。

同社では既に2008年から「Analog FastSPICE」を導入しており、アナログおよびミックスシグナルIC の複雑なブロックのキャラクタライゼーションや、回路全体のパフォーマンスシミュレーションで実績があり、既存手法よりも5?10倍高速なシミュレーションを実現している。

Sunplus Technologyは、これら実績をうけて、バークレーのソリューションをデバイスノイズ解析の様々な課題に幅広く適用すべく、「Analog FastSPICEプラットフォーム」の導入を決めた。

「Analog FastSPICEプラットフォーム」には、「Analog FastSPICE」のほかに、「AFS Nano」、「AFS Co-Simulation」、「AFS Transient Noise Analysis」、「AFS RF Analysis」のライセンスが含まれている。

※Berkeley Design Automation社

2010.05.06

2010年5月5日、ビラージロジックは2010会計年度第2四半期(10年1月-3月)の売上を報告した。

プレスリリース文

ビラージロジックのQ2(2010年1-3月)の売上は、前年同時期より約129%増、前Q4より約16%増の2520万ドルという好結果を残した。ビラージロジックは、前Q1(2009年10-12月)も前年比92%という好結果を記録しており、2四半期連続で大幅な売上アップとなった(※GAAP基準による会計結果)

ビラージによると、Q2売上はライセンスの売上が前年同時期の倍以上、ロイヤリティ収入は前年同時期よりも3倍以上という内容だった。

ビラージは、次期Q3(2010年4-6月)の売上を今期を上回る2600-2700万ドルと予測している。

※ビラージロジック株式会社

※ビラージロジック株式会社

2010.05.06

2010年5月6日、メンター・グラフィックスは、新製品「Calibre® InRoute」設計検証プラットフォームを発表した。

プレスリリース文

メンターによると新製品「Calibre® InRoute」は、物理検証ツール「Calibre」と配置配線ツール「Olympus-SoC」を統合し、DFMを考慮した物理設計フローを実現するツールで、「Olympus-SoC」から「Calibre」を起動し、デザインのDRC違反を自動的に検出・修正することが可能。MCMM(マルチコーナー/マルチモード)ベースの解析および最適化を実施し、面積、タイミング、消費電力およびシグナル・インテグリティを自動的に最適化することが出来る。

「Calibre® InRoute」は、配置配線ツールと物理検証ツールを分けて利用する事によって生まれる、レイアウトの品質的な問題と工数的な問題を合わせて解消するもので、設計者は同ツールを利用すれば、配置配線ツール上で製造性も考慮に入れたデザイン・クロージャを実現出来る。

※メンター・グラフィックス・ジャパン株式会社

2010.05.06

2010年5月5日、マグマは、アナログ設計者に向けた教育プログラム「Titan Up!」の開始を発表した。

プレスリリース文

マグマによると「Titan Up!」は、アナログ設計者に対し、アナログ/ミックスド・シグナル設計の最新技術を教育するためのもので、マグマのアナログ設計ソリューション「Titan」ファミリ製品をベースに、デザイン探索、設計自動化、再利用など、これまで困難だったアナログ設計における課題への対処法を解説する。

教育プログラムは、Web上で配布されるクイズをベースに進められ、無償の「Titan」トライアル・バージョンも用意される。なた、ツールと合わせて再利用可能なアナログのライブラリも提供され、それらを用いたアナログ回路の設計を体験出来る。クイズはステップ毎に複数用意されているようで、正解者を対象に毎週アップルの「iTouch」が抽選でプレゼントされるという。

クイズのダンロードは既に開始されており6月21日まで続けられる予定。「Titan」の無償トライアル・バージョンのダウンロードは6月より開始される予定となっている。

※「Titan Up!」紹介ページ

※マグマ・デザイン・オートメーション株式会社

2010.05.06

2010年5月3日、ザイリンクスは、自社のFPGA専用開発環境「ISE」のバージョン12を発表した。

プレスリリース文

発表によると、新たなISEバージョン12には、ダイナミック・パワーの削減を狙った新機能「'intelligent' clock-gating technology」が搭載されており、同機能を利用すればツールがデザイン中に自動的にクロック・イネーブル回路を挿入。クッロク・ゲーティングによってダイナミックな消費電力を約30%削減できるという。

自動的なクロック・ゲーティング化による消費電力削減を実現するツールとしては、カリプト社の「PowerPro CG」があるが、FPGAベンダの専用環境にこのような機能が取り込まれるのは業界初となる。

また、ISEバージョン12では、Virtex-6およびSpartan-6の両製品ファミリがサポートされているほか、AMBA 4 AXI4-compliant IPも新たにサポートされた。更に、部分的なコンフィギュレーションを行うための新たなGUIも用意されたという。

※ザイリンクス株式会社

2010.05.06

2010年5月5日、シノプシスは、配置配線ツール「IC Compiler」の最新バージョン2010.03のリリースを発表した。

プレスリリース文

発表によると「IC Compiler 2010.03」では、フロアプランの生成機能や配線探索、MCMM(マルチコーナー/マルチモード)解析など、包括的なエンハンスにより個別機能の処理速度を2?3倍高速化。その結果、従来バージョンをベースとしたテープアウト・フローと比較してフロー全体で3倍以上の処理の高速化を実現した。

また、新たにリーク電流の最適化エンジンが用意され、「PrimeTime」と共に消費電力の削減が可能となったほか、「PrimeRail」と連動したダイナミックIRドロップ解析や「IC Validator」と連動したDRCエラーの自動デバッグ・修正機能なども強化され、周辺ツールとの連携がより緊密かつ効果的なものとなった。これはシノプシスの推し進める「分断されない」デザイン・フローを実現する「In-Design Technology」が更に進化したと言える。

尚、「IC Compiler 2010.03」は、大手ファウンドリの28および32nmプロセスのデザイン・ルールをサポートしており、既に先行顧客によるテープアウトが進行中だという。

※日本シノプシス株式会社

2010.05.05

2010年5月3日、シノプシスは、DesignWareの新製品「MIPI 4G DigRF Master Controller IP」のリリースを発表した。

プレスリリース文

シノプシスによると今回発表した「MIPI 4G DigRF Master Controller IP」は、MIPI DigRF v4 1.00仕様に準拠した設計用IPで、DigRF v4インタフェースのインプリメントを加速するもの。これを利用すればLTEたWiMAX向けSoCの開発を加速出来る。

シノプシスは、MIPI DigRF v4 interfaceのD- PHY IPも並行して開発中で、既にリリース済でシリコン実績のある「MIPI DigRF v3」IP製品と合わせてDigRF関連IPを包括的にカバーする。

※日本シノプシス合同会社

2010.05.04

2010年5月3日、米SIA(Semiconductor Industry Association)は、2010年3月の世界半導体売上高を発表した。

プレスリリース文

SIAの報告によると、2010年3月の世界半導体売上高は230億6000万ドルで前年同時期の145億7000万ドルに対して58.3%増。2010年2月の売上に対しては4.6%増という統計結果となった。

2009年の1月-3月は、世界的な経済不況の影響で半導体売上もドン底に陥ったが、この1年で市場は安定を取り戻し、今回発表された2010年3月の世界半導体売上総額は、2007年11月の最高記録の次に位置する好結果となっている。

※SIA

※SIA

2010.05.03

2010年4月28日、WebベースのIPベース設計ソリューションを手掛ける、米Parallel Engines社は、FPGA設計向けのIP検索サイト「FPGAIPDirectory」の開設を発表した。

プレスリリース文

Parallel Enginesによると、「FPGAIPDirectory」上には300社以上のIPおよびFPGAベンダから集めた、ソフトIP、ハードIP、検証IPならびにFPGAやストラクチャードASICの製品情報が4000件以上カテゴリ別に分類・登録されており、そのインデックス数は17000以上。だれもが無料でサイトにアクセスし、製品情報の検索サービスを利用することが可能で、費用を払えばIPのメタ情報(Soft-IP BRAM, LUT, embedded IP, Power Information, Performance Data (DMIPS), I/O Interfaces, standards, usage guides )、FPGAコンフィギュレーションなどを入手することができる。

また、Parallel Enginesでは、未だベータ版の状態だが、「FpgaRFQ (standing for FPGA Request-for-Quote)」と呼ぶ、デザインの仕様検討システムを開発しており、最終的にこのシステムを利用することで、FPGAと各種標準インタフェース、IPを組み合わせたデザインの仕様検討を行い、そこから実設計へ落としこんでいく設計スタイルの確立を目指している。

尚、Parallel Enginesは、今年3月に設立されたベンチャーでCEOはGeorge Janac氏。George Janac氏は同じくWebベースのIPベース設計ソリューションを提供する「Chip Estimate」(2008年にケイデンスが買収)を立ち上げた人物で、今回のParallel EnginesではFPGAをターゲットとしたIPベース設計向けEDAソリューションの提供を目指しているようだ。

※Parallel Engines社

2010.04.30

2010年4月28日、ケイデンスは2010会計年度Q1(10年1-3月)の売上を報告した。

プレスリリース文

ケイデンスの2010年Q1(1-3月)の売上は、前年同時期比約7.7%増、直前のQ4(09年10-12月)と比較して約1%増の2億2200万ドル。収支は1200万ドルの損益という結果だが、その損益額は昨年同時期の5分の1以下に抑えた。(※GAAP基準による会計結果)

ケイデンスによると市場としては北米およびアジア地域の売上が好調。製品分野では検証関連およびデジタル/カスタム設計関連が好調だという。

ケイデンスは次期2010年Q2の売上を2億1500-2500万ドルと予測。2010年通年の売上予測は8億6500万-9億ドルと前期時と特に変更は無い。

尚、ケイデンスは先頃「EDA360」と称する新たな経営ビジョンを示し、変化の必要性を強調。業界内で話題となっている。

※ケイデンス株価推移

※ケイデンス株価推移

※日本ケイデンス・デザイン・システムズ社

2010.04.29

2010年4月28日、ザイリンクスは2010会計年度第4四半期(10年1-3月)の売上を報告した。

プレスリリース文

ザイリンクスの2010会計年度Q4 (10年1-3月) の売上は、前年比34%増、前期(Q3)比3%増の5億2900万ドルで、前Q3に続いて四半期売上の最高記録を塗り替える好結果になった。純利益は前年同時期のほぼ倍の1億4850万ドルで、前Q3比約4割増だった。

ザイリンクスの2010会計年度の売上合計は18億3000万ドルで、2009会計年度の結果とほぼ同額。純利益は僅か1%減の3億7500万ドルだった。

売上の内訳としては、ニュープロダクトに分類される65nmFPGA「Virtex-5」の売上が最も多く、昨年よりも倍増。今後はより高性能かつ低消費電力を実現する40nmFPGA「Virtex-6」および「Spartan-6」の両新製品ファミリで攻勢をかけていく。

地域別の売上でみると日本市場売上は前年比35%増。ヨーロッパは前年比48%増と大きく売上を伸ばした。しかし、市場規模でみると日本市場の売上はザイリンクス全売上の僅か8%で、ここ最近の傾向としては北米・日本における売上が減り、ヨーロッパ・アジアの売上が伸びている。マーケット別では通信分野における売上が全体の47%と大きなウェイトを占めている。

ザイリンクスは、2011年度も成長は継続し5?9%の売上増を見込んでいる。

※ザイリンクス株価推移

※ザイリンクス株価推移

※ザイリンクス株式会社

2010.04.28

2010年4月28日、ケイデンスは、「EDA360」と呼ぶ半導体業界に対する新しいビジョンを発表した。

プレスリリース文

発表された「EDA360」は、ケイデンスの今後のビジネス戦略の青写真となるもので、キーワードの一つとして「system realization(システムの実現)」が謳われている。これは、半導体業界に対し、変化しつつあるセットメーカーからのアプリケーションの要求に応えるためには、新たなエコシステムが必要だと訴えるもので、「system realization(システムの実現)」の第一歩として、WindRiver社との技術的な協業を発表している。

WindRiverとの協業は、ケイデンスの「Incisive Software Extensions」とWind Riverの仮想開発環境「Simics」の統合を狙いとしたもので、WindRiverに買収された「Simics」の開発元Virtutech社とケイデンスが以前より進めていたもの。両社のソリューションが統合されることで、仮想プラットフォームを用いたハード/ソフトの先行開発に加え、OVM(Open Verification Methodology)のシステムレベル適用や「Incisive」の検証マネジメント機能や検証プランを用いた仮想プラットフォーム・ベースの機能検証が可能となる。

ケイデンスとしては、アプリケーション主導の開発手法を提供すべく、ソフトウェア開発に対するアプローチの一つとしてWindRiverとの協業を拡張。時代の変化に対応する新たなエコシステムの構築に向けて、新たな設計ソリューションの展開を進めていくという事のようだ。

※日本ケイデンス・デザイン・システムズ社

2010.04.28

2010年4月28日、ザイリンクスは、ARM Cortex-A9 MPCoreベースの新FPGAプラットフォーム「ザイリンクス エクステンシブル プロセッシング プラットフォーム」を発表した。

プレスリリース文

今回発表されたザイリンクスのARM Cortex-A9 MPCoreベースのプラットフォームは、最高800MHzで動作するデュアルコア・プロセッサと業界最高峰の性能を実現する28nmFPGAの組み合わせによって、性能要求が高まる一途の各種アプリケーション・システムの性能向上を効率的かつ容易に実現するもので、プロセッサとプログラマブル・ロジックが「AMBA-AXI」バスによって繋がっているところが特徴。これにより、一般的なコ・プロセッサ手法で起こりがちなI/Oボトルネックを回避する事が可能となり、プロセッサ-プログラマブル・ロジック間の機能トレードオフも容易となる。

また、ザイリンクスは、FPGAを用いたシステム性能の向上を促進すべく、従来から力を入れているCコードからのFPGA合成ツールを利用するためのインフラ整備を強化。ポピュラーなCtoFPGAツールへのオープンサポートを備えたGNUベースのコンパイラ、デバッガ、ドライバ類を独自に提供していく計画だという。

また、ザイリンクスは、FPGAを用いたシステム性能の向上を促進すべく、従来から力を入れているCコードからのFPGA合成ツールを利用するためのインフラ整備を強化。ポピュラーなCtoFPGAツールへのオープンサポートを備えたGNUベースのコンパイラ、デバッガ、ドライバ類を独自に提供していく計画だという。

ザイリンクス エクステンシブル プロセッシング プラットフォームを用いた新製品の詳細は、2011年中頃に明らかにされる予定で、製品化され利用できるまでには少々時間がかかりそうだ。

※ザイリンクス株式会社

2010.04.28

2010年4月26日、高周波IC設計環境「Microwave Office」を手掛ける米AWRは、13期連続で売上増を達成したことを発表した。

プレスリリース文

発表によるとAWRは、2010年3月末決算の2010年度売上が過去最高を記録。13期連続で売上増を達成した。また、同社は業績の拡大に伴い従業員数も増やし韓国にも拠点を設立。電磁界解析ツール「AXIEM」が好調な他、軍事/宇宙航空、防衛産業の顧客が不景気により設計環境の見直しを進めたことが同社への追い風になったという。

※AWR社

2010.04.28

2010年4月27日、アームは、2010会計年度第1四半期(2010年1-3月)の売上を報告した。

プレスリリース文

アームの2010会計年度Q1 (2010年1-3月) の売上は、前年比19%増、前Q4比2%増の1億4330万ドル。ユニット出荷数は四半期で過去最高を記録し、ロイアリティ収益の記録も伸ばした。

アームはスマートフォンを中心に前年比50%増のペースで携帯電話市場での好調が続いており、今後はモバイル・コンピューター市場も動き出すとみている。また、モバイル市場以外のインテリジェント・センサー、ネットワーキング、スマート・メーターといった分野でも着々と契約を増やしているようだ。

つい先日、アップルがアームを買収するかもしれないという噂がロンドンから流れ出し、様々な物議を巻き起こしているが、成長を続けるアームの企業価値は7000億とも8000億とも言われている。

※アーム株価推移

※アーム株価推移

※アーム株式会社