NEWS

2011.05.18

2011年5月17日、オープンコアプロトコル(OCP)の普及団体OCP-IPは、OCPコンプライアンスチェックの最新版のリリースを発表した。

機能チェックとアサーションから成る最新のコンプライアンスチェックは、OCPインタフェースの最新バージョン「OCP 3.0」に対応するもので、システムレベルからコンプライアンスチェックを実現。ユーザーはフォーマル検証やプロトコル・チェッカーの構築などで利用する事ができる。

最新のコンプライアンスチェックは、現在のところスポンサー・メンバーのみに限定的に提供中。OCPの次期バージョンに対応するコンプライアンスチェックの開発も進められているという。

2011.05.17

2011年5月16日、FPGAプロトタイピング向けの検証ソリューションを手掛けるInPA Systemsは、FPGAプロトタイピング・ボード・メーカーS2Cとのコラボレーションを発表した。

発表によると、両社のコラボレーションによるFPGAプロトタイピングのデバッグ・ソリューションは、現在のところβ版で今年Q3(7-9月)に正式リリースされる予定。InPAは同ソリューションのデモを5/24上海、5/26北京で開催予定の「SoCIP 2011 Conference」と6/5からSanDiegoで開催予定の第48回DACで展示する。

複数FPGAを搭載した大規模FPGAプロトタイピング・ボードのデバッグを行なうにあたりInPAは、S2Cのボードに備えられたI/Oコネクタを利用して信号やFPGAコントローラーにアクセスし自社の可視化技術「Active Debug」を応用。現在のところ、S2Cの提供するVirtex-6搭載のプロトタイピング・ボード

「V6 TAI Logic Module」にてこのソリューションを利用できる。

2011.05.17

2011年5月16日、業界標準ツール「SpyGlass」をはじめとしたRTL解析ソリューションを手掛ける米Atrenta社は、同社の「SpyGlass」ファミリ製品の一斉バージョンアップを発表した。

Atrentaによって今回発表された主な製品のバージョンアップは以下の通り。

・RTL解析ツール「SpyGlass」:

-Tclコマンドライン・インタフェースを用意

-デバッグ機能を強化(抽象化および「シナリオ」コンセプトの導入)

・CDC解析ツール「SpyGlass CDC」:

-CDC問題だけをピンポイントで指摘可能な構造的なCDC解析機能を追加

・設計制約検証ツール「SpyGlass Constraints」:

-デザイン制約の解析処理を高速化。パフォーマンスが向上。フォルス・パスの特定も高速化。

・DFT解析ツール「SpyGlass DFT」および「SpyGlass DFT DSM」:

- DFTデバッグ機能を強化(IEEE 1149.1および1500セットアップ・シーケンスの検証)

-パワー記述フォーマットCPFおよびUPFのサポート

・メモリBIST自動挿入ツール「SpyGlass MBIST」:

-TclベースのメモリBIST挿入フローをサポート

・ローパワー設計ツール「SpyGlass Power」:

-パワー記述フォーマットCPFおよびUPFのサポート

Atrentaはここ最近、「SoC Realization」という新たな企業コンセプトを打ち出し、「SpyGlass」ファミリをベースとした包括的なソリューションで、IPベースSoC設計の効率的なインプリメントを目指すと積極的にアピールしている。

2011.05.16

2011年5月16日、フォーマル検証ツールを手掛ける独OneSpin Solutionは、ルネサス エレクトロニクスが同社のフォーマル検証ツール「OneSpin 360MV」を採用した事を発表した。

発表によるとルネサス エレクトロニクスは、MCUプラットフォーム向けの機能検証環境を構築するにあたり、OneSpinのフォーマル検証ツール「360MV」と合わせて提供される「オペレーショナルABV」と呼ばれるライブラリを採用した。

「オペレーショナルABV」は、タイミング・ダイアグラム全体を単一のアサーションで記述するためのSVAライブラリで、ルネサス エレクトロニクスでは同ライブラリとフォーマル検証ツール「360MV」を組み合わせて利用する事で、プラットフォーム開発における製品展開時の動作確認を素早く実施したいというニーズを満たした。

実際に「360MV」をベースに構築された検証環境は、MCUプラットフォームの動作確認において論理シミュレーションベースの検証環境よりも50倍高速であることが実証されており、MCUプラットフォームを構成する各機能ブロック間の接続確認(バストランザクションなど)をチップレベルで従来手法よりも短期間に実施することが可能になったという。

OneSpinによると、「オペレーショナルABV」を利用する事でアサーションの開発をよりシンプルに効率化する事が可能で、わずか1日のトレーニングを受けるだけで、エンジニアはタイミング・ダイアグラム全体のアサーションを直感的かつ簡潔に記述することができるようになるという事だ。

2011.05.16

2011年5月16日、プロセッサ開発システム「ASIP Meister」を手掛ける国内のEDAベンチャーエイシップ・ソリューションズは、「ASIP Meister」のオプション製品「テストベンチ・ジェネレータ」のリリースを発表した。

発表によると新オプション機能「テストベンチ・ジェネレータ」は、「ASIP Meister」で作成されたプロセッサの設計データを基にプロセッサ記述の単体テストに使用するテストベンチを自動生成する事が可能。合わせて、ユーザが作成するテンプレートからテストプログラムを自動生成する事もできる。

自動生成されるテストベンチは現行バージョンではVHDLとなるが、今後Verilog-HDL、SystemCの生成にも対応する予定。テストプログラムの自動生成機能では、専用言語のテンプレートをベースに様々なパラメータを与え、単一のテストシナリオから複数のテストプログラムを自動生成する事が可能となっている。

現在ASIPではこの新機能の評価版を提供中。6月から年間ライセンス105万円(税込)にて販売を開始する。

※ASIP Meisterオプション機能「テストベンチ・ジェネレータ」の詳細は

こちら

2011.05.13

2011年5月11日、Synopsysは、中国オーディオ標準規格「DRA」に対応したソフトウェアIP「DesignWare ARC Sound DRAデコーダ」のリリースを発表した。

「DRA(Dynamic Resolution Adaption)」は中国独自のオーディオ規格で、Chinese National HD(High-Definition)オーディオ標準規格として、中国国内コンスーマ・エレクトロニクス製品で利用されている。

今回SynopsysがリリースしたソフトウェアIP「DesignWare ARC Sound DRAデコーダ」は、同標準規格に対応する業界初のソフトウェアIPで、同社の提供するオーディオIP「DesignWare ARC Sound AS211SFXオーディオ・プロセッサ」および「「DesignWare ARC Sound AS221BDオーディオ・プロセッサ」上でDRAデコーダ機能を実現するもの。

Synopsysは実チップとして実績のある「ARCオーディオ・プロセッサ」と合わせてソフトウェアIPを提供する事で、成長を続ける中国市場向けのエレクトロニクス製品の開発ニーズを狙う。

2011.05.13

2011年5月11日、ESLソリューションを手掛ける米Carbon Design SystemとMIPSは、バーチャル・プラットフォーム用のプロセッサ・モデルの提供に関するコラボレーションを発表した。

発表によるとCarbonは、RTLコードから生成した100%サイクル精度のバーチャル・プラットフォーム用のMIPSプロセッサモデルを同社の「IP Exchange」サービスを通じて提供。ここまでは以前から報じられているコラボレーションで、既に複数のMIPSモデルがCarbonから提供されているが、今回の発表で新しいのは、Carbonの提供するバーチャル・プラットフォーム用のMIPSモデルにgdb(GNUデバッガ)やMIPSのソフトウェア開発環境「MIPS Navigator ICS」が接続できるようになるという点。これによりユーザーは、Carbonのバーチャル・プラットフォーム「SoCDesigner Plus」と「MIPS Navigator ICS」によるインタラクティブなパフォーマンス解析やソフトウェア・デバッグが実現できるようになる。

同ソリューションの正式リリースは今後の予定だが、Carbonは6月5日から開催される第48回DACにて同ソリューションのデモを行う予定。Carbonは今回の発表と合わせて、新たなMIPSモデル「MIPS32 M14K」および「MIPS32 M14Kc」をリリースしている。

尚、MIPSは今年2月にCarbonと同じくバーチャル・プラットフォームのソリューション手掛ける英ImperasともMIPSモデルの提供に関するOEM契約を発表しており、自社のプロセッサモデルが扱える仮想開発環境の整備に力を注いでいる。

2011.05.12

2011年5月11日、Cadenceは、PCB設計ツール「OrCAD」ソリューションをWebベースで提供する「OrCAD Capture Marketplace」を発表した。

発表によると「OrCAD Capture Marketplace」は、「OrCAD」の最新バージョンによってアクセス可能なオンライン上のサービス空間で、Webを通じてオンデマンドでユーザーに「OrCAD」ソリューションを提供するというもの。

業界初となるこの画期的なソリューションである「OrCAD Capture Marketplace」は、Webを通じてデザイン・データや設計ノウハウ、ホワイト・ペーパー、製品情報などの各種リソースを提供するだけでなく、Cadenceのパートナー各社が開発した「OrCAD」環境をカスタマイズするためのサード・パーティー製アプリも提供。ユーザーは設計に役立てる情報やデザイン・データの入手だけでなく、設計環境のカスタマイズ・ツールもダンロードできるようになる。

Cadenceは、「OrCAD Capture Marketplace」という言わばオンライン・ストアを作り、そのインフラを顧客およびパートナーに提供する事で、「OrCAD」を中心としたPCB設計エコシステムの更なる拡大を目指しており、2011年Q2(4-6月)後半には正式に「OrCAD Capture Marketplace」のサービスを開始する。

Cadenceは、他社に先駆けて早いうちから特定顧客向けにオンラインのサポート・サービスを提供しているほか、「ChipEstimate」のようなWebベースのオンライン・ソリューションも手掛けており、「オンデマンド」なEDAソリューションの提供に積極的な姿勢を見せている。今回発表した「OrCAD Capture Marketplace」のコンセプトには、「オープンなエコシステムの構築」が明確に打ち出されており、サードパーティーのソリューションも含めたオンラインのサービス提供は、「OrCAD」ユーザーに様々な利益を与える事だろう。OrCAD Capture Marketplace」の今後の発展に期待したい。

2011.05.12

2011年5月11日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、同社製品「Certitude」のバージョンアップを発表した。

SpringSoftの「Certitude」は、検証環境そのものの品質をチェックするツールで、「ミューテーション解析」と呼ばれるソフトウェアのテスト手法をベースに、チェック・メカニズムやスティミュラス(テスト)の品質を客観的に評価できる。

SpringSoftは今回のバージョンアップで「Certitude」に新しいフォルト検出、ランキング、トラッキング機能を追加。これにより「検出されないフォルト」をより迅速に検出できるようになったほか、解析の優先度もツールが示唆してくれるようになった。

また、ユーザーが事前に定義した基準に応じて、重要な解析結果が検出されるとツールが自動的に停止する機能や検出結果に透過的にIDをマッピングする自動ID機能も追加された。

尚、SpringSoftによると、「Certitude」を検証工程の初期段階で使用する新しいモードを追加する予定があるとの事で、今回のバージョンアップを含めたそれら機能改善により、検証環境の品質チェックをより効率的かつ効果的に実現できるようになる。

「Certitude」は、2009年にSpringSoftに買収されてからも機能エンハンスが進められており、富士通セミコンダクターやメガチップスなど、国内の採用事例も増えている。

2011.05.11

2011年5月10日、Cadenceはセル・キャラクタライゼーション・ツールを手掛ける米Altos Design Automation社の買収を発表した。

Cadenceは、今回のAltosの買収に関する条件など具体的な詳細は発表していないが、既に買収は完了した様子。

Altosは2005年に設立された会社で、その経営陣は元Cadenceおよび元CadMOS(2001年にCadenceに買収されたEDAベンダ)出身者でCadenceとの馴染みが深かった。

Altosは、スタンダード・セル、I/Oライブラリ、エンベデッド・メモリのキャラクタライゼーション・ツールと各SSTA用のキャラクタライゼーション・ツールを提供しており、新世代のキャラクタライズ・ソリューションとして高速・高精度な処理を武器に、半導体大手上位20社中の11社をはじめとする30社以上の企業とビジネスをしていた。

発表されている顧客名としては、STマイクロ、TI、Alteraなどがあり、同社のキャラクライゼーション・ツール「Variety」と「Liberate」はTSMCの40nmプロセスのリファレンス・フローにも採用されていた。

CadenceはAltosを獲得する事によって、同社ビジネスの基盤であるSilicon Realization ツールを更に拡充するとしている。

2011.05.10

2011年5月10日、Alteraは、同社デバイスの専用開発環境「Quartus II」の最新バージョン「Quartus II v11.0」のリリースを発表した。

今回バージョンアップされた「Quartus II v11.0」の目玉は、「SOPC Builder」の後継ツールとなるシステム統合ツール「Qsys」の搭載で、昨年12月以降ベータ版としてリリースされていた「Qsys」が正式な製品版として登場した。

「Qsys」はFPGA上にシステムを構築する上で欠かせないシステム統合ツールで、プロセッサをはじめとするIPコアをFPGAに接続するために利用される。「Qsys」は、FPGAに最適化された独自のネットワーク・オン・チップ (NoC)・ベース・インタコネクト機能によって、「SOPC Builder」の約2倍のインターコネクト性能を実現するということで、今回の製品版では同インターコネクトのインタフェースとしてAlteraの「Avalon」インタフェースがサポートされている。

「Qsys」には、複数の標準インタフェース間のブリッジング処理を自動化する機能が備えられており、今後は「Avalon」インタフェースに加えてARMの「AMBA AXI」インタフェース等もサポートされる予定。 異なる業界標準インタフェースに準拠したIPコアを自由にシステムに追加出来るようになる。

尚、今回の「Quartus II v11.0」のリリースに伴い、Alteraは「PCIe to DDR3 リファレンス・デザイン」を用意。このリファレンス・デザインは、メモリ・マップド PCIe Gen2x4 エンドポイントと外部 DDR3 メモリ間で、1,400MB/s を超えるスループットを達成するという事で、AlteraのWebからダウンロードして、「Qsys」の実現する高性能なインタコネクト機能を確認できるという。

「Quartus II v11.0」は既に出荷中で無償のウェブ・エディションも配布中。「Quartus II 開発ソフトウェア サブスクリプション契約」の年間費用は、米国内販売価格 2,995 ドルから。

2011.05.10

2011年5月9日、Cadenceは、顧客へのDFMサービス提供に関するTSMCとのコラボレーションを発表した。

Cadenceによると今回発表したTSMCとのコラボレーションは、CadenceおよびTSMCの両社の顧客に提供するDFMサービスに関するもので、CadenceはTSMC40nmプロセス以降の先端プロセスを対象としたリソグラフィプロセスのモデルベース・シミュレーションやバーチャルCMPなどDFM作業をサービス化し、これをTSMCは自社プロセス向けのDFMサービスとして正式に認証した。

同サービスの最終的なゴールは、テープアウト前のlithoおよびCMPホットスポットの発見を手助けする事にあり、CadenceはTSMCのDFM Data Kitをベースとした解析レポートを顧客に提供。この解析結果を活用することで、ユーザーは「Encounter」や「Virtuoso」を用いたテープアウトをより確実なものにする事ができる。

同サービスは既に提供されているようで、100コアの汎用プロセッサを手掛ける米Tilera社の担当者が同サービスを利用した事をコメントしている。

2011.05.09

2011年5月3日、Cadenceは、新製品2種を含む最新の「Cadence System Development Suite」について発表した。

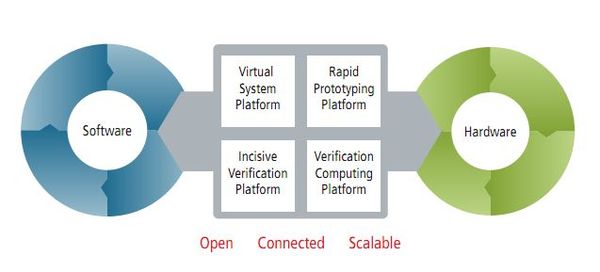

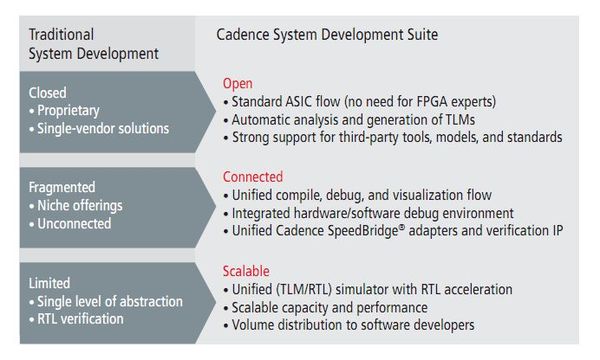

「Cadence System Development Suite」は、アーキテクチャ検討からFPGAプロトタイピングまでを包含するハード・ソフトの協調設計ソリューションで、同社のエミュレーター環境「Palladium XP Verification Computing Platform」、シミュレーター環境「Cadence Incisive Verification Platform」の他に、新製品となる「Cadence Rapid Prototyping Platform」および「Cadence Virtual System Platform」の4つのプラットフォームで構成されている。

「Cadence Rapid Prototyping Platform」は、Cadence初のソリューションとなるラピッド・プロトタイピング向けのFPGAボードで、最大3000万ASICゲートのデザインに対応。複数FPGAへのデザイン分割やFPGAへのマッピング機能など、FPGAベースのプロトタイピング・システムとしてのソフトウェア環境も用意されている。

最大の特徴は、同社のエミュレーター環境「Palladium XP Verification Computing Platform」との互換性で、クロックの定義やメモリのモデリングなどを気にする事無く「Palladium XP」上の環境を再利用できるほか、Cadenceがエミュレーション環境への接続アダプタとして用意していた「SpeedBridge Adapters」とも互換性があるようだ。

また、「Cadence Rapid Prototyping Platform」は、ASIC設計スタイルのクロッキングや、メモリの自動変換(ASICtoFPGA)をサポートしており、インプリメント先はFPGAであっても既存のASIC設計スタイルのままで利用できるとCadenceは強調している。

※画像は「Cadence Rapid Prototyping Platform」」の構成イメージ CadenceのWeb上のドキュメントから抜粋

尚、この「Cadence Rapid Prototyping Platform」は、既にNVIDIAがユーザーとして利用しているようで、現在用意されているボードは4種類は全てAlteraのFPGA「Stratix-4」ベース。最も小さいボードは「Stratix-4」2個搭載で1000万ASICゲート対応。最も大きいボードは「Stratix-4」6個搭載で3000万ASICゲートに対応。オンボード・メモリは最大16GBで、PCIe12レーン、 Ethernetソケットが2個備えられている。

※画像は「Cadence Rapid Prototyping Platform」」のボード仕様 CadenceのWeb上のドキュメントから抜粋

2011.05.09

2011年5月2日、アサーション自動生成ツール「BugScope」を手掛ける、NextOpは、 NVIDIAとのライセンス契約拡張について発表した。

発表によるとNVIDIAは「BugScope」のライセンスを複数導入。今回の契約は既存の契約を拡張するもので、NVIDIAが「BugScope」の有用性を認めたと理解できる。NVIDIAでは「BugScope」をRTLおよびテスト・スイートに重要な変更が有った際に活用しており、生成したアサーションおよび機能カバレッジ・プロパティをシミュレーター、エミュレーター、フォーマル検証ツールで利用している。

NextOpによると、NVIDIAによる「BugScope」の活用実績として、以下のような事例があるという。

・10万行のRTLコードに対して1200のアサーションと800の機能カバレッジ・プロパティを生成した。

・生成したアサーションおよびプロパティはターゲット品質とパフォーマンス仕様に適したものであり、シミュレーション時間に与える影響は2%以下だった。

・「BugScope」の示したテスト・ポイントによってRTLのバグを発見することができた。

2011.05.09

2011年5月4日、Mentor Graphicsは、機能検証に関するTSMCとのコラボレーションについて発表した。

発表によるとTSMCとMentorは共同でMentorの「Questa Ultra」をベースとした最新の機能検証環境を確立。その最たるモチベーションは、チップの機能検証における「カバレッジの収束」で、TSMCは自社の顧客が直面している検証課題の克服に向けてMentorと新たな機能検証環境の構築に取り組んだ。

「Questa Ultra」とは聞き慣れない製品名だが、Mentorによると同社の様々な機能検証ソリューションを包括的に統合した環境のようで、テストベンチを賢く自動生成するインテリジェント・テストベンチ自動生成、ロー・パワー検証、検証マネジメント、CDC検証、フォーマル検証といった各種機能が「Questa」のシミュレーション・プラットフォームにインテグレーションされており、TLMからRTL、そしてチップ・インプリメンテーションまでの機能検証プロセスをカバーしているとの事。

実際にこの「Questa Ultra」をベースに構築した機能検証環境は、TSMCとMentor共通の顧客であるAppliedMicro社によって評価済で、AppliedMicro社の担当者は「ローパワー・デザインにおけるカバレッジ測定基準を全体的に管理する事が可能となった。」、「インテリジェント・テストベンチ自動生成機能はカバレッジ収束時間を100倍以上短縮できる。」とコメントしている。

尚、Mentorによると「Questa Ultra」は既に製品として利用可能な状態にあるという。

2011.05.08

2011年5月4日、e/SystemVerilogのフロントエンド環境を手掛けるルーマニアのEDAベンダAMIQは、同社製品「DVT」の新機能「e言語デバッグ機能」を発表した。

AMIQによると今回発表された「e言語デバッグ機能」は、e、SystemVerilogおよびVerilog、VHDLのフロントエンド環境として提供されている同社のエディタ「DVT」のオプション機能として提供されるもので、ブレークポイントの設定、スレッドやコールスタックのナビゲーション、ローカル変数のチェックや値の変更などがGUIからのワンクリック操作で実行可能。デバッグの前後関係をビューワーで確認しその結果を管理することもできる。

環境としては、Cadenceの「Incisive Enterprise Specman Simulator」とシームレスに接続することが可能で、ユーザーは「Incisive Enterprise Specman Simulator」でe言語ライブラリをプリロードまたはプリコンパイルしておくだけで、「DVT」のデバッグ機能を利用可能。Specmanのシミュレーション・スクリプトを利用する事もできるという。

2011.05.07

2011年5月3日、Cadenceは、新製品2種を含む最新の「Cadence System Development Suite」について発表した。

発表によると「Cadence System Development Suite」は、アーキテクチャ検討からFPGAプロトタイピングまでを包含するハード・ソフトの協調設計ソリューションで、同社のエミュレーター環境「Palladium XP Verification Computing Platform」、シミュレーター環境「Cadence Incisive Verification Platform」の他に、新製品となる「Cadence Rapid Prototyping Platform」および「Cadence Virtual System Platform」の4つのプラットフォームで構成されている。

※画像は「Cadence System Development Suite」の構成イメージとその特徴 CadenceのWeb上のドキュメントから抜粋

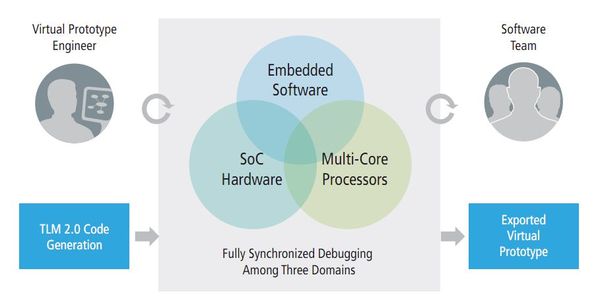

新製品「Cadence Virtual System Platform」は、今回ようやく明らかにされたいわゆるCadence独自の「バーチャル・プロトタイピング環境」で、実機同等の仮想的なハードウェア・プラットフォームを作成し、ハード上で走るソフトウェアの開発効率アップを狙うもの。基本的にSystemC TLMをベースとした環境で、作成したバーチャル・プラットフォームをシミュレーター、エミュレーター、更にはインプリメントまで繋げる事が出来るというのが、Cadenceソリューションならではの大きな特徴と言える。

競合他社のソリューションとしては、Synopsysの「CoMET/METeor」、「Platform Architect/Virtual Platform」、Mentorの「Vista」などがあるが、それら競合製品と「Cadence Virtual System Platform」とでは「プロセッサ・モデル」の扱いをはじめ、各所に大きな違いがある。

例えば、Synopsysのソリューションでは、独自のプロセッサ・モデルを提供する事で高速あるいは高精度なシミュレーションを実現しており、それが他のソリューションとの大きな差別化要因となっているが、「Cadence Virtual System Platform」は、独自のプロセッサ・モデルは提供せず、ARMから提供される「Fast Models」またはImperasから提供される「OVP fast processor model(ARM, MIPS, Renesas, PowerPC) 」を利用する。

Cadenceのこのアプローチは、ARMをはじめとしたメジャーなプロセッサをターゲットとするユーザーにとっては、ツール環境に依存しない仮想環境を構築できるという大きなメリットがある。しかし、裏を返せばARMとImperasがモデルを提供していないプロセッサはターゲットに出来ないという事になってしまうため、Cadenceは何か手立てを用意しているのかもしれない。

(※Platform Architect/Virtual Platformでは、サードパーティの提供するプロセッサ・モデルも利用可能。)

また、「Cadence Virtual System Platform」は、バーチャル・プラットフォームを「自動的に作成」する仕組みを用意しているようで、プロセッサ・モデル以外の各種周辺機能モデルは、IP-XACT仕様のメタデータを読み込むことで自動生成できるほか、Cadenceの用意するSystemC TLM 2.0のテンプレートを元に自動生成できるようだ。ライブラリとしては下記のような多様なモデルが用意されている。

【Cadenceの提供するVirtual System Platform向けモデル】※ブローシャからの抜粋情報

・Basic components

UART, keyboard/mouse controller, real time clock, programmable timer, interrupt controller, multimedia card, audio codec interface, programmable LED, color LCD, etc.

・Complex components

Ethernet controller, I2C, SPI, bus controller, serial interface, buffer, memory logger, battery, touch screen input, flash memory, initiator, multi-plexor, arbiter, router, etc.

・Virtualized hardware

terminal, Ethernet, etc.

「Cadence Virtual System Platform」には、作成したバーチャル・プラットフォームをパッケージしてソフト開発向けにエクスポートする機構が備えられており、ソフトウェアのみならずハードウェアも同期して可視化・デバッグできるGUIも用意されている。また、バーチャル・プラットフォーム上でのソフトウェアのデバッグには、ARM、Lauterbach、GDBなどのデバッガを利用する事も可能。ソフトウェアの検証および解析には、Imperasの提供するツールも利用できるという。

※画像は「Cadence Virtual System Platform」の運用イメージ CadenceのWeb上のドキュメントから抜粋

尚、「Cadence Virtual System Platform」は、シミュレーター(Incisive)と接続する事も可能でHDLでモデリングされたRTL資産も取り扱う事ができるが、基本的なコンセプトは、SystemC TLM 1.0またはTLM 2.0ベースのバーチャル・プロトタイピングの容易な実現で、SystemC TLMベースのオープンなプラットフォームを容易かつ短時間で作成するという方針を打ち出している。

「Cadence Virtual System Platform」は、「バーチャル・プロトタイピング環境」としては業界の中で後発の製品となるが、SystemC TLMをベースにCadenceの包括的な検証ソリューションならびにサードパーティーとの各種ソリューションに繋がる点は、他社ソリューションに無い大きな差別化要因と言える。年内には正式リリースされるという同製品の今後の活躍に注目したい。

2011.05.06

2011年5月3日、Mentor Graphicsは、GNUツールチェーンをベースとした組み込みC/C++開発環境「Sourcery CodeBench」のリリースを発表した。

Mentorのリリースした「Sourcery CodeBench」は、昨年11月にCodeSourcery社から買収したオープンソースのGNUツールチェーン資産をベースとした組み込みC/C++開発環境で、Mentorの開発チームによって、 NetLogic Microsystems XLP multi-core processor, Freescale Kinetis, Xilinx Zynqといった各プラットフォームの新規サポートや、ソフトウェアのパフォーマンス解析機能「Embedded Sourcery System Analyzer technology」の追加が実現されている。

製品パッケージはコマンドラインのみの無償版以外に、Personal Edition,Standard Edition,Professional Editionの3種類のパッケージが用意されており、最も安価なPersonal Editionは、1ライセンス399米ドル。同パッケージと同等のアカデミック版は99米ドルとなっている。

2011.05.06

2011年5月3日、今年で21回目の開催となる米EDN誌の「INNOVATION AWARDS」の受賞者が発表された。

昨年までの「INNOVATION AWARDS」では、EDA部門としてバックエンド、フロントエンドと計3つの部門が用意されていたが、今年は「EDA Tools and ASIC Technologies」という一つの部門に集約された。

「EDA Tools and ASIC Technologies」部門の受賞者として表彰されたのは、Apache Design Solutionsで製品は「PathFinder」。

「PathFinder」は、2010年5月にリリースされた新製品で、フルチップのESDフィジカル・インテグリティ解析ツールとして、ESD検証における、モデリング、抽出、シミュレーションを包括的にカバーする。

尚、今回惜しくも受賞を逃した「EDA Tools and ASIC Technologies」部門、その他のファイナリストは以下の通り。

・Calibre InRoute, Mentor Graphics

・DRC+, GlobalFoundries

・SoftPatch for RocketVision, GateRocket Inc

2011.05.06

2011年5月2日、Cadenceは、自動車サプライヤー独BOSCHが「Virtuoso v6.1」をベースとしたCustom/Analog設計フローを標準採用した事を発表した。

発表によるとBOSCHはCadenceの協力により、「Virtuoso v6.1」をベースに社内のCustom/Analog設計フローを最適化。これまでは複数のベンダのツールを組み合わせて設計フローを構築していたが、Cadenceの「Virtuoso Schematic Editor」、「Virtuoso Analog Design Environment」、「Virtuoso Layout Suite」をベースに「Constraint-Driven Design methodology」を実現。「Virtuoso v6.1」ベースの新たなCustom/Analog設計フローを社内標準フローとして採用した。BOSCHはこの新たなフローによって、設計生産性を約25%向上できたという。

2011.05.06

2011年5月2日、FPGAプロトタイピング向けの検証ソリューションを手掛けるInPA Systemsは、FPGAプロトタイピング・ボード・メーカーDini Groupとのコラボレーションを発表した。

発表によると両社のコラボレーションは、大規模ボードに搭載される「マルチFPGA」の高速なデバッグ手法に関するもので、Dini Groupが開発したXilinxの「Virtex-6」を複数搭載した大規模プロトタイピング・ボードに備えられるデバッグ用のコネクタを活用し、InPAが独自の可視化技術「Active Debug」を応用するものだという。

両社のコラボレーションによって実現されるソリューションは、今年のQ3にリリースされる予定で、今年のDACでは先行してデモを披露する計画となっている。

2011.05.06

2011年5月2日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、同社の提供するデバッグ環境「Verdi」が検証メソドロジ「UVM」を包括的にサポートした事を発表した。

UVM:Universal Verification Methodology

発表によると、SpringSoftは業界標準のHDLデバッグ・プラットフォーム「Verdi」にUVMソースと効率的にトランザクション・データをダンプし表示する新しい「UVMトランザクション・レコーディング機能」を追加することで、テストベンチ構造およびテストベンチとデザイン間の情報の視覚化を実現。「Verdi]には、ダンプしたトランザクションをハイライト、フィルタリングする表形式のスプレッドシート、テストベンチの階層をナビゲートするブラウザ、テストベンチの問題の原因を特定する自動トレース機能等が備えられており、成熟した既存のデバッグ環境「Verdi」上でUVMテストベンチを取り扱う事が可能となる。

SpringSoftでは、今後もダイナミックなデータのダンピング機能をはじめ、異なる種類のデータをダンプするための自動ダンプの強化、新しい表示機能など、Verdiを強化していく予定としている。

尚、発表された「Verdi]によるUVMの包括サポートは既に実現済で、「Verdi」の最新バージョンにてUVMテストベンチ・デバッグ機能とトランザクション・レコーディング機能を使用可能。「Verdi」の定価は、3年契約の場合、年間ライセンス140万円となっている。

2011.05.06

2011年5月2日、Altera、MIPS、System Level Solutionsの3社が、MIPS完全互換のソフト・プロセッサをAltera製デバイス上で実現するソリューションを発表した。

発表によると、インドの設計IPプロバイダSystem Level Solutions(以下、SLS)が、MIPS2.0アーキテクチャーに100%完全互換のソフト・プロセッサ「MP32」を開発。同プロセッサは、Altera製のFPGAおよびASIC(Hard Copy)向けに最適化されており、Altera製デバイスを用いたMIPS搭載システムを容易に開発することができる。

開発環境としては、、Alteraのシステム統合ツール「SOPC Builder」の後継となる、次世代システム統合ツール 「Qsys」を利用してFPGA+MIPのシステムを構築する事が可能なほか、ソフト開発環境としてはMIPSから提供されているMIPS純正環境「MIPS Navigator ICS」が利用可能。また、組込みOSとしては「VxWorks」がサポートされており、Wind Riverより「MP32」向けの「VxWorks board support package (BSP)」が提供される。

尚、今回発表された「MIPS on Altera」を実現するソフト・プロセッサ「MP32」は、SLS社より提供される形。Altera製デバイスをターゲットに同プロセッサを利用する場合、原則的にロイヤリティ不要だという事で、費用的な面で同ソリューションを選択するメリットは大きそうだ。

2011.05.02

2011年5月2日、米SIA(Semiconductor Industry Association)は、2011年3月の世界半導体売上高を発表した。

SIAの報告によると、2011年3月の世界半導体売上高は252億6000万ドル。前年同時期比は約8.8%増、前月比約2.5%増という統計結果となった。

世界半導体売上は、2009年12月から2011年2月まで15ヶ月間連続して売上前年比2ケタ増を記録してきたが、この3月でついに前年比1ケタ増に落ち着いた。

四半期の売上で見ると、2011年Q1(1-3月)は2010年Q1の698億ドルに対して約8.6%増の758億ドルとなった。

地域別売上で見ると、北米の売上が前年比18.1%と大きな伸びを示しているのに対し、日本市場は0.2%増といギリギリ前年比増をキープした状況。これは震災の影響が大きいと思われる。

ゆるやかになったとは言え、世界半導体市場の成長は以前継続しており、現在のところ各調査会社の予測する「2011年は前年比4?7%成長」のライン上にあると言える。

2011.04.28

2011年4月26日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automationは、RFチップの米ファブレスIO Semiconductorが同社の「Analog FastSPICE」を採用したことを発表した。

発表によるとIO Semiconductorは、マルチバンド、マルチモード携帯電話向けのフロントエンド チップ「ZEROcap」の設計において、RF検証とキャラクタライゼーションでBerkeleyの「Analog FastSPICE」を採用。その結果、ナノメータSPICE精度のシミュレーションを従来のSPICEよりも5倍から10倍の速さで実施することに成功。その性能は、IOsemiの必要とする条件を超えるものだったという。

2011.04.28

2011年4月27日、EDA関連の標準化団体Accelleraは、ソフトIPのトラッキングを実現する「タグ付け」に関する技術標準化チーム「IP Tagging Technical Subcommittee」の立ち上げを発表した。

発表によるとAccelleraが進めようとしているIPタグ付けの標準化は、元々IPコア関連の標準化団体「VSI Alliance」で進められていた活動で、その後「SPIRIT Consorsium」にその活動が引き継がれ、「SPIRIT Consorsium」が「Accellera」に合併されたことで、今回の「IP Tagging Technical Subcommittee」の発足に至っている。

IPタグ付けの標準化の狙いは、LSI設計におけるソフトIP利用の透明性を高めるためであり、最終的にGDSIIデータにおいてソフトIPタグを認識できる形を目指す。ソフトIPにタグを付ける事によってIPのトラッキングが可能となり、ロイヤリティや海賊版製品のチェックに限らず、GDSIIを生成するまでの設計の各工程でIPバージョンを確認できるなど、IPの供給者にとっても利用者にとってもメリットは大きい。

Accelleraは、関係各社に「IP Tagging Technical Subcommittee」への参加を呼び掛けている。

2011.04.28

2011年4月27日、Xilinxは、2011会計年度第4四半期(2011年1-3月)の売上を報告した。

Xilinxの2011年Q4(1-3月)の売上は、前年同時期比約11%増、前期Q3(10年10-12月)比約4%増の5億8790万ドル。営業利益は前年比8%増、前期比5%増の1億6010万ドルという結果だった。

Xilinxは3月が決算月であるため、2011会計年度の売上合計額を合わせて報告。その額は前年比29%増の23億7000万ドルで過去最高。営業利益の合計は6億4190万ドルで前年比80%増だった。

同社の2011年Q4(1-3月)の売上を地域別に見ると、そのシェアは北米27%、アジア35%、欧州30%、日本8%、分野別で見ると、通信分野47%、FAその他32%、コンスーマ&自動車14%、データ・プロセッシング7%となっている。

製品の分野別で見ると、新製品としてカテゴライズされているVirtex-6, Virtex-5, Spartan-6, Spartan-3A, Spartan-3E の売上が前売上の46%を占めている。今後はこれら新製品カテゴリに28nmFPGAのVirtex-7シリーズも加わることになり、更にはARM搭載FPGA「Zynq 7000」ファミリも追加される予定である。

尚、Xilinxは次期2012年Q1(11年4-6月)の売上は今期の4%増程度と見込んでいる。

2011.04.28

2011年4月27日、Cadenceは、2011会計年度第1四半期(2011年1-3月)の売上を報告した。

Cadenceの2011年Q1(1-3月)の売上は、前年同時期比約20%増、前期Q4(10年10-12月)と比較して約7%増の2億6600万ドル。600万ドルの営業利益を計上した。(※GAAP基準による会計結果)

今回Cadenceが報告したQ1売上2億6600万ドルは、2月時点での同社のフォーキャストを上回るもので、社長兼CEOのLip-Bu Tan氏のコメントによると、エミュレーター「Palladium XP ―Verification Computing Platform」が売れているとの事。この2月にはBroadcomによる「Palladium XP」の採用も報じられている。また、カスタム設計環境「Virtuoso」、デジタル・インプリメント環境「Encounter」といった同社の売上の柱である「Silicon Realization products」が好調だったという。

Cadenceが新ビジョン「EDA360」を打ち出してから早一年。売上報告を見るとその経営は完全に回復軌道に乗り、このところ5四半期連続で売上前年比増を達成している。

尚、Cadenceは次期2011年Q1の売上を2億7000-8000万ドルと予測、2011年売上合計の予測を10億7500-11億1500万ドルと上方修正した。

2011.04.28

2011年4月27日、アームは、2011会計年度第1四半期(2011年1-3月)の売上を報告した。

アームの2011会計年度Q1 (2011年1-3月) の売上は、前年比29%増、前期(2010年Q4)比3%増の1億8550万ドルで前期に続いて四半期売上記録を更新。営業利益は前年比約18%増の約4880万ドルを計上した。

アームによると、このQ1で新たに39件のプロセッサ・ライセンスを獲得。(前Q4では35件)BroadcomやLGがARMとのライセンス契約を更に拡張している。Q1で出荷されたARM搭載チップの総数約18.5億個のうち11.5億個はスマートフォンなどのモバイルデバイスで、前期Q4と比較して5000万個出荷数を増やした。残りの7億個はゲームやテレビ、カメラなどの家電とクルマ向けとなる。

尚、ライセンスの売上は前年比49%増の6390万ドルで、契約数39件のうち15件は「Cortex-M」の契約(うち6件は新規契約)、GPU「Mali」の契約も7件あった。ユニット出荷数ではARM11とCortexが少し割合を増やし全体の25%となった。

2011.04.27

2011年4月26日、米EETimes誌は、EDA関連標準化団体Si2による3D-IC設計の標準化プロジェクトの始動を報じた。

同誌によるとSi2では、2.5-Dおよび3-Dチップ設計のEDA標準仕様の策定を目指し「Open3D Project」を始動する計画で準備を進めているとの事。既に12社以上の企業がこの活動に興味を示しており、6月に開催される第48回DACにてキックオフ・ミーティングが開催される予定。同活動で標準化を進めるEDA標準は、TSVベースの3D-IC設計を想定したもので、ツールの相互運用が可能な3D-IC設計環境の実現を目指している。

2011.04.27

2011年4月26日、SynopsysはHiSilicon社によるIC Compilerの成功事例を発表した。

発表によるとHiSiliconは、「green networking」アプリケーションをターゲットとしたIC設計フローでSynopsysの配置配線ツール「IC Compiler」を採用。同ツールを用いた設計によってテープアウトを成功させ、チップとしてスタンバイ時の消費電力を40-50%削減する事に成功したという。

2011.04.27

2011年4月26日、ARMは、韓国LG Electronicsとの新たなライセンス契約を発表した。

発表によると今回LGがライセンス契約を結んだのは、ARMの最新プロセッサコア「Cortex-A15 MPCore」および「Cortex-A9 MPCore」、「Mali-T604」GPU、インターコネクトおよびシステムIP「CoreLink」など。

ARMによるとLGはこれら新規IPを用いて、デジタルTV、STB、携帯電話、タブレット、スマート・グリッドといったアプリケーションのプラットフォーム戦略をドライブしていく計画だという。ちなみにARMとLGの契約関係は1995年から。

2011.04.27

2011年4月26日、Alteraは2011年Q1(1-3月)の売上を報告した。

発表によると2011年Q1売上は、前年同時期比約33%増、前期(2010年Q4)比約4%減の5億3580万ドル。純利益は2億2410万ドルで前年同時期約46%増、前期比約3%減という結果だった。

売上の内訳を見ると、やはり新製品として分類しているStratix III, Stratix IV, Arria II GX, Cyclone III,Cyclone IVといった製品群が好調で前期に続いて売上額を13%増やし、売上全体の18%占めるに至った。

地域別の売上では、これまで好調でシェア40%以上だったアジアが30%台に落とし、日本もシェア15%台に落とした。一方で欧州は売上好調を維持しており、前期は落としていた北米も今期は回復を見せた。

分野別の売上では、売上の柱のテレコム及びワイヤレス分野が売上を落とし、その分、FA、ミリタリー、自動車分野が売上を伸ばした。アジアの売上減とテレコム及びワイヤレス分野の売上減は連動しているかに見える。

2011.04.27

2011年4月26日、Cadenceは、PCBおよびICパッケージ設計の統合設計環境「Allegro」のバージョンアップを発表した。

Cadenceの発表によると、リリースした「Allegro」の最新バージョン16.5では、小型化機能、電源ネットワーク解析機能、ボードとパッケージのコ・デザイン機能、チーム設計機能といった新機能追加および機能強化が実現されており、PCBおよびICパッケージ設計をより包括的にカバーすると同時にその生産性が高められた。

具体的な例としては、電源ネットワーク解析機能により、完全に配線されたPCBの消費電力のトレードオフが可能となったほか、「PCB Interconnect Design Planning」と呼ばれる新しいオプション機能では、特許取得済みの階層抽象化手法によりタイミング収束を加速。また、多拠点にまたがるチーム設計の効率化に向けてオーサリング機能も強化された。

更に今回の「Allegro」のバージョンアップで目を引く点が2つ。一つは、デザイン・キットの提供で、Cadenceは「Allegro 16.5」からパッケージおよびPCB設計を考慮したSoC向けのIP(デザイン・キット)の提供を開始。手始めにDDR3向けのキットを提供し、今後そのバリエーションを増やしていく計画で、このソリューションを利用すれば、SoCからパッケージおよびPCBまで一貫した形で標準規格に準拠した迅速なインプリメンテーションが可能となる。

もう一つは製品構成の変更で、Cadenceは「Allegro 16.5」からオンデマンド型の製品構成を採用。基本構成とオプションから成る新たな方式により、ユーザーは必要な時に必要な機能をオンデマンドで利用できるようになり、無駄なツール費用を削減可能となる。これはユーザー企業にとってツールの機能アップと同等に大きなメリットになると言える。

尚、今回の「Allegro」バージョンアップの発表は、同社の「EDA360ビジョン」の発表からちょうど1年目に当たるとの事。

2011.04.26

2011年4月25日、米国の半導体製造技術研究のコンソーシアムSEMATECHは、同組織の「3Dプロジェクト」にAdvanced Semiconductor Engineering、Altera、Analog Devices、LSI、ON Semiconductor、Qualcommの6社が参加した事を発表した。

SEMATECHでは、同組織のメンバー企業で独自にTSVの研究を進めていたが、2010年12月にSIA(米国半導体工業会:Semiconductor Industry Association)およびSRC(米国半導体研究所:Semiconductor Research Corporation)と共同でヘテロジニアス3D-IC製造の技術仕様の標準化を目的とした「3D Enablement program」を始動。CNSE(College of Nanoscale Science and Engineering) , GlobalFoundries , Hewlett Packard , Hynix , IBM , Intel , Samsung , UMCが同活動に参画していた。

2011.04.26

2011年4月25日、LSI機能検証ソリューションを手掛けるCMエンジニアリングは、新製品となるAMSライブラリ開発キット「SAQuT! AMS」のリリースを発表した。

今回発売された「SAQuT! AMS」は、既に提供されている「SAQuT! AHB/AXI」、「SAQUT! VMM/OVM」に続くSAQuT!ファミリの第3弾で、アナログ回路に不慣れなデジタル回路設計者を主たるターゲットとしたAMSライブラリ開発キットで、ミックスドシグナル設計におけるボトルネックの解消を支援するもの。

キットの内容は、アナログモデリング設計手法を学習するためのドキュメント、Verilog AMS/Aのサンプルモデル(ファンクションモデル)、テストベンチ、OPUSデータ、スクリプト、仕様書/検証報告書などのドキュメント類一式、アナログ検証セミナーの受講券と盛り沢山で、Verilog AMS/Aの導入を包括的にフォロー。既にリリースしているSAQuT!ファミリ製品と同様のコンセプトで、「SAQuT! AMS」を利用することで環境立ち上げ工数を大幅に削減し、Verilog AMS/Aの環境をサクっと立ち上げることができる。

デジタル設計者がVerilog AMS/Aを習得してアナログ回路のモデリングが可能となれば、ミックスドシグナル設計の検証の効率化や早期バグ収束といった効果が見込める。

2011.04.23

世界EDA売上推移を更新しました。

地域別の売上推移も作成しました。

※EDAC MSSレポートの数字をベースに作成しています。

2011.04.22

2011年4月21日、SoC/ASICプロトタイピング・システムを手掛ける米S2C社は、同社の第4世代製品ファミリの新製品「Quad S4 TAI Logic Module」のリリースを発表した。

S2Cによると新製品「Quad S4 TAI Logic Module」は、Alteraの40nmFPGA「Stratix IV 820」を4個搭載したプロトタイピング・ボードで、インプリメント可能なデザイン容量は3280万ゲート。DDR2およびDDR3のソケットを2個ずつ備え、各FPGAのI/Oは480、4個のFPGAは300のインターコネクトによって接続されている。また、デザインを分割してFPGAへのマッピングをコントロールするソフトウェア環境「TAI Player」も今回の製品リリースと合わせてバージョンアップされた。

S2Cによると、2010年6月に出荷を開始したStratix IVベースの第四世代製品は既にボードにして計100枚の販売を達成しているとの事。S2Cは、Altera製FPGAをベースとした製品以外に、Xilinx製FPGAを用いたプロトタイピング・ボードも提供しており、同最新製品としてはVirtex-6を用いた「V6 TAI Logic Module」がある。

また、S2Cではプロトタイピング用の各種拡張ボードも提供しているほか、シリコンIPも提供しており、独自の特許技術「TAI IP技術」によって、製品購入前に暗号化したIPを評価できる仕組みを整えている。この「TAI IP技術」は同社の提案する「FPGA-based ESL methodology」にも生かされており、競合製品には無い同社ソリューションの大きな特徴となっている。

※画像は「Quad S4 TAI Logic Module」(S2C社Web掲載データ)

2011.04.20

2011年4月19日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、半導体ターンキー・サービス大手のVeriSiliconがデバッグ環境「Verdi」を標準採用した事を発表した。

SpringSoftの発表によると、VeriSiliconは「Verdi」を社内のデバッグ・リファレンスフローにおける標準ツールとして採用。既に同社の世界各地の拠点にて既存の検証フローに統合する形で「Verdi」を導入しており、ハードウェア設計の機能検証に関わる全てのエンジニアが「Verdi」を使用中。その可視化能力によってデバッグ期間を平均20%削減しているという。

2011.04.19

2011年4月19日、Alteraは、同社の28nmFPGA Stratix VがICチップ上のトランジスタ搭載数の最多記録を達成したことを発表した。

Alteraによると、TSMCの28nm High-Performanceプロセスで製造している同社の最上位FPGA「Stratix V」 FPGA は、業界初となる39億個のトランジスタを搭載しており、これまでの記録を塗り替えた。同製品は2010年末に初のテープアウトが成功しており、現在サンプル出荷中となっている。

2011.04.15

2011年4月12日、Mentor Graphicsは、SPICEシミュレーターの新製品「Eldo Premier」のリリースを発表した。

Mentorによると新製品「Eldo Premier」は、従来SPICEおよびFastSPICEではない「FasterSPICE」すなわち、SPICE精度を維持した高速高精度SPICEに分類される製品で、名前は既存の従来型SPICE「Eldo」を継承しているが、そのエンジンはBerkeley SPICEとは異なる。

具体的には、内部のMetrixソルバー、代数ソルバーが刷新されたほか、マルチスレッド処理のために新たなシミュレーション・カーネルが用意されている。これにより、シミュレーション速度は従来のclassic「Eldo」よりも2.5?20倍の高速化を実現。(ノード数が増えるほど速度効果を発揮)容量も従来比約10倍の10Mトランジスタまで拡大された。

「Eldo Premier」は、大規模なアナログ設計におけるSPICEへの高速高精度化ニーズに応えるために開発された製品で、Berkeley Design Automationの「Analog FastSPICE」やMagmaの「FineSim」などが競合製品となる。これら競合製品は、他製品へのインテグレーションやサードパーティー・ツールとの連携が積極的に進められているが、Mentorの「Eldo Premier」もそのエンジンを業界デファクトのアナログ/ミックスシグナル・シミュレーター「Questa ADMS」で利用する事ができる。

※画像はMentor Graphics社の提供

2011.04.13

2011年4月12日、セル・キャラクタライゼーション・ツールを手掛ける、米ALTOS Design Automationは、同社がTexas Instrumentsの2010 Supplier Excellence Awardを受賞した事を発表した。

Texas InstrumentsのSupplier Excellence AwardはTIへの功労賞とも言うべき優れたサプライヤを表彰するもので、2010年アワードでは12000以上のサプライヤの中から16社が選ばれた。ALTOS Design Automationはそのうちの1社となる。

ALTOSによると、 ALTOSとTIは共同でセル・キャラクタライゼーション・ツール「Liberate」、「Variety」、「Liberate MX」をベースとしたスタンダード・セルおよびメモリのライブラリIPのキャラクタライザーション・フローを構築。更に両社は共同でSRAMおよびTCAMコンパイラを開発したという。

2011.04.13

2011年4月12日、タイミング解析ツールを中心としたEDAソリューションを手掛ける、米Incentia Design Systems社は、Richtek Technology社が同社の論理合成ツールとスタティック・タイミング・アナライザを採用したことを発表した。

発表によると、パワー・マネジメントICを手掛けるRichtekは、社内のMiked-signal設計フローにおいてIncentiaの論理合成ツール「DesignCraft」とSTA「TimeCraft」をセットで採用。両ツールを用いた設計により、チップ面積と消費電力の削減を実現し、テープアウトを成功させたという。

IncentiaのSTA「TimeCraft」は、日本国内でもNECやリコーに採用されているほか、STARCの手掛けるデザイン・フローSTARCADにも採用されている。

また、論理合成ツール「DesignCraft」は、今年2月にAmerican Semiconductorによって同じくMixed-signal設計フローで採用されたことが発表されている。

2011.04.12

2011年4月11日、Cadenceは、DDR4メモリの標準規格に準拠したIP製品のリリースを発表した。

プレスリリース文

http://www.cadence.com/cadence/newsroom/press_releases/Pages/pr.aspx?xml=041111_ddr4&CMP=home

「DDR4」規格は、「DDR3」に続く次世代メモリ規格で現在JEDEC(半導体技術協会)で標準化作業が進められている。(今年後半に標準化が完了予定)

「DDR4」メモリは、「DDR3」メモリよりも高速かつ低消費電力で、最高転送速度は「DDR3」の倍の最高3.2Gbps。今年に入り韓国Samsungが「DDR4 DRAM」の市場投入を開始。つい先頃は韓国Hynixも「DDR4 DRAM」の開発を発表している。

今回Cadenceが発表した製品は、業界初となる「DDR4」に準拠した包括的なIP製品群で、ハードおよびソフトのPHY IP、コントローラIP、メモリモデル、検証IP、ツール環境とメソドロジ、ボードおよびパッケージ向けのシグナル・インティグリティのリファレンス・デザインなどが含まれている。

Cadenceでは、DDR4を用いた設計が2012年頃から始まると見込んでいるという。

ちなみに調査会社iSuppliは、2015年にはDRAM市場におけるDDR4の割合が50%に達すると予測している。

2011.04.12

2011年4月11日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、米国のファブレス・メーカーEon Silicon Solution社が同社の「Laker」カスタムIC設計ツール群を採用した事を発表した。

発表によるとEON社は、NORフラッシュ・メモリの専門ファブレス・メーカーとして自社のメモリ製品の設計に長年Lakerレイアウト・ツールを使用しており、今回新たにLakerレイアウト・ツールと統合された新たなカスタム・デジタル・配線機能を採用。その結果、レイアウト作業を従来の3倍の速さで実現可能となった。

SpringSoftの「Laker」は、Hynix Semiconductor、Winbond Electronicsといったメモリ大手にも採用されているという。

2011.04.12

2011年4月11日、Mentor Graphicsは、同社のPCB設計ソリューションの市場シェアが50%に達したことを発表した。※訂正あり

Mentorの発表によると、同社のPCB設計ソリューションの市場シェアが50%に達した事は、EDAの業界団体EDA Consortiumの2010年の市場調査において明らかになった事実。同調査によると、北米で60%、欧州で57%、アジア・パシフィックで50%、そして日本においては自社のシェアを75%以上伸ばしているという。

尚、日本市場においては、図研の存在からかMentorはこれまでトップ・シェアを獲得するに至っていなかったが、2009年から2010年にかけて一気にシェアを伸ばしたようだ。

2011.04.08

2011年4月7日、富士通と図研はPCBの設計・解析システムに関するパートナー契約の締結を発表した。

発表によると両社は、富士通の子会社富士通アドバンストテクノロジが開発するPCB解析システム「SignalAdviser-SI」と、図研のPCB設計用ビューワー「CR-5000/BD-Viewer Advance」を接続するデータ変換プログラムを開発し、両ツールのシームレスな連携を図る予定で、最終的には富士通の「SignalAdviser-SI」と図研のPCB設計環境「CR-5000/Board Designer」を連携させる計画。

※図は両社の発表資料より抜粋

このツール連携により、PCB設計者は解析システムと設計システムがセットになった環境を入手可能となる。また、国内でのシェアが高い図研の「CR-5000/Board Designer」を使うユーザーは、富士通のPCB解析システム「SignalAdviser-SI」を容易に利用可能になる。

両社は、このPCB設計・解析統合環境を2011年度に計30セット販売する事を目標としている。

2011.04.06

2011年4月5日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automationと、セル・キャラクタライゼーション・ツールを手掛ける、米ALTOS Design Automationは、両社製品のコラボレーションを発表した。

発表によると、今回Altosのセル・キャラクタライゼーション・ツール「Liberate」がBerkeleyのSPICEシミュレーター「Analog FastSPICE」をサポートし、両製品を組み合わせて利用することで従来よりも高速なセル・キャラクタライズを実現できるようになった。

この両社製品のコラボレーションは、高速化の求められるI/Oセルのキャラクタライズをターゲットとしており、高速かつ高精度がウリのBerkeley「Analog FastSPICE」を用いる事で、Altos「Liberate」によるキャラクタライズ処理を従来よりも5-10倍高速に実行することが可能。もちろん、ナノメーターレベルのSPICE精度が維持されている。

Berkeleyの回路シミュレーター「Analog FastSPICE」は、Solido Design Automationのトランジスタレベルの統計的ばらつき解析ツール「「Variation Designer」の解析エンジンとしても利用されている。

2011.04.06

2011年4月5日、ESLソリューションを手掛ける米Carbon Design SystemsとMentor Graphicsは、CarbonのWebポータル「IP Exchange」でMentor製「8051」CPUコアモデルの供給を開始したことを発表した。

発表によると、Carbonが各種ESLモデルの供給手段として運用しているWebポータル「IP Exchange」の製品ラインナップとして、今回新たにMentor製「8051」CPUコアモデルが追加され、 8051、8051W、8051EWのCarbonモデルが供給される事になった。

「Carbon IP Change」は、ユーザーがモデルの提供元のIPベンダと直接的に契約を行う事なく、ワンパスで100%CA精度のCarbonモデルを入手できるクラウドベースの仕組みで、モデルの使用権はCarbonのバーチャル・プラットフォーム作成環境「SoC Desginer Plus」にバンドルされる。

既に「Carbon IP Change」を通じて、ARM、Cadence(Denali)、Elliptic Technologies、 MIPS Technologies、Tensilica、VeriSilicon、VivanteのCarbonモデルが提供されており、これらは全て実際のRTLコードから生成されたモデルとして100%のCA精度が保証されている。ユーザーはこれらモデルをCarbonの仮想環境「SoC Desginer Plus」で利用するだけでなく、市販論理シミュレーターでの高速検証にも利用可能。今回供給が発表されたMentorの「8051」CPUコアモデルは、8051の開発環境「uVision」やMentorのデバッガ「Questa Codelink」と繋いでソフトウェアのデバッグにも利用できるという。

2011.04.05

2011年4月4日、米SIA(Semiconductor Industry Association)は、2011年2月の世界半導体売上高を発表した。

SIAの報告によると、2011年2月の世界半導体売上高は251億9000万ドル。前年同時期比は約13.6%増、前月比約1.1%減という統計結果となった。

世界半導体売上はこの4ヶ月の間、2010年11月、12月、そし2011年2月と前月比増を記録しているが、次の2011年3月の売上は日本における震災の影響が出る可能性が高い。

今回の売上統計報告にあたり、SIAのPresidentも日本の震災についてコメントしている。