NEWS

2011.10.26

2011年10月25日、図研はプリント基板設計の統合環境として新製品「CR-8000 Design Force」および「CR-8000シリーズ」を発表した。

発表によると新製品「Design Force」は、「CR-8000シリーズ」の中核をなすプリント基板設計環境で、既存ツールの操作性やパフォーマンスを大きく見直し、マルチCPU/マルチスレッド、3Dグラフィックス、タッチパッド操作などの新技術を採用しているほか、基板内蔵部品、TSV、SIPなどの新しい基板実装技術にも対応している。

図研はこの新製品「Design Force」を中心に、構想設計ツール「System Planner」、回路設計ツール「Design Gateway」、製造設計支援ツール「DFM Center」から成る電子機器設計プラットフォームを「CR-8000シリーズ」として展開していく。

「CR-8000シリーズ」の大きな特徴は以下の通り。

・複数基板の設計、LSIとパッケージ/プリント基板の協調設計など、複数の設計対象を含むシステム全体の設計/検証/レビューが可能。

・各種設計プロセス間の連携はもちろん、ネットワークを介したコンカレント(同時並行)設計など設計の水平分業にも対応。

・図研のエンジニアリングPLM「DS-2」のデータベースをネットワーク経由で直接シェアすることができ、部品情報、ワークインプログレス(設計途上)の設計成果物管理、設計要件管理をより効率的に行うことが可能。

・現行「CR-5000シリーズ」のツールと設計データ、ライブラリが互換であり、「CR-5000」と「CR-8000」のツール群の混在運用が可能。

尚、「CR-8000 Design Force」の国内販売価格は、3Dモデリング・テクノロジー編集機能、コンストレインツドリブン設計機能、SI・PI・EMI解析エンジン、各種インテリジェント配線機能などを含む基本構成(Professionalバージョン)で980万円となっている。

2011.10.26

2011年10月25日、XilinxはFPGAの新製品「Virtex-7 2000T」の出荷開始を発表した。

「Virtex-7 2000T」は、スタックド・シリコン・インターコネクト技術を用いて複数FPGAを並べて繋ぐ「2.5D」と呼ばれる二次元の配置手法を用いた初のFPGAで、TSMCの28nm High Performance Low Power(HPL)プロセスで量産されている。「Virtex-7 2000T」には、68億トランジスタで実現される業界最大の2000万ASICゲート相当、200万ロジック・セルが集積されており、トランシーバーの最大速度は12.5Gb/s。Xilinxの最高峰ハイ・パフォーマンスFPGAとして出荷される「Virtex-7 2000Tに」は、通信/放送インフラをはじめ、ハイ・パフォーマンス・コンピューティングやASICプロトタイプ、エミュレーションなどでの利用が想定されている。

※画像はVirtex-7 200T のイメージ Xilinx提供

※画像はスタックド・シリコン・インターコネクト技術のイメージ図 Xilinx発表資料抜粋

2011.10.26

2011年10月25日、ARMは、2011会計年度第3四半期(2011年7-9月)の売上を報告した。

ARMの2011会計年度Q3 (2011年7-9月) の売上は、前年比22%増、前期(2011年Q2)比1.1%増の1億9230万ドルでまたしても四半期売上記録を更新した。四半期売上記録の更新はこれで6四半期連続となる。営業利益は4370万ドルで前年比約33%減だった。ARMの今年の売上累計(1月-9月)は5億6800万ドルで前年比26%増となっている。

ARMはこのQ3で新たに28件のプロセッサ・ライセンスを獲得(前Q2では29件)。その内14件は新規顧客だった。新規契約の大半は新製品のライセンスで、Cortex-Aシリーズのライセンスが9件、Cortex-Mシリーズのライセンスが14件だった。

また、ARMはQ3でCortex-AシリーズのフジカルIP「POP(Processor Optimisation Pack)」のライセンスを新たに4件獲得。この中には28nmプロセスのCortex-A15のPOPも含まれている。前期Q2で5件獲得していたGPU「Mali」の新規契約はQ3は2件だった。

※画像はARM発表資料より抜粋

Q3で出荷されたARM搭載チップの総数は全Q2とほぼ同じ約19億個で、うち約11億個はスマートフォンなどのモバイルデバイス向けに、約9億個はコンシューマーおよびクルマ向けで、コンシューマーおよびクルマ向けの出荷数は前年比50%増となっている。

売上の内訳を見ると、プロセッサ・ライセンスの売上は前年比41%増の5970万ドルで、プロセッサ・ロイヤリティの売上は前年比20%増の8420万ドルとなっている。ユニット出荷数ではARM11とCortexが前期に続き割合を増やし全体の31%となった(前Q2では28%)。

※画像はARM発表資料より抜粋

ARMは次期Q4売上をQ3とほぼ同一水準と予測。2011年合計売上は7億6800万ドル前後とみている。

2011.10.25

2011年10月24日、業界標準ツール「SpyGlass」をはじめとしたRTL解析ソリューションを手掛ける米Atrenta社は、Cadenceの「System Realization Alliance」に加盟した事を発表した。

発表によるとAtrentaは「System Realization Alliance」に加盟し、最初の活動としてCadenceと共同で高位合成ツール「C-to-Silicon Compiler」の生成するRTLのチェックに取り組む。具体的には、AtrentaのRTL解析ツール「SpyGlass」で使用する「高位合成用ルール」を作り、「C-to-Silicon Compiler」の生成するRTLの構文的な正しさ、パワー、テスタビリティ、クロック同期などのパラメーターをチェックする。

Atrentaは、Cadenceと共同で作成する「高位合成用ルール」は、「C-to-Silicon Compiler」の合成チェックの一部として機能し、そのサブセットはエンドユーザーも利用できるだろうとしている。

Cadenceは、これまで「C-to-Silicon Compiler」の合成チェックに関してCalypto社とのパートナーシップに力を入れていたが、CalyptoがMentorから高位合成ツール事業を獲得した為、高位合成ツールにおける競合企業となってしまった。そのような背景が今回のAtrentaとCadenceのコラボレーションを後押ししたと想像できる。

また、AtrentaとCadenceはいずれもARMおよびTSMCのフローでクオリファイを受けている事から、共同ソリューションを構築することで、ARMやTSMC顧客に対する他社ソリューションとの差別化を図る狙いがあるのかもしれない。

2011.10.25

2011年10月24日、バーチャル・プラットフォーム「OVP」を手掛ける英Imperasは、新たなプロセッサ・モデルのリリースを発表した。

発表によるとImperasは新たにXilinxの組み込みプロセッサ「MicroBlaze」のモデルをリリース。合わせてXilinxのアライアンス・プログラムにも加入した。

「MicroBlaze」のプロセッサ・モデルは既に「OVP(Open Virtual Platforms)」のWebサイトより無償で入手可能で、Imperasの提供するシミュレーター上で実行することができる。Imperasはシミュレーターと合わせてソフトウェア開発環境を有償で提供。ソフトウェア開発環境には、マルチ・プロセッサ/マルチ・コア/マルチ・スレッドの検証、解析、プロファイリングを可能とする解析ツール「M*VAP」が含まれている。

Imperasによると、既に実例としてOVPの「MicroBlaze」モデルと「ARM Cortex-A9MPcore」モデルを用いて、ARMとFPGAの統合プラットフォーム「Zynq-7000」のバーチャル・プラットフォームを構築した顧客もいるという。

尚、Imperasは同日、Cadenceとのコラボレーションを発表。CadenceのESL環境「Virtual System Platform」上でOVPのプロセッサ・モデルを利用できる事をあらためて強調した。

2011.10.25

2011年10月24日、TSMCは28nmプロセス製品の量産開始を発表した。

発表によるとTSMCの28nmプロセスは4種類あり、このうちHigh Performance(HP)、High Performance Low Power(HPL)、Low Power(LP)、の3種類のプロセスが量産を開始。残るHigh Performance Mobile Computing(HPM)については、2011年末までに量産開始予定としている。

TSMCによると既に28nm製品のテープアウト数は80以上で40nm時の倍以上という状況。と比較して2倍以上となっており、80製品以上がテープアウト済み。発表にはFPGA,GPU,モバイル向けSoCなど自社の先端製品をTSMC28nmプロセスで製造するAltera,AMD,NVIDIA,Xilinx,Qualcommがコメントを寄せている。

尚、かのAppleも次期A6プロセッサはTSMC28nmプロセスで製造予定と言われているが、つい先日、A6の製造は引き続きサムスンと報道された。また、現行のA5プロセッサでTSMCの製造(40nm)が開始され、そのままA6の製造(28nm)も進められるとする報道もあり、AppleによるTSMCへの製造委託に関しては情報が錯綜している。

2011.10.21

発表によるとAlteraの2011年Q3(11年7-9月)売上は、前年比約1%減、前期Q2比約5%減の5億2250万ドル。営業利益は前年比約15%減の1億8540万ドルという結果だった。

Alteraの売上減は同業ライバルのXilinxと同様、世界経済の悪化に影響を受けたもので、Alteraは9月時点でQ2以上としていた今期Q3の売上予測を下方修正していた。

地域別の売上を見ると北米市場での売上が前年比19%減と大きく落ちた。その一方で欧州売上は17%増と好調を示した。日本市場の売上は前年比1%減だった。

売上の内訳を見ると、新製品としてカテゴライズされるStratix V、Stratix IV、Arria II、Cyclone IV、MAX V、HardCopy IVといった製品群が前年比112%増と非常に好調。前Q2から出荷が開始された28nmFPGA、Stratix Vの売上が牽引していると思われ、新製品分野はAlteraの売上全体の27%を占めるまでになった。その一方で旧世代製品、PLD製品は前年比29%減と売上を落とした。分野別の売上では、ネットワーク、コンピューター、ストレージ分野が前年比50%増となり売上全体の20%を占めている。

AlteraはQ4の売上をQ3比7-11%減と予測している。

2011.10.21

2011年10月19日、Xilinxは2012会計年度第2四半期(2011年7-9月)の売上を報告した。

Xilinxの2012年Q2(11年7-9月)の売上は、前年同時期比、前期比ともに約10%減の5億5520万ドル。営業利益は前年比26%減の1億2630万ドルという結果だった。

今期の売上減という結果は世界経済状況の悪化によるところが大きく、Xilinxは7月1時点で示したQ2売上予測を9月に下方修正していた。

地域別売上では北米とアジアがそれぞれ前年比2ケタ減となり大きく売上を落とした。その一方で日本市場は前年比10%増の伸びを示した。分野別の売上構成を見ると主力の通信分野の売上が前年比18%減となっており、同社の総売上に大きく影響している事が分かる。

製品の分野別売上を見ると、新製品分野だけが前年比増。今期からVirtex-7, Kintex-7が新たに新製品としてカテゴライズされている。

Xilinxは次期2012年Q3(11年10-12月)の売上は今期の-3%から-8%と予測している。

2011.10.20

2011年10月18日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftとバグ原因解析ツール「OnPoint」を手掛けるVennsa Technologiesは、両社製品の連携を発表した。

発表によると両社は、バグ原因の解析ツール「OnPoint」とデバッグ環境「Verdi」を連携させ、バグ原因の解析、特定、修正という一連の作業を繋ぐシームレスなフローを構築。具体的には、「Verdi」上から「OnPoint」にアクセスする形を整えた。

この連携は、「Verdi」へのツール接続や「Verdi」向けのカスタム・アプリ開発を容易化する、SpringSoftの「Verdi Interoperability App ( VIA ) platform」によって実現されるもので、今回用意された「Verdi」と「OnPoint」の接続インタフェースは、SpringSoftの運営するWebサイト

「VIA Exchange」上でユーザーに無償公開される。

多くのハードウェア設計者がデバッグツールとして利用する「Verdi」の強力なグラフィカル環境に「OnPoint」のバグ原因の解析機能が加われば、デバッギングの生産性は大きく向上するだろう。

2011.10.20

2011年10月19日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automationは、 Deloitte社の「2011 Technology Fast 500」に選出されたことを発表した。

プレスリリース文

http://www.berkeley-da.com/news/news_pr/news01_pr_2011_10_19.html

Deloitte社は国際的な会計事務所で、優秀なテクノロジー企業の成長率を過去5年間の収益(売上高)で順位付けした「2011 Technology Fast 500」を地域別に発表している。

今回、Berkeley Design Automationは、北米およびカナダ地域における成長率の高いテクノロジー企業500社の1社としてランキングされた。

発表によると、Berkeley Design Automationの2006年-2010の5年間の売上成長率は787%。ワールドワイドで半導体関連の顧客110社を獲得しているという事で、この実績から「2011 Technology Fast 500」に選ばれた。

Berkeley Design Automationは、2006年に最初の製品であるPLL向けノイズ解析ツール「PLL Noise Analyzer」をリリース。同製品により実績を固め、翌2007年にリリースしたアナログ/ミックスシグナルおよびRF設計向けの回路シミュレーター「Analog FastSPICE」が大ヒットし、EDA業界で一目置かれる存在となった。

2011.10.19

2011年10月18日、ライブラリの開発ソリューションを手掛けるデンマークのNangate社は、同社製品を富士通セミコンダクターが採用した事を発表した。

発表によると富士通セミコンダクターは、28nmSoC設計環境向けにNanGateのライブラリ開発環境「NanGate Library Creator」とレイアウト・デザインの解析およびポスト・ルート最適化ツール「NanGate Design Optimizer」の2製品を採用した。NanGateの「NanGate Library Creator」は同社の提供するライブラリ開発で使用されているツールで、「Design Optimizer」と併用することで飛躍的に結果を改善することが可能。既存のEDAフローにシームレスに取り込む事ができるという。

2011.10.19

2011年10月17日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、同社の「Verdi」自動デバッグシステムに関する、アドバンテストとの複数年包括契約の締結を発表した。

発表に寄せられたアドバンテスト社 設計推進統括部 設計技術部 部長 佐藤新哉氏のコメントによると、アドバンテストでは設計検証作業の効率化のためにESL設計環境を整備しており、その設計フローにおいても、高位合成後のRTLの解析等、様々なデバッグ作業において「Verdi」を標準ツールとして活用していくという。

今回の発表において、アドバンテストが使用する高位合成ツール名は触れられていないが、同社はかつてNECの高位合成ツール「CyberWorkBench」のユーザー・フォーラムでその導入効果を発表している。

2011.10.19

2011年10月17日、TSMCとCadenceは、両社共通の顧客に対し、ライブラリ・キャラクタライゼーション・リファレンス・キットを提供すると発表した。

発表によると、両社の提供するライブラリ・キャラクタライゼーション・リファレンス・キットは、スタンダード・セル・ライブラリの再キャラクタライゼーションの加速を狙ったもので、ユーザーはTSMCのTSMC?Onlineからダウンロードして同キットを利用する事が可能。このリファレンス・キットを用いてCadenceの「Cadence Library Characterizer」でライブラリの再キャラクタライゼーションを実施すれば、TSMCと同じ環境・制約による一貫したキャラクタライゼーションが可能となる。

今回提供が開始されるライブラリ・キャラクタライゼーション・リファレンス・キットは、Cadenceが今年5月に買収を完了した米Altos Design Automation社のキャラクタライゼーション・ツール「Liberate」の技術が活かしたもので、TSMCの40nmおよび28nmプロセス向けに提供。旧Altos社の「Liberate」は、2005年にリリースされた比較的新しい製品であるが大手中心に多数の導入実績を誇るツールで、TSMCの40nmプロセスのリファレンス・フローにも採用されていた。

2011.10.19

2011年10月18日、TSMCとARMは、業界初となる20nmマルチコア・プロセッサ 「ARM Cortex-A15」をテープアウトしたことを発表した。

発表によるとTSMCとARMの両社はTSMCの20nmデザインエコシステム「Open Innovation Platform(OIP) 」を活用して、RTLからテープアウトまでを6か月で達成した。

「Open Innovation Platform(OIP) 」には、ESL設計からRTL設計、インプリメント、サインオフまでチップ設計に関するあらゆるソリューションが含まれているが、今回の20nm「ARM Cortex-A15」のテープアウトにあたり、TSMCとARMはCadenceのRTL-to-signoff flowを利用。具体的なツール名としては、アナログ/カスタム環境「Virtuoso」やデジタル・インプリメント環境「Encounter」の名が挙がっているが、その他にもCadenceのサインオフツールが利用されたようだ。ARMとCadenceは、「ARM Cortex-A15」向けのデザイン・フローの構築に向けて1年半前からコラボレーションを進めてきたという。

尚、TSMCの20nmプロセスを利用する事により「Cortex-A15」は、前世代のプロセスと比べ2倍以上の性能向上を達成。ARMは今回のテープアウトを基に、特定のTSMC20nmプロセス技術に即したPPA(Power、Performance および Area)モデルに合わせて物理IP技術を最適化し、ARMのユーザーに提供する「Cortex-A15 Processor Optimization Pack (POP)」の仕様開発の促進を図るという。

2011.10.13

2011年10月12日、バーチャル・プラットフォーム「OVP」を手掛ける英Imperasは、新たなプロセッサ・モデルとして「V850」モデルを開発した事を発表した。

発表によるとImperasはルネサスエレクトロニクスの協力の下で、新たに「V850」ファミリのOVP Fast Processor Modelsを開発。同モデルはImperasの提供するシミュレーター「OVPsim」で利用することができる。同シミュレーターは大学関係には無償で、企業向けには有償で提供される。

※OVPで提供される全てのモデルは無償。OVPを用いたソフト開発環境は有償。

Imperasの「OVP」をはじめとするバーチャル・プラットフォームは、ソフトウェア開発向けのソリューションとして実用が進んでおり、電機メーカーに限らず自動車メーカーや自動車部品のサプライヤも積極的にその活用に取り組んでいるが、車載ECU用のマイコンとして広く利用されているルネサスの「V850」のモデルは、これまでSynopsysのシミュレーター「CoMET」にしか用意されていなかった。

今回のImperasの発表には、車載システムを開発するスウェーデンのNIRA Dynamics社が「既存のソリューションよりも50倍高速」とコメントしている。

Imperasは2010年にも同様の「V850」モデルのリリースを発表しているが、当時は独自開発のモデルという位置付けで、ルネサスエレクトロニクスの協力については触れられていなかった。今回発表された「V850」モデルの開発にあたり、ルネサスエレクトロニクスは検証面で協力しているようだ。

尚、Imperasは今回の発表と合わせて更に2件の発表を行った。

一つは、Imperas社製品の日本国内の販売を東京ナノファーム社が担当するという

アナウンス。もう一つは、設計コンサルティングおよび設計サービスを手掛けるエッチ・ディー・ラボ社が、同社のSystemCトレーニング・コースにおけるバーチャル・プラットフォーム向けモデル開発環境として「Open Virtual Platforms」を採用したという

アナウンスである。

2011.10.12

2010年9月30日、Mentorは、富士通セミコンダクター・ヨーロッパが「Mentor Embedded Sourcery Codebench」をFM3 Cortex-M3マイクロコントローラおよびハードウェア評価ボードの開発環境として採用したことを発表した。

Mentorの「Sourcery CodeBench」は日本では馴染みが薄いかもしれないが、GNUツールチェーンのデファクトとなっているソフトウェア開発環境で、2010年11月にMentorがその資産を買収するまでは、CodeSourcery社から有償/無償の環境が提供され、ワールドワイドで多数のユーザーを抱えていた。「Sourcery CodeBench」は様々なCPUアーキテクチャをサポートするソフトウェア開発環境として、ARM,MIPS,PowerPC,SHなど各種CPUベースのプラットフォームをサポートしており、Mentorによって提供されている現在も月8000件以上のダウンロード実績がある。Mentorによると世界の大半のSH4ユーザーは「Sourcery CodeBench」を利用しているそうだ。

今回の富士通セミコンダクター・ヨーロッパの発表は、同社のARM搭載マイコン「FM3」を販売するにあたり、顧客に提供する開発環境としてMentorの「Sourcery CodeBench」を採用したというもので、富士通「FM3」のユーザーは、組込みソフトウェア開発においてMentorの「Sourcery CodeBench」を利用し、Mentorのサポートを受けることが可能となる。富士通としても「Sourcery CodeBench」を採用することで、これまでのように自前のマイコン開発環境を用意し、メンテ、サポートする必要が無くなるという大きなメリットを手に出来る。

このようなMentorと半導体ベンダとのパートナーシップは、組込みOSやUI開発などMentorの組込みソリューションをベースにこれまでも実現されていたが、「Sourcery CodeBench」が加わった事でよりサービスの幅が広くなった。そこでMentorは、「Mentor Embeddedハードウェア・イネーブルメント・プログラム」と名付けてハードウェア・ベンダ向けの組込みサービス・ソリューションの展開に力を注ぎ始めている。現在のところ大きく下記5つのサービスを展開中で、既にルネサス、富士通、Freescale、Texas Instruments、Qualcommなど大手各社がパートナーとしてMentorのソリューションを利用している。

【Mentor Embeddedハードウェア・イネーブルメント・プログラムの主要サービス】

・Linuxサービス 商用Linuxプラットフォームの構築を中心としたサービス

・Androidサービス Android環境を構築を中心としたサービス

・Sourceryサービス GNUツールチェーン関連サービス

・Inflexion UIサービス ユーザ・インタフェースの作成を中心としたサービス

・Vertical Platformサービス 垂直型の組込みプラットフォーム作成サービス

このように「Sourcery CodeBench」はMentorの組込みソリューションの強化に大きな役割を果たしているが、その一方で、Mentorの組込みソリューションとEDAソリューションを繋ぐという別の役割も果たしている。

今年サンディエゴで開催された48回DACにて、Mentor Embedded Software Division GMのClenn Perry氏に聞いたところ、Mentorは、「Sourcery CodeBench」をリリースするにあたり「System Analyzer」というグラフィカルな解析機能を新たに開発し、「Sourcery CodeBench」に追加した。同解析機能は組込みソフトに限らず組込みシステム全体の可視化を実現するもので、マルチコア・システムにも対応。Mentorはこの新しい解析機能を備えた「Sourcery CodeBench」をFPGAボードや同社のバーチャル・プロトタイプ環境「Vista」、エミュレーション環境「Veloce」と繋げるためのAPIを開発済みで、既にこれら環境の接続は実現されているとの事。同環境を利用すれば、ソフトウェア開発者は「Sourcery CodeBench」からハードウェアに容易にアクセス出来るようになり、システムのパフォーマンスや消費電力を考慮したソフトウェアの最適化も可能になるという。

※画像はMentor提供の画像 「System Analyzer」の概要

※画像はMentor提供の画像 「Sourcery CodeBench」とハードウェア開発環境の接続

※画像はMentor提供の画像 「Sourcery CodeBench」と「Vista」の連携例

Mentorは、約2年前までは組込みRTOS「Nucleus」にフォーカスした組込みビジネスを展開していたが、その後AndroidやLinuxをターゲットにオープンソースOSのプラットフォーム開発にシフト。組込みUIソリューションやオープンソース・ツールも取り込み、今ではオープンソース・ベースの組込みソリューションを展開するベンダとして大きな存在となっている。この動きに合わせてMentorは日本における更なる事業展開を目指し、日本の事業体制も強化しており、国内ユーザー向けに「Sourcery CodeBench」の日本語サポートを行う体制を整えているとの事。また、EDA製品としてESL分野にカテゴライズされていた「Vista」などの製品は、組込みソフトウェア製品として同社の組込み事業部門に移管されているという。

※Embedded Software Division GMのClenn Perry氏は、Mentorに買収された旧Summit Designの出身である。

※メンター・グラフィックス・ジャパン株式会社

2011.10.12

2011年10月11日、Alteraは、ARMベースの28nmFPGA「SoC FPGA」ファミリを発表した。

発表によると「SoC FPGA」は、Alteraの28nmFPGA上にARM Cortex-A9 MPCoreプロセッサ、ECC付きメモリ・コントローラ、ペリフェラル、広帯域幅インタコネクトを搭載したシングル・チップで、低コストFPGA「Cyclone V」ベースと、AlteraのミッドレンジFPGA「Arria V」をベースにしたものの2品種が用意される。

「SoC FPGA」に搭載されるARMプロセッサは、デュアルコアで最大動作周波数は800MHz、様々な汎用ペリフェラルで構成されるプロセッサ・システムは、4000DMIPSのピーク性能を1.8ワット未満の消費電力で実現できる。また、このARMベースのプロセッサ・システムとFPGA部は、高スループット・データ・パスによって相互接続されており、データの一貫性を保ちながら125Gbpsを超えるピーク帯域幅を実現。プロセッサとFPGA部は別々に電源供給される仕組みとなっており、順番を問わずコンフィギュレーションおよび起動が可能で、稼働中にFPGA部をパワーダウンすることもできるという。

「SoC FPGA」の開発環境としては、FPGA部のハード設計は「Quartus II」、ARM上のソフト開発は既存の各種ARM開発環境、FPGAとARMベース・プロセッサ・システムの統合には「Qsys」を利用する事が可能で、「Qsys」ではARMの「AMBA AXI」インタフェースもサポートしている。更にAlteraは「SoC FPGA」向けのソフトウェア開発環境として、今回新たな開発ツール「SoC FPGA Virtual Target」を用意した。

「SoC FPGA Virtual Target」は、「SoC FPGA」の開発ボードを仮想化したソフトウェア開発向けのバーチャル・プラットフォームで、Synopsysのバーチャル・プロトタイピング・ソリューションをベースに開発されたもの。このバーチャル・プラットフォームには、ARM Cortex-A9 MPCoreプロセッサ、システム・ペリフェラル、DDR SDRAM、Flashメモリ、Virtual I/Oなど、各種コンポーネントのシミュレーション・モデルが用意されており、ソフトウェア開発者はPC上で動かせる仮想ボードとしてソフト開発に利用する事が可能。GNUツール、ARM RVDS、ARM Development Studio 5 (DS-5)、Lauterbach TRACE32Rデバッガ、Wind River Workbenchといった開発ツールをサポートしており、既存のソフトウェア開発環境を併用しながら実機ベースの開発よりも遥かに高度なシステムの可視性と制御性を手にする事ができる。

また、「SoC FPGA Virtual Target」には、「FPGAイン・ザ・ループ」と呼ばれるオプションの拡張機能が用意されており、「SoC FPGA Virtual Target」とFPGA開発ボードを接続することが可能で、プロセッサ・システムとユーザー自身がデザインしたFPGAベースIPの両方をターゲットにするアプリケーション・ソフトウェアを開発することもできる。

「SoC FPGA Virtual Target」は、当然ながら実機の「SoC FPGA」開発ボードと機能的に同等で、バイナリおよびレジスタの互換性を持つため「SoC FPGA Virtual Target」上で開発したソフトウェアは、容易に実機ボードに移行する事が可能。組込みOSとしてLinuxとVxWorksをサポートしている。

尚、「SoC FPGA」の出荷開始は2012年後半の予定で、米国内販売価格は15ドル未満から。「SoC FPGA」向けの新たな開発環境「SoC FPGA Virtual Target」は既に入手可能で、オプションの「FPGAイン・ザ・ループ拡張」は、来年初めから提供が開始される予定となっている。

2011.10.11

2011年10月3日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、同社製品「Verdi」向けのカスタム・アプリの開発・利用促進サイトを開設した事を発表した。

SpringSoftの開発したWebサイトは、「VIA Exchange」という名称でURLは以下の通り。

http://www.via-exchange.com/

「VIA Exchange」は、SpringSoftの提供する業界デファクトのデバッグ・ツール「Verdi」向けのカスタム・アプリケーションの開発および利用を促進するために立ち上げられたWebサイトで、名前とメールアドレスだけのユーザー登録で誰もが無料で利用することができる。

サイト上には大きく下記4つのメニューがあり、サイトの利用者は「Verdi」向けのカスタム・アプリケーションを開発するノウハウやライブラリを入手できる他、サイト上の無償アプリケーションやスクリプトをダウンロードする事が可能。更に独自に開発したカスタム・アプリケーションをサイト上のコミュニティに公開(共有)したり、ユーザー同士の交流を図ることもできる。

■VIA Exchangeのメニュー

・Getting Started カスタム・アプリの開発に関する情報

・Download ライブラリ、カスタム・アプリのダウンロード

・Share カスタム・アプリの公開(申請)

・Forum ユーザー交流スレッド

※画像はVIA Exchangeトップページのスクリーンショット

今回のSpringSoftによる「VIA Exchange」立ち上げの肝は、「Verdi」のデータベースとGUIのインタフェースが公開されたという事で、これによりユーザーは業界デファクトとなっているSpringSoftのデバッグ用データベース「KDB(Design Knowledge Database」と「FSDB(Fast Signal Database)」にアクセスできるようになる。すなわち「Verdi」ユーザーは、KDB/FSDB各データベースの情報を活用した設計や、設計/検証用の独自のアプリケーション開発が可能となるほか、「Verdi」のGUIのカスタマイズも可能となる。

これまでSpringSoftは、サード・パーティーや一部ユーザーにインタフェースを公開し、サードパーティーとのツール連携や顧客におけるカスタム・アプリケーション開発に対応してきていたが、日本国内だけでも2000を数えるという膨大なユーザー数を考えると、「Verdi」に関する「細かなカスタム要求」に個別に対応するよりも、APIを公開して「ユーザー自身にカスタマイズしてもらう」方がより効率的と判断した。そのためのインフラとなる「VIA Exchange」は、ユーザーにとっても情報やツールの入手場所として利用メリットは非常に高く、まさにWin-Winのインフラと言える。

既に運用が開始されている「VIA Exchange」には、SpringSoftおよび同社パートナーが用意したKDB/FSDBアクセス関数やスクリプト/カスタム・アプリなど計100種近くがアップロードされており、今後は一般ユーザーが開発したアプリの公開なども順次進められる予定。(※アプリ公開にあたりSpringSoft側でテストなどのチェックが実施される)

SpringSoft日本法人社長の河原井 智之氏によると、これまで日本ユーザで多かった「Veridi」関連のカスタム要求は、ユーザー独自の機能追加、データベース格納情報の設計利用、GUIのカスタマイズなどで、これら要求の殆どは「VIA Exchange」を利用することで解消可能との事。Web上のコンテンツだけでは要求が満たされない場合は、要望に応じてコンサルティングやトレーニングのサービスも提供可能だという。

2011.10.11

トランジスタレベルの統計的ばらつき解析ソリューションを手掛けるカナダのSolido Design Automation社がTSMCと共同でWebinarを開催する。

Webinarでは、最新のTSMC AMSリファレンスフロー2.0にも採用されたSolidoのばらつき解析ツール「Variation Designer」の詳細をはじめ、NVIDIA,Qualcomm,HiSiliconらによるユーザー事例の紹介も予定されている。

ここのところEDAベンダによるWebinar開催が活発化しつつあるが、TSMCとのダブルネームでの開催は珍しい。Webinarは日本時間10/13 10:00amから。

2011.10.11

2011年10月7日、Synopsysは、STAおよびSSTAを手掛けるEDAベンチャーExtreme DA社の買収を発表した。

※STA:static timing analysis(静的タイミング解析)

※SSTA:statistical static timing analysis(統計的タイミング解析)

今回の買収に関する詳細な条件などは明らかにされていないが、Synopsysは10月6日にExtreme DAの買収手続きを完了したとしている。

Exteme DAは、2005年に業界初となる商用SSTAツール「GoldTime」をリリースし、その後同ツールに、スタティックタイミング解析(STA)とシグナルインテグリティ解析(SI)も取り込み、既存の「STAソリューションの置き換え」を狙う統合的なタイミング解析ソリューションとして製品展開を進めていた。

2010年は過去最高の売上を記録し、ファブレス上位10社のうち4社が「GoldTime」を採用するなど(2011年1月時点での実績)、ビジネスは好調だった様子で、配置配線ツールのATopTech社とのコラボレーションなどにも取り組んでいた。

Synopsysは「PrimeTime」という業界デファクトのSTAを提供しており、同分野のトップシェアを確保しているが、今回買収したExtreme DAのようにその牙城を狙うベンダが常に存在しており、最近ではMagmaの「Tekton」がそのパフォーマンスの優位性をアピールしている。

2011.10.06

2011年10月6日、Cadenceは、富士電機による「Virtuoso Accelerated Parallel Simulator」の採用事例を発表した。

発表によると富士電機は、マルチCPUに対応した分散シミュレーション技術を持つCadenceのSPICE精度シミュレーター「Virtuoso Accelerated Parallel Simulator」を利用することによって、パワーマネジメントICの開発およびシステム全体検証の期間を25パーセント削減する事に成功。設計全体のプロセスを「Virtuoso Accelerated Parallel Simulator」ベースに切り替え、更にVerilog-A モデルによるIPを多数併用することで、検証時間の短縮を図ることができたという。

同件に関する詳細については、10月13日に開催されるCadenceのプライベート・イベント「CDNLive! Japan 2011」で発表される予定との事。

2011.10.06

2011年10月6日、Cadenceは、アナログ・ミックスシグナル半導体にフォーカスしたドイツのファウンダリX-FAB社が、同社の全プロセスノード向けに「Cadence Physical Verification System」を認定したと発表した。

「Cadence Physical Verification System」は、DRCとLVSから成るCadenceの物理検証ソリューションで、デジタルおよびアナログのインプリメント環境と密接に統合されており、サインオフ検証だけでなく、インプリメント作業を進めながらの「in-design 」検証を実現することが可能。設計と検証のイタレーションを減らし、作業工数の削減と設計品質の向上に貢献する。

今回、X-FABは1.0?m-0.18?mまで10種以上ある同社の全てのプロセス・ノードにおいて、「Cadence Physical Verification System」のシリコン精度を承認。物理検証ツールとしての精度と合わせて、その生産性の高さにお墨付きを出した格好だ。

Cadenceはアナログ/ミックスシグナルの設計環境において強力なシェアを持っているが、今回の件はCadenceの「物理検証ツール」が、ミックスシグナル半導体ファウンドリの大手「X-FAB」によって認定されたという事で、多数存在するという同ファンドリの日本ユーザーにとってもインパクトのある話である。

2011.10.06

2011年10月5日、米EDA Consortiumは、2011年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

EDACの発表によると、2011年Q2(4月-6月)の世界のEDA売上総額は、前年比17.6%増、前Q1比0.6%減の14億3810万ドル。この四半期の平均アベレージは、前年比16.3%増で好調な売上を維持した。半導体関連各社が軒並みQ3売上予測の下方修正を迫られる中、次のQ3の売上統計がどう変化するのか注目される。

分野別売上でみると、全ての分野で前年比増を達成。CAE,PCB,IPは2ケタ増となった。中でもIP分野は22.6%増と非常に好調。この1年間の平均アベレージは前年比25.1%増となっている。

地域別でみると、全ての地域で前年比増を達成。中でも北米とアジアその他地域が2ケタ増を記録した。この1年間の平均アベレージはアジアその他地域が最も高いが、このQ2売上に関しては、北米市場が前年比21.1%増と最も高い成長を示した。

2011年Q2時点でのEDA業界の従業員数は26721人で、前期Q4比1.0%増となっている。

2011年Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 5億4980万ドル 19.8%Up

■IC Physical Design & Verification分野 2億8690万ドル 5.8%Up

■IP分野 3億6770万ドル 22.6%Up

■サービス分野 8880万ドル 19.9%Up

■PCB/MCM分野 1億4490万ドル 21.7%UP

2011年Q2地域別の売上と昨年同時期との比較は以下の通り。

■北米 6億2610万ドル 21.1%Up

■ヨーロッパ 2億4650万ドル 8.8%Up

■日本 2億5390万ドル 17.8%Up

■アジアその他地域 3億1160万ドル 18.1%Up

2011.10.05

2011年10月3日、米SIA(Semiconductor Industry Association)は、2011年8月の世界半導体売上高を発表した。

SIAの報告によると、2011年8月の世界半導体売上高は前年同時期比約2.2%減、前月比約0.7%増の250億3000万ドルという統計結果となった。

7月売上よりも若干売り上げ増となった要因は、PCおよびタブレット需要、日本市場の回復、自動車向け半導体の好調などで、前月比としては日本市場が最も伸び率が高く5.5%増となったが、前年比では日本市場が9.4%減と最下位で、市場は回復しつつあっても前年の水準には程遠い事が分かる。前年比、前月比ともにプラスとなっているのは、アジア市場だけである。

2011.10.03

2011年9月29日、SynopsysとARMは、バーチャル・プラットフォーム用のARMプロセッサ・モデルに関する両社の契約について発表した。

発表によるとARMは、同社の開発・販売するバーチャル・プラットフォーム用のプロセッサ・モデル「Fast Models」の販売権ならびに、とARM Cortexプロセッサ・ファミリーのモデル開発権をSynopsysに付与する契約をSynopsysと締結した。

ARMの「Fast Models」は、ソフトウェア開発向けに用意されるARMプロセッサの高抽象度モデルで、ARMによってモデルの機能的な等価性は保証されている。これまで同モデルは、ARMまたはESLツールを提供するCarbon Design Systems社が販売していたが、新たにSynopsysからも入手する事が可能となった。

またSynopsysは今回の契約により、TrustZoneやVector Floating Point(VFP)などのARMの最新テクノロジも組み込んだモデルの開発が可能となった。SynopsysはARMの「Fast Models」には無いタイミング情報を持ったARMプロセッサの高抽象度モデル「ファスト-タイムド・モデル」の提供を計画しており、それをバーチャル・プラットフォーム上で活用すればタイミング精度の高速なシステム検証が可能となる。

Synopsysによると、Cortexプロセッサの「Fast Models」は既にSynopsysより出荷中。「ファスト-タイムド・モデル」については未だ出荷されておらず、情報提供が開始されている状態だという。これらTLMモデルに関する情報は、Synopsysが開設したウェブサイト「TLMCentral」を通じて入手する事ができる。

2011.09.30

2011年9月29日、Synopsysは、SystemC TLMモデルのポータルサイト「TLM Central」のオープンを発表した。

発表によると開設されたWebサイト「TLM Central」のURLは以下の通り。

※画像はTLM CentralのTOPページのスクリーンショット

サイトにアクセスすればそのコンテンツは一目瞭然だが、「TLM Central」はSystemC TLMモデルの流通を促すオープンなポータルサイトで、サイトへのアクセスは完全に無料。名前、Eメールアドレスのみの簡単なユーザー登録をすれば、誰でもサイト上にTLMモデル及びモデル情報をアップロードしたり、無償モデルをダウンロードしたりできる。

(※ユーザー登録はFacebookのアカウントを利用することも可能。)

既にサイト上には670種に及ぶモデル情報が登録されており、利用者はそれらモデルをモデルの種類や抽象度、アプリケーション分野などから検索する事が可能で、立ち上げたSynopsys自身も有償/無償の多数のモデル情報をアップロードしている。有償モデルに関してはリンク情報から問い合わせを行う事が可能な仕組みとなっている。

またサイト上にはユーザー同士の交流を促すフォーラムも用意されており、欲しいモデルをリクエストする仕組みや、モデルに関するFAQコーナーもある。更にフォーラムを通じて、モデル作成やモデルを用いたバーチャル・プロトタイプに関する専門知識などを入手することも可能となっている。

※画像はSynopsys提供のデータ。TLM Centralの概要説明。

Synopsysによると「TLM Central」は、全てのTLMユーザーにオープンなインフラとして提供されるサイトで、サイトを通じた情報のやり取りはユーザー任せで完全に自由。仮に競合ベンダであっても自由に情報・モデルをアップロード可能で、その内容に関してSynopsysがチェックを行うような事は無い。

「TLM Central」は、言わば「TLM」に特化した課金システムの無い「Android Market」のようなもので、有償/無償を問わず誰もが開発したモデルをアップロード可能。モデル利用者は多数のモデル情報の中からニーズにあったモデルを探すことができ、モデル開発者は「TLM Central」を通じて無償モデルを提供し、有償モデルの販売に結びつけるなどジネスの場としても利用できる。

このようなサイトが生まれる背景としては、昨今、ソフトウェア開発を主たる目的としたバーチャル・プラットフォームの利用ニーズの増加があり、バーチャル・プラットフォームの作成・実行環境の大きなシェアを握るSynopsysとしては、オープンなモデル流通インフラを作る事で、ユーザーやサードパーティーによる「利用可能なTLMモデルの流通」を活性化したいという狙いがある。バーチャル・プラットフォームを利用する上で必要不可欠な各種モデルをEDAベンダ1社で全て用意する事は事実上不可能だからだ。

また、バーチャル・プラットフォームのユーザーは、その利用価値の高さを認識しつつも、モデルの用意で苦労するケースも多く、このようなサイトの登場によって、単なる情報入手だけではなく、モデル入手の機会やエンジニア同士のコミュニケーションの機会が増えることは非常に嬉しいはずで、EDAベンダやIPベンダのメリットだけではなく、ユーザーのニーズにも呼応するインフラとして「TLM Central」の存在意義は高い。

SystemCの利用では依然世界をリードしていると言える日本のエンジニア達にも、サイトを通じたモデル流通、情報発信、コミュニケーションに積極的に参加して頂き、TLMを取り巻くエコシステムを盛り上げて頂きたい。

尚、開設された「TLM Central」に対して、早速下記の関係各社が賛同のコメントを寄せている。

・ARM

・Arteris

・Carbon Design Systems

・CEVA

・National Chip Implementation Center

・Doulos

・Forte Design Systems

・HCL Technology

・hdLab

・Imperas

・ITRI

・Kasura

・MIPS

・OCP-IP

・OSCI

・RICOH

・RWTH Aachen University

・SONICS

・Synopsys

・Tensilica

・TI

・Vayavya Technology

・VLSI Test Lab

・VDC Research

・Vivante

2011.09.29

2011年9月28日、NECは、変動する大量の時系列データをリアルタイムで処理できるハードウェア設計技術の開発を発表した。

発表によるとNECは、株価データの分析など金融業界のシステムで活用されている「複合イベント処理」をハードウェア化する技術を開発。従来ソフトウェアで行われていた「複合イベント処理」をハードウェアで行う事で、約50倍の高速化を実現した。

具体的には、「複合イベント処理」をハードウェア化するために、文字列の正規表現を関数に応用した「関数の正規表現」を開発。それを用いることで、正規表現による一致処理と関数による計算処理を同時に行う独自のハードウェア処理機構を実現した。

また、ハードウェア化にあたっては、NECの高位合成ツール「CyberWorkBench」を利用することで、ユーザが独自のデータ分析・処理の関数をC言語でプログラミングするだけでハードウェアを実現できる形にした。

尚、詳細は不明だが、発表文には「C言語を用いてユーザが自由に回路を書き換えできるハードウェアを利用」とあり、「Cyber Workbench」とFPGAを組み合わせてハードウェア化を実現しているようだ。(NECは「CyberWorkBench」のFPGA専用版の販売を今年8月から開始している。)

NECはこの成果をギリシャで開催された「International Conference on Field Programmable Logic and Applications」にて、さる9月5日に発表。今後も、ハードウェアを活用したリアルタイム分析技術の研究開発に積極的に取り組んでいくという。

2011.09.28

2011年9月28日、Cadenceは、ST-EricssonがCadenceのミックスシグナル・ソリューションを使用して生産性を10倍向上したと発表した。

発表によるとST-Ericssonは、携帯電話向けの40nmベースバンドSoCの設計にCadenceのカスタム・アナログ統合環境「Virtuoso」とデジタル・インプリメンテーション環境「Encounter」を使用し、65nmでのチップ開発と比較して設計期間を10分の1に短縮。ST-Ericssonの担当者によると、Cadenceツールの機能もさることながら、アナログおよびデジタル設計の単一データベースとして「OpenAccess」を初めて使用した事で、チーム設計の進行において驚くほど大きな時間短縮を実現できたという。

今回使用されたCadenceのツールは以下の通り。

・カスタム/アナログ統合環境「Virtuoso Analog Design Environment XL」

・SPICE精度シミュレーター「Virtuoso Accelerated Parallel Simulator」

・フルチップ・ミックスシグナル・シミュレーター「Virtuoso AMS Designer」

・カスタム/アナログ・レイアウト・ツール「Virtuoso Layout Suite XL」

・寄生抽出ツール「Cadence QRC Extraction」

・デジタル・インプリメント環境「Encounter Digital Implementation System」

2011.09.27

2011年9月26日、LSI機能検証ソリューションを手掛けるCMエンジニアリングは、「ワイヤレスマコン開発キット」の発売開始を発表した。

CMエンジニアリングの「ワイヤレスマイコン開発キット」は、UHF帯の無線通信機能を有したCPU搭載のFPGA評価ボードで、近距離特小無線機能をマイコンに搭載したいというニーズを狙ったもの。

ボード上にはARM8051を搭載するActelのミックスド・シグナルFPGA「Fusion」、オリジナルの通信プロトコルIP、RFIC、各種ペリフェラルが装備されており、小電力のニーズも意識して単三電池でも駆動可能。購入後すぐに駆動して利用することができる。

※画像はCMエンジニアリングのFPGAボード

ユースケースとしては、無線通信のテストなどの他に、ARM上にアプリケーションを搭載して既存製品の無線化を実現したり、FPGAの空き領域利用した通信機能の強化やアプリケーションのハード化等、近距離特小無線機能を用いた無線システムの様々な評価利用が想定されており、CMエンジニアリングでは評価されたシステムの商用化(小型モジュール化、IC化)もサポートしているという。

CMエンジニアリングは、検証サービスやIPベース設計サービスを通じて確立した独自の「検証技術」の他に、「無線通信技術」や「アナログ設計技術」も強みとしている。同社の河井社長によると、設計面でのソリューションでは自社の強みを活かしたIP製品の提供にも注力しているという事で、今回製品化した「ワイヤレスマイコン開発キット」の他に、既に同社ではOFDM、DSSS、MACといったカスタマイズ可能な無線IPコアを提供中。これからは「いかにIPを使いこなすかが設計の鍵」という河井社長の持論に則り、自社製IPの開発に限らず顧客の保有するIPの最適化などにも取り組み、最終的には自前のIPベース設計技術を駆使したオリジナル・チップの開発も視野に入れているという。

尚、CMエンジニアリングでは、今後920MHz帯域対応版や自社RFIC搭載版の「ワイヤレスマイコン開発キット」も開発予定との事。提供中の検証キットと同じく同社の評価ボードの開発には「サクっと使える」というコンセプトが根底にあるようだ。

2011.09.22

2011年9月21日、Mentor Grapphicsとマスク描画装置、マスク検査装置を手掛けるニューフレアテクノロジー社は両社のコラボレーション強化を発表した。

今回発表された両社のコラボレーション強化は、高度なマスク描画の実現を目的としたもので、Mentorのマスク作成ほか各種マスクデータ準備ツールやフラクチャリング・ツールの共同販売とサポートを推進するもの。

具体的には、ニューフレアテクノロジーのマスク描画装置「EBM-3000」から「EBM-8000」シリーズで使用される以下のツールがその対象となっている。

・Calibre FRACTUREt

・Calibre FRACTUREv

・Calibre MDPmerge

・Calibre MDPverify

・Calibre nmMPC

・Calibre MDPview

2011.09.22

2011年9月20日、Mentor Grapphicsは、同社のDFTツール「Tessent TestKompress」および「Tessent FastScan」の新機能を発表した。

今回の両製品の新機能の中心となるのは、Mentorが新たに開発した「ユーザ定義故障モデル(UDFM)」とそれを用いたセル対応ATPG機能で、これらを活用することで従来手法では検出の難しかった標準セル内の欠陥を検出可能になる。

「UDFM」は、Mentorの「Calibre」および「Eldo」を用いた1回のセルライブラリのキャラクタライゼーションで生成でき、ユーザーはその作業をMentorに依頼することも可能。(コンサルティング・サービスとして)「Tessent TestKompress」は、生成された「UDFM」を用いてセル内の欠陥をターゲットとしたパターンを自動生成可能で、「Tessent FastScan」を用いてセル対応ATPGを実行できる。

2011.09.22

2011年9月21日、Mentor Grapphicsは、ブラジル市場向けにポルトガル語をサポートするPCB設計ツール「PADS」の特別バージョンを出荷することを発表した。

Mentorによると「PADS」の特別バージョンは全てのメニュー、ダイアログがポルトガル語化されており、ポルトガル語版の「PADS Evaluation Guide」も用意される。

PCB設計ツール「PADS」は、日本市場向けに日本語バージョンも用意されているが、今回のポルトガル語のサポートは、PCBツールの展開先としてMentorがブラジル市場を重要視していることの表れと言える。

2011.09.21

2011年9月20日、マスクレス製造のDFEB(design-for-e-beam)技術を推進する米D2S社は、業界初となるマスク-ウエハ・ダブルシミュレーション用のワークステーション「TrueMaskTM DS」のリリースを発表した。

D2Sワークステーション「TrueMaskTM DS」は、フォトマスク技術の研究・開発、メモリ・ビット・セルの設計、ホット・スポット解析、マスク欠陥分類などの利用に向けて開発されたもので、ハードウエア・アクセラレータの搭載によって、5x5 micron(ウエハ上)のマスクとウエハの会話型のダブルシミュレーションが可能。これにより、ウエハ品質とマスク描画時間の許容範囲のトレードオフ、描画の実験など、従来のリソグラフィ・シミュレーションだけでは対応できなかったリソグラフィ・イメージの確認が可能となる。

■「TrueMaskTM DS」の特徴は以下の通り

・解像度、0.1nmで300x300 micron(マスク上)までシミュレーションが可能

(オーバラップ図形、ドーズ量変調可能)

・任意のPoint Spread Function(PSF;点拡がり関数)による先端電子ビームモデリング

・ハードウエア・アクセラレータによる、高速・会話型リソグラフィ・シミュレーション

・5x5 micron(ウェファ上)のマスク-ウエファ・ダブルシミュレーションが可能

・シミュレーション像と重ね合せ解析を行なうためのSEMインターフェース

2011.09.21

2011年9月20日、Synopsysは、同社の提供する「DesignWare STAR Memory System」の出荷数が10億チップに達した事を発表した。

Synopsysの「DesignWare STAR Memory System」は、BIST機能とリペア機能を備える組込みメモリIPで、同社が2010年に買収した旧Virage Logic社が開発した製品。同製品が初めて出荷されたのは2002年で、累計出荷数(搭載チップ数)が10億に達した。

元々単体製品であった「DesignWare STAR Memory System」は、Synopsysに買収された結果、SynopsysのDFTツール「DFTMAX Compression」、「TetraMAX ATPG」と連携して動作可能となり、組込みメモリおよびSoCの欠陥検出能力を更に強化しているほか、2010年11月には、先端プロセス製品で発生するソフト・エラーなどのトランジェント・エラー(一時的故障)に対応する新製品「DesignWare STAR ECC(Self-Test and Repair Error Correcting Codes)」がリリースされている。

2011.09.20

2011年9月20日、Cadenceは、富士通セミコンダクター社が28nmプロセスでのASICおよびミックスシグナルSoC設計向けに、CadenceのDFMサインオフ・テクノロジを採用したと発表した。

今回、富士通セミコンダクターが採用したのは、「Cadence Litho Physical Analyzer」、「Cadence CMP Predictor」、「Cadence Litho Electrical Analyzer」という3種類のDFMツールで、28nmプロセスにおける設計品質の向上とばらつき最適化を目的に導入。これらツールで実現されるDFM考慮の設計「in-design DFMテクノロジ」は、Cadenceのカスタム/アナログ設計環境「Virtuoso」ならびに、デジタル・インプリメント環境「Encounter」でサポートされている。

富士通セミコンダクターは、40nmプロセスからTSMCに製造を委託しているため、TSMCのリファレンスフローで採用されているツール環境であれば、どのツールを利用しても設計・製造に大きな支障は出ないはずだが、市販製品を評価した結果、CadenceのDFMツールを選択した。Cadenceの設計ツールを標準利用する同社にとって、既存の設計フローの中で簡単にDFM技術を活用できるというメリットも大きかったようだ。

2011.09.20

2011年9月19日、Cadenceは、最新のDDR PHY Interface 3.0仕様に準拠した設計IPおよび検証IPのリリースを発表した。

DDR PHY Interface(DFI)3.0仕様は、DDR4メモリ向けに用意されるメモリコントローラとPHYs間の最新のインタフェース・プロトコル仕様で、本Cadenceの発表と同日の9月19日にDFI Technical Groupより3.0仕様の公開が発表された。

元々DFI仕様は、Cadenceに買収されたDenali Softwareを中心に策定されたもので、最初のバージョンのリリースは2007年。現在もその仕様策定にあたってはCadenceが主導的な立場にあると推測される。

Cadenceは今年4月に、PHY IP、Controller IP、Memory model、Verification IPなど、業界初の「DDR4 IP」をリリースしており、「DFI 3.0 IP」に関しても業界初の製品化を実現した。Cadenceによると、DDRコントローラおよびPHYのIPで既に400デザインの成功実績があるとの事で、同社はDenaliの強みであったメモリ・ソリューションを中心にIP戦略の展開を推し進めている。

2011.09.20

2011年9月19日、Mentor Graphicsは、ARMと共同でARMベースデザインのリファレンスDFTフローを開発した事を発表した。

開発されたDFTフローは、MentorのTestツール「Tessent」をベースとしたもので、両社のコラボレーションによりARMコアのMBISTインタフェースを「Tessent」がサポート。ARMのフィジカル・メモリIP「Artisan」向けの既存のBISTソリューション(Tessent MemoryBIST)やATPGツール「Tessent TestKompress」も包含されており、SoC内で利用されるARMのコア、ロジック、組み込みメモリのテストに必要な工程を全てサポート。また、このリファレンスDFTフローには、ドキュメントの他にMentorのTestツール「Tessent」のインタフェースおよびスクリプトが用意されており、単純化された自動テストフローを実現できるという。

2011.09.20

2011年9月19日、フランス原子力庁の電子・情報技術研究所CEA-Letiは、同研究所のマスクレス・リソグラフィ開発プロジェクトにSynopsysが参加した事を発表した。

「IMAGINE Program」と呼ばれている同プロジェクトは、CEA-LetiとオランダMAPPER Lithography社が2009年7月に立ち上げたもので、STMicroelectronics,TSMC,Mentor Graphicsらが参画しており、今回Synopsysが10社目のメンバーとなった。

プロジェクトとしては、大規模データをハンドリングするための標準フォーマットの確立を目指しており、その課題解決に向けてSynopsysの協力に期待しているという。

2011.09.16

2011年9月15日、Mentor Graphicsは、同社のDFMツール「Calibre YieldEnhancer」がTSMCの65nm以降の製造プロセスに対応するSmartFill機能をサポートしたことを発表した。

発表によると「Calibre YieldEnhancer」のSmartFill機能は、TMSCの最先端プロセス・テクノロジの新たなフィル要件を満たす目的でTSMCとの提携の下で設計されたもので、同機能を使用することで手修正を必要とせずに1回の処理でICフィル制約を満たすことができる。

65nm以降のプロセス・ノードでは、製造面、設計面、両面においてフィルの影響度が増すため、フィル要件を満たしつつ最適化されたフィルを自動生成可能なSmartFill機能は、MentorのDFMソリューションにおける重要機能の一つと言える。

2011.09.15

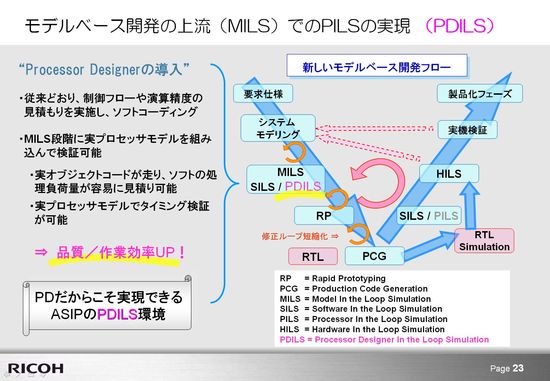

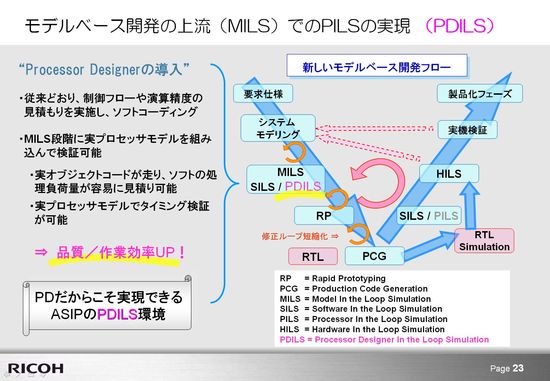

2011年9月7日に開催された、Synopsys Users Meeting 2011(JSNUG2011)における、株式会社リコーの講演レポート。

株式会社リコーはSynopsysのユーザーとして、「Processor DesignerによるASIP開発におけるモデルベース信号処理開発との協調検証について」と題したシステムレベル設計の成功事例を発表した。

今回発表を行ったのは、株式会社リコー、研究開発本部、基盤技術開発センターの久保田修司氏で、無線システムにおけるデジタル信号処理部の設計に関するものであった。

久保田氏によると、リコー社内ではデジタル信号処理開発にMATLABを用いたモデルベース設計手法が定着しており、MATLABで開発したモデルからSynopsysの高位合成ツール「Synphony」を用いてRTLを合成し、FPGAへ実装するという早期プロトタイプ・フローが確立されていた。

※画像はリコー提供のデータ

しかし近年、無線規格が多数登場し、デジタル信号処理がより複雑になり、回路規模の増大を抑えるために、伝播路の計算やモードによって切り替える誤り訂正処理など、ベースバンド処理の一部をソフトで処理する事を考えるようになった。

そこで同社では、既に社内で利用実績のあるSynopsysのカスタム・プロセッサ開発環境「Processor Designer」を用いて専用プロセッサ(ASIP)を開発する事にした。これをきっかけに久保田氏はMATLABを用いたDSPのモデルベース設計フローにカスタム・プロセッサ開発環境「Processor Designer」をリンクさせる手法を思いつく。

※画像はリコー提供のデータ

久保田氏曰く、「V字フロー」と呼ばれる一般的なモデルベース開発フローでは、開発の早期段階でMATLABを用いてシステムのモデリングを行っても、そのシミュレーションでは制御フローや演算精度の見積りまでしか評価できず、ソフトウェアの処理量の見積や物理モデルとのタイミング検証などは、より後工程の「PILS」または「HILS」以降の実機検証で行うしかなかった。そこで久保田氏はMATLABを用いた「MILS」のフェーズで実ソフトを検証したいと考えるようになった。

MILS:Model In the Loop Simulation

PILS:Processor In the Loop Simulation

HILS:Hardware In the Loop Simulation

当初久保田氏は、「PILS」にあたるSynopsysの「Platform Archtect」をベースに、MATLABで設計したモデルと「Processor Designer」の出力するSystemCモデルをインポートしてシミュレーションを行うという事を考えていたが、「Processor Designer」の出力するモデルをMATLAB/Simulink環境にインポートするという手法を思いついた。

※画像はリコー提供のデータ

具体的には、「Processor Designer」の出力するSystemCモデルのDLLのみを利用してISSを作成。次に「Microsoft Visual C++」を用いてISSのラッパーを作成。そして「MATLAB」で「Simulink」のS-Functionを作成しS-Functionを用いてSimulinkシミュレーションにプロセッサーモデルをインポートする。

実際にこの手法によって「Processor Designer」で開発したASIPモデルをSimulink上にインポートしたところ、通常のシミュレーションよりも「Processor Designer」モデルをインポートした方がより高速にシミュレーションでき、従来のMATLAB/Simulink環境のみでは確認できなかった、割り込みタイミングのオーバーヘッドや、ソフトウェアの処理量およびレイテンシ、初期化処理の挙動などを確認。通常、実機評価の段階で判明する問題を「MILS」のフェーズで確認することが出来たという。

※画像はリコー提供のデータ

久保田氏は従来手法よりも作業効率が高く、製品の品質向上にも役立つこの手法を、「Processor Designer」ならではのモデルベース・シミュレーション手法として「PDILS(Processor Designer In the Loop Simulation」と独自に命名。今後リコー社内の様々なプロジェクトに同手法を展開していきたいと意気込みを語っていた。

2011.09.15

2011年9月14日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、米Agnisys社とのコラボレーションを発表した。

Aldecによると、今回のAgnisysとのコラボレーションは検証の早期収束に向けたもので、Agnisysの検証データ・マネジメント・ツール「IVerifySpec」とAldecの論理シミュレータ「Riviera-Pro」を接続。これにより「Riviera-Pro」のユーザーは、論理シミュレーションを進めながら「IVerifySpec」を通じて検証対象のデザイン、検証用ソースコード、リグレッション・データ、バグ・トラッキング・データ、検証要件、検証プランなど、検証に関するあらゆるデータを効率良く統合的に確認することが可能となるという。

シミュレーション環境としての「Riviera-Pro」と、検証データのマネジメント環境「IVerifySpec」が補完し合う事でより効率的な検証および検証の収束を実現するという事のようだ。

尚、Agnisysは、検証データ・マネジメント・ツール「IVerifySpec」の他に、レジスタ・マップから各種ドキュメントを自動生成する「IDesignSpec」、アサーション開発環境「IAssertSpec」などを提供している。

2011.09.15

2011年9月14日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、中国にて同社の製品が2011年FPGA Best Dvelopment Toolを受賞したことを発表した。

Aldecが受賞した「FPGA Best Dvelopment Toolアワード」は、中国の情報誌「Chinese Electronics News」が主催し、中国で3度目の開催となる「FPGA Industry Development Forum」にて発表された。

Aldecによる同アワードの受賞は昨年に続き2度目で、昨年はHDLシミュレーター「Active-HDL」が対象製品とされていたが、今年はAldecの「design and verification platform」に対して賞が贈られている。

2年連続のアワード受賞は、シミュレーターを中心とするAldec製品のコストパフォーマンスの高さと、中国における知名度の高さを物語っていると言っても過言では無いだろう。

2011.09.15

2011年9月13日、アナログ/ミックスドシグナル設計統合環境およびMEMS向け設計環境を手掛ける、Tanner Research社のEDA事業部Tanner EDAは、同社の2011会計年度の営業実績を発表した。

Tanner EDAによると、2011年5月末を締めとする同社の2011会計年度の売上は前年比8%増を記録。具体的な売上額は公表されていないが、日本、アジアおよびその他地域における売上増が好結果を牽引し、1年間で139の新規顧客を獲得したとしている。

製品としては、主力のアナログ/ミックスド・シグナルIC設計ツール・スイート「Hyper Silicon」ほか、MEMS向けレイアウトツール「L-Edit MEMS」が好調だったという。

2011.09.14

2011年9月13日、EDA ConsortiumとIEEE Council on EDA は、両団体がスポンサーとなっている「Kaufman Award」の今年の受賞者を発表した。

「Kaufman Award」は、EDA業界に対する貢献を称える権威ある賞で、1992年に他界した元Quickturn Systems社のCEO Phil Kaufman氏の功績を称え1994年に設立されたもの。18回目となる今年の「Kaufman Award」は、Dr. C.L. David Liu氏に授与される事となった。

Dr. C.L. David Liu氏は、EDAにおける基礎技術の研究開発で多くの実績を残した人物で、同氏の考案したフロアプランニング・アルゴリズムやスケジューリング・アルゴリズム(Rate Monotonic Scheduling)は、現在の高位合成、論理合成、フィジカル・デザインツールやRTOSで活かされている。研究者としては、25年間イリノイ大学の教授を務めコンピュータ・サイエンス関連の研究に従事した後、台湾に戻り2002年まで台湾Tsing Hua Universityの学長を務めた。

また、Dr. C.L. David Liu氏は研究者としてだけではなく、教育者、財界人としても手腕を発揮している事で有名で、60年代から80年代にかけてコンピュータ・サイエンスに関する複数の教科書を執筆。IEEEより技術者としての賞と合わせて複数の教育賞を授与されている。更に1998年以降は台湾半導体業界で活躍。現在、台湾TrendForce社の取締役会長であるほか、PowerChip Semiconductor、UMC、MediaTek、Macronix、Anpec Electronicsと複数の台湾半導体関連企業の取締役を兼務。Cadence Methodology Service社の取締役でもある。

Dr. C.L. David Liu氏の「Kaufman Award」授賞式は、2011年11月8日、サンノゼで開催されるICCADのパーティーで行われる予定。

2011.09.13

2011年9月12日、Alteraは、浮動小数点DSPアルゴリズムのFPGA実装を実現する新しいDSPデザイン・フローを発表した。

Alteraの発表した新たなDSPデザイン・フローは、Alteraの提供する「DSP Builder アドバンスト・ブロックセット」に統合された浮動小数点 DSP コンパイラ、FPGAインプリメント環境「Quartus II」、Mentor社製論理シミュレータ「ModelSim」、DSPアルゴリズムの開発環境であるMathWorks社製の「MATLAB/Simulink」で構成されており、アルゴリズムのモデリングおよびシミュレーション、RTL生成、論理合成、配置配線、デザイン検証と、アルゴリズム開発からFPGA実装までの一連のフローが包括的にサポートされている。

同DSPデザイン・フローを評価したBerkeley Design Technology社のレポートによると、のデザインの検討、シミュレーション、合成、RTLシミュレーションはいずれもSimulink

環境上で行う形となっており、Alteraの「DSP Builder アドバンスト・ブロックセット」には、データ型伝播やベクトル・データ処理などのSimulinkの機能が組み込まれているという。同DSPデザイン・フローを利用すれば、複雑な浮動小数点アルゴリズムの実装と検証を従来のHDLベースのデザインよりも素早く行えるようになる。

2011.09.13

2011年9月12日、マスクレス製造技術「design-for-e-beam (DFEB) 」の普及・促進を目標としたフォーラムeBeam Initiativeは、新たに5社がメンバーに加わったことを発表した。

発表によると、新たにApplied Materials, IMS CHIPS, Mentor Graphics, Multibeam Corporation, SoftJin Technologiesの5社がeBeam Initiativeのメンバーに加入。これで業界20社で立ち上げられた同組織のメンバー企業・団体数は39社となった。

尚、eBeam Initiativeは、9/19よりカリフォルニア州モントレーで開催される「SPIE/BACUS Photomask Symposium 2011」にて、メンバー会社によるマスク技術および直描技術の最新の成果を報告するという。

2011.09.09

2011年9月8日、Mentor Graphicsは、仮想プロトタイピング・ツール「Vista」の拡張を発表した。

発表によると、Mentorのバーチャル・プロトタイピング環境「Vista」の拡張により、「Vista」とCalyptoの高位合成ツール「Catapult C Synthesis」がSystemC TLMベースで連携可能となった。すなわち、「Vista」でモデリングしたTLMモデルを「Catapult C Synthesis」で合成するという、バーチャル・プロトタイプから実装へのフローが確立された。Mentorはこれを「VistaとCatapult C Synthesisの統合」と表現している。

しかしながら、そもそも「Catapult C Synthesis」はMentorの製品であり、「Vista」との連携は「TLM合成機能」の開発など以前から進められていた事。今回の発表は、ツールの強力な連携をアピールすることで、Calyptoとの関係強化を強調するという側面が伺える。

尚、今回の発表においては、「Vista」と組込みソフトウェア統合開発環境「Sourcery CodeBench」の統合についても触れられているが、バーチャル・プロトタイピング環境としては、高位合成ツールとの連携よりもむしろ膨大なユーザーを抱える「Sourcery CodeBench」との連携の方がインパクトが大きいと思われる。

2011.09.08

2011年9月7日、Xilinxは、同社の45nmFPGA「Spartan-6」がシグマのデジタル一眼レフカメラに採用された事を発表した。

発表によると「Spartan-6」が採用されたのは、シグマのフラッグシップ製品となる4600万画素のデジタル一眼レフカメラ「SIGMA SD1」で、既に6月から市場に出回っている。

(※実売価格56万円?ボディのみ)

「Spartan-6」はイメージセンサーからのインターフェイスとして利用されており、DDR3 バッファ・メモリをサポートすることで、高速での大量データの制御を実現。これにより、連続撮影モードで5コマ/秒、最大7コマまでのRAWデータ (RGB画素センサーが取り込んだオリジナルの出力データ) の取り込みが可能だという。

シグマでは現在、今回発表された「SIGMA SD1」を含むデジタル一眼レフカメラ2種、コンパクトカメラ2種においてXilinxのFPGAを採用している。

2011.09.08

2011年9月6日、Alteraは、同社の28nmFPGA「Stratix V GX」を搭載した「Stratix V GX FPGA シグナル・インテグリティ開発キット」の出荷開始を発表した。

米国内販売価格4995米ドルの「Stratix V GX FPGA シグナル・インテグリティ開発キット」は、600Mpbs-12.5Gbpsまでの高速トランシーバのリンク性能を計測・評価するためのプラットフォームで、「Stratix V GX FPGA」を搭載した開発ボードと合わせて、開発ツール「Quartus II(1年間ライセンス)」、デザイン例、「Nios II Embedded Design Suite」を含むアルテラの「MegaCore IP」ライブラリへのアクセスが含まれている。

同キットを利用することで、高バンド幅アプリケーションを開発する設計者は、以下のようなプロトコル規格への準拠を確認できるようになる。

?10GbE、10GBASE-KR

?PCI Express Gen1、Gen2、Gen3

?Serial RapidIO

?Gigabit Ethernet、10GbE XAUI

?CEI-6G、CEI-11G

?HD-SDI

?Interlaken

?Fiber Channel

2011.09.06

2011年8月30日、ESLツールを手掛ける仏CoFluent Design社は、Intelに吸収合併された。CoFluent Design社の関係者が明らかにした。

この吸収合併により、CoFluent Design社の全ての従業員はIntelの社員となり、引き続き顧客サポートに対応。CoFluent Designの提供していたESLツール「CoFluent Studio」はIntelの所有となり、今後はIntelより提供される事になる

CoFluent Designは、仏ナント大学での研究成果をベースに2003年にフランスで設立された会社で、設計初期段階での仕様レベルの情報からアーキテクチャ探索を実現するESLツール「CoFluent Studio」を提供していた。ツールの実績としては、スマートフォン向けSoCの開発用途にノキア、TI、RIMなどの大手が採用しているほか、複写機や自動車関連などワールドワイドで十数社の顧客を抱えていた。

今回の吸収合併に関して未だ公式な発表は行われていないが、Intel本社にはESL手法に取り組む専門チームが組織されており、高位合成やバーチャル・プロトタイプなどESLツールの実用について様々な事例発表が行われていることから、Intelも「CoFluent Studio」のユーザーだった可能性が高い。