NEWS

2012.02.03

2012年2月1日、SoCインターコネクトIPを手掛ける米Sonicsは、Arterisとの特許侵害訴訟を進めていく方針であることを表明した。

今回のSonicsの表明は、1月27日にArterisがSonicsに対して行った申し立てに反応したもので、SonicsはArterisの主張を否定し訴訟を継続する意志を強く示した。

Arterisは特許侵害で訴えを起こしたSonicsに対し特許侵害の事実を否定し、逆に同社の特許侵害を申し立てている。

2012.02.03

2012年2月2日、EDAツール用の各種機能コンポーネントを手掛ける米Verific Design Automationは、パワー・フォーマットIEEE 1801-2009のパーサーを開発した事を発表した。

発表によると、UPF2.0の名で知られるパワー・フォーマットIEEE 1801-2009に対応したVerificのパーサーは製品としてすぐに利用可能。他のパーサー製品と同じくC++ソースコードで提供され、スタンドアロンでの利用のほか、Verificの提供するSystemVerilogやVHDLのパーサーにアドオンする形で利用することもできる。

UPF(Unified Power Format)2.0は、EDA関連の規格標準化団体Accelleraが策定したパワー記述フォーマットで、2009年3月にIEEE標準化を完了。低消費電力設計向けに電力に関する仕様をデザインに反映させるために作られた規格で、電力の定義や意図を明確化するもの。

発表に寄せられたコメントよると、既に仏DeFacTo TechnologiesがVerificのUPFパーサーをEDA製品に利用しているようだ。

2012.02.02

2012年1月28日、幻冬舎より、東京大学准教授竹内健氏の著書「世界で勝負する仕事術」が出版されました。

竹内健氏は、フラッシュ・メモリ、次世代メモリの研究で世界的に有名な東芝出身の研究者で、当サイトでも先日同氏の講演に関する記事を掲載致しました。

今回出版された「世界で勝負する仕事術」は、竹内氏のエンジニア人生が綴られた自叙伝で、タイトル通り、世界で戦うエンジニア竹内氏の仕事に対する取り組み方、思い、視点、戦略、理論などがリアルに描かれています。物語として読み易くまとめられている同書は、同じ半導体の世界に属するエンジニアの方々にとって、きっと良い刺激となるでしょう。エンジニアではない文系の方にもおすすめです。

「世界で勝負する仕事術」

最先端ITに挑むエンジニアの激走記

著者:竹内健(たけうちけん)

東京大学工学系研究科准教授

定価:本体780円+消費税

新書判並製208ページ、1月28日発売

内容紹介:

デジカメやiPod、携帯電話などに使われ、生活に不可欠な存在であるフラッシュメモリ。著者は東芝の開発チームの一員として、世界シェア40%の主力事業にまで成長させる技術を確立した。その後、MBAを取得し、半導体ビジネスの最前線で、各国の企業とわたりあう。世界中のライバルとしのぎを削るのが当たり前、毎日が世界一決定戦の世界で働き続けるとはどういうことなのか? 異色のエンジニアが初めて語る仕事論。理系・文系問わずグローバル人材が求められる時代へのヒントが満載。

内向き志向じゃつまらない。元気が湧く仕事論。

■会社が認めないなら、世界で認めさせてやる

■誰も注目していない分野、歴史の浅い分野をねらう

■半導体は「走りながら考える」ビジネス

■自動車、電機・・・・・日本の強みを放棄してはいけない

■「ドラえもんがいたらいいな」から始まる技術開発

■勝ち残るのは、見る前に跳んで、たくさん失敗した人

◆◇◆読者プレゼント◆◇◆

著書「世界で勝負する仕事術」を抽選で1名様にプレゼント致します。

当選者発表:大手セットメーカー勤務 ハード設計者 山村様

コメント:「画像処理関連の設計をしています。将来の起業に向けて参考になればと応募しました。よろしくお願いします。(当選しなくても購入の予定です)」

ご希望の方は、本日2月2日22時までに下記メールアドレスに「一言コメントを添えて」応募の旨ご連絡下さい。頂いたコメントを基に当選者を発表させて頂きます。

応募メール送付先: info@eda-express.com

2012.02.02

2012年2月1日、Cadenceは、2011会計年度第4四半期(2011年10-12月)の売上を報告した。

Cadenceの2011年Q4(10-12月)の売上は、前年同時期比約23.7%増、前期Q3(11年7-9月)と比較して約5.5%増の3億800万ドル。営業利益は1100万ドルで前年の赤字から一転、黒字となった。(※GAAP基準による会計結果)

同実績は10月末時点での予測を上回るもので、Cadenceは8四半期連続、丸二年に渡り前年比増の四半期売上を叩き出した事になる。

2011年売上合計は前年比22.9%増の11億5000万ドル、営業利益は前年比約42%減の7200万ドルだった。

Cadenceは2012会計年度も更なる業績アップを見込んでおり、次期2012年Q1売上は3億500-1500万ドル、年間売上を12億4000-8000万ドルと予測している。

2012.02.01

2012年1月31日、ミックスド・シグナル設計向けの自動化ツールを手掛ける、米Orora Design Technologiesは、STARCが同社のポスト・レイアウト検証ツール「Arena」を採用した事を発表した。

発表によるとSTARCはアナログ/ミックスシグナル設計のTAT半減を目指す設計フロー「STARCAD-AMS」の開発にあたり、Orora Design Technologiesのポスト・レイアウト検証ツール「Arana」を評価。ネットリストからPVT(プロセス/電圧/温度)考慮のビヘイビア・モデルを生成する「Arana」のコア機能を用いる事で、シミュレーション時間を短縮できる事を確認し同ツールの採用を決めた。実施した評価では、精度誤差1%以内の高精度でポスト・レイアウト・シミュレーションの時間を200倍以上短縮。ツールが要したビヘイビア・モデルの生成およびセットアップ時間はわずか1時間以下で、通常の手作業では数週間を要するという。

2012.02.01

2012年1月27日、SoCインターコネクト設計ソリューションを手掛ける仏Arterisは、同社の特許を侵害しているとして競合の米Sonics社に対して申し立てを行った。

昨年11月にSonicsは特許侵害でArterisを提訴したが、Arterisは特許侵害の事実は無く、Sonicsが主張する特許は無効であると主張、合わせてSonics最新のインターコネクトIP製品「SonicsGN」がArterisの特許を侵害しているとして、損害賠償ならびに衡平法上の救済を申し立てた。

Arterisは今回の申し立てを含むSonicsとの訴訟対応にあたり、ハイテク特許訴訟で世界的に有名な法律事務所 DLA Piper LLPを弁護人に立てたという。

2012.02.01

2012年1月31日、ARMは、2011会計年度第4四半期(2011年10-12月)の売上を報告した。

ARMの2011会計年度Q4 (2011年10-12月) の売上は、前年比21%増、前期(2011年Q2)比12.8%増の2億1700万ドルで四半期売上記録を更新した。四半期売上記録の更新はこれで7四半期連続となる。営業利益は前年比45%増の6900万ドルだった。

ARMの2011年の売上累計は前年比24%増の7億8500万ドルで、営業利益は前年比37%増の2億2970万ドルを記録した。同実績はもちろん過去最高記録となる。

ARMはこのQ4で新アーキテクチャのARMv8コアを含む25件のプロセッサ・ライセンスを獲得(前Q3では28件)。その内3件は新規顧客でいずれもCortexシリーズのライセンス契約だった。また、Cortex-AシリーズのフジカルIP「POP(Processor Optimisation Pack)」のライセンスを新たに3件獲得。GPU「Mali」の新規契約は5件だった。プロセッサ・ライセンスの契約数でみるとこの1年間で106件の契約を獲得した計算となる。

※画像はARM発表資料より抜粋

Q4で出荷されたARM搭載チップの総数は約22億個で、うち約12億個はスマートフォンなどのモバイルデバイス向けに、約10億個はコンシューマーおよびクルマ向けで、コンシューマーおよびクルマ向けの出荷数は前年比40%増となっている。

売上の内訳を見ると、プロセッサ・ライセンスのQ4売上は前年比36%増の7890万ドルで、年間売上合計は前年比37%増の2億8570万ドルだった。プロセッサ・ロイヤリティのQ4売上は前年比22%増の1億1470万ドルで、年間売上合計は前年比21%増の4億560万ドルだった。

ARMは次期2012Q1売上を2億ドル前後と予測。2012年合計売上は約10%増の8億6000万ドル前後と予測している。

2012.01.26

2012年1月25日、Synopsysは、同社のカスタム・プロセッサ開発ツール「Processor Designer」をヤマハが採用したことを発表した。

発表によるとヤマハは自社のサウンド・ジェネレーター向けDSP「XMP-1」の開発にSynopsysのカスタム・プロセッサ開発ツール「Processor Designer」を採用。これによりDSPの高性能化を実現しサウンド・チャンネル数を倍の32に増やしたほか、DSPの面積を20%削減することに成功。設計期間も従来の約半分に短縮し半年間でテープアウトした。

ヤマハ半導体事業部 部長 森島守人氏は、「Processor Designer」は、より高品質な製品開発プロセスを容易化し設計コストも削減したとコメントしている。

2012.01.25

2012年1月23日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のリントツール「ALINT」のバージョンアップを発表した。

発表によると、Aldecのリントツール「ALINT」の最新バージョン2012.01では、新たに航空電子機器向けのハード設計規格「DO-254」、電子機器の機能安全規格「IEC 61508」、自動車向け機能安全規格「ISO 26262」、原子力関連の機能安全規格「IEC 61513」といった各種設計基準に対応するドキュメンテーション機能が追加され、コーディング違反の検出や検出した違反の解析、除外の理由を付加したレポートの生成などが可能となった。これにより、エンジニアによるドキュメント作成工数を削減できるという。

Aldecは論理シミュレーター「Active-HDL」、「Riviera」において「DO-254」対応機能をサポートしているほか、エミュレーション・ボード「HES」をベースとした「DO-254」準拠のFPGA検証ソリューション「Aldec DO-254/CTS (Compliance Tool Set)」を提供しており、主要FPGAベンダらと「DO-254エコシステム」を設立しているなど、標準規格へのコンプライアンス・ソリューションに力を入れている。

2012.01.25

2012年1月24日、ESLソリューションを手掛ける米Carbon Design Systemsは、同社の2011年売上実績について発表した。

Carbonは具体的な売上額を明らかにしていないが、2011年も売上好調で前年比増の売上記録更新を実現。これで2007年から5年間連続で前年増の成長となった。

Carbonによると、同社の運営するバーチャル・プロトタイプ用仮想ハード・モデルの供給ポータル「Carbon IP Exchange」は、登録ユーザーが400を越え2011年1年間で同サイトを通じて2500以上のモデルがダウンロードされたとの事。

Carbonはつい先日、各種プロセッサ・モデルに加えて周辺IPやソフトもパッケージしたバーチャル・プロトタイピング環境「SoCDesigner Plus」用の仮想プラットフォーム「Virtual Reference Platform」の提供開始を発表している。

2012.01.25

2012年1月24日、Mentor Graphicsは、Alteraが同社のエミュレーター「Veloce」を採用したことを発表した。

発表によるとAlteraは次世代製品の開発における検証用途でMentorの「Veloce」を採用。「Veloce」は、高速なランタイム、高速なコンパイラ技術、使いやすさ、優れたデバッグ能力、トランザクション・ベースのアクセラレーションとエミュレーションの複合能力などが評価され、Alteraのグローバルな開発チームの共有リソースとして配備された。

Alteraは、「Veloce」と合わせてアクセラレーション用の通信リンク「TestBench XPress(TBX)」やSoC上のプロトコル検証用のソフトウェア・モデル「iSolve」も採用しているという。

2012.01.25

2012年1月24日、SoCインターコネクト設計ソリューションを手掛ける仏Arterisは、同社の2011年の業績に関して発表した。

Arterisは具体的な売上額等は明らかにしていないが、2011年度の売上実績は前年比100%増以上の好成績で、主力製品のインターコネクトIP「FlexNoC」およびC2C(Chip to Chip Link IP)にて21の新規ライセンシー獲得。これにより同社のライセンシー数は累計39となった。Arterisによると受注合計の約60%は既存のライセンシー、約40%は新規のライセンシーからのもので、2011年1年間でArteris製品を用いた45件のSoC開発プロジェクトがスタートしたという。

発表に寄せられた市場調査会社Semico Research社アナリストのコメントによると、インターコネクトIP市場は2011年28.2%の成長を遂げているという事であるが、当然ながらArterisは市場の成長率を大きく上回るペースでビジネスを拡大している。日本市場においてはこれまでイノテックが代理店としてArteris製品を販売していたが、今年1月より設立した日本法人による営業を開始している。

当サイトで2011年に紹介したArterisの採用事例は以下のとおり。

2012.01.25

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2012.01.25

2012年1月24日、Alteraは2011会計年度第4四半期(11年10-12月)の売上を報告した。

発表によるとAlteraの2011年Q4(11年10-12月)売上は、前年比約18%減、前期Q3比約12%減の4億5780万ドル。営業利益は前年比約40%減の1億6000万ドル、Q3売上報告時の予測値を下回る結果だった。

Q4売上を地域別で見るとアジアと欧州の売上がQ3売上と比較してそれぞれ4%減、3%減と落ち込んだ。売上の内訳はQ3とほぼ同じで、新製品としてカテゴライズされるStratix V、Stratix IV、Arria II、Cyclone IV、MAX V、HardCopy IVといった製品群が売上全体の27%を占めた。

最終的にAlteraの2011会計年度の売上合計は、前年比5.6%増の20億6440万ドルで過去最高記録を更新、営業利益は前年比約2.2%減の8億4920万ドルだった。

2012.01.24

2012年1月24日、Synopsysは図研の子会社インベンチュア株式会社の買収で図研と最終合意に達したことを発表した。

今回の買収に向けた条件などの詳細は明らかにされていないが、Synopsysの発表によると買収は2012年Q1に確定する予定。Synopsysは買収するインベンチュアの開発チームを自社のIP開発部門に取り込み、IPの開発および技術サポート力を増強する。

インベンチュアは図研の100%子会社として2006年に設立された会社で、各種IPの開発および販売を専業としていた。製品としては、「Z-Core」シリーズとして、PCI Express、USB 3.0、DisplayPort、OCP InterConnect MIIX-mf、Gigabit Ethernet MAC、USB 2.0、PCIなどの各種IPを提供しており、中でもPCI Express IP「Z-core PCI Express」は国内でも多数の採用実績を誇っていた。

2012.01.24

2012年01月24日、Mentor Graphicsは、富士通セミコンダクターが同社の物理検証およびDFMツール「Calibre」ファミリ製品の利用を拡大したことを発表した。

発表によると富士通セミコンダクターは、最先端プロセスでの全ての製品開発(アナログデジタル)にあたり、設計フローに「Calibre」の最新の物理検証機能とDFM機能を採用。具体的には、主に下記機能を用いる事で先端プロセスでの複雑な設計の効率化を図るとしており、中でも「Calibre SmartFill機能」の必要性を重視しているようだ。

・「Calibre Pattern Matching」:リソグラフィ・ホットスポットやその他のデザインルール・チェック(DRC)違反を迅速に識別する

・「Calibre Automatic Waivers」:DRC中の自動疑似エラー除外機能を提供

・「Calibre PERC」:信頼性検証のための電気的チェックを実行

・「Calibre SmartFill」DFMのための高度なタイミング・アウェア・フィルを実現する

2012.01.24

2012年1月23日、Synopsysは、業界標準プロトコル向けの検証IPを手掛ける米ExpertIO社の買収完了を発表した。

今回のExpertIOの買収についてSynopsysは取引条件などを明らかにしていないが、発表によるとExpertIOの全エンジニア・チームはSynopsysの検証IPグループに移籍、ExpertIOの創業者兼CEOのCraig Stoops氏もテクニカル・リーダーとしてSynopsysの検証IPグループに加わっているという。

Craig Stoops氏は元IBMのエンジニアでRS/6000のプロセッサおよびI/Oサブシステムの開発者。IBM初のギガビットI/Oアダプタやファイバーチャネルを含むストレージおよびネットワーキング向けのバス・アダプタ等を開発した経験を持つ。

ExpertIOは以下の標準プロトコル向けの検証IP製品を提供していた。

・PCI Express(Gen 1, 2 and 3)

・Ethernet MAC/PHY(MAC, 10/100/1000, XAUI, KX, KX4, KR, 40/100Gb)

・Serial ATA (NCQ, Port Multiplier / Selector)

・Serial SCSI(Including optional STP support)

・Fibre Channel(Link, AL, 10G, 16G)

2012.01.19

2012年1月18日、Xilinxは2012会計年度第3四半期(2011年10-12月)の売上を報告した。

Xilinxの2012年Q3(11年10-12月)の売上は、前年同時期比10%減、前期比8%減の5億1110万ドル。営業利益は前年比25%減の1億3710万ドルという結果だった。売上前年割れは11年7-9月期に続き2四半期連続となる。

地域別売上ではアジアが前年比17%減と大きく売上を落とした。その他の地域も軒並み前年割れとなった。分野別の売上構成では主力の通信分野の売上が前年比13%減、前期よりも10%落ちた。唯一データ・プロセッシング分野だけは前年比6%増を記録した。

製品別売上では新製品だけが前年比5%増。今期からZynq-7000も新たに新製品としてカテゴライズされている。

Xilinxは次期2012年Q4(12年1-3月)の売上を今期の2%から6%増になると予測している。

2012.01.18

2012年1月17日、Magmaは、低消費電力CMOS技術を手掛ける米SuVolta社が同社の回路シミュレーター「FineSim SPICE」の採用を拡張したことを発表した。

「PowerShrink」と呼ばれるSuVolta社の低消費電力プラットフォームは、トランジスタ特性を改善することにより電源電圧を下げ、性能(動作速度)を落とさずに消費電力を50%削減できるCMOSデバイス技術で、SuVolta社は同技術の開発にあたりMagmaのマルチCPU回路シミュレータ「FineSim SPICE」を利用することで、シミュレーション時間を短縮し、精度を損なうことなくテストカバレッジを約4倍向上できたという。

2012.01.18

2012年1月17日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、米Berkeley Design Automationは、米Triad Semiconductorが同社の回路シミュレーター「Analog FastSPICE」を採用した事を発表した。

発表によるとTriad Semiconductorは、アナログ/ミックスシグナル設計のブロックレベルでのキャラクタライゼーション、ならびに回路全体の検証にBerkeley DAの「Analog FastSPICE (AFS) Platform」を採用。これにより、既存のツールでは現実的ではなかった、デルタシグマ変調やフィルタなどスイッチド・キャパシタ回路全体の検証を行う事が可能となった。また、「Analog FastSPICE」は、PLLやADCのナノメータ精度の検証において、従来のSPICEと比較して10倍ものパフォーマンス向上を達成しているという。

Triad Semiconductorは、「Via-Configurable Array (VCA) 」と呼ぶ独自の特許技術でミックスド・シグナルASICを実現している。

2012.01.18

2012年1月17日、ESLソリューションを手掛ける米Carbon Design Systemsは、同社のWebポータル「IP Exchange」上で「virtual reference platforms」の提供を開始したことを発表した。

発表によるとCarbonは、Webポータル「IP Exchange」上で提供している各種プロセッサ・モデルにペリフェラル・モデルやサンプル・プログラム実行用のソフトウェアを組み合わせた「virtual reference platforms」の提供を開始。ARM Cortex A15、A9、R4、MIPS 34Kcなどポピュラーなプロセッサ・モデルをベースとした「virtual reference platforms」が既に用意されており、「IP Exchange」上で入手することができる。

「virtual reference platforms」は、プロセッサ・モデルにペリフェラル・モデルが組み合わされた仮想ハードウェア環境で、ファームウェアのデバッグやパフォーマンスの最適化、新たなIP利用時の学習や新たなデザイン環境構築の際のベースとして利用することが可能。既に複数のユーザーが「virtual reference platforms」を実用しているという。

現在、「IP Exchange」上で提供される「virtual reference platforms」のラインナップは以下の通り。

・34Kc Platform

・ARM1136 Platform

・ARM1176 Platform

・ARM7TDMIS Platform

・ARM926 Platform

・ARM946 Platform

・ARM968 Platform

・Cortex A15 Platform

・Cortex A8 Platform

・Cortex A9 Platform

・Cortex M0 Platform

・Cortex M3 Platform

・Cortex M4 Platform

・Cortex R4 Platform

・M14K Platform

・M14Kc Platform

2012.01.18

2012年1月18日、Mentor Graphicsは、同社の日本法人とCalypto社との日本国内におけるCalypto製品の再販契約締結を発表した。

発表によると今回の再販契約によりメンター・グラフィックス・ジャパンは、Calypto Design Systemsが提供する全てのEDA製品を日本国内で販売。既に昨年12月21日からメンター・グラフィックス・ジャパンによるCalypto製品の販売は開始されており、テクニカル・サポートも同社から提供される。

再販契約は日本国内の全ての営業をメンター・グラフィックス・ジャパンに任せるものではなく、Calypto KKも引き続き自社製品の販売を継続するようで、両社は製品販売先などをガイドラインに規定しているという。

Calyptoは、昨年8月にMentorから高位合成ツール「Catapult C Synthesis」の事業を買収しており、その際に「Catapult C Synthesis」の新規顧客への営業およびサポートはCaryptoが遂行し、既存の「Catapult C Synthesis」の顧客は、引き続きMentor側でサポートを継続するという方針を発表していたが、日本市場に関しては今回の再販契約により、特別な協業体制が敷かれる事になった。

「Catapult C Synthesis」のみならず、シーケンシャル等価性検証ツール「SLEC」ファミリ、消費電力最適化ツール「PowerPro」ファミリについてもMentorによる製品販売およびサポートが実施されるという事で、日本においてMentorとCalyptoの両社は、包括的なESLソリューションの協業体となる言っても過言ではない。Calyptoの製品はMentorの力によって更に国内ユーザーを増やすことになるだろう。

尚、Calyptoは、「Catapult C Synthesis」の機能強化に取り組んでおり、低消費電力化ツール「PowerPro」のLowPower化技術の応用やRTL合成エンジンの移植などを進めている最中。6月のDAC頃には新機能のリリースが発表されるかもしれない。

2012.01.18

2012年1月17日、Cadenceは検証エンジニア向けの書籍「Advanced Verification Topics」の出版を発表した。

「Advanced Verification Topics」は全229ページ、定価60ドル、AmazonやLuluで購入可能。章立ては以下の通り。

1.Introduction to Metric-Driven Verification

2.UVM and Metric-Driven Verification for Mixed-Signal

3.Low-Power Verification with the UVM

4.Multi-Language UVM

5.Developing Acceleratable Universal Verification Components(UVCs)

6.Summary

2012.01.16

2012年1月9日、標準言語SystemC規格の初の改訂版となるIEEE 1666-2011のLRMがリリースされた。

同LRMはIEEEのWebサイトからPDF版を無料でダウンロードすることが可能。今回のLRMの改訂では、IEEE 1666 SystemC標準に「TLM(transaction -level modeling)」に関する仕様が正式に追加され、データ・タイプの拡張ほか以下のような複数の新機能追加およびエンハンスが実施されている。

・Event list objects

・Hierarchically named events

・Multiple writer policy for sc_signals

・Asynchronous update requests for primitive channels

・Binding operators for sc_port and sc_export are now virtual

・Certain fixed-point constructors have been made explicit

尚、SystemCの標準化団体OSCI(Open SystemC Initiative)は、昨年12月にEDA関連規格の標準化団体Accelleraと統合し、Accellera System InitiativeとしてSystemC規格の改訂作業を継続中。現在、最新のSystemC 2.3 Libraryの公開レビューを行なっている。

2012.01.13

2012年1月12日、Mentor Graphicsは、バーチャル・プロトタイピング・ソリューションに関するFreescaleとの長期パートナーシップについて発表した。

発表によるとMentorは、同社のバーチャル・プロトタイピング環境「Vista」を用いて、Freescaleの組み込み向け通信プロセッサ「QorIQ」ベース・システムのシミュレーション・プラットフォームを構築。Freescaleはこのシミュレーション・プラットフォームをバーチャル・プロトタイプ・パッケージとして自社の顧客にソフトウェア開発環境として提供する。

対象となるのはFreescaleの「QorIQ」PシリーズとAMPシリーズ、「QorIQ Qonverge」プラットフォームで、ベースとなるSoCモデルはFreescaleによって確認・提供され、「Vista」のライブラリとしてインテグレーションならびにパッケージされる。顧客に提供される「Vista」のバーチャル・プロトタイプ・パッケージにはSoCのHWモデルも含まれており、カスタムIPの追加やI/Oの変更などユーザー側でカスタマイズして利用することが可能。Linuxの移植も可能で、ソフトウェアを実行させたリアルな環境下で消費電力とパフォーマンスのトレードオフ解析を行うこともできるという。

2012.01.13

2012年1月11日、フォーマル検証を中心とした検証ツールを手掛ける米Real Intent社は、同社のCDC検証ツール「Meridian」の最新バージョン4.0のリリースを発表した。

発表によるとCDC検証ツール「Meridian CDC」の最新バージョン4.0では、ツールの処理速度が改善され、デザインの構造解析、フォーマル解析、デザインの読み込み、GUIでのデバッグなどの各処理が既存バージョンよりも最大5倍高速化された。また、メモリ使用量も改善され、100Mゲート以上のSoCデザインのCDC解析を数時間で実行可能となった。

機能面では、ネットリストにおけるデータ、クロックのグリッチがチェック可能となったほか、シミュレーション実行中にカバレッジ情報が確認できるようになった。また、デバッグ機能の改善や、SpringSoft社のデバッグ環境「Verdi」とのシームレスな連携など、様々な形でユーザビリティが改善された。

Real IntentのCEO Prakash Narain氏によると、CDC検証ツール「Meridian CDC」はRial Intentの旗艦製品としてエンハンスに力を注いでいるという。

2012.01.12

2012年1月12日、クラウドサービスやモバイルアプリケーション開発を手掛ける株式会社ランディードは、フリーのCPUエミュレータ「QEMU」を用いたシミュレーション環境構築支援サービスの提供開始を発表した。

発表によるとランディードの提供するサービスは、顧客のニーズに応じて「QEMU」をベースとしたシミュレーション環境を構築するもので、新規アルゴリズムの開発やファームウェア開発など組込みシステム開発の効率化を側面支援するもの。

ARMプロセッサをターゲットとしたシミュレーション環境やQEMUとSystemCを接続したシミュレーション環境も構築可能で、「QEMU」を利用する事により特定のツールベンダに依存しない安価なシミュレーション環境を構築できるとしている。

「QEMU」はx86上で様々なプロセッサをエミュレートできるオープンソースのCPUエミュレーターで、ARM、MIPS、PowerPC、SHなどのCPUもサポートしてているため、組込みシステム開発においても利用されるケースがある。昨年12月には約8年間の開発を経てバージョン1.0が公開された。

ランディードは2010年設立のベンチャーで、企業向けにクラウド端末の企画・開発やシステム実装サービスを提供しているほか、コンスーマ向けのアプリケーション開発も行なっている。

2012.01.12

2012年1月10日、タイミング解析ツールを中心としたEDAソリューションを手掛ける米Incentia Design Systemsは、米Triad Semiconductorが同社の静的タイミング解析ツール「TimeCraft」を採用した事を発表した。

発表によるとTriad Semiconductorは、旗艦製品のミックスド・シグナルASIC「VCAシリーズ」の開発フローにIncentiaのSTA「TimeCraft」を採用。ツールの性能と合わせてコスト・パフォーマンスが評価された。Triad Semiconductorは、「Via-Configurable Array (VCA) 」と呼ぶ独自の特許技術でミックスド・シグナルASICを実現している。

2012.01.12

2012年1月9日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米AldecとVHDLを専門とする設計トレーニング会社SynthWorksは、VHDLユーザー向けの検証メソドロジ「OS-VVM」のリリースを発表した。

発表によると「OS-VVM(Open Source VHDL Verification Methodology)」は、文字通りオープンソースとして公開される無償のパッケージで、VHDLユーザーにファンクショナル・カバレッジ、制約付きランダムテスト、カバレッジドリブン・ランダムテストといった検証手法を提供するもの。

カバレッジドリブン・ランダムテストとは、ファンクショナル・カバレッジの実行結果によって、ランダム・スティミュラスの生成を制御する手法で、これによりテストケースの数を必要最小限に抑える事が可能になるという。

これまで世に送り出されてきたVMM、OVM、UVMといった検証メソドロジは、いずれもSystemVerilogをベースとしたもので、VHDLをベースとした検証メソドロジは無かった。そこでAldecとSynthWorksは新たな言語の習得を必要としないVHDLユーザーのための検証メソドロジを開発した。

Aldecの示す「OS-VMM」の利点は以下の通り。(Web記載情報抜粋)

・先進のランダマイゼーションおよびファンクショナル・カバレッジ機能にアクセスし、どのようなテストベンチでも使用できます。(以前はシステムレベル手法でのみ利用可能でした。)

・制約付きソルバを使うよりも、ファンクショナル・カバレッジのモデルとのやり取りを行うことで、ランダムのバランスがとれ、結果としてシミュレーション・サイクルが短くなります。

・ダイレクテッド、アルゴリズム、ファイルベースの手法などが容易に混在できるプロシージャコードと、追加のランダマイゼーションを使うことにより、初期のランダマイゼーションを改善します。

・容易な使用モデルにより、ユーザはVHDLを使い続けるための自由度と柔軟性を維持しながら、迅速に速度を向上させることができます。

尚、「OS-VMM」はAldecのWebサイト上からダウンロード可能で、Aldecのシミュレーターで無償で利用できる。Aldecはホワイトペーパー、ユーザガイド、サンプルデザイン、VHDLパッケージソースファイルを含む追加リソースも用意しているとの事。SynthWorksは「OS-VMM」の保守管理を担当しつつ「OS-VMM」のトレーニングや「OS-VMM」で利用するスコアボードやメモリ、抽象インタフェース用の追加パッケージ等を提供するという。

2012.01.11

2012年1月10日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、中国の専業ファウンダリShanghai Hua Hong NEC Electronicsが同社のカスタムIC設計ツール「Laker」ならびにデバッグツール「Verdi」を採用した事を発表した。

発表によるとHua Hong NECは、プロセスデザイン・キット(PDK)開発にSpringSoftのカスタムIC設計ツール「Laker」を採用し、0.13μm組み込みFlashファウンダリ・プロセス対応の「Laker PDK」を自社の顧客向けにリリースした。同PDKと「Laker」を活用すれば、カスタムチップのフィジカル・レイアウトを自動化し、開発期間を短縮できるという。

またHua Hong NECは、カスタムIC設計ツール「Laker」と合わせてデバッグ環境「Verdi」も採用し、自社の検証リファレンスフローに統合した。

2012.01.11

2012年1月10日、SystemCからの高位合成ツールを手掛けるForte Design Syntemsは、同社のCTOであるJohn Sanguinetti氏が2011年ACMフェローに選出された事を発表した。

※ACM:Association of Computing & Machinery

発表によるとJohn Sanguinetti氏のACMフェロー選出は、ハードウェア・シミュレーションに関する同氏の貢献を称えたもの。John Sanguinetti氏は約20年間に渡りコンピューター・アーキテクチャ、パフォーマンス解析、デザイン・ベリフィケーションに関する活動に従事してきており、DEC、Amdahl、ELXSI、Ardent、NeXT computer manufacturersと複数企業を経て1991年にChronologic Simulationを設立。1995年まで社長を務めた。

John Sanguinetti氏は、論理シミュレーターVCS(Verilog Compiled Simulator)の主要な開発者の一人で、Verilog言語を用いた設計コミュニティに大きく貢献。1992年から1995年までVerilog言語の標準化組織「Open Verilog International」の役員を務め、Verilog言語のIEEE標準化にも貢献した。

John Sanguinetti氏は、Chronologic SimulationがViewlogicに買収された後、1997年にCynAppsの設立に参画。その後CynAppsはChronologyと合併し新会社Forte Design Syntemsが生まれ、同社のCTOに就任。現在に至っている。

ACMフェローは、会員数8万人を誇る世界最大の国際計算機学会であるACMの会員の約1%のみに与えられる名誉ある地位で、2011年のACMフェローにはJohn Sanguinetti氏を含む35名が選出されている。

2012.01.11

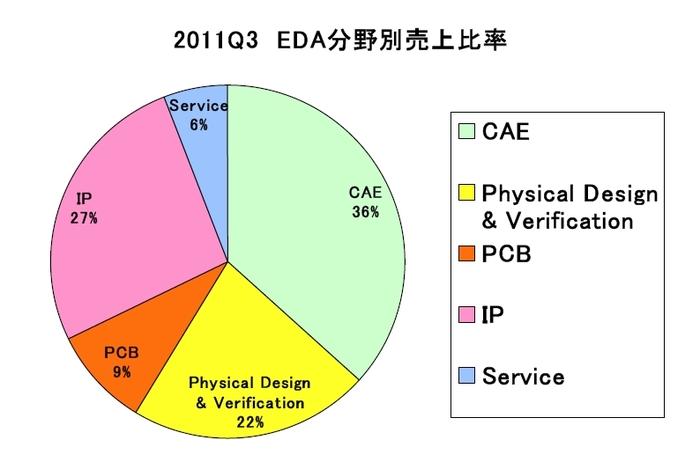

2012年1月10日、米EDA Consortiumは、2011年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

EDACの発表によると、2011年Q3(7月-9月)の世界のEDA売上総額は、前年比18.1%増、前Q2比7.4%増の15億4390万ドルで四半期売上記録として過去最高を記録。直近の4四半期の平均アベレージをQ3時点の前年比16.3%増から17.8%増へと押し上げた。半導体関連各社は軒並みQ3売上を落としたがEDA売上への影響は未だ現れていない。世界半導体市場は、Q4も引き続き厳しい状況と予測されているが、EDA業界への影響は2012年Q1以降に現れると思われる。

分野別売上でみると、全ての分野で売上前年比2ケタ増を達成。特にIP分野は37.4%増と非常に強い伸びを示した。同分野のこの1年間の平均アベレージは前年比28.4%増となっている。

地域別売上についても、全ての地域で前年比2ケタ増を達成。特に北米とアジアその他地域がそれぞれ22.4%増、17.6%増と強い伸びを示した。日本市場は前年比11%増でこの1年間の平均アベレージを16%増とした。

2011年Q3時点でのEDA業界の従業員数は27162人で、前期Q2比1.7%増となっている。

2011年Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 5億6670万ドル 10.5%Up

■IC Physical Design & Verification分野 3億3830万ドル 16.0%Up

■IP分野 4億1000万ドル 37.4%Up

■サービス分野 8870万ドル 13.1%Up

■PCB/MCM分野 1億4030万ドル 11.6%UP

2011年Q3地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億670万ドル 22.4%Up

■ヨーロッパ 2億5790万ドル 14.9%Up

■日本 2億5690万ドル 11.1%Up

■アジアその他地域 3億2240万ドル 17.6%Up

2012.01.10

2012年1月9日、Cadenceは、同社のメモリ・インタフェース設計用IPがOpen NAND Flash Interface (ONFI) 3.0仕様をサポートした事を発表した。

Cadenceの提供するメモリ・インタフェース設計用のIPは、2010年のDenali社の買収によって製品ラインナップに加わったもので、以前は「Databahn」の名で提供されていたもの。PCI Express、DDR-SDRAMメモリ、NANDフラッシュ・メモリなどのチップ・インターフェイス向けに様々な設計IPが用意されているが、今回NANDフラッシュ・メモリの設計IPとして、新たにOpen NAND Flash Interface (ONFI) 3.0仕様をサポートしたController IPとPHY IPがリリースされた。

Open NAND Flash Interface (ONFI) 3.0仕様は、NANDフラッシュ・メモリのインタフェース仕様の標準化団体「ONFI」の策定する標準インタフェース規格で、昨年の3月に3.0仕様がリリースされていた。同標準仕様をサポートする設計IPはCadenceの製品が業界初となる。

尚、CadenceのNANDフラッシュ・メモリの設計IPは、ONFI 3.0と合わせて東芝およびサムスンの推進する「Toggle DDR 2.0仕様」もサポートしているという。

2012.01.10

2012年1月9日、Mentor Graphicsは、流体解析(CFD)ソフトを手掛けるの英Flowmaster Groupの買収を発表した。

発表によるとFlowmaster Groupは、1次元の熱流体解析ソフト「Flowmaster」の提供で20年以上の実績を持つソフトウェア・ベンダで、航空、自動車、船舶、資源開発、インフラ開発など様々な分野でワールドワイドに製品を展開。日本では伊藤忠テクノソリューション社が代理店として製品を提供していた。

今回のMentorによるFlowmaster Groupの買収は、2008年に行った熱流体解析ソフト業界首位Flomericsの買収を補完するもので、熱流体解析ソフト分野におけるMentorのポートフォリオを更に拡張。Mentorは1次元解析から3次元解析まで対応する業界一の熱流体解析ソフト・ベンダとなる。

尚、今回の買収に関する条件等は未公開。買収したFlowmaster Groupは、MentorのMechanical Analysis Divisionに取り込まれるようだ。

2012.01.07

各組織の発表している現時点での2012年世界半導体市場成長予測をまとめてみました。

2012.01.07

2012年1月6日、アナログ/カスタムIC向け自動レイアウトツールを手掛ける、米Ciranova社は、2011年の売上が過去最高を記録したことを発表した。

発表によるとCiranovaの2011年売上は2010年の倍を記録。その原動力となったのはアナログ/ミックスドシグナル・デザインのフロアプランおよび自動配置を実現するツール「Helix」で、28nm以下の設計ニーズに応えた。

Ciranovaによると、ファブレス半導体ベンダTOP10のうちの2社が新規顧客となり、複数の既存顧客から追加発注を獲得した。また、OpenAccessベースのPCell作成環境「PyCell Studio」についても複数顧客が20nmプロセスで採用したという。

微細化により配置がより複雑になった事で、Ciranovaの提案する手作業から自動化への流れが促進しているようだ。同社はSynopsys、Mentor、Intelから出資を受けている。

2012.01.06

DRAM価格の下落により2010年の急成長から一転、2011年はマイナス成長となった半導体メモリ市場。年明け早々に不振のエルピーダメモリと東芝が統合するという噂が広がるなど、業界は引き続き混迷の様相を強めている。DRAMおよびNANDフラッシュメモリの2大メモリ市場でトップを走るサムスンもウォン高が進行すると収益の悪化は必至で、半導体メモリ市場は先の読めない状況が続きそうである。

ここではそんな半導体メモリ市場をいずれ変えて行くであろう、DRAM、NANDフラッシュに続く次世代メモリ「SCM(Storage Class Memory)」に関する話を紹介したい。

今更ではあるが、昨年9月7日に開催された「Synopsys Users Meeting 2011(JSNUG2011)」にて、東京大学竹内健准教授による講演「仮想プラットフォームを用いたストレージ・クラス・メモリ(SCM)搭載SSDのアーキテクチャ探求」の内容を紹介する。

■SCM(Storage Class Memory)とは

東京大学 工学部 電子工学科 准教授である竹内氏は、東芝で15年間に渡りNANDフラッシュ・メモリの開発に携わってきた人物で、2007年から東京大学での研究活動をスタート。メモリに関連する様々な研究活動を行なっている。(※詳細は竹内研究室HP参照)

竹内氏が講演で紹介したのは、現在進行中の数々の研究活動の一つである「SCM(Storage Class Memory)」の開発に関する話。「SCM」はDRAMとNANDフラッシュの中間に位置する次世代のストレージ向けメモリとしてIBMが作った言葉で、竹内氏曰く、単純に言うとNANDフラッシュメモリとメインメモリとの間にもう少し高速な不揮発性メモリを入れてあげようという考えから生まれたもの。定義としては、NANDフラッシュのように不揮発で、DRAMと同等とは言えないがフラッシュよりケタ違いに高速、NANDフラッシュ並みに大容量、HDDより信頼性が高く少面積で軽いとされている。技術的な候補としては、PRAM、MRAM、ReRAMなど複数あるが、まだ標準と言える技術は無くメモリの世界では今まさにホットな技術分野であると言える。

※画像はIBMのデータ。竹内氏の講演とは無関係。

竹内氏は1年ほど前から「SCM」の研究開発に着手。未だ学会発表などは行なっていないが(11年9月時点)、東芝、シャープ、エルピーダといったメモリ関連大手と共同で開発を進めており、自身はメモリ・アーキテクチャを担当。デバイスを作るだけではすぐに韓国勢らにコスト戦略で追いつかれてしまうので、メモリ・アーキテクチャの検討に力を注ぎ、米ラムバス社のようにメモリの仕様を牛耳る形を目指したいとする。

■肝はNANDコントローラー

竹内氏によると、NANDフラッシュ・メモリのスケーリング凄い勢いで進んでおり、現在20数nmで64Gビットが最大容量。単位チップ面積あたりの記憶容量は年平均3倍のペースで伸びており、プロセス微細化の最先端を突き進んでいるが、もはや限界を迎えつつある状況。そこでSSD(Solid State Drive)やNANDフラッシュ・メモリを縦型に繋げる3次元構造のメモリなども注目されはじめている。

※画像は竹内氏の講演資料からの抜粋。

SSDは東芝やサムスンが販売しているが、フラッシュ・メモリと共に搭載しているコントローラーが肝となる製品で、これはSSDに限らずUSBメモリやSDカードにおいても同じ。何故コントローラーが肝になるかと言うと、NANDフラッシュ・メモリは微細化するほど遅くなり、3000-4000回書き込むと確実に壊れるためウェアレベリング等を行うコントローラーの付加価値が高まるため。東芝がサムスンとの差別化に成功しているのは、コントローラー開発における「知恵の勝負」の結果だという。また、最近のメモリ開発ではOSも含めてカスタムおよび最適化する方向に移行しつつあり、竹内氏がメモリ・システムのアーキテクチャ検討に力を注ぐのはそのような背景があるため。竹内氏は、世の中の水平分業という流れよりも、むしろ垂直統合で様々なシステムを取り込む方が良いメモリを開発できると主張する。

※画像は竹内氏の講演資料からの抜粋。

■SSDの利点とNANDフラッシュの限界

SSDが注目される理由は他にもある。それはストレージとメモリの間にある大きなギャップを埋めるという期待で、実際に読み出し速度に関しては性能差を1ケタ程度に縮める事が可能なため、データの読み出しが中心となるエンタープライズのデータセンター等で高速化と低電力化を目的に利用されようとしている。しかし、書き込み速度の遅さはNANDフラッシュ・メモリの物理的な原理から解消できず、ギガ超えが当たり前となってきている各種インタフェースの進化に追いつかない状況となっている。NANDフラッシュ・メモリ業界では複数のNANDフラッシュ・メモリを同時に動かすという取り組みを行なっているが、電力が爆発的に増えてしまうため、これ以上NANDフラッシュ・メモリの性能向上は見込めない。そこで次に「SCM(Strage Class Memory)」が注目されるようになった。

※画像は竹内氏の講演資料からの抜粋。

竹内氏によると、SCMがモバイル端末で利用されると、無圧縮のデータをストレージを通じてネットワークへ高速にデータ転送可能となり、モバイル端末の大幅な性能向上が見込めると同時に消費電力の削減にも繋がる。また、消費電力の削減という側面では、データセンターにおける消費電力の削減に有効で、データセンターのコストの半分以上を占めている冷却費込みの消費電力を大幅に削減できる見込みであるほか、将来的には、ノーマリ・オフ・コンピューティングの実現にも貢献する可能性があるという。

※画像は竹内氏の講演資料からの抜粋。

■SCMのアーキテクチャ検討はESLツールで

竹内氏はSCMの研究開発としてSCMを搭載したSSDのアーキテクチャ探求を進めており、性能や信頼性など様々なトレード・オフを行うためにSynopsysのバーチャル・プロトタイピング環境「Platoform Architect」を活用し、メモリの開発と同時にCPUなどのセットを想定してシステム・レベルで性能や電力を見積っている。SCMはDRAMとNANDフラッシュの良いところを取った中間的なデバイスであるため、周辺のDRAMやNANDフラッシュ・メモリを含めてどのようなメモリ・アーキテクチャを構成するかが非常に重要で、SCMを実現するための信号処理(誤り訂正)も鍵となってくるという。

※画像は竹内氏の講演資料からの抜粋。

竹内氏曰く、従来は大手顧客の要望通りのメモリを開発していたが、最適なメモリを開発するためにはアーキテクチャからと、次のステップでは、メモリ・アーキテクチャを考えながらメモリに最適なCPUやコンパイラの開発などにも取り組む計画であるとの事。現在のところは、SSDの中のSCM、NANDフラッシュ・メモリ、NANDコントローラなどをSystemCでモデリングしシミュレーションを実施しており、いずれ半導体ベンダと組んでプロセッサ・モデルを作る予定。3年後を目処にDRAMよりも1ケタ遅いがNANDフラッシュよりも2ケタ速く、コストはDRAMとNANDフラッシュの中間に位置するというSCMを世に送り出す計画だという。

2012.01.04

約1ヶ月前の2011年12月2日、新横浜のホテルでパワー解析および最適化ソリューションを手掛ける、米Apache Design Solutions社主催の「Apache Technology Forum 2011」が開催された。

ここでは同セミナーで行われた、コバレントマテリアル株式会社 シニアアドバイザー 香山晋氏による基調講演「エレクトロニクス/半導体産業における「エネルギー問題社会」について紹介する。

香山晋氏は、東京大学工学部卒業後、1969年に東芝に入社し以降30年近く半導体の研究開発に従事していた人物で半導体の世界では著名な存在。2004年に東芝の執行役員上席常務(電子デバイス事業グループCTO)を経て、東芝セラミックス社長に就任してからは、シリコンウエハ、半導体製造部材に関わるようになり、2007年6月に経営陣による企業買収(MBO)という形で東芝グループから独立。新会社コバレントマテリアル株式会社を立ち上げ約4年間社長を務めた。

香山氏は現在、会社経営の一線から退き個人事務所を開設。「もう一度日本でアプリケーション・プロセッサ開発を」と事業開発に取り組んでいるということで、過去から遡り現在浮き彫りとなっているエレクトロニクス産業ならびに半導体産業の課題について語った。

■半導体における古典的なスケーリングの破綻

まず香山氏が指摘したのは、自己達成型の予言ともいえるムーアの法則の限界、即ち半導体における古典的なスケーリング戦略の行き詰まりだった。香山氏曰く、結局のところ半導体の微細化を牽引してきたのは半導体の価格であり、微細化によって半導体のゲート単価は下がり続けてきたが、22nm以降はそれも限界。これまでは微細化によりコスト低減という恩恵を得られたが、今後はダブルパターニングやEUVなどの必要性からむしろコストは増える方向となり、これをどう正当化するかは重要であると強調。更にウエハの大口径化はコスト増に拍車をかけることになり、450mmウエハは現実的では無いと語った。

■ロードマップの在り方と半導体産業の健全性

香山氏は半導体スケーリングの破綻を語る中で、プロセス微細化とウエハ大口径化を関連付けるかのようなITRSの半導体技術ロードマップを取り上げ、そもそも半導体の微細化とウエハの大口径化は無縁であるはずと指摘。しかし、実際にロードマップに従うように微細化、大口径化が進み、それがファブの高コスト化を生み出し半導体産業の寡占化を招いたとして、ロードマップのあり方についても考える必要がある時代だと主張した。また合わせてプロセスの微細化に伴うファブの寡占化を表す図を示し、製造面での競争が制限されている現在の半導体産業の形を今後も許すのか? この状況はエレクトロニクス産業として健全なのか?と疑問を投げ、国全体が影響力のないロードマップに準拠してしまっては競争力が失われるのは明らかで、日本はその状況に陥りつつあると警鐘を鳴らした。

※香山氏が講演スライドで紹介した図

■今後のLSI開発と注目すべき技術

微細化による限界の克服に向けて香山氏は、3次元化などの実装技術の革新が必要であり、異なるチップを自由に集積できる技術が確立されれば、従来の微細化の延長線上から違った世界が展開される可能性があると語り、当面は2.5Dが加速するだろうと予測。3次元化に伴う新技術として、内部配線のボトルネックを克服するワイヤレス・インターコネクトやオプティカル・インターコネクトにも注目しているとの事で、既存のマルチコア・チップにおいてもチップ上にネットワークを組む上でインターコネクト技術は重要であるとした。

また、チップのマルチコア化については、僅かな性能向上のために膨大な電力を消費しなければならない現状を打破するには、省電力に向けた電力の動的制御、デバイス構造の改善、ソフトウェアの改善など複合的な対処が必要で、中でも並列演算の効率化は最大のチャレンジであると指摘。これら課題に取り組むためには、最終的に優れた技術者の能力と道具が必要不可欠であり、日本においてEDAへの投資が遅れているのは問題だとした。

■チップのパワー・マネジメントと都市設計

香山氏は講演の最後に、チップのマルチコア化に伴うパワー・マネジメントは、大都市におけるスマート・グリッドと共通点が多いというユニークな持論を展開。具体的には、大都市とLSIは似ていて、いずれも電力やエネルギー効率など技術開発のテーマがパワーの整理に集約しつつあり、チップ設計というミクロの世界と都市設計というグローバルな世界で本質的な共通点があるというもの。

結論として香山氏の主張は、LSIのパワー・マネジメントの手法や考え方などはスマート・グリッドにも応用できるはずというもので、LSIにおけるパワー・マネジメントと比べると国内のスマート・グリッド分野で行われている議論は低品位で、そこには先端LSI設計者の知恵が必要な状況であるとのこと。スマート・グリッドに限らず医療機器の実装などにおいても似たような状況があるという話で、香山氏は、優秀な日本の半導体技術者の知恵は様々な分野で活用することが可能。その知恵とスキルを活かし

て新たな分野に意欲的に進出して欲しい。今はチャンスの多い時代だ。と熱く語った。

2012.01.03

2012年1月2日、米SIA(Semiconductor Industry Association)は、2011年11月の世界半導体売上高を発表した。

SIAの報告によると、2011年11月の世界半導体売上高は前年同時期比約3.1%減、前月比約2.4%減の251億3000万ドルという統計結果となった。

2011年の売上累計は現時点で2768億6000万ドルとなっており、2010年の11月時点よりも0.8%増という状況。SIAも支持している2011年売上合計が3020億ドルに達するというWSTSの予測はほぼ確実となった。

※WSTS:World Semiconductor Trade Statistics

地域別の売上で見ると日本市場の売上は10月比1.7%減の38.2億ドルで世界市場の約15.2%、5ヶ月ぶりに前月を下回る結果となった。9月-11月の3ヶ月のアベレージは他地域よりも突出して伸びているが、11月単月では前年比8.2%減だった。

2011.12.21

2011年12月20日、Mentor Graphicsは、同社のエミュレーター「Veloce」向けにプロトコル・トランザクタをリリースした事を発表した。

発表によると「Veloceトランザクタ」という呼称で提供されるプロトコル・トランザクタは、ARM AMBA AXI/AHB/APB、USB、PCI Express、SAS、SPI、I2C、I2Sなどの各標準規格に対応するもので、同トランザクタを利用すれば、SystemVerilog、OVM/UVM、SystemC/Cベースのシミュレーション・テストベンチから生成されたスティミュラスをVeloce上のDUTに適用可能。これにより複数のプロトコル・インタフェースを備えたDUTの高速なトランザクションレベルのテストが可能となる。

「Veloceトランザクタ」は、Veloceのトランザクションベースのアクセラレーション・モードとエミュレーション・モードの両方で利用する事が可能で、シミュレーションと同じテストベンチを使用できるため、テストの高速化と合わせてテストベンチの開発工数の削減にも繋がる。

2011.12.20

2011年12月19日、オープンコアプロトコル(OCP)の普及団体OCP-IPは、「Contributor Of the Year Award 2011」の受賞者がCadenceに決定した事を発表した。

プレスリリース文

http://www.businesswire.com/news/home/20111219005038/en/Cadence-Wins-OCP-IP-Contributor-Year-Award

発表によるとOCP-IPは、 Functional Verification Working Groupの活動における同WGチェアマンのGABRIELE ZARRI氏(Verification IP Solutions Architect for Cadence Design Systems)およびCadenceの功績を評価。同氏の所属するCadenceに賞を贈った。

GABRIELE ZARRI氏は、2011年Q1にリリースされたコンプライアンス・チェックおよび機能カバレッジを含む「OCP Compliance document」の最新版の作成にあたり、重要な役割を果たした。同仕様はCadence以外にMIPS, Sonics, Texas Instrumentsらの協力によって開発された。

尚OCP-IPでは現在、次世代のヘテロジニアス・マルチコア・プロセッサ向けの標準インタフェース仕様の開発を進めているという。

2011.12.20

2011年12月8日、米Electronic Design誌は恒例の「Best Electronic Design Award 2011」の受賞者を発表した。

「Best Electronic Design Award」は米Electronic Design誌が2002年から表彰を始めたアワードで、同誌スタッフおよびエディターらによって今年一年の優れた製品・サービスをカテゴリ別に表彰するもの。今年EDA部門で受賞したのは下記2製品だった。

? Mentor Graphics

Calibre RealTime/Springsoft Laker layout system

SpringSoft社のカスタムIC設計環境「Laker」とシームレスに繋がるリアルタイムDRC

http://www.mentorg.co.jp/products/ic_nanometer_design/news/2011/110311_02.html

? Altium

Altium Designer 10

WindowsベースのPCBおよびFPGA設計統合環境

http://www.altium.com/jp/altium_home.cfm

尚、SpringSoftは昨年「Laker Custom IC layout system」でBest of 2010 EDA部門を受賞している。

2011.12.16

2011年12月15日、GLOBALFOUNDRIESとARMは、 28nmプロセスで製造したdual-core Cortex-A9 processorベースSoCのテストチップと20nmTQVのテープアウトを発表した。

発表によるとGLOBALFOUNDRIESの28nm HPP(High-Performance plus)プロセスとARMのフィジカルIPの「Artisan」を用いて作製された、dual-core Cortex-A9 processorベースSoCのテストチップは、業界初となる2.5GHzを超える動作周波数を記録。また両社は、GLOBALFOUNDRIES初の20nmプロセスを用いた同Cortex-A9 processorベースSoCのTQV(Technology Qualification Vehicle)のテープアウトに成功した。TQVはCortex-A9 processor向けに最適化されたプロセス・テクノロジを開発するための試作で、GLOBALFOUNDRIESの次世代20nmプロセス・テクノロジを用いる事で28nmプロセスよりも35%の性能向上と消費電力の半減が見込めるという。

尚、20nmプロセスのTQVは、Synopsysのインプリメント・ツール「IC Compiler」、寄生抽出ツール「StarRC」、タイミング解析ツール「PrimeTime」によって設計され、ダブル・パターニング技術が適用されているとSynopsysが別途発表している。

2011.12.15

2011年12月14日、Cadenceは、同社のエミュレーション・システム「Palladium XP」をパナソニックが導入した事を発表した。

発表によるとパナソニックは、次世代のデジタル・コンシューマ製品向けのSoC設計を加速するためにCadenceの「Palladium XP」を導入。自社の検証環境を「Palladium XP」に接続したシステムレベルのハードウェア・ソフトウェア協調検証を行う事によりSoCの開発期間を短縮した。

パナソニック デジタルコア開発センター 所長 藤川 悟 氏のコメント:

「デジタル・コンシューマ製品がますます複雑になるにつれ、それら製品の中枢となるSoCの検証も複雑になっています。Palladium XPシステムにより、高度に複雑なSoC設計をシステムレベルで検証できました。また、チップレベルでの検証は加速され、予測性が向上、その結果製品の市場投入期間に対する要求に応えることができました。」

Cadenceの「Palladium XP」は、エミュレーションおよびアクセラレーション機能を備える検証プラットフォームで、最上位製品の「Palladium XP GXL」は、最大で20億ゲート規模のデザインに対応。512ユーザまで同時利用可能で実行速度は最大4MHzを実現する。

これまでの「Palladium」は、エミュレーション/アクセラレーション・システムとして独立した単独製品というイメージが強かったが、システムレベルのバーチャル・プロトタイピング環境「Virtual System Platform」、論理シミュレーター「Incisive」、FPGAベースプロトタイピング環境「Rapid Prototyping Platoform」と繋がり、現在は「System Development Suite」の一部として各ツールとの連携利用が可能となっている。用途としてはトランザクション・ベースのアクセラレーションでのニーズが高く、「AVIP」と呼ぶアクセラレーション用の検証IPも用意されている。

尚、「Palladium」は、かの世界最速スパコン「京」のインター・コネクト・チップのシステム検証にも利用された実績がある。

2011.12.09

2011年11月16-18日、パシフィコ横浜で開催されたEDSFair 2011NovおよびEmbedded Technology 2011に出展していた、検証関連製品を展示していた企業のブース・レポート。

・株式会社スピナカー・システムズ

スピナカー・システムズは、Embedded Technology 2011にブースを構え、この11月より取り扱いを開始したイスラエルvSync Circuits社のCDC(クロック・ドメイン・クロッシング)設計・検証ツール「vGenerator」、「vChecker」を展示していた。同社のソリューションの特徴は、既存のCDC検証ツールのようにシミュレーションでは検証できないCDC問題を静的に検証すると同時に、その解決策として同期ロジックを自動生成してくれる点。

「vChecker」はCDCの静的検証とCDCの管理を行うツールで、「vGenerator」は各プロトコル・インタフェース要求と対象CDCに対して、絶対に危険のない同期用のシンクロナイザを自動生成する事が可能。両ツールを組み合わせて利用すれば、安全なCDCインタフェースのデザインを実現できる。

「vChecker」および「vGenerator」は、Verilog,SystemVerilog,VHDLをサポートしており、「vChecker」による静的検証はRTLとゲート・レベルに対応。「vGenerator」はメジャーなFPGA設計フローをサポートしており、ランダム検証用のシミュレーションモデルや合成制約の自動生成機能も備えている。

スピナカー・システムズの片桐社長によると、vSync Circuits社のCDCソリューションを利用すれば非同期設計が非常にラクになるため、非同期設計によって回路の低消費電力化を実現しているユーザーもいると聞いた。

※画像は「vGenerator」および「vChecker」の説明パネル

・CMエンジニアリング(株)

CMエンジニアリングは得意分野である検証ソリューションをはじめ、幾つか初めて目にするサービスを紹介。ブースはなかなかの人の入り様で熱気を帯びていた。

まず目を引いたのが、ミックスド・シグナルLSIのターンキー・サービス。これは設計サービスでも実績の高い同社の強みを生かしたサービスで、製品の小型化や低消費電力化、ディスコン製品の再設計などのニーズを意識したもの。短納期・低コストをうたう同サービスでは、仕様設計からGDSIIまでをCMEが対応。その先の製造に関しても面倒をみてくれる。

また、ミックスド・シグナルLSIのターンキー・サービスとも関連性ある新サービスがIPリフレッッシュ・サービス。同サービスは回路データ(CまたはRTL)から仕様書を起こし、更に回路の最適化、検証まで実施してくれるというもの。再利用が困難であった既存資産の復活などをCMEが手助けしてくれるという。

いずれのサービスも検証および設計エキスパート集団としての同社のノウハウが活かされたものと言えるが、同社はそのノウハウを出展社セミナーでも披露。「仕様書の書き方のコツ」、「アナログモデリング手法による開発TAT短縮のコツ」、「消費電力削減のコツ」などを紹介した3種類の出展社セミナーはいずれも好評だったようで、初日の「仕様書の書き方のコツ」は立ち見の出る盛況ぶり。「消費電力削減のコツ」では、乗算器1個のレベルからコツコツやる「節電式」のローパワー手法の他、「ローパワー・リフレッシュ・サービス」なる既存資産のローパワー化サービスも紹介されていた。

CME社の長谷部氏によると、検証キット「SAQuT!」シリーズ製品も好調で、後発のアナログモデリング向けのキット「SAQuT! AMS」も引き合いが多く、実績が出始めていると聞いた。

※画像はCME社の展示パネルとセミナー資料抜粋

・日本イヴ(株)

EVEのブースではEDSFair2011が初披露となる新製品「ZeBu-Blade2」を大々的に展示していた。「ZeBu-Blade2」は、Xilinxの40nmFPGA「Virtex6」をベースにしたエミュレーション・プラットフォームで、Virtex-6を5個または9個搭載する2種類の製品があり、それぞれ1800万および3200万ASICゲートのデザイン容量を備えている。

展示されていた「ZeBu-Blade2」の筐体は確かに小型でデスクトップサイズと呼べる大きさ。このシステムで最高40MHzに達する高速エミュレーション性能を実現。デザイン容量的には現在のASICデザイン規模の約70%はカバーできるだろうとの話で、その費用対効果には絶対的な自信を持っているという。

尚、EVEはEDSFair2011の最終日に近隣のJAZZクラブでパーティーを開催。同社の顧客やEDA業界関係者など100人を優に超える参加者を集めた大規模なパーティーで、ショーありコンテストあり、同社の本社CEOであるLuc Burgun氏がバンド演奏を披露するなど、DAC名物のDenaliパーティーさながらの盛り上がりを見せていた。

※画像は「ZeBu-Blade2」の筐体と展示の様子

・スプリングソフト(株)

SpringSoftのブースでは、今年5月に発表したプロトタイプボードのデバッグ・ソリューション「ProtoLink」が展示されていた。「ProtoLink」は、FPGA内部の信号をFPGA内のブロックRAMを使用することなく大量かつ高速にプローブする事ができるツールで、論理合成・配置配線を繰り返すことなくプローブポイントを変更する事が可能。ブローブしたデータを元に同社のデバッグ環境「Verdi」上で論理回路をRTLベースでデバッグすることができる。

SpringSoft KK社長の河原井氏によると、「ProtoLink」は既に海外顧客の導入実績があり日本国内の顧客からも引き合いが多数あるとの事。また、富士通セミコンダクターのデザインサービス「Cedar-ESL」でも、ESL環境とFPGAボードを繋ぐキーとなるツールとして採用され話題を集めていた。同社ではコ・エミュレーション環境の実現に向けた取り組みに力を注いでいるという。

また今年10月に開設した「Verdi」向けカスタム・アプリの開発・利用促進サイト「VIA Exchange」については、現在SpringSoft自ら開発した「Verdi」向けのカスタム・アプリケーションをWeb上にアップしており、予定では200種類ほどのアプリケーションがWeb上に登録される計画との事。同サイトは現場設計者に限らず学生の利用者も多いと聞いた。

※画像はSpringSoftブースの展示の様子と、富士通セミコンダクター「Cedar-ESL」のブローシャ。

・アルデック・ジャパン(株)

Aldecのブースでは、UVMサポートを発表したばかりの論理シミュレーター「Riviera-PRO 2011.10」、「Riviera-PRO」とエミュレーション・プラットフォーム「HES」を接続して効率的なデバッグ環境を提供する「HVD(Hardware Visibility-based Debugging)」テクノロジなどが紹介されていた。「HVD」は今回のEDSFair2011が初披露だった。

UVMサポートに伴い「Riviera-PRO」ユーザー向けに用意されるUVMレジスタ・キットは、UVMのスターター・キットとして、OVMからUVMへの検証環境の移行を手助け。OVM/VMM相互運用キットは、既存資産にラッパーを被せるイメージでOVMおよびVMMベースIPの単一環境動作を実現する。

Aldecでは現在キャンペーンにより、FPGA設計向けの論理シミュレーター「Active-HDL」のDesigner Editionを定価の半額の¥99,000ーで提供中との事だった。(2012年3月末まで)

※画像はAldecブースの様子

・プロトタイピング・ジャパン(株)

プロトタイピング・ジャパンは、エイシップ・ソリューションズと共同でJEVeCビレッジ内に出展。主軸のプロトタイピング・ボード製品のほか、複数の製品を展示していた。

プロトタイピング・ボードとしてはAltera版とXilinx版の双方をラインナップする米S2C社の製品、コストパフォーマンスの高いAltera搭載の米IRIS Technologies社の製品、Alteraベースでミドルエンドのデザインを狙う台湾Terasic Technologies社の製品、ARMアプリケーションのプロトタイピングに強い韓国Huins社の製品を展示。

更に今年6月よりパートナーとして営業窓口を担当することになったエイシップ・ソリューションズの互換プロセッサIPや、某大手メーカーが開発し外販を検討しているという「液晶パネル用のLVDS高速インタフェース」、硬貨サイズの超高密度モジュールの製作サービスなど、プロトタイピング・ソリューションに限らず様々な製品/サービスが展示されていた。

※画像は韓国Huins社のボードと展示パネル

・(株)アイヴィス

アイヴィスのブースでは同社の取り扱う、TCAD、SW電源回路設計・解析ツール、設計IP、組込みソフトウェアのテスト自動化ツールなど様

々な製品を展示していたが、崔社長に「最近引き合いの多い製品は?」と聞いたところ、真っ先に出たのがSiSoft社のシグナルインテグリティ解析ツール「Quantum Channnel Designer」だった。

SiSoft社は、元DECでAlphaプロセッサを使った高速システムを設計していたメンバーが中心となり1995年に設立された会社で、高速システム設計向けのノウハウをベースにEDAツールを開発し、コンサルティング・サービス等にも活用している。

「Quantum Channnel Designer」は、5Gbps超の高速シリアル・リンクのSI解析ツールで、IBISモデルを用いたシミュレーションによりSPICEでは不可能な解析を実現。SerDes IPベンダなどは、業界唯一の高速シリアル・リンクのSI解析ソリューションとして「Quantum Channnel Designer」に頼らざるを得ない状況にあるという。

※画像は「Quantum Channnel Designer」の説明ボード

2011.12.09

2011年12月8日、Synopsysは、同社の物理検証ツール「IC Validator」がGLOBALFOUNDRIESにサインオフ・ツールとして認証されたことを発表した。

発表によるとGLOBALFOUNDRIESは、Synopsysの物理検証ツール「IC Validator」を同社の28nm、40nm、65nmプロセスのフィジカル・サインオフ・ツールとして認証した。「IC Validator」は2009年にリリースされた「Hercules」の後継となるDRC/LVSソリューションで、配置配線ツール「IC Compiler」とのシームレスな連携による設計を進めながらのインクリメンタルなレイアウト検証や、マルチスレッド技術による複数CPUでの高速化などが特徴。TSMCも40/65nmプロセスでサインオフ・ツールとして認証しているほか、NVIDIAによる採用なども知られている。

物理検証ツールは、Mentorの「Calibre」がデファクト・スタンダードとして強固な牙城を築いているが、配置配線ツール「IC Compiler」のシェア拡大を背景に、Synopsysは「Calibre」ユーザーの切り崩しを狙っている。

2011.12.09

2011年12月8日、パワー解析および最適化ソリューションを手掛ける、米Apache Design Solutions社の親会社Ansysは、富士通セミコンダクター社がApacheの「Totem」を採用したことを発表した。

発表によると富士通セミコンダクターは、同社の全てのカスタムIC設計用に解析・最適化ツールとしてApacheの「Totem」を採用。アナログ、メモリ、高速I/O、PMIC(パワーマネージメントIC)、RF ICの設計に「Totem」を使用するという。

Apacheは大きくデジタル向け、アナログ・ミックスドシグナル向け、パッケージ/ボード向けにパワー解析および最適化ツールを提供しており、「Totem」はアナログ/ミックスドシグナル設計に対応するフルチップ、レイアウトベースのパワー・ノイズ、信頼性解析ツールとして、アナログ回路の設計に伴う電源ノイズ、基板ノイズ、パッケージ/PCB の容量性/誘導性ノイズの正確な解析を実現する。

富士通セミコンダクター、開発・製造本部 共通テクノロジ開発統括部第四設計技術部 伊藤 優 部長のコメント

「アパッチのTotemにより、先端プロセス技術でフルチップレベルの電源、基板、パッケージ/PCBノイズカップリングを正確にモデル化しシミュレーションすることができます。Totemを使用して、ノイズカップリングによる回路の性能への影響を解析し、重要なレイアウト変更の必要性を初期の設計段階で判断できるため、生産性の向上とリスピン(設計のやり直し)のリスクを軽減できます。」

2011.12.07

2011年12月6日、Magmaは、半導体IPプロバイダのDolphin Technology社が、Magmaの社内標準ツールとして採用した事を発表した。

Dolphin Technologyは、組込みメモリ、高性能スタンダードIO、高性能スタンダード・セル・ライブラリなど半導体IPを手掛ける企業で、発表によると同社はMagmaの回路シミュレーター「FineSim SPICE」を社内標準ツールとして採用した。「FineSim SPICE」のマルチCPU回路シミュレーション・テクノロジを利用することにより、シミュレーションのランタイムを6倍高速化し、IP品質の向上と製品市場投入期間の短縮を実現したという。

2011.12.07

2011年12月6日、SoCインターコネクト設計ソリューションを手掛ける仏Arterisは、TSMCとのコラボレーションを発表した。

発表によるとTSMCは、シリコン・インターポーザー・テスト・チップのプロジェクトにてシリコン・インターポーザー上のSoCダイに実装するインターコネクトにArterisの「FlexNoC」を選択した。このプロジェクトのゴールは、ArterisのインターコネクトIPソリューションを用いた、より効果的かつタイムリーなTSV技術の商用化で、TSMCとArterisの両社は、両社共通の顧客がこれら技術を容易に採用できるよう協業を進める。

Arterisは、TSMCのOpen Innovation Platform Partnerの一員であり、同社のインターコネクトIPは、TSMCのReference Flows 11.0および12.0に取り込まれている。