NEWS

2012.05.09

2012年5月1日、パワー解析および最適化ソリューションを手掛ける、米Apache Design社は、同社の4世代目の製品となるダイナミック・パワー解析ツール「RedHawk-3DX」のリリースを発表した。

発表によると「RedHawk-3DX」は、20nm以降のプロセス技術を見据えた新製品で、既存製品を上回る解析精度、キャパシティ、パフォーマンス、ユーザビリティを実現。動作周波数3GHz超、数億ゲート規模のデザインや3D-ICにも対応できる。

ダイナミック・パワーの解析にあたっては、テスト・ベクタを用いたRTLによるサイクル・アキュレートなシミュレーションと「VectorLess」と呼ぶ入力信号を用いない高速な解析の2つのモードを利用可能でより高精度な解析を実現。2つのモードを組み合わせて利用することも出来る。また、シミュレーション速度はエンジンの改良により最高で40%高速化されている。エレクトロ・マイグレーション解析についても、モデリング技術の向上や主要ファウンドリの20nmEMルールのサポートなどその機能が更に強化された。

その他、最新のローパワー技術をサポートするために、LDO電圧レギュレーターのビヘイビア・モデルが用意されたほか、マルチ・ダイおよび3D-ICの解析に向けて独自モデル「CPM(Chip Power Model)」の利用が可能となり、マルチ・ウインドウの新たなGUIも用意された。

2012.05.08

2012年4月30日、Synopsysは、同社の配置配線ツール「IC Compiler」でSamsungがARM Cortex-A15ベースのモバイル・デバイス向けSoCをテープアウトした事を発表した。

発表によるとSamsungは、モバイル・デバイス向けSoCにARMの最新コア「Cortex-A15 MPCore」プロセッサ・コアを300万インスタンスで実装。同SoCは同社の32nm LP high-Kメタルゲート(HKMG)プロセスで製造され1GHzを超える動作周波数を達成した。

量産ベースでのCortex-A15プロセッサ・コアのテープアウトは今回のSamsungの事例が世界初で、SynopsysはSamsungのプロセッサ実装の要となったのは、「Design Compiler Topographical」と「IC Compiler」の「Physical Datapath」テクノロジであったと強調している。

Samsungは、昨年11月にARM Cortex-A15プロセッサ「Exynos 5250」のサンプル出荷を開始しており、2012年Q2(4-6月)に量産開始予定としていた。

2012.05.08

2012年5月7日、FPGAベースのプロトタイピング・ソリューションを手掛ける米S2Cは、同社プロトタイピング・システム向けのオプション・モジュールのリリースを発表した。

発表によると、「Prototype Ready accessories」と呼ばれるオプション・モジュールは、プロトタイピング環境の構築に利用するドーター・ボードで、下記7種の製品が新たに用意された。

※画像はS2C社Webページ掲載のデータ

2012.05.08

2012年5月7日、Cadenceは、IPコンプライアンス・テスト向けの新製品「TripleCheck IP Validator」を発表した。

発表によると新製品「TripleCheck IP Validator」は、Cadence既存のコンプライアンス・ソリューション「PureSuite」および「Compliance Management System (CMS)」の機能を統合し、更に新機能を追加したもので、同社の検証IPソリューション「Cadence Verification IP (VIP) Catalog」に新たにラインナップされる。

「TripleCheck IP Validator」は各種標準インタフェース・プロトコルを実装するデザインのコンプライアンス・テストを効率化するもので、SystemVerilog、およびe言語のカバレッジ・データベースを提供。Cadenceの「Incisive」に限らず主要なシミュレーターをサポートしている。製品としては現在第一弾としてPCIe Gen 3向けのソリューションを提供中。今年後半には新しく複数のインタフェース・プロトコルが追加される予定だという。

2012.05.02

2012年5月1日、米SIA(Semiconductor Industry Association)は、2012年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年3月の世界半導体売上は前年同時期比約7.9%減、前月比約1.5%増の233億1000万ドルという統計結果となった。これで売上前年割れは2011年6月から10ヶ月連続となったが、2011年10月から続いていた売上減にようやく歯止めがかかり、半年ぶりに前月の売上を上回った。

四半期でみると2012年Q1(1-3月)の売上は699億ドルで前年比7.9%減、2011年Q4に対しては2.2%減となっているが、ここ直近の大手半導体各社の業績予測からすると半導体市場は底を打ったと見られ、次期Q2はより売上が回復すると思われる。

2012.05.01

各組織の発表している2012年4月時点での2012年世界半導体市場成長予測を再更新しました。新たにIDCが予測を発表しました。

直近予測値を更新したGartner、IHS、IDCはいずれも予測を上方修正。各社ともに2012年上半期でシリコンサイクルの底を脱し、2012年下半期は好転すると予測しています。

2012.04.27

2012年4月26日、Synopsysは、FPGAベースのプロトタイピング・システム「HAPS」の新機能「Deep Trace Debug」を発表した。

Synopsysによると「HAPS」の新機能「Deep Trace Debug」は、RTLデバッガ「Identify」と新たに用意された「HAPS Deep Trace Debug SRAMドータボード」が実現する機能で、FPGAのオンチップ・メモリの代わりにドータボード上の大容量SRAMを利用する事で、HAPSのデバッグ能力を高めるというもの。ドータボードに搭載されるSynopsysの「NBT SRAM」は、従来のFPGAオンチップ・メモリの約100倍の容量があり、高速なリードが可能なほか、2種類のモードでリード速度を優先するかリード後の処理速度を優先するか選択可能。これにより検証のパフォーマンスを損なうことなく大量なデータ収集とプロービングが可能になるという。

2012.04.27

2012年4月26日、SystemCからの高位合成ツールを手掛ける米Forte Design Systemsは、Cadenceのパートナー・プログラム「Connectionsプログラム」への参加を発表した。

Cadenceの「Connectionsプログラム」は、Cadenceの提供するツール・フローと同プログラムに参加するツールとのインターオペラビリティの確立を目指すもの。今回Forteは同プログラムに参加し、同社の高位合成ツール「Cynthesizer」とCadenceのシミュレーション環境「Cadence Incisive Enterprise Simulator」との接続を実現したという。

2012.04.27

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2012.04.27

2012年4月25日、Xilinxは2012会計年度第4四半期(2012年1-3月)の売上を報告した。

Xilinxの2012年Q4(12年1-3月)の売上は、前年同時期比5%減、前期比9%増の5億5900万ドル。営業利益は前年比10%減の1億6290万ドルという結果だった。売上前年割れは11年7-9月期に続き3四半期連続となるが、売上、営業利益ともに前四半期(11年10-12月)を上回る結果となり、業績の回復を表した。

地域別売上では景気低迷で落ち込んでいた欧州市場が盛り返し、売上全体に占める割合を増やした。日本市場も前Q3に続き前年を上回る10%のシェアを維持した。分野別の売上構成では主力の通信分野の売上が減った分、FA/その他の分野が全売上の37%を占めた。製品別売上では新製品だけが前年比7%増と好調で、40nm製品ならびに28nm製品が順調に売上を伸ばしているという。

尚、Xilinxの2012会計年度(11年4月-12年3月)の売上合計は前年比5.5%減の22億4073万ドル、営業利益の合計は前年比4%減の7億8607万ドルだった。

Xilinxは次期2013年Q1(12年4-6月)の売上を今期の1%から5%増になると予測している。

2012.04.26

2012年4月25日、Mentor Graphicsは、同社のエミュレーター「Veloce」の2代目製品「Veloce2」のリリースを発表した。

Mentorによると新しい「Veloce2」は、新たに開発された65nmプロセスで製造されるLUTベースの独自チップ「Crystal2」を搭載しており、パフォーマンス、デザイン容量ともに初代Veloceの倍に引き上げられた。「Crystal2」は最大256個搭載可能(正確には16個搭載したボードを16枚搭載可能)で、そのデザイン・キャパシティは最大20億ゲート。ボード1枚につき1名が利用可能で最大構成で16名が同時に利用することが出来る。エミュレーション速度は最高で3MHzと45nmチップを用いる競合製品よりも速く、消費電力についても競合製品の1/4に抑えられているということで、生産性を4倍に向上しながら、競合を下回る所有コストを実現している。

※画像はMentor提供のデータ

またMentorは、今回「Veloce2」のリリースと合わせて新しいソフトウェア機能「Veloce VirtuaLab」を用意。「Veloce VirtuaLab」は、DellまたはHPのLinuxワークステーション上で稼働するソフトウェア・ベースのペリフェラル・モデルで、「Veloce2」を用いたSoC検証環境を迅速に構築するためのオプション製品。Mentorは「Veloce」向けに「iSolve」と呼ぶハードウェアおよびソフトウェアのICEを提供しているが、「Veloce VirtuaLab」はこの「ソフトICE」に相当するもので、USB3.0やEthernetなど数種類の標準規格モデルを用意している。同モデルを利用することでペリフェラルの構成を柔軟に再構成可能なほか、起動したRTOSの状態をセーブ/リストア出来るなど、ハードウェアのICEでは実現できない恩恵を享受可能。また「Veloce VirtuaLab」の各モデルには、パケット・ジェネレーターや解析機能などモデルに応じたツールが付属され、これらを利用することでハード/ソフト、ペリフェラルのインタフェースを高精度かつ効率的に検証することが出来る。

※画像はMentor提供のデータ

尚、この「Veloce VirtuaLab」は、初代「Veloce」でも利用できるほか、「iSolve」のハードウェアICEと組み合わせて利用する事も可能。また、ライセンス数に応じて複数ユーザーで利用することも可能となっている。「Veloce2」を複数ユーザーで使用する際には複数のジョブをパッチ実行で流し実行ログを取り、「Questa Codelink」という別ツールを利用しオフラインでデバッグするという手法が効率的であるという。

※画像はMentor提供のデータ

Mentor Graphicsのエミュレーション事業部、プロダクト・マーケティング・マネージャーのGabriele Pulini氏によると、「Veloce2」は先行顧客向けに半年前にリリースしており、既に初代「Veloce」の総売上を超える販売実績を叩き出しているという話。エミュレーション市場における「Veloce」シェアは2010年時点で36%に達していたという事で、それに「Veloce2」の実績を加えると現時点で相当なシェアを握っていると思われる。ちなみに「Veloce2」の価格はその台数、構成により異なるが、一つの目安としては「1ゲート当たり1円」との事だった。

2012.04.26

各組織の発表している現時点での2012年世界半導体市場成長予測をまとめてみました。

直近予測値を更新したGartnerとIHSはいずれも予測を上方修正。WSTS,IDC,TSMCはその後特にアナウンス無し。

2012.04.26

2012年4月25日、Cadenceは、2012会計年度第1四半期(2012年1-3月)の売上を報告した。

Cadenceの2012年Q1売上は、前年同時期比約18.8%増、前期Q4(11年10-12月)と比較して約2.6%増の3億1600万ドル。営業利益は3100万ドルで前年の600万ドルを大きく上回った。(※GAAP基準による会計結果)

この2012年Q1の売上実績は今年2月時点での売上予測を上回るもので、これでCadenceは9四半期連続で前年比増の四半期売上を叩き出した事になる。

Cadenceは次期2012年Q2売上を今期同等以上の3億1500-2500万ドルと予測。2012年年間売上については予測を12億7000-13億ドルと上方修正している。

2012.04.25

2012年4月24日、ARMは、2012会計年度第1四半期(2012年1-3月)の売上を報告した。

ARMの2012会計年度Q1の売上は、前年比13%増、前期比3.5%減の2億940万ドルで営業利益は前年比22%増の約1億ドルだった。ARMは前期2011年Q4まで7四半期連続で四半期売上記録を更新していたが、その記録はこのQ1で途絶えた。しかしながら依然売上好調を維持しており、売上、営業利益ともに前年比2ケタ増を継続している。

ARMはこのQ1で新アーキテクチャのCortex-A15コアを含む22件のプロセッサ・ライセンスを獲得(前Q4では25件)。その内8件はCortex-Aシリーズ、10件はCortex-Mシリーズのライセンス、2件はGPU Maliのライセンス契約だった。

※画像はARM発表資料より抜粋

2012Q1で出荷されたARM搭載チップの総数は約19億個で、うち約11億個はスマートフォンなどのモバイルデバイス向けに、約8億個はコンシューマーおよびクルマ向けで、コンシューマーおよびクルマ向けの出荷数は前年比15%増となっている。プロセッサの種類別で見ると、出荷数の73%はARM7,9,11のv6アーキテクチャ製品で残りの27%がCortex-A,R,Mのv7アーキテクチャ製品となっている。

売上の内訳を見ると、プロセッサ・ライセンスのQ1売上は前年比20%増の7680万ドルで、プロセッサ・ロイヤリティのQ1売上は前年比7.5%増の1億600万ドルだった。

※画像はARM発表資料より抜粋

2012.04.25

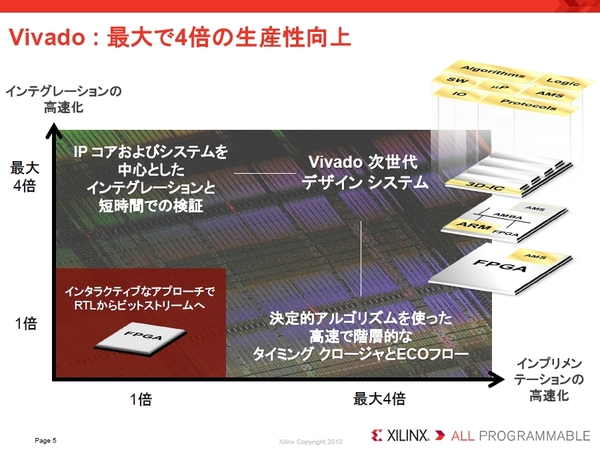

2012年4月25日、Xilinxは、Vertex-7シリーズ以降の次世代デバイス向けの専用設計環境「Vivado」を発表した。

Xilinxによると「Vivado」は、次の10年を見据えて新規開発した設計ツールで、SoC化するFPGAの効率的な設計を実現するもの。論理合成、配置配線、シミュレーターと設計環境を構築する各エンジンが既存の「ISE」で使われているものから刷新され、新たに高位合成のエンジンも搭載された。

これまでの設計環境「ISE」は、プログラマブル・ロジック・デバイスの設計環境として、FPGA上のロジック設計を中心としたものであったのに対し、新たな「Vivado」は、ARMプロセッサをはじめとする様々なIPの搭載やデバイスの三次元化などFPGAの進化に対応するもので、言わばFPGAシステム全体のインテグレーションを実現する環境。

今回の「Vivado」の発表と合わせXilinxは、「ALL PROGRAMMABLE」という企業のキャッチ・コピーを新たに打ち出しており、既に出荷しているVertex-7シリーズのFPGAと新たな設計環境「Vivado」によって、同社のソリューションが更にプログラマブルなソリューションとして進化・強化していくことを強調。Xilinx日本法人社長のSam Rogan氏は、今回の「Vivado」の発表を「Xilinxの方向を定義する重要な発表」とコメントしている。

「Vivado」は、既に100社を超える企業が1年に渡るベータ版プログラムに参加し試用しており、その生産性の高さは実証済み。Xilinxは「Vivado」の実行速度をシステムのインテグレーションにおいてもインプリメンテーションにおいても、ISE現行バージョンおよび他社ツールと比較して最大で4倍高速としており、実際に「Vivado」を試用した国内のパートナーからも以下のような評価結果が報告されている。

・OKI情報システムズ

Vivadoベータ版をXilinx-7 LX690ターゲットにPCI-E gen3のデザインで評価したところ、を実装したところ、ISE14.1よりもインプリメントのランタイムが3.3倍高速、インプリメント実行中のメモリ使用量は1.2倍向上、フロアプランにおいて省スペース配置を実現。

・東京エレクトロンデバイス

評価ボード試験用の回路と画像処理回路をミックスした複雑なデザインでVivadoベータ版を評価したところ、ランタイムはISEよりも2倍高速、ISEでは要求性能を満たすために多数のカット&トライが必要だったが、Vivadoでは一発で配置配線を完了できた。

・ベリフィケーション・テクノロジー

512ビットの高速バスを内蔵するブロードキャスト用チップの実製品設計でVivadoベータ版を評価したところ、ISE13よりもイタレーション回数を大幅に削減。苦労した配置配線がスムーズに実行でき、全体的な設計生産性3-4倍向上できた。

※画像はXilinx提供のデータ

具体的に「Vivado」の大きな特徴と言える機能は大きく2つ。

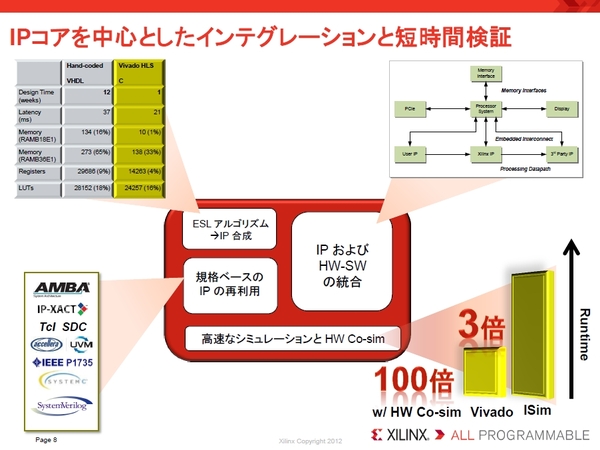

まず、システムのインテグレーションを高速化する機能として、昨年2月に買収したAutoESL社の技術をベースとした高位合成機能が用意され、C言語ベースでのFPGA設計が可能となった。この高位合成エンジンは、C/C++/SystemCからの合成が可能でこれら言語の混在記述にも対応可能。ループのパイプライン化をはじめとする各種合成指示や面積、パフォーマンス、消費電力などの各種パラメーターを設定した自動合成が可能なほか、合成したRTLをIP-XACTフォーマットでパッケージ化する事もできるという。

FPGA向けの高位合成は、これまで多くのEDAベンダがツールを提供してきているが、FPGAベンダの提供する設計環境に高位合成エンジンが搭載されるのは今回の「Vivado」が業界初。競合のAlteraは、並列プログラミング向けの言語OpenCLを用いたFPGA設計の研究を積極的に進めているが、Xilinxは高位合成を用いたC言語によるFPGA設計手法を推し進め、その環境の提供で先行した格好だ。システムレベルの設計環境に関しては、今後両社のソリューションはそれぞれ異なる方向へと発展していくのかもしれない。

※画像はXilinx提供のデータ

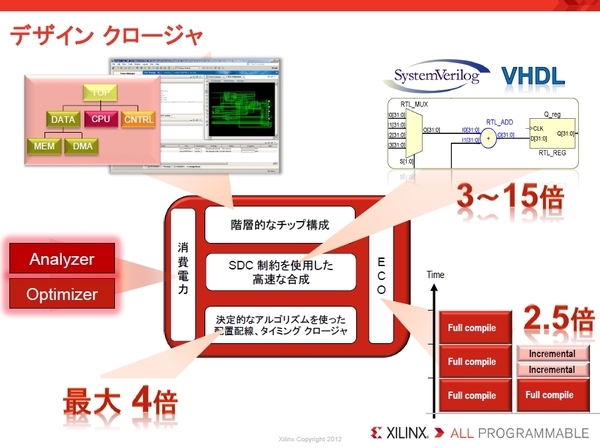

もう一つ「Vivado」の特徴と言えるのが進化したインプリメント機能である。「Vivado」では、「shared scalable data model」と呼ぶ新たなデータモデルを採用しており、各ツールで利用するデータモデルが統一された。このモデルを利用することで階層的なチップのプランニングやパーティショニングが可能となった。また論理合成エンジンも刷新され、SystemVerilogからの合成が3-15倍に高速化されたほか、そのキャパシティは1億ロジック・セルに拡張された。更にタイミング、ワイヤ蝶、配線密度などを同時に考慮する新たな配置配線エンジンによってデザインの収束時間が最大4分の1に短縮可能となり、ECOにおいてもインクリメンタル機能のサポートでその生産性は2.5倍向上された。その他、自動クロック・ゲーティング機能により消費電力も最大30%削減可能となるなど、インプリメント作業全般に渡ってその生産性が大きく向上された。

※画像はXilinx提供のデータ

その他、今回「Vivado」で実現された新機能としては、IP-XACTの技術を用いたシステムレベルのIPの接続機能「IP Integrator」やC言語ベースのモデルを利用した、ブロック単位あるいはシステム全体のビヘイビア・シミュレーションなどがある。

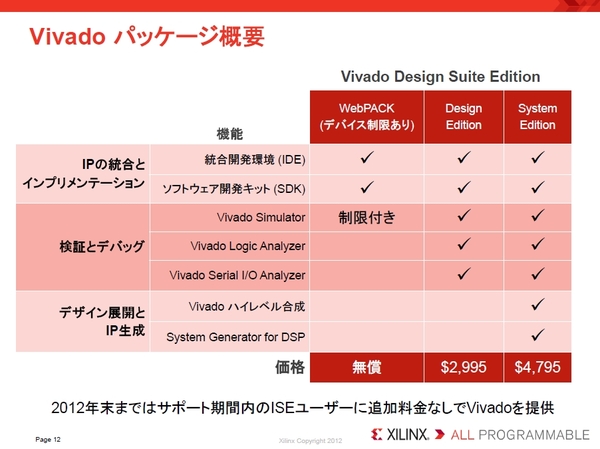

尚、「Vivado」は既に早期顧客向けに提供されており、一般顧客向けには2012年Q3(7-9月)に有償版を提供開始予定。無償版の提供は2012年Q4からを予定している。「Vivado」のリリースにより既存の「ISE」のエンハンスは終了するが、既存ユーザー向けのサポートは引き続き継続される。高位合成機能を含む「Vivado」の最上位パッケージの米国でのライセンス価格は年間$4,795?となっている。

※画像はXilinx提供のデータ

2012.04.23

2012年4月19日、Alteraは2012会計年度第1四半期(12年1-3月)の売上を報告した。

発表によるとAlteraの2012年Q1(12年1-3月)売上は、前年比約28%減、前期Q4比約16%減の3億8380万ドルで2四半期連続で前年比2ケタ減となり、全四半期以上の売上の低迷を表した。純利益は前年比約48%減の1億1580万ドルで、前期に続き大きく減らした。四半期売上の前年割れはこれで3四半期連続となる。

AlteraのCEO兼会長のコメントによると、2012年Q1は主力の通信関連市場で売上が落ち込んだほか、受注分の出荷に問題が生じ総じて売上減に繋がったという事。しかし、Q2には28nmFPGAの好調により売上回復を見込んでいるという。

Q1売上を地域別で見ると北米市場が前年比、前期比ともに売上を減らしその分アジア市場のシェアが伸びた。製品カテゴリ別では新製品としてカテゴライズされるStratix V、Stratix IV、Arria II、Cyclone IV、MAX V、HardCopy IVといった製品群の売上がかろうじて前年比増となったが、その他分野は軒並み前年比減。前期に対しては総崩れの状態だった。

2012.04.18

2012年4月17日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、第三世代のカスタムIC設計環境「Laker3」と新製品「Laker Analog Prototyping」のリリースを発表した。

今回発表された「Laker3」は、OpenAccessデータベースをサポートした第二世代の「Laker」の後継製品で(第一世代は初代Laker)、OpenAccessベースの統合環境としてツールのインフラ自体が強化され、パフォマーンスの向上や先端プロセスへの対応、新たなアナログ設計技術の搭載など、大掛かりなエンハンスが一気に実施された。SpringSoftは今年3月に次世代版のデバッグ環境として「Verdi3」を発表しているが、同様にネーミングされた今回の「Laker3」は、次世代版のカスタムIC設計環境として大きな進化を遂げている。

具体的に進化した点は大きく3つ。まずツールのインフラの刷新により統合環境としての完成度が高められ、パフォーマンスおよびユーザビリティ、そしてOpenAccessベース・ツールとのインターオペラビリティの向上が実現された。パフォーマンス面では描画性能がSi2のリファレンス・ツールと比較して2-10倍にまで高速化されたほか、書き込み速度も最大6倍の高速化が実現された。「Laker」は元々「サクサク動く」その速さに定評があるツールと言えるが、今回のエンハンスでその特徴が更に強化された格好となる。また、GUIも「Verdi3」と同じくQTベースに刷新され、ウインドウ操作などよりカスタム性と操作性が高められた。

※画像はSpringSoft提供のデータ。Laker3のGUI画面。

更に各Lakerファミリ製品に内蔵されるDRCエンジンも新たなものに取って代わられ、ダブル・パターニングなど20nmデザイン・ルールにも対応可能となった。SpringSoftはサインオフ用のDRCはMentorの「Calibre」との連携という形を取りつつ、先端プロセスへの対応に向けて自前のDRCエンジンの機能強化も着々と進めている形だ。また、今回の「Laker3」からOpenAccessベースのパラメトリック・セル「PyCell」も取り扱えるようになった。

そして最もインパクトのある進化と言えるのが、新ツール「Laker Analog Prototyping」の登場で、新たに「Laker3」統合環境上でアナログ設計の「半自動処理」が可能となった。「Laker Analog Prototyping」は、「Laker」の最上位製品パッケージ「L4」に含まれるツールで、設計した回路(ネットリスト)からレイアウト制約を抽出し、それを元に複数の配置パターンを自動生成してくれる。設計者は自動生成されたレイアウト候補から最適なものを選び、それをチューニングする事で所望のレイアウトを実現する形となる。

「Laker Analog Prototyping」の提供する「アナログ・プロトタイピング」というアプローチはこれまで無かったもので、制約の自動生成と高速な配置パターン生成を実現できるからこそ成せる技。アナログ配置配線を完全に自動化するものではないが、レイアウトとレイアウト制約のイタレーションを効率化するソリューションという意味で「アナログ・プロトタイピング」と命名されている。同機能は他のLakerファミリ製品と同じバイナリを共有して実行できるため、「Laker」統合環境上で最も力を発揮するが、基本的にOAベースのツール上であれば動作可能なため、同機能だけを利用して他社のツール上で「アナログ・プロトタイピング」を実施するというユース・ケースも有り得る。実際に今回の発表にコメントを寄せているSTARCは、同社のOpenAccessベースのSTARCAD-AMS環境上で「Laker Analog Prototyping」を評価しており、「STARC-AMSデザインフローに統合できると考えている。」と語っている。

※画像はSpringSoft提供のデータ。アナログ・プロトタイピングのフロー。

尚、SpringSoftのLakerプロダクト・マーケティング、シニア・テクニカル・マネージャーのLucas Chen氏によると、ファブレス上位5社のうち2社がヘビー・ユーザーで「Laker」を社内標準ツールとして利用しており、半導体上位10社のうち5社がユーザーであるという話で、一昔前の印象では「Laker」は日本市場ではマイナーな存在と思えていたが、ワールドワイドで実績を伸ばしているようだ。市場としては北米および本拠地台湾が強いのは言うまでもないが、アジアの中では日本のシェアが高く、次いで韓国、中国、インドという順番だという事で、今回発表された「Laker Analog Prototyping」を含む「Laker3」は既に日本国内の顧客が導入済みとの話。既存製品の実績としては、大手IDMでも導入されているほか、デザイン・ハウスでの利用が非常に多いと聞いた。

※画像はSpringSoft社のWeb掲載画像。Lakerファミリ製品。

2012.04.17

2012年4月16日、業界標準ツール「SpyGlass」をはじめとしたRTL解析/最適化ソリューションを手掛ける米Atrenta社は、同社のIP認証キットのキャンペーンを発表した。

AtrentaのIP認証キット「Atrenta IP Kit」は、設計で利用するソフトIPの評価・認証を行うためのキットで、RTL解析ツール「SpyGlass」と「DashBoard」ならびに「DataSheet」と呼ばれる文書化ツールをベースに構築されている。同キットを用いることで、対象とするソフトIPの各種チェックを容易に行え、そのレポートをIPの品質の判断基準として自動生成する事が可能。TSMCは自社プロセスで利用するサードパーティーIPの認証に同キットを利用している。

【Atrenta IP Kitのチェック項目例】

?シミュレーションと合成のミスマッチ

?ERCチェック

?CDC検証

?テスタビリティ解析

?パワー評価

?タイミング制約検証

今回Atrentaが発表したキャンペーン「Atrenta IP Kit Spring Cleaning Promotion」は米国内の半導体設計部門を対象にしたもので、期間は4月16日から5月31日まで。同期間中に2週間無料で「Atrenta IP Kit」を利用できる。

※Atrenta IP Kit Spring Cleaning Promotionに関する詳細は

こちら

2012.04.17

2012年4月12日、富士通セミコンダクター株式会社は、オンラインで利用できるシミュレーション・ツール「Easy DesignSim」を用いた設計サービスの開始を発表した。

富士通セミコンダクターの発表によると、同社の「Easy DesignSim」は、エンジニアがWEB上で利用できるシミュレーターで、オンライン上で手軽に電源回路を設計することが可能。入出力電圧、出力電流、スイッチング周波数など、いくつかの設計条件を入力することで電源部の回路図を作成し、動作確認ができる。

また、「Easy DesignSim」を用いれば、Web上で電子部品商社のデータベースから部品を選定し回路の動作確認を行うことも可能。 設計条件と回路図、波形、部品リスト(BOM)をPDFファイルに出力できる。

この「Easy DesignSim」を用いたソリューションは、富士通セミコンダクターが米Transim Technology Corporation社との協業で開発したもので、下記URLから利用手続きが可能。

2012.04.17

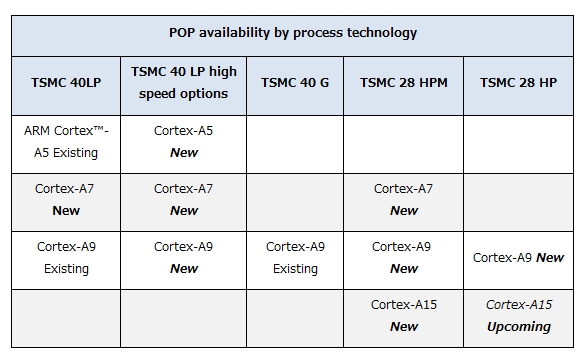

2012年4月16日、ARMは、TSMC向けのPOP(Processor Optimization Pack)の新ラインナップを発表した。

ARMの提供するPOPは、特定プロセスをターゲットにARMコアの最適かつ短期間での実装を実現するもので、フィジカルIP、リファレンス・フロー、各種ベンチマーク・データなどがパッケージ化されたもの。

今回新たに発表されたTSMC向けのPOPは全9種類でその内容は下記表の通り。

既にTSMC 40nm LP向けのCortex-A5,A9のPOPは存在していたが、「TSMC 40nm LP high speed options」および「TSMC 28 HP/HPM」向けのPOPは今回が初のリリース。Cortex-A7,A15が新たにPOPのラインナップに加わった。これらCortex-A7,A15のPOPは、ARMの提唱する低消費電力化手法「big.LITTLE」を実現するための保証されたソリューションとなる。

※発表された新POPの一覧表。ARM社Webサイトに掲載。

2012.04.12

2012年4月10日、Alteraは、同社のFPGA向けOpenCLプログラムの事例を発表した。

AlteraのFPGA向けOpenCLプログラムは、並列プログラミング向けのOpenCLを用いたFPGA設計の研究開発プログラムで、昨年11月に業界初の試みとして発表されたもの。VerilogやVHDLなどHDLの代わりにOpenCLを用いることで、短い開発期間でCPUとFPGAで構成される高性能なヘテロジニアス・システムを実現することを目指している。

今回発表されたのは同プログラムに参加しているgoHDR社の事例で、同社は既存のテレビでHDRビデオ・コンテンツを最低でも25フレーム/秒でリアルタイム表示すべく、自社のビデオ・コーディック・アルゴリズムをAlteraのFPGAに実装。実装にあたってはHDLを用いず、アルゴリズム(Cコード)をOpenCL規格に移植しOpenCLベースで設計する事で、通常のHDLベース設計で3-6ヶ月は要するFPGAへのアルゴリズム実装を1週間で完了した。実装に関する詳細には触れられていないが、Alteraの提供するOpenCL Cコンパイラを用いて並列化とFPGAへのマッピングが行われたと推測される。

goHDR社の担当者は、VHDL設計には慣れていなかったが、AlteraのOpenCLソリューションにより、プロジェクトの性能要件を限られた開発期間で満たすことができたとコメントしている。

2012.04.11

2012年4月10日、業界最速と称する高速RTLフィジカル合成ツールを手掛ける、米Oasys Design Systemsは、資金調達の第二ラウンドを完了したことを発表した。

Oasysは今回の資金調達額について明らかにしていないが、IntelおよびXilinxが出資したとの事。両社のうち少なくともXilinxはOasysの「Realtime Designer」のユーザーで、実設計にも利用している。

「Realtime Designer」は、1億ゲート規模の大規模ハイエンド設計をターゲットとしたRTLからのフィジカル合成ツールで、市場デビューは2009年。論理合成とレイアウト間のイタレーションを行わないRTLレベルからの配置手法でデザインの高速なインプリメントを実現しており、既に45nm、28nmデザインのテープアウト実績によってその速さは証明済みという。

Oasysは今回調達した資金をサポート体制の強化と研究開発充てる計画。同社の顧客としては、Xilinxの他に、TI、Qualcomm、Juniper Networks、NetLogic、STMicroelectronicsなどの大手の名前が公表されている。

2012.04.10

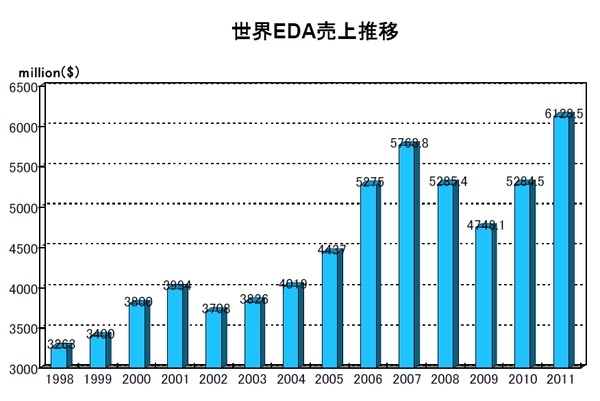

世界EDA売上推移を更新しました。

地域別の売上推移も更新しました。

2012.04.10

2012年4月9日、米EDA Consortiumは、2011年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

EDACの発表によると、2011年Q4(10月-12月)の世界のEDA売上総額は、前年比12.7%増、前Q3比10%増の17億10万ドルで全Q3で更新した四半期売上記録をまたしても更新した。

2011年の世界EDA売上合計は前年比約16%増の61億2850万ドルで、2007年の最高記録57億6880万ドルを4年ぶりに更新した。

2011年Q4の売上を分野別に見ると、PCB/MCM分野以外は全て前年比増を記録。中でもIC Physical Design & Verification分野が前年比30%増と大きく売上を伸ばした。

2011年Q4の売上を地域別に見ると、日本市場以外は全ての地域で前年比2ケタ増を記録。中でもアジアその他地域は前年比34%増と大きな伸びを示した。日本市場は前年比10.5%減で前Q3に続き欧州市場を下回ってしまった。

2011年Q4時点でのEDA業界の従業員数は27623人で、前期Q3比1.7%増となっている。

2011年Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億4480万ドル 11.9%Up

■IC Physical Design & Verification分野 3億9240万ドル 30.0%Up

■IP分野 4億3220万ドル 13.4%Up

■サービス分野 9090万ドル 9.8%Up

■PCB/MCM分野 1億3970万ドル 15.6%Down

2011年Q4地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億2630万ドル 12.8%Up

■ヨーロッパ 3億610万ドル 11.8%Up

■日本 2億4810万ドル 10.5%Down

■アジアその他地域 4億1960万ドル 34.0%Up

2012.04.05

2012年4月3日、オープンコアプロトコル(OCP)の普及団体OCP-IPは、「SystemC TLM Kit」のエンハンスを発表した。

「SystemC TLM Kit」は、OCP準拠のTLMベースの通信モデル、インタフェースモデルをモデリングするためのキットで、OCP-IPが会員向けに無料提供している。

発表によると「SystemC TLM Kit」の最新バージョンversion 2_2x2_2では、Accellera Systems InitiativeのOSCI SystemC TLM2.0規格に沿った以下のような機能強化が更に進められた。

・payload-event-queuesのデータ堅牢性向上

・thread-busy signaling APIの修正

・interrupts, sideband error signaling, sideband user flagsのサポート

・TL3とTL1間、TL1とTL0(RTL)間のTLM2.0ネイティブ・アダプタのサポート

「SystemC TLM Kit」は、OSCI SystemC TLM2.0の全ての抽象度をサポートするものだが、OCP-IPの示すTL3,TL1,TL0という表現は、OCP-IPが独自に定義するモデルの抽象度で、OSCI TLM2.0の定義とは異なるもの。その対応関係については以下の表が分り易い。

尚、「SystemC TLM Kit」は、OCP-IPのSystem Level Design Working GroupがオープンソースのSystemCモデルを手掛けるGreensocsと共に開発したもので、OCP仕様としてはバージョン2.1および2.2をサポート。(OCP3.0仕様は未サポート)OSCI TLMのバージョンは2.0.1をサポートしている。同キットは既にOCP-IPの会員向けに無償提供されており、非OCP-IP会員でもモニターの無いバージョンを無償利用できる。

2012.04.04

2012年4月2日、Synopsysは、FPGA論理合成ツール「Synplify」ファミリ製品のバージョンアップを発表した。

発表によると「Synplify Pro」および「Synplify Premier」の最新バージョン2012.03は、合成アルゴリズムが改善されツールの実行時間を最大で30%削減することが可能に。また上位製品の「Synplify Premier」には、新機能「Continue On Error機能」が搭載された。

「Continue On Error機能」は今回のバージョンアップの目玉と言える新機能で、HDLコードのコンパイル・エラーを一度にまとめて修正するもの。従来手法ではHDLコードに不備があると都度エラーの修正と再コンパイルが必要であったが、「Continue On Error機能」を用いるとエラーが発生しても最終段階までコンパイルを続行し、最後にエラーレポートを出力。設計者はこのエラー・レポートを元にエラーの修正を一度に出来る。Synopsysは、内容が良くわからないHDLコードを扱うプロトタイプ開発者のために同機能を用意したようだ。

また、「Synplify Premier」の新バージョンには故障対策の機能として、適用箇所を選択可能なTMR(Triple Modular Redandancy)機能やメモリーエラー修正コード推定/挿入するECC(Error Correcting Code)機能、Hamming-3エンコーディングを搭載しているという。

「Synplify Pro」および「Synplify Premier」の最新バージョン2012.03は既に出荷中。

2012.04.04

2012年4月3日、米SIA(Semiconductor Industry Association)は、2012年2月の世界半導体売上高(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年2月の世界半導体売上高は前年同時期比約7.3%減、前月比約1.3%減の228億8000万ドルという統計結果となった。これで売上前年割れは2011年6月から9ヶ月連続となったが、マイナス幅は徐々に狭まり市場回復の兆しを示し始めている。それを証拠に北米市場の売上が前月よりも1.1%増加。市場全体の前月比は1月の2.7%減から1.3%減と戻した。

直近報じられている各社の業績予測を見ると、3月売上は前月比増となる見通しでQ2(4-6)から本格的な半導体市場の景気回復が見込まれている。

2012.03.30

2012年3月28日、Synopsysは同社の寄生容量抽出ツール「StarRC」の実績について発表した。

発表によるとSynopsysの寄生容量抽出ツール「StarRC」は、40社以上の半導体開発企業で導入され、電気特性を高精度にモデル化できるその寄生容量抽出ソリューションは主要半導体ファウンドリおよび主要半導体ベンダ各社で認定されており、28nmプロセスの設計で既に150を超えるテープアウト実績があるという。

別リリースで発表された情報によると、「StarRC」はTSMCのプロセスで製造されるAlteraの28nm FPGA「Stratix V」の寄生容量サインオフ・ソリューションとして利用されているようだ。

Synopsysによると下記企業が「StarRC」を28nmプロセス設計の寄生容量サインオフ検証ソリューションとして認定しているとの事。

Altera、Bull、富士通セミコンダクター、HiSilicon Technologies、Imagination Technologies、LSI、Moortec Semiconductor、NVIDIA、Qualcomm、ルネサスエレクトロニクス、Samsung Electronics、STMicroelectronics、東芝、他。

2012.03.29

世界最大規模で開催されているSystemCの技術セミナー「SystemC Japan」が今年も以下の通り開催されます。

会期:2012年7月6日(金)

セミナー 9:30?17:40, パーティー18:00?19:30

会場:新横浜国際ホテル 南館2F

〒 222-0033 横浜市港北区新横浜 3-18-1

http://sinyokohama.khgrp.co.jp/info/access.html

参加:無料(定員350名先着順 )

主催:Accellera System Initiative

メインスポンサー:

日本ケイデンス・デザイン・システムズ社

フォルテ・デザイン・システムズ株式会社

インテル株式会社

メンター・グラフィックス・ジャパン株式会社

日本シノプシス合同会社

※セミナー内容に関する詳細は6月上旬に公開予定

※セミナー参加登録の受付は6月上旬に開始予定

今年はSystemCユーザーによる事例講演の公募が予定されており、明日3/30より公募の受付が開始されます。

2012.03.29

2012年3月27日、Synopsysは、ハードとソフトで構成するオーディオIPサブシステム「DesignWare SoundWave Audio Subsystem」を発表した。

Synopsysの「DesignWare SoundWave Audio Subsystem」は、同社のハードIPコア「ARC 32bitオーディオ・プロセッサ」と各種オーディオ・コーデック・ソフトウェアをベースとしたSoC開発のためのオーディオIPサブシステムで、その開発環境としてバーチャル・プロトタイプ環境とFPGAベースのハードウェア・プロトタイプ環境も用意されている。

※画像はSynopsys提供のデータ

ハードウェア・コンポーネント群としては、DesignWare ARC 32bitオーディオ・プロセッサ、各種標準デジタル・インターフェイス、各種アナログ・コーデックが、ソフトウェア・コンポーネントとしては、Dolby、DTS、SRS Labsなどの各種オーディオ・フォーマットに対応したオーディオ・コーデック・ソフトウェアが用意されており、これら事前検証済のIPコンポーネントと提供されるバーチャル・プロトタイプ環境、FPGAプロトタイプ環境を利用することで、従来数週間要していたオーディオ・サブシステムの構築作業をわずか数時間の単位で完了可能となるという。

「DesignWare SoundWave Audio Subsystem」は既に先行顧客に提供されており、一般顧客へは4月か提供される予定。

※画像はSynopsys提供のデータ

2012.03.29

2012年3月27日、 アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、Berkeley Design Automationは、同社の回路シミュレーター「Analog FastSPICE」をTFT-LCDパネルドライバICを手掛ける台湾のファブレスRaydium Semiconductorが採用したことを発表した。

発表によるとRaydium Semiconductorは、TFT-LCD パネルドライバのブロックレベルキャラクタライゼーションおよび回路全体の検証にBerkeleyの「Analog FastSPICE Platform」を採用。Raydiumの副社長、Chin-Chieh Chao 博士のコメントによると、RaydiumがTFT-LCDアプリケーションをターゲットとした複雑なアナログ回路で「Analog FastSPICE」のベンチマークを実施したところ、既存のデジタルFastSPICEシミュレータよりも5倍高速にSPICE精度を達成したとの事。また同社ではSPICE精度と合わせて価格性能比も重要な評価ポイントだったという。

数年間に渡り好調な実績を維持しているBerkeley Design Automationはコンスタントに導入顧客を増やしており、今年に入って新規顧客導入事例の発表は既に4件目。

2012.03.29

2012年3月27日、米業界紙EE TimesとEDNは「2012 UBM Electronics ACE Awards」の受賞者を発表した。

「UBM Electronics ACE Awards」は「EE Times ACE Awards」と「EDN Innovation Awards」が統合された新たな業界アワードで今回が初の表彰となる。各部門の受賞者は、EE TimesとEDNの記者によって選ばれ、プロダクト部門については読者による投票で受賞者が決定された。「2012 UBM Electronics ACE Awards」の主要部門の受賞者は以下の通り。

・STARTUP OF THE YEAR - mCube

・COMPANY OF THE YEAR - Qualcomm, Inc.

・EXECUTIVE OF THE YEAR - Rich Beyer, Freescale Semiconductor

・DESIGN TEAM OF THE YEAR - Tilera Corporation

・INNOVATOR OF THE YEAR - Michael McCorquodale, Integrated Device Technology

・ENERGY TECHNOLOGY AWARD - Maxim Integrated Products

・ULTIMATE PRODUCTS

-SoCs - Zynq-7000 EPP (Extensible Processing Platform), Xilinx

-Analog ICs - 3LG family of CrystalFree CMOS oscillators, Integrated Device Technology

-Digital ICs (MCUs, FPGAs, microprocessors) - LPC11U00 microcontrollers, NXP Semiconductors

-Power - LTC6803 multicell battery stack monitor, Linear Technology

-Human-Machine Interface Technology - Xtrinsic capacitive and resistive touch sensing platform, Freescale Semiconductor

-Software - Virtual System Platform, Cadence Design Systems

-Passive Components, Sensors, Indicators and Interconnects - TMP006 temperature sensor, Texas Instruments

-Development Kits, Reference Designs & SBCs - Home Health Hub reference platform, Freescale Semiconductor

-Test & Measurement Systems & Boards - MDO4000 mixed-domain oscilloscope, Tektronix

2012.03.29

2012年3月28日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、STMicroelectronicsによる「VIAプラットフォーム」の採用事例を発表した。

発表によるとSTMicroelectronicsは、社内の論理設計で活用しているデバッグ環境「Verdi」の運用をより効率的なものにするために、「Verdi Interoperability App (VIA)プラットフォーム」を導入しロジック違反の特定を自動化するためのTCLスクリプトを開発。これにより、違反レポートをVerdiにロードするだけで、Verdi上で表示する階層を選択し、波形ビューワーに対応する信号を表示し、そのサイクルの正しい時間までをトレースするという作業フローを実現した。

SpringSoftの「VIAプラットフォーム」は、デバッグ環境「Verdi」のユーザー向けに提供される「Verdi用カスタム・アプリ」の開発インフラで、「Verdi」のデータベースを利用した独自のアプリケーション開発やGUIのカスタマイズなどを実現できる。SpringSoftは、この「VIAプラットフォーム」の運用を促進するためのWebポータル

「VIA Exchange」を開設しており、同サイトにアクセスすると無料のカスタム・アプリやカスタム・アプリ開発に関する情報を入手することができる。

「VIAプラットフォーム」は、多数の「Verdi」ユーザーを抱えるSpringSoftが細かいユーザーのカスタム要求に応えるために考案したソリューションで、サード・パーティー・ツールとの連携などにも活用されている。

2012.03.28

2012年3月26日、アナログ設計の技術コンサルティングを手掛ける株式会社モーデックは、アナログ・シミュレーション用のSPICE「MDW-SPICE」の日本語Windows版を無償配布するサービスを発表した。

発表によると無償配布されるSPICEシミュレーター「MDW-SPICE」は、spice3f5をベースにモーデック社が独自開発したもので、同社のモデリング・ツール「MoDeCH-Extractor」や「MOSTAT」のSPICEエンジンとして搭載されており、Windows環境で動作し日本語をサポートしている。

また、「MDW-SPICE」には CMC認定のコンパクトモデル(BSIM3、 BSIM4、 BSIMSOI4、 HiSIM-HV、 HiCUMなど)の最新版が搭載されているほか、BSIM3、BSIM4などのBINNING機能にも対応。測定データとシミュレーションの比較検証機能が備えられており、無償版といっても特にシミュレーション素子数の制限など設けられてはいない。

尚、今回モーデックが無償配布する「MDW-SPICE」は、同社のSPICEシミュレーター製品「MoDeCH-SPICE」のバージョンのひとつで、「MDW-SPICE」以外に製品版としてWindows、SUN、Linuxなどでエンジンとして動作する高速、コンパクトなバージョンが用意されている。

2012.03.28

2012年3月27日、FPGAベースのプロトタイピング・ソリューションを手掛ける米S2Cは、同社プロトタイピング・システムのソフトウェア環境「TAI Player Pro」のバージョンアップを発表した。

発表によると最新の「TAI Player Pro」バージョン4.1では、新たに複数FPGAのデバッグが可能となり、大規模デザインを複数FPGAに分割して実装する際に、最高4個のFPGAを同時にデバッグできるようになった。また、GUI上でI/Oピン・アサインメントが可能となったほか、電圧および電流のモニタリング、クロック周波数のリアルタイム計測といった機能が新たにサポートされた。

2012.03.28

2012年3月27日、Cadenceは、ストレージ向けの新しいプロトコル規格「12Gbps SAS」および「NVM Express」の検証IPが同社のVerification IP (VIP)カタログに追加されたことを発表した。

「12Gbps SAS」は、現在の6Gbps SASの2倍のデータ転送レートを実現する次世代のシリアル・プロトコルで、ストレージのパフォーマンスを引き上げるもの。3Gbps/6Gbps SASとの下位互換性があり、2013年から「12Gbps SAS」対応のサーバーやストレージが市場に登場する予定となっている。

もう一つの「NVM Express」は、SSD(Solid State Drive)をPCI Expressインターフェイスに直接接続するための次世代のストレージ・インターフェイス・プロトコルで、「12Gbps SAS」と同様にストレージのパフォーマンス向上を実現する。

今回Cadenceは、両インタフェース・プロトコル規格の検証IPを開発し、同社のIPラインナップに加えた。「NVM Express」の検証IPは先ごろ競合のSynopsysもリリースを発表したばかりだが、「12Gbps SAS」の検証IPは恐らく業界初。Cadenceの提供するインターフェース・プロトコルIPは40種類以上にのぼる。

2012.03.27

2012年3月26日、Synopsysは、3次元IC(3D-IC)の設計を可能にする同社の包括的なソリューション戦略を発表した。

発表によるとSynopsysは、TSV(シリコン貫通電極)技術を用いて実現する3次元IC(3D-IC)の設計を実現すべく、自社既存のツールをベースとした包括的なソリューションを構築。TSVのモデリングを実現する強力なシェアを誇るTCADを起点に、インプリメント設計、テスト容易化設計、物理検証、寄生容量抽出ほか各種解析など計9種類のツールを3D-IC設計に対応させた。

※画像はSynopsys提供のデータ

※画像の表はEDA Express作成のデータ

これらツール群による3D-ICソリューションは、現在先行顧客にベータ・バーションを提供中で2012年Q2(4-6月)には一般提供が開始される予定。Synopsysは3D-ICソリューションの提供にあたり主要な半導体企業と協業を進めているほか、ベルギーIMECや台湾ITRSなど研究組織との共同研究にも取り組んでいるという。

※画像はSynopsys提供のデータ

2012.03.26

2012年3月22日、Synopsysは、ソフトウェア開発向けの新たなESLソリューション「Virtualizer Development Kit(VDK)」を発表した。

VDKはその名の通りバーチャル・プロトタイピング・ツール「Virtualizer」をベースとしたソフトウェア開発キットで、今回その第一弾としてARM Cortexプロセッサ向けVDKファミリーが発表された。

Synopsysによると、ARM Cortexプロセッサ向けのVDKファミリーには以下のものが含まれており、ARM最新の「Cortex-A15 MPCoreプロセッサ」と「Cortex-A7 MPCoreプロセッサ」で構成する高性能化と低消費電力化のための技術「big.LITTLE処理」に対応するソフトウェアの開発を加速させる事が可能となる。

・プレ・コンフィギュレーションが施されたLinuxおよびAndroid OS

Linux(Vanilla 2.6.38)/Android(Gingerbread 2.3.4)

・「big.LITTLE処理」で用いられるマルチコア・タスク・マイグレーション・ソフトウェア・レイヤのためのプレ・コンフィギュレーション環境

・インターフェイスおよびペリフェラル・コンポーネント

USB 3.0、Ethernet、UART、LCD、キーボード、バッテリー、メモリーなど

現在のところ「big.LITTLE処理」を実現するARMの低消費電力コア「Cortex-A7」は、2013年に市場に出てくる見通しとなっているが、今回発表されたSynopsysのARM Cortexプロセッサ向けのVDKファミリーを利用すれば、「Virtualizer」の謳い文句通り実機が出てくる前から「big.LITTLE処理」を用いたシステムの開発が可能となる。Cortexプロセッサ向けVDKファミリーは2012年Q2(4-6月)に一般提供が開始する予定。

2012.03.26

2012年3月22日、Synopsysは、ストレージ・インターフェイス・プロトコルNVMe(Non-Volatile Memory Express)の検証用IPのリリースを発表した。

NVMeは、2011年3月に公開された次世代のストレージ・インターフェイス・プロトコルで、SSD(Solid State Drive)をPCI Expressインターフェイスに直接接続するための規格。規格の標準化団体には業界80社以上が加盟しており、「NVMHCI Work Group」が規格の策定を進めている。

今回SynopsysがリリースしたNVMeの検証用IPは、同インタフェース・プロトコル規格をサポートする業界初の検証IPで、

Synopsysが今年1月に買収を完了したExpertIO社の技術をベースに開発。既存の「ExpertIO PCI Express VIP」と統合するための新しいアッパーレベルのプロトコル・レイヤであるという。

2012.03.23

2012年3月21日、Cadenceは、同社のエミュレーション・システム「Cadence Palladium XP Verification Computing Platform」をLSIデザインサービスを手掛ける三栄ハイテックスが導入したことを発表した。

発表によると三栄ハイテックスは、得意とする画像処理向けLSI設計の受託開発サービスをESL分野に拡張し、システムレベル設計・検証に注力することに伴い、Cadenceの「Palladium XP」を導入。同製品をサービスの中核技術として活用していくという。

Cadenceのエミュレーターを活用した設計サービスというと、富士通セミコンダクターの「Cedar」が有名で同社もESLにフォーカスした「Cedar-ESL」というサービスを提供している。但しこちらはエミュレーターよりもバーチャル・プラットフォームを中心としたサービスとなっている。今回の三栄ハイテックスのESLサービスの詳細は不明だが、「Palladium XP」はCadenceのバーチャル・プラットフォーム「VSP」とも連携可能なため、バーチャル・プラットフォームを活用したサービスも提供されるのかもしれない。

ここ数年で、デザインサービスにおいてもESL技術の採用は徐々に拡大する傾向にあり、例えば日本システムウェアは、ARMベースSoC設計環境をクラウド形態で提供するサービス「EDA Cloud Solution」を開始。東芝情報システムでは、バーチャル・プラットフォームや高位合成ツールを活用したSystemCベースの設計サービスを提供している。

2012.03.15

2012年3月14日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の高機能論理シミュレーター「Riviera-PRO」のバージョンアップを発表した。

発表によると最新の「Riviera-PRO 2012.02」では、検証メソドロジUVM(Universal Verification Methodology)のクラスライブラリのサポートが拡充され、ほぼそのままの形でUVMのソースを扱えるようになったほか、設計言語SystemVerilog、VHDLのサポートも強化された。同シミュレーターでは、UVMのほかに同社がSynthWorksと開発したVHDLベースの検証メソドロジOS-VVM(Open Source VHDL Verifivcation Methodology)もサポートされている。

新機能としては、テストベンチから生成するクラス・オブジェクトをトレースし、それらを波形ビューワに表示しダイナミック・オブジェクトの時系列の解析が可能となった。また合わせて、内蔵するHDLエディタや波形ビューワもエンハンスされ、例えばクロスプロービング機能を用いてUVMメッセージの発生箇所の特定などが可能となった。更に、マルチスレッド・コンパイル機能が追加され、SystemVerilogおよびVerilog、VHDLのコンパイルをより高速化出来るようになった。

※画像はAldec提供のデータ

これら新機能追加および言語サポート強化を実現した「Riviera-PRO 2012.02」は、ドレスデンで開催中のDATE2012において披露されている。

2012.03.15

2012年3月13日、カスタムIC設計環境ならびにハードウェア検証・デバッグソリューションを手掛けるSpringSoftは、同社の日本法人副社長に川原常盛氏が就任した事を発表した。

発表によると川原氏はスプリングソフト株式会社の副社長兼営業本部長として同社の営業強化に注力する予定との事。当面は、検証環境の品質を評価する「Certitude Functional Qualification」やFPGAプロトタイプのデバッグツール「ProtoLink Probe Visualizer」といった同社の新製品を中心に営業活動を展開すると本人がコメントしている。

川原氏は元京セラのエンジニアでハード設計に限らずソフト開発に関する経験と知識を持つ人物。京セラ退社後はイノテックを経てESLベンダCoWareに移り、同社日本法人の創成期から約12年間に渡りESLの世界で活躍した。川原氏は日本のESLの立ち上げに大きく貢献した人物として知る人ぞ知る、いや、知らない人は少ないと思われるほど有名。技術に明るい持ち前のマーケティング手腕でこれからも新天地での活躍に期待したい。

2012.03.15

2012年3月14日、2D/3DグラフィックスGPU IPを手掛ける米Vivanteは、同社IPソリューションでCadenceのDDRコントローラIPを採用した事を発表した。

発表によるとVivanteは、同社のマルチコア3DグラフィックスGPU IPソリューションの開発でCadenceのDDRコントローラIPを利用。Cadenceの協力を得てGPUと外部DDRメモリ間のデータ転送効率を最大化するメモリ・サブ・システムを構築した。Cadenceのメモリ・コントローラIPは、同社が得意とするIP製品のうちの一つで、旧Denali社の時代から多くのシリコン実績を誇る。VivanteのGPU IPソリューションはスマートフォン、タブレット、HDTVなどで利用されているという。

2012.03.15

2012年3月13日、TSMC子会社の設計会社台湾Global UnichipとSynopsysは、両社の協業による実績を発表した。

発表によるとGlobal Unichipは、Synopsysの設計IPの「DesignWare IP」を利用して過去4年間に30件の顧客デザインをテープアウト。製造されたチップは130nm-40nmプロセスを利用したもので、最終製品としてデジカメ、デジタルTV、PDA、監視装置、HDDなどに搭載されたという。

尚、台湾のメディアDIGITimesが報じたところによると、Global UnichipはTSMCのFabの稼働率の上昇と合わせて業績を回復させており、2012Q2量産予定の4GベースバンドおよびモバイルTV向けの40/28nmチップの設計を日本および韓国から受注するなど、2012年Q2いっぱいは業績好調が見込まれているという。

2012.03.12

2012年3月9日、Mentor Graphicsは、同社コンサルティング部門がGLOBALFOUNDRIES向けに歩留まり向上のためのカスタムDFMフローを開発した事を発表した。

発表によるとMentorのコンサルティング・チームは、GLOBALFOUNDRIES向けのカスタム・DFMフローとして、GDSデータベースを高速に解析しDFM処理を施す「Calibre」ベースのソリューションを開発。同ソリューションはGDSデータベースを直接修正するもので、具体的には、メタル拡張、ビア二重化(角ビアのサポートを含む)、ビア・エンクロージャ改善といったDFM処理を「Calibre」製品群を組み合わせて自動的に実行する。当然ながら修正後のレイアウト・データは「Calibre」製品によってDRCエラーの有無など修正に伴う影響を即座にチェックされる。

同カスタムDFMフローはシリコン・テストにより大幅に歩留まりを向上できる事が確認されており、45/40および32/28nmプロセスを使用するGLOBALFOUNDRIESの顧客に提供されるとの事。尚、同フローはカスタムDFMフローと言っても、モジュラ構造のスケーラブルなフローで、GUIを始めユーザビリティが高く新しいプロセスへの移行もし易いようで、同フローをわずか数日で32/28nmから45/40nmに移植できた例もあるという。

2012.03.09

2012年3月8日、エレクトロニクス業界向けのハード設計管理ソリューションを提供する米ClioSoftは、2011年の同社の業績について発表した。

発表によるとClioSoftの2011年の受注額は前年比53%増を達成。具体的な受注額は明らかにされていないが、受注増は既存顧客に加え新規顧客を23社獲得したことによるもので、中でも欧州地域が好調で前年比139%増の受注を獲得したという。

ClioSoftは2011年の同社の業績アップを支えた製品導入顧客として、Allegro Microsystems , Lattice Semiconductor , ON Semiconductor , Rohde & Schwarz, Analog Devices , International Rectifier , Linear Technologyといった大手の名前を挙げている。

ClioSoftの提供するハードウェア設計管理ツール「SOS」は、複数ツールのデータ管理や設計データのバージョン管理など、統合的なプロジェクト/データ管理機能を持ち、多拠点にまたがる分散設計のメネジメントにも対応。設計データの管理機能としてCadence,Mentor,Synopsys,SpringSoftの各社設計ツールのデータを統合する機能を備えている。また、上記ベンダ以外のツールが扱う設計データについても、UDMA(Universal Data Management Adaptor)という機能によってデータの統合と管理が可能。「SOS」は、コストパフォーマンスの優れた設計マネジメント・ツールとしてワールドワイドで多くの採用実績がある。

2012.03.09

2012年3月7日、Mentor Graphicsは、PCB設計ツール「PADS」のバージョンアップを発表した。

発表によると「PADS」の最新バージョン9.4では大きく2つの機能強化が実施された。

一つは配線機能の強化で、新機能「ネット関連付け機能」によりネットをグループ化し制約を割り当てることにより、ハイスピード制約を満たす配線を対話型の作業で短時間で自動処理できるようになった。

もう一つはDFM解析機能の追加で、「PADS Layout」上で設計したPCBデザイン・データのDFMルール・チェックが可能となった。このDFM解析機能は同社のPCB製造ソリューションである「Valor」製品の技術をベースとしており、100を超える製造/実装ルールをPCBの設計段階でチェックすることで、製造上の問題を早い段階で解決できる。

2012.03.09

2012年3月8日、ESLソリューションを手掛ける米Carbon Design SystemsとSoCインターコネクト設計ソリューションを手掛ける仏Arterisは、バーチャル・プラットフォーム用モデルの供給に関する両社のパートナーシップを発表した。

発表によると両社は、Carbonのバーチャル・プラットフォーム作成環境「SoC Designer」向けにArterisのインターコネクトIP「FlexNoC」のCarbonizedモデルを開発。Carbonは同社のWebポータル「IP Exchange」上で同モデルの供給を開始した。

Carbonの提供するCarbonizedモデルは、バーチャル・プラットフォーム上で使用する100%サイクル精度の高速シミュレーション・モデルで、プロセッサ・モデルを中心に様々なモデルが提供されている。供給されるモデルは当然ながらSoC開発のニーズに則したラインナップとなっており、この程先端SoCでの採用実績を拡大しているArterisのNoCモデルが加わった。

2012.03.08

2012年3月5日、Mathworksはアルゴリズム開発環境「MATLAB」に付属する2つの新製品「HDL Coder」と「HDL Verifier」のリリースを発表した。

今回発表された2つの新製品「HDL Coder」および「HDL Verifier」は、「MATLAB」の新バージョン2012aに付属するハードウェア設計向けのオプション製品で、厳密に言うと中身的には新製品ではない。「HDL Coder」はこれまで「Simulink HDL Coder」として、「HDL Verifier」は「EDA Simulator Link」として提供されていた。

では今回リリースされた製品は何が違うかと言うと、既存の「Simulink HDL Coder」がSimulinkモデルからRTLを自動生成するツールだったのに対し、新しい「HDL Coder」はSimulinkモデルからの生成に加えてMATLABのMファイルから直接RTLを生成することが可能となった。これまではMATLAB環境からRTLを生成するにはSimulinkを介す必要があったが、「HDL Coder」を使用すればその必要は無くなる。

※画像はMathWorks提供のデータ。

MATLAB MファイルからのRTL生成にあたっては、アルゴリズム中の浮動小数点を固定小数点に自動変換する事も可能だが、この処理には別売のオプション・ツール「MATLAB Fixed-Point Toolbox」が必要となる。また、「HDL Coder」はメモリ・マッピング、パイプライン、演算リソースの共有などについてユーザー任意の指定が可能で、入力するMファイルのテストベンチからRTLのテストベンチを生成することも可能。VerilogまたはVHDLのRTLコードと合わせてAltera,Xilinx,Mentor,Synopsys各社の論理合成ツール用のスクリプトも出力できる。更に別売りオプション・ツールの「Embedded Coder」を利用すれば、MファイルからSystemC TLM2.0のコードも出力することが可能だという。

※画像はMathWorks提供のデータ。HDL CoderのGUI画面

MathWorksジャパンの柴田克久氏によると、「HDL Coder」は主にアルゴリズム開発者をターゲットとした製品で、アルゴリズム開発者が下流のハードウェア設計者に設計データを渡す際に役立つとしている。同種の製品としてはSynopsysの提供する「Synphony Model Compiler」があるが、こちらは論理合成ツールと連動してターゲット・デバイスに特化した回路の最適化を行うなど、実装向けのコード生成に主眼を置いた製品で、どちらかと言えばハード設計者向けであり「HDL Coder」のコンセプトとは温度差を感じる。アルゴリズム開発者にしてもハード設計者にしても、MATLAB/SimulinkからのRTL合成を求めるニーズは少なからずあるが、両者のニーズをうまく吸収するには、MATLABからRTLにダイレクトに落としこむよりも、まずは中間フォーマットとしてESLシミュレーションにも利用可能なCやSystemCをキッチリ出力する。そんなソリューションが有ると合成エンジンの選択肢も広がり、ユーザーにとっては嬉しいかもしれない。そういった意味で「HDL Coder」で実現されるMファイルからTLM2.0へのパスは興味深い。

もう一つの新製品「HDL Verifier」は、以前の「EDA Simulator Link」で実現していたMATLAB/Simulinkと論理シミュレーターとの連携に加え、FPGAボードとの連携機能を実現したもので、機能としてはMATLABの前バージョンから実装されていた。MATLAB/SimulinkとFPGAボードとはEthernetインタフェースで接続され、「HDL Coder」で生成したRTLコードをAlteraおよびXilinxのインプリメント環境に渡してFPGAボードに実装可能。これまではXilinx製FPGAへのインプリメント・パスをサポートしていたが、今回リリースした「HDL Verifier」からAltera製FPGAへのインプリメントとハンド・コーディングされたRTLコードの実装が可能となった。同環境を利用すれば、MATLAB/Simulink環境で開発したアルゴリズムを「HDL Coder」でRTLに落とし、「HDL Verifier」を用いてFPGAボードで検証する事が可能となる。

※画像はMathWorks提供のデータ。

尚、「HDL Coder」および「HDL Verifier」は既に出荷中でライセンス価格は、「HDL Coder」が135万円、「HDL Verifier」が42万5000円から。それぞれのツールを利用するためには既存のMATLAB/Simulink環境を最新のバージョン2012aにアップグレードする必要がある。また、MathWorksではAlteraおよびXilinx製FPGAを搭載した15種類のFPGAボードとCadenceおよびMentorのHDLシミュレーターを「HDL Verifier」で正式サポートしている。

2012.03.07

2012年3月6日、Cadenceは「Encounter」インプリメント・ツール製品群による最新のRTL-to-GDSIIフローを発表した。

今回Cadenceが発表した「Cadence Encounter RTL-to-GDSIIフロー」は、最先端の20nmプロセス向けを含む高性能かつ大規模な設計向けに顧客企業との共同開発で実現されたソリューションで、以下の各ツールおよび技術によって実現されている。

・Encounter RTL Compiler

・Encounter Test

・Encounter ECO Designer

・Encounter Digital Implementation System、Clock Concurrent Optimization (CCOpt)・Encounter Timing System

・Encounter Power System

・Cadence QRC Extraction

・Cadence Physical Verification System

・その他各種DFMテクノロジ

「Cadence Encounter RTL-to-GDSIIフロー」では、20nm設計向けの機能としてダブル・パターニング機能などがサポートされてようだが、3つの新しいCadenceの独自技術「GigaOptエンジン」、「CCOptテクノロジ」、「GigaFlexテクノロジ」が実装されており、これが今回の新フローの目玉と言える。

「GigaOptエンジン」は、配置・配線情報考慮の論理合成とレイアウト最適化機能を統合した最適化エンジンで、マルチCPUを用いた分散処理をサポート。相関性のとれた迅速なタイミング収束を実現する。「CCOpt(Clock Concurrent Optimization)テクノロジ」は、クロックツリーの消費電力とチップ面積を削減する最適化機能で、パフォーマンスも最大で10パーセント向上させることが可能。「GigaFlexテクノロジ」は1億インスタンスを超える大規模デザインの迅速な設計を実現する技術で、トップレベルとブロック階層の設計をコンカレントに扱い設計期間を10分の1までに短縮できるという。

SoC,ASSPの世界では、現在28nmプロセスの量産がようやく立ち上がった段階であるが、既に業界は次の20nmプロセスでのチップ試作を進めており、EDA各社も20nmプロセス製品を実現するキー・プレイヤーとしてファブ、ファブレス・ベンダ、IPベンダらと様々な形で協業を進めている。

Cadenceは既に、ARM、TSMC、Samusung、GLOBALFOUNDRIESのそれぞれと共同して20nmテスト・チップをテープアウトする事に成功しており、ARMとの協業においては競合他社に先行する形で業界初となる20nmマルチコア・プロセッサ 「ARM Cortex-A15」のテープアウトに成功している。20nm設計への対応に関しては、当然ながら競合のSynopsys,Mentorも積極的に取り組んでおり、STMicroelectronics向けにはCadenceよりも両社が先行しているように見える。先端プロセス向け配置配線で勝負するAtopTechは、28nmプロセスでTSMCの認証を勝ち取ったが未だ20nmプロセスの話題には登場してきていない。また、同分野では、SynopsysがMagmaのソリューションを取り込んだ事で新たな技術が生まれてくる可能性もある。