NEWS

2012.07.26

2012年7月25日、Synopsysは、同社のバーチャル・プロトタイピング・ツール「Virtualizer」と同ツールを用いたバーチャル・プロトタイプ作成キット「Virtualizer Development Kits(VDK)」のバージョンアップを発表した。

発表によると最新の「Virtualizer 12.06バージョン」では、バーチャル・プロトタイプを作成するための機能が拡充された。具体的には、新しくモデル・オーサリング機能とIP仕様インポート機能が追加され、従来よりもモデリングの生産性を高める事が可能となった。

モデル・オーサリング機能としては、自動デザイン・ルール・チェック機能やデザインに則したヘルプ機能などが用意され、よりモデル作成を簡素化/自動化できるようになった。また、IP仕様インポート機能は、IP-XACT、Excel、Word、PDF形式のIP仕様からモデルを自動生成することが可能。同機能でSystemC Modeling Library(SCML)ベースのモデルやTLM-2.0バス・インターフェイス・モデルを自動生成できるという。

更に今回のバージョンアップでは、新たにシミュレーション解析用のシミュレーション・プロファイラーが追加されたほか、Lauterbach TRACE32 System、ARM DS-5など汎用ソフトウェア・デバッガをプラグインで利用できるようになった。また、MathWorks社のシミュレーション環境 「Simulink」と「Virtualizer」が統合可能となり、電子回路以外のモデルを用いたバーチャルHILS(Hardware-in-the-Loop)テストのようなシミュレーションを容易に実現可能となった。

この最新の「Virtualizer 12.06バージョン」は既に出荷が開始されている。

2012.07.25

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2012.07.25

2012年7月24日、Alteraは2012会計年度第2四半期(12年4-6月)の売上を報告した。

発表によるとAlteraの2012年Q2(12年4-6月)売上は、前年比約15%減、前期Q1比約21%増の4億6480万ドル、営業利益は前年比約33%減、前期Q1比36%増の1億5930万ドルだった。これでAlteraは4四半期連続で売上前年比2ケタ減となったが、売上、営業利益共にQ1実績を上回り業績回復の兆しを見せている。

AlteraのQ2売上を地域別で見るとアジア市場が前期比29%増と大きく伸び、全売上に占める割合が46%となった。製品カテゴリ別では28nm FPGA「Stratix V」が前期比190%増と非常に大きな伸びを見せた。この売上急増は「Stratix V」の量産開始が今年3月からであったためだが、市場における28nm FPGAへの強いニーズを示していると言える。分野別では、テレコム及びワイヤレス分野が前期比33%増、ネットワーキング、コンピュータ及びストレージ分野が前期比26%増と共に好調だった。

2012.07.23

2012年7月19日、Synopsysは同社の配置配線ツール「IC Compiler」の最新版2012バージョンのリリースを発表した。

発表によるとリリースされた「IC Compiler 2012バージョン」には、ギガヘルツ級の高性能デザインを実現するための新機能として、クロック周波数を上げるマルチソースCTS(クロック・ツリー合成)、タイミング最適化機能、強化されたフロアプラン機能、最先端プロセスのメリットを活用できる新たな配置配線アルゴリズムなどを搭載している。

「IC Compiler」のユーザーであるルネサス エレクトロニクスは、早速この「IC Compiler 2012バージョン」の新機能マルチソースCTS(クロック・ツリー合成)を複数の複雑なクロック構造を持つデザインで試したとの事。その結果「我々が目標としていたスキューとレイテンシの目標を容易に達成することができた」とコメントしている。

2012.07.20

各組織の発表している2012年7月時点での2012年世界半導体市場成長予測を更新しました。新たにIDCとTSMCが予測値を発表しました。

※6/11に報じたWSTSによる予測値の上方修正は誤りでした。訂正の上、謹んでお詫び申し上げます。

2012.07.20

2012年7月18日、Xilinxは2013会計年度第1四半期(2012年4-6月)の売上を報告した。

Xilinxの2013年Q1(12年4-6月)の売上は、前年同時期比5%減、前期比4%増の5億8280万ドル。営業利益は前年比13%減、前期比12%増の1億6460万ドルという結果だった。これで売上前年割れは4四半期連続となるが、2012年Q4に続いて今期も売上が前四半期を上回る結果となった。

地域別売上ではアジアの売上が前期比16%増と大きく伸び、昨年同時期と同等の地域別シェアに戻した。その一方で北米だけは唯一前期よりも売上を落とした。分野別の売上構成では、ブロードキャスト、コンシューマーおよび自動車分野が好調で前年比14%増、前期比12%増と伸びを示し、売上全体に占める割合を16%に伸ばした。製品別売上では、Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6で構成される新製品カテゴリがかなり好調で、既に全売上の17%を占めるに至っている。

尚、Xilinxの2012会計年度(11年4月-12年3月)の売上合計は前年比5.5%減の22億4073万ドル、営業利益の合計は前年比4%減の7億8607万ドルだった。

Xilinxは次期2013年Q2(12年7-9月)の売上を今期の4%から8%減になると予測している。

2012.07.19

2012年7月、パシフィック・デザイン株式会社は、自社開発したRTLフォーマル・プロパティ・チェッカ「AiPG」の発売を開始した。

パシフィック・デザインの「AiPG」は、EDA技術の研究で有名な東京大学藤田昌宏教授の指導の下、2010年から具体的な開発が開始されたフォーマル検証ツールで、「SMTソルバ」と呼ばれるwordベースの探索エンジンをRTL検証に適用するもの。

「AiPG」は「SMTソルバ」の中でも世界最高速の「Boolector」というオーストリア ヨハネス・ケプラー大学が開発したGNU/GPLベースの探索エンジンを採用しており、最小限のプロパティ記述およびプロパティ指定をもとにwordベースでVerilogで記述されたRTLの網羅的検証を自動実行する事が可能。検証対象を自動的に指定するプロパティ生成機能と分散型並列処理により容易かつ高速な網羅的検証が可能で、Dead Codeの検出、対抗Deadlockの検出、リソース衝突の検出など、フォーマル検証ツールが有効とされる用途において、これまでに無いアプローチでのプロパティ・チェックを実現する。

「AiPG」はこの7月より販売が開始されており、パシフィック・デザインでは顧客のプロパティ要求を「AiPG」に組込み、プロパティ生成を自動化させるといった対応も行なっている。

2012.07.19

2012年7月18日、Cadenceは、シャープによるEncounter RTL-to-GDSIIフローの採用事例を発表した。

発表によるとシャープはCMOSイメージ・センサの開発に向けて「Encounter RTL-to-GDSIIフロー」を採用。同フローにはツールとして論理合成「Encounter RTL Compiler」、フォーマル検証「Encounter Conformal Equivalence Checker」、配置配線「Encounter Digital Implementation System」、DFT/ATPG「Encounter Test」が含まれており、実際に設計に適用したところ、これまでのフローと比較して設計期間を1/2に短縮できたという。

また、シャープはタイミング、チップサイズ、生産性におけるQoRの向上も実現したという事で、「設計期間および設計品質の劇的な改善を目の当たりにした」という「Encounter RTL-to-GDSIIフロー」の採用事例の詳細は、7月20日にみなとみらいで開催されるCadenceのプライベート・イベント「CDNLive! Japan 2012」で発表される。

2012.07.18

2012年7月18日、Cadenceは、富士通セミコンダクターが同社のタイミング解析ツール「Encounter Timing System」をサインオフ向けツールとして採用したことを発表した。

発表によると、富士通セミコンダクターとグループ会社の富士通VLSI株式会社が共同で「Encounter Timing System」を評価したところ、ECOフローにおいて1回のイタレーションで99%のhold violationを処理。競合製品と同等のセットアップ時間で優れた配線性を実現した。物理性を考慮したタイミングECOが可能な「Encounter Timing System」は、富士通セミコンダクターの評価基準を満たし、富士通セミコンダクターの製造向けリファレンス設計フローに統合されたという。

尚、富士通セミコンダクターは、従来から使用しているCadenceのインプリメンテーション・ツールと「Encounter Timing System」を組み合わせて利用する事で、ECOループの回数を削減することに成功。同事例は7月20日にみなとみらいで開催されるCadenceのプライベート・イベント「CDNLive! Japan 2012」で発表される。

2012.07.17

2012年7月12日、Cadenceは、同社のIP製品の一つであるPCI Expressの検証IPへの新機能追加を発表した。

発表によると今回Cadenceは、既存のPCI Expressの検証IPに下記の機能追加を実施。

・PCI Express PIPE4仕様のサポート

・新しい性能測定機能の追加

・コンプライアンス・テストを短縮、簡易化するテスト・スイートの追加

・カバレッジおよび検証プランから成るTripleCheck機能の追加

・検証スピードを加速するAccelerated PCIe VIPのサポート

今回の新機能追加でPIPE4(PHY Interface for PCI Express)がサポートされたことにより、CadenceのPCI Expressの検証IPは、SR-IOV、MR-IOV、NVMe、PIPE4と広範囲にPCI Expressアプリケーションの開発に対応可能となる。

Cadenceによると「TripleCheck機能」は、PCI Express仕様の全セクションを網羅したテスト・スィート、カバレッジ・モデル、検証プランを単一環境で提供するもの。その中身はユーザーの個別の構成に合わせて自動的にカスタマイズされる。

また、「Accelerated PCIe VIP」は、Cadenceのアクセラレーター/エミュレーター「Palladium XP」を使用してUVM準拠のテストベンチでのシミュレーションをアクセラレーションするためのもので、シミュレーターよりも100倍高速なフルチップ・シミュレーションを実現できるという。

2012.07.17

2012年7月10日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の論理シミュレーター「Riviera-PRO」とAgilentのESL環境「SystemVue」との協調シミュレーション・インターフェースの提供を発表した。

発表によると、提供される協調シミュレーション・インターフェースは、AldecとAgilent Technologiesの両社が共同で開発したもので、Aldecの論理シミュレーター「Riviera-PRO」の最新バージョンを用いたハードウェア設計とAgilentのESL環境「SystemVue」を用いたアルゴリズムおよびシステム・レベル設計をリンク出来るようになる。

AgilentのESL環境「SystemVue」は、RFを考慮したベースバンド設計を可能とする環境で、同環境とAldecの「Riviera-PRO」が繋がる事で、「Riviera-PRO」を利用しているハードウェア設計者は、シミュレーションでSystemVueのコンポーネントを再利用したり、シミュレーションのテストベンチとしてSystemVueを使用できるようになるという。

2012.07.17

2012年7月11日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、Berkeley Design Automationは、同社の回路シミュレーター「Analog FastSPICE」を先端プロセス向け配置配線ツールを手掛けるATopTechが採用した事を発表した。

発表によるとATopTechは、同社の配置配線ツール「Aprisa」のタイミング解析の精度を改善するためにBerkeleyDAの「Analog FastSPICE (AFS)Platform」を選択。「Aprisa」のタイミングドリブン配置配線テクノロジでは、先端テクノロジノードでSPICEレベルの精度を達成するため絶えずキャリブレーションが行われており、そのキャリブレーションに「Analog FastSPICE Platform」を用いることでタイミング解析の精度を改善する。ATopTechは「Analog FastSPICE Platform」を採用した理由として、同製品の高速・高精度なパフォーマンスと合わせて、「大規模なポストレイアウトのキャリブレーションに必要なキャパシティを備えているから」と、そのキャパシティを挙げている。

2012.07.17

2012年7月16日、ハードウェア設計関連の技術および言語規格の標準化団体Accellera Systems Initiativeは、システム記述言語「SystemC」の最新バージョン2.3.0のライブラリの公開を発表した。

公開されたSystemCバージョン2.3.0のライブラリは、2011年11月に改訂されたIEEE 1666 SystemC LRMと互換性があり、トランザクション・レベル・モデリング(TLM)のをサポートしているが、そのほかにもモデリング面での機能向上(パワー・ドメインや抽象的なスケジューラーのモデリング、モデリングの簡素化)が実現され、シミュレーションAPIの改善や新たなスレッド・セーフティ・メカニズムにより、外部ツールとのより高度な連携やマルチ・スレッディングも可能になるという。

その他にも多くの重要な機能追加やエンハンスが施されているSystemCバージョン2.3.0のライブラリは、オープンソースのライブラリとして無料で下記URLよりダウンロード出来る。(※要ユーザー登録)

http://www.accellera.org/downloads/standards/systemc

尚、先日開催された国内のセミナー「SystemC Japan 2012」で公開されたAccelleraのデータによると、IEEE 1666-2005 SystemC標準のダウンロード数は2012年1月時点で47,165件。LRMが改訂された最新のIEEE 1666-2011 SystemC標準は今年1月から4月末までの間に5,738件のダウンロード実績があるという。

2012.07.13

2012年7月12日、SoC機能検証ソリューションを手掛ける米Breker Verification Systemsは、同社初となる投資会社からの資金調達を発表した。

発表によると今回Breker Verification Systemsに投資したのはアジアの投資会社Astor Capital Groupで金額にして500万ドル。これら資金はSoC向けにセルフ・チェック用のCのテストケースを自動生成する「TrekSoC」の営業、サポート及び製品開発の拡大に充てられる予定となっている。

同社は業績好調の様子で2011年は売上前年比150%増であったことを発表している。今年2月には、本社をテキサスからシリコンバレーに移し、シリコンバレーのエンジェル投資家としても有名なMichel Courtoy氏を役員に迎え入れていた。

49DACで取材に訪れた際に聞いた話では、今年に入ってからも順調にビジネスが成長しており、公表済みのNVIDIA、STMicroelectronicsの他にIBM、Broadcom、Qualcommなどの大手が既に同社の顧客になっているとの事だった。同社は未だ日本で営業展開していないが、代理店は探している様子であった。

※画像は49DACで撮影した同社のパネル

2012.07.12

2012年7月11日、米EDA Consortiumは、2012年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

EDACの発表によると、2012年Q1(1月-3月)の世界のEDA売上総額は、前年比6.3%増、前Q4比9.6%減の15億3690万ドルだった。これで9四半期連続で売上前年比増を達成した。

2012年Q1の売上を分野別に見ると、最も市場規模の小さいサービス分野以外は全て前年比増を記録。IC Physical Design & Verification分野は前四半期に続いて前年比2ケタ増を記録した。

2012年Q1の売上を地域別に見ると、日本市場だけが前年割れで、それ以外の地域は全て前年比増を記録。日本市場の売上はかろうじてヨーロッパの売上を超えたが、2四半期連続で日本市場だけ前年割れという状況は、国内半導体の厳しい現実を表していると言える

2012年Q1時点でのEDA業界の従業員数は27848人で、前期Q4比0.8%増となっている。

2012年Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 5億6480万ドル 6.5%Up

■IC Physical Design & Verification分野 3億5090万ドル 10.2%Up

■IP分野 3億9130万ドル 5.4%Up

■サービス分野 8240万ドル 3.8%Down

■PCB/MCM分野 1億4750万ドル 5.1%Up

2012年Q1地域別の売上と昨年同時期との比較は以下の通り。

■北米 6億6150万ドル 9.8%Up

■ヨーロッパ 2億6170万ドル 8.2%Up

■日本 2億6240万ドル 11.1%Down

■アジアその他地域 3億5130万ドル 14.4%Up

※EDAC(EDA Consortium)

2012.07.06

第49回Design Automation Conferenceに出展していたJasper Design Automationブースのレポート。

Jasperは49DAC開催前の5月に新製品「JasperGold Apps」を発表。DACでは同製品の話題が中心となっていた。

※画像は49DACでのJasperブースの様子

Jasperによると、これまで旗艦製品として提供してきた「JasperGold」が総合的なフォーマル検証・ソリューションであったのに対し、今回発表された「JasperGold Apps」は、論理検証における様々な個別の問題に特化した専用ツールで、現在下記6種類の「JasperGold Apps」を提供中。各アプリは共通のGUIを使用しており、使用しているデータベースも共通であるため、アプリ間の連携も可能。そのメリットは特定の目的をシンプルに解決出来る事にあり、Jasperはリーズナブルな価格設定による費用対効果も大きいとする。ちなみに、価格はアプリ毎に個別に設定されており使用本数により幅があるようだが、安いものでは年3000ドルからという事だった。

【提供中のJasperGold Apps】

・ Formal Property Verification App:基本的なアサーション検証

・ Connectivity Verification App:接続検証

・ X-Propagation Verification App:RTLでX伝搬の網羅検証

・ RTL Development App:設計時のダイレクトテスト

・ Control/Status Register Verification App:レジスタ検証

・ Architectural Modeling App:アーキテクチャ検証

尚、この「JasperGold Apps」は、既に大手顧客によって利用されており、ブースではST Microelectoronics、NVIDIA、ARM、Broadcomらが「JasperGold Apps」のユーザー事例を発表していた。(後述の6/29セミナー・レポート参照)聞くところによると日本国内にもユーザーがいるという話で、Jasperとしてはユーザーのニーズに応じて順次アプリ数を増やしていく計画。既に8月には更に2種類の「JasperGold Apps」が追加される計画と聞いた。

※画像は49DACでのJasperブースの様子

■6/29 JASPER Seminar2012

Jasperは、6/29に新横浜のホテルで同社の日本代理店である株式会社シンコムと共にJASPER社の製品紹介セミナー「JASPER Seminar2012」を開催した。セミナーでは、Jasper本社並びにシンコムのメンバーにより、「JasperGold Apps」を含むJasper製品の紹介や事例紹介が行われ、70名ほどの参加者を集めた。

やはりセミナーの中心となったのは「JasperGold Apps」の話題であったが、49DACで紹介された大手ユーザーの事例が興味深かった。以下、事例の概要を紹介する。

ARMはJasperのヘビー・ユーザーとして知られているが、昨年11月にARM ACEプロトコルの仕様検証などを目的にJasperとの契約を強化。ARMではプロトコル検証に限らずJasperのツールを設計初期からポストシリコンまであらゆるところで使用しており、何千というプロパティの検証状況が自動的にレポートされる仕組みが社内に構築されているとの事。その検証手法はARM Cortex R7 MP Core, Cortex A15などの開発にも適用されているという。

NVIDIAもJasperの大口顧客の一つで、事例として紹介されたのは、低消費電力化のために挿入したクロック・ゲーティングが機能に影響を及ぼさないことをJasperツールで網羅的に検証するというもの。NVIDIAでは、全てのプロジェクトでJasperツールを用いてクロック・ゲーティングやX伝搬の検証を行うことになっているようで、2009年から超大規模ロジックでJasperのフォーマル検証が利用されているという話も紹介された。

※画像は6/29 Jasperセミナーの発表スライド

ST Microelectoronicsの事例では、Jasper LPV(Low Power Verification)という新しい「JasperGold Apps」が紹介されていた。同アプリはSTのニーズに応じて開発が進められているもので、低消費電力デザインの検証を目的にパワー記述フォーマットの標準規格「CPF」および「UPF」をサポート。X伝搬検出も利用しており、いずれ製品としてリリースされる可能性がある。

Broadcomの事例として紹介されたのはFIFOの検証。Jasperの非同期状態をモデリングする検証モジュール( Frequency Jitter PA)とデータ転送のための検証モジュール(Scoreboard PA)を利用することでシミュレーションでは不可能だった網羅検証を行うことが出来たとの事。

尚、セミナーでは今後製品化予定の新たな2種類の「JasperGold Apps」が紹介された。一つは「Property Synthesis」でRTLやシミュレーション結果からプロパティを自動生成するアプリ。この機能は元々「JasperGold」には無かったもので、別製品「ActiveProp」で実現されていた機能がアプリ化された形だ。シミュレーションのホールをレポートする機能も備えるという。

もう一つのアプリは「Coverage Metrics」で、文字道りフォーマル検証のカバレッジ解析を行うもの。Accelleraが49DACで発表したカバレッジ標準「UCIS 1.0」をサポートし、シミュレーション結果なども取り込みながらカバレッジの指標をレポート可能なようで、その詳細は今後明らかになる予定。

※UCIS:Unified Coverage Interoperability Standard

※画像は6/29 Jasperセミナーの様子

2012.07.05

2012年7月3日、米SIA(Semiconductor Industry Association)は、2012年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年5月の世界半導体売上は前年同時期比約3.4%減、前月比約1.4%増の243億9000万ドルという統計結果となった。過去1年間連続して売上前年割れを記録しているが、この3ヶ月は連続して売上前月増を達成している。

前月比3.4%増という数字は、2010年5月以来の水準で過去2年間で最大の成長率となった。

2012年5月の売上を前年比でみると、欧州の売上減が相変わらず大きいが、前月と比較すると若干回復しているのが分かる。好調なのは日本を除くアジア地域で前年売上は下回るものの、先月比は3.1%増、11年12月-12年2月の売上平均と比較すると10.5%増と大きな伸びを示している。

2012.06.21

第49回Design Automation Conferenceに出展していたAtrentaブースのレポート。

Atrentaのブースを訪れてまず目についたのは、新しくなった同社のロゴ。以前と違い旗艦製品「SpyGlass」のロゴを会社ロゴのように使用しており、そのロゴも新たなデザインに変更されていた。話によると、RTL解析ツール「SpyGlass」製品ファミリのプラットフォームの刷新に伴いロゴも一新したとの事で、「SpyGlass」を全面に押し出し更なる成長を目指す意気込みが感じられた。

その「SpyGlass」、今年5月にリリースされたバージョン4.7によって、これまで個々のポイント・ツールとして機能していた「SpyGlass」ファミリの各ツール群が統合された。これにより各ツールの連携利用が可能となり、例えば1プッシュでデザインに対する独自のルール・チェックやCDC,ERCといった解析結果をまとめてレポート出力する事が可能となった。Atrentaは、1ライセンスで全ての「SpyGlass」ファミリ製品を利用できるIPの品質認証キット「Atrenta IP Kit」を提供しているが、今回のプラットフォームの統合は、TSMCも採用したこの「Atrenta IP Kit」の開発の延長線上の対応と想像できる。

また、今回のバージョンアップでは、「SpyGlass Power」によるRTLパワー・リダクション機能や、「SpyGlass」の基本機能であるLint機能のランタイムなど、個々のツールの機能強化も図られている。49DACにおいては、「Fast Lint」と呼ぶ新たなLintメソドロジが発表され、従来比4-9倍の速さでLintチェックが可能とされていた。また、デモ・スイートでは、Ciscoによる「SpyGlass CDC」の事例、CiscoとIBMによる「SpyGlass Power」の事例、ST Microによる「GenSys Assembly」の事例が紹介されていた。ST Microの事例によると、通常1ヶ月は要するデザイン変更に伴うインプリメントの修正作業を「GenSys Assembly」を用いて僅か1日で完了した実績もあるという。

尚、Atrentaは、Qualcomm、ベルギーIMEC、AutoESLらと3D-IC向けのアーキテクチャ解析手法の開発に取り組んでいたが、AutoESLがXilinxに買収された現在も同研究開発は着々と進めていると聞いた。

■6/20 アサーション合成ツールを手掛けるNextOp社の買収を発表

2012年6月20日、Atrentaは、アサーション合成ツール「BugScope」を手掛けるNextOp社の買収を発表した。

買収条件などの詳細は明らかにされていないが、社長兼CEOのYunshan Zhu氏をはじめとするNextOp社のチームはAtrentaへ移る様子。Atrentaは同社初となる企業買収によって、シミュレーター、エミュレーター、フォーマル検証ツールと様々な検証ツールに繋がる「アサーション合成」という武器を手にする事になる。

NextOpは、2009年にDACに登場した新興EDAベンダでコア・メンバーは中国系。社長兼CEOのYunshan Zhu氏は元シノプシスAdvanced Technology Groupのメンバーだった。同社は2010年に製品「BugScope」をリリース以降、順調に顧客を開拓していた様子でNVIDIAやAlteraなど大手が「BugScope」を採用していた。NetxOpは今年の49DACにおいても展示ブースを構え多くの来場者を集めており、「BugScope」のライセンスは順調でカバレッジ品質を評価できる「Progress ReportT」機能がユーザーに受けていると話を聞いていた。

※画像は49DACでのNextOp社のブース

■7/19 第一回Atrenta Technology Forum開催

Atrentaは来月7月19日に「第一回Atrenta Technology Forum」を開催する。同セミナーでは49DACでの最新情報をはじめ、ディジタルメディアプロフェッショナル、日本システムウェア、ルネサスエレクトロニクス等、同社の日本ユーザーの事例が紹介される予定。

2012.06.20

第49回Design Automation Conferenceに出展していたAldecブースのレポート。

Aldecの今年の話題は大きく2つ。

一つは現在米国においてβテストを開始している「Aldec Cloud」と呼ぶ新サービス。「Aldec Cloud」は、Amazon社の提供するクラウド環境を利用したサービスで、1時間単位US$25-でAldecの論理シミュレーター「Riviera-PRO」が使用できるというもの。1時間US$25-という料金にはAmazonのインフラ使用料も含まれており、現在のところ利用料の決済はAldecと直接やり取りする形だが、将来的にはクレジット決済の導入も計画されている。

「Aldec Cloud」はAldecのユーザーでなくても利用可能で、サービスを利用する際にはAldecの用意する所定のWebサイトにアクセスする。(Amazonの環境は意識しないで良い。)ユーザーは必要に応じて「Riviera-PRO」のライセンスを時間単位で利用可能で、例えば、1本のライセンスを100時間使用しても100本のライセンスを1時間使用しても料金は同一。大量のライセンスを集中的に使用するような大口顧客のニーズにも、必要なときに必要な分だけライセンスを利用したいという中小企業の小口ニーズにも対応可能だが、クラウド環境上で一気にシミュレーションを走らせ、シミュレーション結果をダウンロードしてデバッグは手元の環境で行うという使い方がAldecの想定。シミュレーションのJob履歴を管理するGUIやAldec独自のセキュリティ機能も用意されている。

話によると米国では既にβカスタマー15社が同サービスを利用中。間もなくワールド・ワイドでβテストを公開する計画で日本でも同サービスを利用可能になるとの事。日本では驚くほどの低価格でサービスが提供されるようで、試用者向けに最初の10時間は無料になる予定と聞いた。

もう一つの話題は、検証メソドロジ「OS-VVM」。

「OS-VVM」はVHDLユーザーのためにAldecとSynthWorks社が開発したもので、VHDLユーザー向けに今年の1月からオープンソースで提供されている。SystemVerilogベースの検証メソドロジで利用されているファンクション・カバレッジやランダム検証といった手法をVHDLベースで実現すべく、「Coverage Package」、「Random Package」といった無償のパッケージが用意されており、VHDLユーザーも高度な検証環境を比較的容易に構築できるようになる。

今回のDACでは、初となる「OS-VVM」のユーザー会も開催され、多くのユーザーを集めた様子で、聞く所によると「OS-VVM」のダウンロード数は月200件のペース。日本でもワールドワイドでもRTL設計者全体の25%近くはVHDLユーザーであるとの話で、Aldecでは今後もユーザーのフィードバックを元にメソドロジのエンハンスを進めていく計画だという。

尚、この「OS-VVM」は、シミュレーターを選ばずに動作可能だが、VHDLのサポート範囲としては、VHDL 2002/VHDL 2008をサポートしているAldecのシミュレーターに分があるようだ。

※画像はAldecブースのマスコット「AL」君。仕組みは秘密との事だが、人間が話しかけると応答するお利口なロボットだった。

2012.06.07

2012年6月5日、米SIA(Semiconductor Industry Association)は、2012年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年4月の世界半導体売上は前年同時期比約2.9%減、前月比約3.4%増の240億7000万ドルという統計結果となった。これで売上前年割れは2011年6月から11ヶ月連続となったが、3月に続いて4月も売上が前月増を達成。前月比3.4%増という数字は、2010年5月以来の水準で過去2年間で最大の成長率となった。

2012年4月の売上を前年比でみると、欧州の売上が前年比14.4%減と大きくマイナス。欧州の経済情勢の悪化が如実に数字に現れている。

また、同日発表された2012年から2014年までの売上予測によると、2012年は前年比0.4%増の約3008億ドル、2013年は前年比7.2%増の3224億ドル、2014年は前年比4.4増の3365億ドルと継続した市場の成長が予想されている。

2012.06.02

2012年6月1日、EDAツール関連の業界団体、米EDA Consortium(EDAC)は、2014年春までの新役員を発表した。

発表によると今回発表された新役員の中からJasper Design Automationの社長兼CEOのKathryn Kranen氏がチェアに選出され、Mentor GraphicsのWalden C. Rhines氏とCadenceの Lip-Bu Tan氏がバイス・チェアに選ばれた。

その他の役員は以下の通りで、NimbicのCEO Raul Camposano氏とIC Manageの社長兼CEO Dean Drako氏の2名が新メンバーとして役員入りした。

? Raul Camposano, CEO, Nimbic

? Edmund Cheng, President and CEO, Gradient Design Automation

? Dane Collins, CEO, AWR Corporation

? Aart de Geus, Chairman and CEO, Synopsys, Inc

? Dean Drako, President and CEO, IC Manage

? John Kibarian, CEO, president and co-founder, PDF Solutions

? Simon Segars, Executive VP & GM, PIPD and PD, ARM

? Ravi Subramanian, President and CEO, Berkeley Design Automation

2012.06.01

2012年5月31日、Cadenceは、STMicroelectronicsがCadenceのツールと協力によって、20nmプロセスのテストチップをテープアウトしたことを発表した。

発表によるとCadenceは、STMicroelectronicsに協力して20nmプロセス向け基礎IP、SKILLベースのPDKを開発。STMicroelectronicsはこれを採用し、更にCadenceのデジタル・インプリメント環境「Encounter」およびカスタム設計環境「Virtuoso」を用いて、20nmプロセスのミックス・シグナルSoC設計メソドロジを構築。同メソドロジを用いて20nmテストチップのテープアウトを完了した。

2012.06.01

2012年5月31日、フォーマル検証ツールを手掛けるドイツのEDAベンダOneSpin Solutionsは、同社の増資と社長兼CEOの交代を発表した。

発表によるとOneSpin Solutionsは、同社の実質オーナー会社であるベンチャー・キャピタルAzini Capitalから追加の出資を獲得。調達した資金は同社の製品開発及び営業活動の加速に充てられるという事だ。尚、今回の増資と合わせてOneSpin Solutionsは社長兼CEOを交代。新たに同社設立当初からのメンバーRaik Brinkmann氏が社長兼CEOに就任した。

2012.06.01

2012年5月31日、FPGAベースのプロトタイピング・ソリューションを手掛ける米S2Cは、新製品「Dual 7V2000T TAI Logic Module」の発売を発表した。

S2Cによると「Dual 7V2000T TAI Logic Module」は、Xilinxの最新の28nm FPGA「Virtex-7 2000T」を2個搭載したSoCプロトタイピング・ボードで、そのデザイン容量は最大4000万ASICゲート。「Virtex-7」を搭載したプロトタイピング・ボードは恐らく現時点で同製品が業界唯一で、単一のプロトタイピング・ボードとしては業界最大のデザイン容量を誇る。

「Dual 7V2000T TAI Logic Module」は、S2Cの製品としては5世代目の製品となるもので、デザイン容量の拡大の他に、プロトタイプのパフォーマンスや信頼性も改善され、リアルテイムにリソースやパワー、クロックをモニタリングするソフトウェアの新機能が用意された他、冷却システムの改善や、ギガビット・イーサネット経由のハードウェア制御などハード面での機能改善も合わせて実施された。搭載されるメモリは 2GBのDDR2メモリと4GBのDDR3メモリでそれぞれ最大800/1333MHzで同時動作可能。既存製品と同じく迅速なプロトタイプ作成のための各種IPが用意される。

「Dual 7V2000T TAI Logic Module」は既に出荷中で受注後8-12週間で納品。今週末から開催の第49回DACでは、その実物が展示される予定となっている。

※画像はS2C社Web掲載のデータ。

2012.06.01

2012年5月31日、レイアウト表示プラットフォーム「LAVIS」を手掛ける日本のEDAベンダTOOL社は、同社の旗艦製品の後継品「LAVIS-plus」の発売を発表した。

発表によると「LAVIS-plus」は「LAVIS」の後継品として、パフォーマンス、操作性、拡張性など、あらゆる面で「LAVIS」上回るスペックを備えており、例えば、マルチスレッド処理によりOASISデータのオープン時間は最大で「LAVIS」の1/5。描画時間はGDSおよびOASISデータで最大1/10。更にデータオープン時のメモリ消費量はLEF/DEFデータで1/2と、自慢の高速化に更に磨きをかけ省メモリも実現した。

更にGUIに大幅に手を入れ操作性を向上させたほか、「LAVIS-plus」をユーザー独自の形でカスタム利用できるように、「LAVIS-plus」のデータ・ベースへアクセス可能なAPIを公開した。

TOOLは今年も出展する49回DACで同新製品を展示する予定。その詳細は別途取材の上、レポート致します。

尚、TOOLはこれまで「LAVIS」を「レイアウト表示プラットフォーム」と表現していたが、今回の「LAVIS-plus」から「ICデザイン視覚検証ツール」と表現を変更。確かにその機能はもはや単なるレイアウト・ビューワではない。ちなみに、この新しい「LAVIS-plus」は「LAVIS」ユーザーは無償で移行可能との事。

2012.05.31

2012年6月3日より、カリフォルニア州サンフランシスコにて第49回Design Automation Conferenceが開催される。

昨年サンディエゴで開催された48回DACでは、減り続けていた来場者数が底を打ち、展示会に出展する企業数が5年ぶりに前年増となったが、今年はと言うと出展企業数は174社と昨年より微減。(EDA-EX調べ) うち、初出展となる企業は21社で昨年の26社を下回った。EDA業界全体の売上は好調に伸びているが、その一方で進む大手による市場の寡占化により、企業としてのプレイヤー数が減少しているのかもしれない。

ちなみに日本からの出展は、常連組のNEC、TOOLの2社に加えジーダットも久しぶりの参加を果たし計3社となった。

※主催者発表は出展社200以上としているが、大手企業ブース内のパートナー出展もカウントしている模様

主催者の発表によると、今年の49回DACで採択された論文数は集まった計742本のうち163本。論文投稿数は過去5年間で最高で、採択された論文の35%は組込みシステムおよびソフトウェア関連のものという事。事務局の発表によると、パワー解析/ローパワー、物理設計/DFM、組込みシステム向けアーキテクチャー/メモリ設計、ESS設計メソドロジ、その他新技術などがポピュラーな論文テーマだという。49DACではこれら論文発表と合わせて10件のSpecial Sessionが予定されており、Bio Design Automation関連3件、ESS関連2件とこの2つの分野が半数を占めている。※ESS:Embedded Systems & Software

また今年は6つのTutorialと8つのWorkshop、Apache(ANSYS)社がスポンサーとなるUser Trackも予定されており、User Trackでは5つの技術テーマに分かれて発表が行われるほか、設計者によるパネル・ディスカッションも予定されている。Keynoteは、ARMのCTO Mike Muller氏ほか、Intel,IBMの技術者、台湾国立清華大学の教授が登壇する。

今回の49回DACの話題の中心は何か? プログラムから読み取るのはなかなか難しいが、主催者側は昨年に続いて「組込みシステム開発」、「組込みソフトウェア開発」を強く推しており、それに関わりの深い「ESL/システムレベル設計」に関する話題も多そうだ。また、製品化が動き出した「3D-IC」関連やローパワー技術、先端プロセス向けのインプリメント技術あたりもキーワードとして目に付く。機能検証関連ではエミュレーション・システムやプロトタイピング・システムなどが熱そうだ。

尚、毎年恒例となっているGary Smith EDA社の

「49DAC要チェックリスト」は既に公開済みで、計27社がリストアップされている。(日本のジーダットもランク・イン) また、間もなく業界の辛口評論家John Cooley氏も自身のサイト

「DeepCHIP」で、49回DAC注目の企業を発表するはずだ。毎年「DeepCHIP」での紹介記事をコピーして配っている出展社も多い。

その他、恒例行事となったAtrenta、Cadence、SpringSoftの3社による

「I Love DAC」キャンペーンは今年も健在で、同キャンペーンに申しこめば展示フロアの3日間フリー・パスが無償で手に入る。 更に夜の恒例行事として有名なCadence主催の

「Denali Party」は、6月5日(火)の夜にダウン・タウンのクラブ貸し切りで開催される予定。

当サイトでは、49回DACのレポート記事を順次アップしていく予定です。乞うご期待!

2012.05.30

2012年5月29日、Cadenceは、同社の設計および検証IPが最新のDDR PHY Interface(DFI)3.1仕様をサポートした事を発表した。

DDR PHY Interface(DFI)3.1仕様は、5月29日にそのリリースがDFI Technical GroupよりアナウンスされたばかりのDDR4メモリ向けのインタフェース・プロトコル仕様で、今回仕様のバージョンアップに伴いCadenceは自社の設計IP(DDRコントローラIPおよびDDR PHY)と検証IP(Cadence Verification IP Catalog)をDFI3.1仕様に対応させた。もちろん設計および検証IPとしては業界最速の対応となる。

尚、最新のDFI3.1仕様には、モバイル端末向けのLPDDR3メモリ規格のサポートが追加されているという。

2012.05.30

2012年5月29日、Mentor Graphicsは、同社のDFM機能「SmartFill機能」をGLOBALFOUNDRIESが20nm製造プロセスで使用することを発表した。

発表によるとGLOBALFOUNDRIESは、同社最先端の20nm製造プロセスでMentorのDFMツール「YieldEnhancer」に搭載される高度な自動フィル挿入機能「SmartFill機能」の使用を決定。同機能を利用すれば設計者は、回路性能への影響とファイルサイズの増大を抑えつつ、正確なダミー・パターンの挿入を短時間で実現可能。GLOBALFOUNDRIESが提供するデザインキットと組み合わせて使用すれば、手作業を挟むこと無く1回の処理でICフィル制約を満たすことができという。

Mentorの「SmartFill機能」は、TSMCの65nm以降の製造プロセスにも対応している。

2012.05.30

2012年5月29日、CAEソフト大手のANSYSは、モデル・ベース設計ソリューションを手掛ける仏Esterel Technologiesを現金5300万ドルで買収する事を発表した。

Esterel Technologiesはフランスのエランクールに本拠を置く従業員約80名の企業で、2011年の売上は約1500万ドル。同社のモデル・ベース設計ソリューション「Scade」ファミリ製品は、航空宇宙、防衛、鉄道、原子力発電所、産業システム分野向けの組込みソフト開発ツールで、各種安全規格に準じたソフト開発を包括的にサポートしている。

同社の歴史は古く、1980年代に開発されたプログラミング言語「Esterel」がルーツとなっており、企業としては1999年に設立され翌2000年に最初の商用製品がリリースされている。現在ビジネスの中心となっている製品「Scade」ファミリもフランスの地で1980年代から開発が進められてきた歴史あるツールで、様々な経緯を経て2001年からEsterel Technologiesが事業を展開。「Scade」エアバス社の航空機開発で採用されている事で有名。

ANSYSは、2008年に電磁界解析ツールを手掛ける米Ansoftを、2011年にパワー解析および最適化ツールのApacheを買収しているが、今回のEsterel Technologiesの買収に関しても、既存ソリューションの補完し更に同社のソリューションを拡張するものとしている。ちなみに同社が組込みソフト開発分野のソリューションを手に入れるのは今回が初となる。

2012.05.30

2012年5月29日、シーケンシャル・アナリシス技術でEDA製品を展開する米Calypto Design Systems社は、高位合成ツールの新製品「Catapult Low-Power」を発表した。

発表によると「Catapult Low-Power」は、高位合成ツール「Catapult C Synthesis」にCalyptoのコア技術の一つである消費電力解析および最適化技術をインテグレーションした新製品で、文字通り消費電力の最適化を踏まえた高位合成が可能。

「Catapult Low-Power」による消費電力の最適化は、アーキテクチャ・レベルとレジスタ・レベルの両方で行われるようで、まずアーキテクチャ・レベルで消費電力、性能、面積を見積り、そこからデザインをリファインメントして高位合成を実行。更に合成されたRTLに対して「PowerPro」で実現している「自動クロック・ゲーティング機能」を施し、消費電力を最適化する。

また、Calyptoは「Catapult Low-Power」と合わせて、RTLの消費電力解析を行う「PowerPro Power Analyzer (PA) 6.0」も発表。 同ツールはRTLにおける消費電力の見積もりをゲートレベルに対して15%の誤差内で行うことができるという。

尚、消費電力最適化をうたう高位合成ツールとしては、ドイツのChipVision社が「PowerOpt」という製品を提供していたが、同社は既に活動を停止している。

今回発表された「Catapult Low-Power」ならびに「PowerPro Power Analyzer (PA) 6.0」は、6/3よりサンフランシスコで開催される49th Design Automation Conferenceにて披露される予定。

2012.05.29

2012年5月18日、Cadenceはイノテックと共同で「C-to-Silicon Compilerセミナー」を開催した。

ここでは同セミナーで発表された、池上通信機株式会社のFPGA設計適用事例について紹介する。

■高位合成ツールを使ったFPGA用映像処理回路の開発例

池上通信機株式会社 開発本部 前里真一氏

前里氏の所属は放送機器向けの画像処理ハードウェアの開発が中心で、アルゴリズムの検討も含めてハードウェアを設計している。これまではASICを設計していたが、最近はFPGAの設計が中心ということで、今回の事例もタイトル通りFPGAをターゲットとしている。

今回前里氏のチームが高位合成ツールを用いて設計したのは、XilinxのVertex-6 2個をターゲットとする映像処理回路で、設計者7名、12ヶ月間で実施。元々、C言語は使わず仕様から直接RTLをコーディングするという設計スタイルで、設計チーム7名のうち6名がC/C++/SystemC、高位合成初心者だった。使用したツールはもちろんCadenceの「C-to-Silicon Compiler」である。

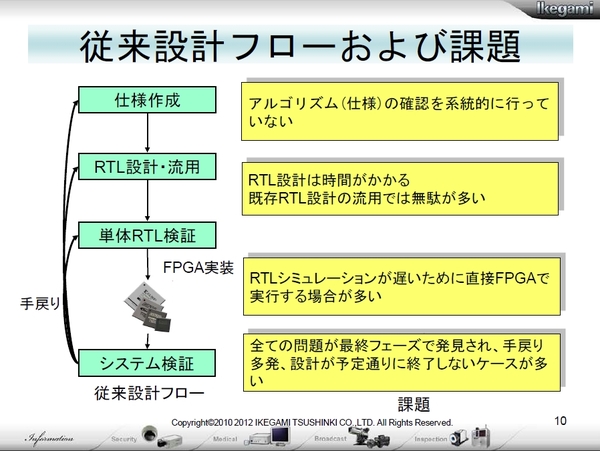

「C-to-Silicon Compiler」を利用するモチベーションは色々とあったが、一番大きかったのは、設計における手戻りの削減。全ての問題が最終的なシステム検証のフェーズで発見され、手戻り多発によってスケジュールに遅れが生じるという課題を何とかしたかったと前里氏。また、過去のRTL資産をそのまま最利用するという無駄も解消したかったという理由も頷けるものだった。

※画像は前里氏の講演スライド

高位合成ツールを導入したC言語ベースの設計フローを実践することにより、設計工数を既存のRTL設計よりも新規設計で半分、流用設計で1/10にする事を目標に掲げた前里氏のチームは、初心者でも効率良く高位合成ツールやSystemCを使えるように、幾つかの工夫を凝らした。

まず、「C-to-Silicon Compiler」の入力となるSystemCモデルの記述スタイルを統一し、記述をパターン化した。アルゴリズム本体記述は、C++のテンプレートクラスをフル活用し、処理はデータクラスに記述する事にして、SystemCの利用はハードウェア・モジュールおよびモジュール間の接続のみに限定した。また制御については構造体で引き渡す形をとった。これによりSystemCによるコーディングの敷居を下げ、効率的なコーディングを実現した。更に入出力端子名やモジュール間の配線名などにルールを設け、チームによる設計作業をスムーズに進めた。

更に「C-to-Silicon Compiler」による高位合成についてもパターン化し、全て内部ループ展開、クラスのメソッドをインライン化、メインループは「C-to-Silicon Compiler」に任せてパイプライン化、という方針で合成を行い、タイミングがメットしない時は合成設定の変更やソースコードの修正を行った。

これらパターン化した記述と合成により、アルゴリズムの検証および合成共に作業を簡略化でき、アルゴリズム検証の段階で機能不具合の95%を検出。合成後のRTLシミュレーションはSystemCのテストベンチを流用した。残りの5%の不具合は最終的な実機でのシステム全体検証で発見した。

デザインのうちSystemCおよび高位合成には向かない、入出力バッファ、DDRメモリ制御、PLL、クロックの切り替え回路については手書きでRTLを起こしたが、最終的にデザイン全体の97%はSystemC/C++から合成したRTLとなった。このRTLで周波数、スループット、面積、設計期間ともに目標を達成し、当初目標としていた早期仕様検討、手戻り削減、設計効率の向上を一通りクリア。高位合成した結果、実機に持って行って動かなかったモジュールは一切無かったという。

尚、前里氏は設計完了後にデザインの一部をASIC向けに合成。幾つかのパターンで試したところ、実デザインの倍の動作周波数300MHzの設定でも高位合成をし直すとタイミング・メットできた。合わせて消費電力も評価したところ、ASICの場合、FPGAよりも1/2-1/7と消費電力が少ない事を確認。同一のソースからターゲットを変えて回路を合成できる事から、高位合成を用いたCベース設計の再利用性の高さも確認できた。

※画像は前里氏の講演スライド

前里氏は最後に幾つかのツールへの改善要求を述べていたが、基本的に「C-to-Silicon Compiler」は使えるという結論でCadenceのサポートにも及第点をつけた。但し、高価なツールであるため、価格だけを見るとFPGA設計には不向きと付け加えた。

■C-to-Silicon Compiler最新のロードマップ

日本ケイデンスの朱氏によると、今年1月にリリースされた現行バージョン11.2.0は、大幅なバージョンアップにより数々の新機能が追加された。

例えば、コードを書き換える事無くコメンドで配列の分割やリストラクチャが可能な「配列のスプリット/リストラクチャ機能」、TLMベース設計で利用するインタフェースのソケット・ライブラリ「Flex Channel」、ゲート・ネットリストを直接生成する機能などが新たに追加された。また、既存の「シーケンシャル・クロック・ゲーティング機能」や、「リソース共有機能」、タイミングがメットするまでレイテンシを延ばしていく「リラックス・レイテンシ・スケジュール・モード」などが大きく機能改善された。

更に今月末(5/27予定)リリース予定のバージョン12.1では、タイミング・クロージャや、パイプラインのマルチ・ストール機能など幾つかの既存機能の改善が予定されているとの事。更にその先には2012年11月のバージョンアップも計画されており、方向性としては、SystemCにおけるUVM検証フローの確立、仮想環境「VSP」との接続、エミュレーター「Palladium」との統合などが予定されているという話であった。

■セミナー参加者へのアンケート結果

当日、日本ケイデンスAvi氏より、セミナー参加者に対して、事前に実施したアンケート結果(回答者数45名)が紹介された。興味深いと思えたポイントは以下の通り。

・SystemC設計・検証における課題は?

A:CとRTLの等価性検証(回答の50%超 ※複数回答あり)

A:記述スタイルの確立(回答の40%超 ※複数回答あり)

・C/C++/SystemCモデルに対してLintチェックを行なっていますか?

A:導入している(回答の約35%)

・高位合成の適用によって従来設計より設計の短縮期間は?

A:1/2-1/5(回答の52%)

A:1/5-1/10(回答の20%)

・今後高位合成技術が普及するために最も重要なポイントは?

A:設計者の意識改革(回答の32.5%)

A:ツールの改善(回答の30%)

・今後5年以内に高位合成技術が従来のRTL設計を取って代わると思いますか?

A:代わる(回答の32.5%)

A:代わらない(回答の32.5%)

A:分からない(回答の35%)

2012.05.29

2012年5月16日および24日、ESLソリューションを手掛ける米Carbon Design Systemsは、SoCのパフォーマンス解析のための仮想環境キット「Carbon Performance Analysis Kit (CPAK) 」を発表した。

発表によると「CPAK」は、SoCやSoCを構成するIPのパフォーマンス解析のための仮想環境キットで、Carbonの提供するESL環境「Carbon SoC Designer」上で利用する事が可能。短時間で仮想環境を立ち上げ、ソフトウェアを用いたハードウェアのパフォーマンス検証が可能な点が特徴と言える。

最初に発表された「ARM Cortex-Aシリーズ」向けの「CPAK」としては、ARM Cortex-A9、A15、A7向けの他に、Cortex-A15とCortex-A7で実現する「big.LITTLE」技術のサブシステム向けのキットが用意される。各キットにはプロセッサ・コア・モデルで構成される仮想ハードウェア環境と解析/デバッグ用のソフトがパッケージされている。

続けて発表されたCadence DDR3メモリ・コントローラ向けの「CPAK」は、ARM Cortex-A9 MPCoreモデルとCadenceの設計IP DDR3メモリ・コントローラ・モデル、EEMBCのベンチマーク・ソフトがパッケージされたキットで、「Databahn」の名で知られる旧Denali社のDDR3メモリ・コントローラ設計IPの性能評価に利用できる。

※EEMBC:Embedded Microprocessor Benchmark Consortium

いずれの「CPAK」もユーザーが独自にSystemCモデルを追加したり、CarbonのWebポータル「IP-Exchange」上で提供しているESLモデルや「Carbon Model Studio」でRTLから作成したESLモデルを追加するなどカスタマイズして利用する事も出来るという。

ARMとの強力なパートナーシップを持つCarbonの顧客は、大半がARMベースのSoC開発を行っており、中でもCadenceのDDR3メモリ・コントローラ設計IPを使う顧客が多いという事で、これらニーズに応えるすぐに使える仮想環境として「CPAK」が提供される事になったようだ。

2012.05.29

2012年5月18日、アナログ/ミックスドシグナル設計統合環境およびMEMS向け設計環境を手掛ける、Tanner Research社のEDA事業部Tanner EDAと論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、両社製品のインテグレーション・ソリューションを発表した。

発表によると両社は、アナログ/ミックスシグナル設計向けのソリューションとして、Tanner EDAの「T-Spice」とAldecの「Riviera-Pro」をインテグレーション。Tanner EDAが「HiPer Simulation A/MS」として製品の提供を開始した。

同製品はSPICEベースのアナログ・シミュレーションとデジタル・シミュレーションの両方に対応可能な統合環境で、デザインのアナログ部分とデジタル部分を自動的に認識し、アナログ-デジタル・ブロック間のインターフェースを容易に確認することが可能。複雑なアナログ/デジタル協調シミュレーションを効率化できるだけでなく、コスト・パフォーマンスも高いという。

2012.05.29

2012年5月24日、アナログ/ミックスドシグナル設計統合環境およびMEMS向け設計環境を手掛ける、Tanner Research社のEDA事業部Tanner EDAは、新製品「Tanner Analog FastSPICE」のリリースを発表した。

発表によると「Tanner Analog FastSPICE」は、Tanner EDAのアナログ/ミックスシグナル設計環境「HiPer Silicon」で利用できるアドオン・ツールで、その中身はBerkeley Design AutomationのSPICEシミュレーター「Analog FastSPICE」。「HiPer Silicon」にはTanner EDAオリジナルの「T-Spice」が用意されているが、「Analog FastSPICE」はそれを補う形で複雑なアナログ/RF回路のSPICE精度シミュレーションを実現する。Tanner EDAは、業界最速のSPICEシミュレーターとしてシェアを伸ばし続けている「Analog FastSPICE」を取り込むことにより、自社のアナログ/ミックスシグナル設計環境の更なる強化を狙う格好だ。

尚、「HiPer Silicon」のアドオン・ツール「Tanner Analog FastSPICE」は、トークン方式のライセンスで提供され、1トークン当たりのデザイン容量は5万素子で価格は年間3万ドルから。購入するトークン数に応じてトークン単価は安くなる。

2012.05.29

2012年5月23日、マルチCPU対応の論理シミュレーターを手掛けるAxiom Design Automationは、同社シミュレーターの新たなライセンス方式「WUL(Worldwide Unlimited Licensing)」を発表した。

発表によるとAxiomが世界初だとする「WUL(Worldwide Unlimited Licensing)」は、固定費用を支払えば無制限に製品を利用できるライセンス方式で、同ライセンスを利用すればAxiomのマルチCPU対応論理シミュレーター「MPSim」をワールドワイドで無制限に使用可能。「WUL」の費用は明らかにされていないが、売上5億ドル未満の企業の場合、その固定費用は100万ドル未満だという。

Axiomによると、既に同ライセンスを用いた「MPSim」による検証を経てテープアウトを終えた顧客が数社存在するとの事。Axiomは「WUL」というライセンス方式は、拡大する検証コストを抑え、大手企業でなくとも「シミュレーション・ファーム」を実現できると主張する。

2012.05.28

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2012.05.27

2012年5月25日、Mentor Graphicsは、2013会計年度第1四半期(2012年2月-4月)の売上を報告した。

発表によると、Mentorの2013会計年度Q1の売上は、前年比約7.8%増の約2億4790万ドルで、前年同時期は損益を計上していたが今期は2818万ドルの純利益を計上した。この結果は前Q4売上報告時点の予測を若干下回るものだった。これでMentorは8四半期連続で売上前年比増を達成した。(※GAAP基準による会計結果)

Mentorは2013会計年度の売上を11億ドル、次期2013会計年度Q2(12年5-7月)の売上を2億4000万ドルと予測している。

2012.05.24

2012年5月23日、Mentor Graphicsは、GLOBALFOUNDRIES、SMIC、TowerJazzの3社によるDFMツール「Calibre PERC」の採用事例を相次いで発表した。

「Calibre PERC」は、Mentorが2009年5月にリリースした、回路のトポロジカル・チェッキングを自動で行う業界唯一のツールで、「PERC」とは、Programmable Electrical Rule Checkerの略。

今回、GLOBALFOUNDRIESは、自社顧客の信頼性検証の向上に役立てるため、28nmバルクCMOSの設計実現化フローに「Calibre PERC」を導入。「Calibre PERC」により、ラッチアップ耐性の検証を自動化するだけでなく、一部の顧客はラッチアップの発生箇所の特定にも役立てているという。

SMICでは、ESD保護回路の設計メソドロジの一部に「Calibre PERC」を使用しており、これにより大規模SoCに対するチップレベルのESD保護回路を保証。また、顧客に対して「Calibre PERC」を用いた信頼性チェックのコンサルティング・サービスを提供しており、今後「Calibre PERCデザイン・キット」を顧客に提供する予定となっている。

TowerJazzもSMICと同じくESD保護回路やパワー・マネジメント回路のチェックに「Calibre PERC」を使用。顧客向けの信頼性チェック・ルールの策定に「Calibre PERC」を使用しており、作成された「Calibre PERCルールデック」は、今後顧客に提供される。

ESD保護回路などの回路構成は、半導体プロセスによって仕様が様々であるため、回路図が仕様を満たしているかどうかを自動チェックする術はこれまでなかった。

2012.05.24

2012年5月23日、Synopsysは、同社のCOO、Chi-Foon Chan氏が現CEOのAart de Geus氏と共に共同CEOになることを発表した。

発表によるとChi-Foon Chan氏は、これまで10年以上に渡りAart de Geus氏と共にSynopsysの経営に携わってきており、今後は両者同じ立場の共同CEOとして経営の指揮を執る。

Chi-Foon Chan氏は、元米国NECのマイクロ・プロセッサ・グループのゼネラル・マネージャー。1990年にアプリケーション及びサービス部門のバイス・プレジデントとしてSynopsysに入社。その後IPビジネスなど数々のビジネスを立ちあげ、1998年にプレジデント兼COOに就任。同社のボード・メンバーとなった。

今回発表の共同CEO体制は、Synopsysの今後の10年に向けた施策のようだ。

2012.05.24

2012年5月23日、Synopsysは、2012会計年度第2四半期(12年2月-4月)の売上を報告した。

発表によると、Synopsysの2012会計年度Q2の売上は、前年同時期比約10%増、前期12年Q1比約1.7%増の4億3260万ドル。この実績は前四半期売上報告時の予測を上回るもので、Q1で更新したばかりの四半期売上記録を更に塗り替えた。

今回発表した2012年Q2売上を含め、Synopsysは7四半期連続で売上前年増を達成。Q2の純利益は2100万ドルで前年同時期の4分の1程度だった。2011年Q2は税制上スポット的な利益を計上していたのに対し、2012年Q2はMagma買収に伴う経費を計上しており、最終的な純利益に差が出た。(※GAAP基準による会計結果)

Synopsysは、次期2012会計年度Q3(12年5-7月)の売上をQ2実績を上回る4億4000-4800万ドルと予測。2012会計年度通期の売上予測は、17億4000-6000万ドルとQ1に続いて上方修正した。

2012.05.17

2012年5月16日、Cadenceは、業界初となる「NVM Express 1.0」規格をサポートするIPサブシステムを発表した。

Cadenceの発表したIPサブシステムには、NVM Expressコントローラ、ファームウェア、NVM Expressの検証IPが統合されたもので、PCI Expressインターフェースから内部バス・ファブリックまでを対象とした検証およびテスト環境も備わっているとの事。同IPサブシステムを利用すればNVM Expressの容易なインプリメントを実現可能で、Cadenceは更に設計を加速させるソリューションとして、「Virtual System Platform」、「Incisive Software Extensions」およびフラッシュメモリ・モデルを活用した設計メソドロジを提供している。

「NVM Express 1.0」は、2011年3月に公開された次世代のストレージ・インターフェイス・プロトコルで、SSD(Solid State Drive)をPCI Expressインターフェイスに直接接続するための新規格。今年3月に「NVM Express 1.0」の検証IPをCadence,Synopsysの両社が相次いで発表したが、設計IPの発表は今回のCadenceの発表が業界初。

2012.05.17

2012年5月16日、Cadenceは、同社のシステム及びSoC検証ソリューションの拡張を発表した。

発表によるとCadenceは、同社のハードウェア/ソフトウェア協調開発プラットフォーム「System Development Suite」に、論理シミュレーター「Incisive」およびアクセラレーション/エミュレーション環境「Palladium XP」をベースとしたインサーキット・アクセラレーションの機能を追加。合わせてこれまでシミュレーション用途に限定されていた検証IP「Cadence Verification IP (VIP) Catalog」をアクセラレーション、エミュレーション向けにも利用可能な形に拡張した。

今回「System Development Suite」にインサーキット・アクセラレーション機能が加わった事により、共通の統合検証環境上でシミュレーション・アクセラレーションやエミュレーションを実行することが可能に。設計者はエミュレーション環境のパフォーマンスとシミュレーション環境の解析機能という双方の強みを享受できるようになり、システムレベル検証の生産性を大きく向上可能となった。更にアクセラレーション、エミュレーション向けに拡張された検証IP「Accelerated VIP」を利用すれば、大規模デザインの検証をより加速することができるという。

Cadenceは新しい「Accelerated VIP」のラインナップとして、下記インタフェース規格向けの検証IPを用意している。

-ARM AMBA AXI 3/4およびACE

-PCI Express 2.0/3.0

-USB 3.0

-10Gb Ethernet

-SATA 3

-HDMI 1.4

2012.05.16

2012年5月10日、新横浜のホテルでSpringSoft社のプライベート・セミナー「SpringSoft Community Conference 2012」が開催され、定員を大幅に上回る約100名の参加者を集めた。

ここでは、同セミナーで発表された「ProtoLink」の活用事例について紹介する。

「ProtoLink」とは、昨年5月にリリースされた、FPGAベース・プロトタイピング・ボードのデバッグ向けのハード及びソフトのツール・セットである。(

関連記事)

■ProtoLink活用による上流設計の加速化!!

Cedar-ESLによるアーキテクチャ設計ソリューションのご紹介

富士通セミコンダクター株式会社 開発本部 SoCソリューション統括部 第一設計技術部

プロジェクト課長 蓮實 直信(はすみ なおのぶ)氏

蓮實氏の講演は、同社の設計サービス「Cedar-ESL」において「ProtoLink」を活用してESL環境を構築した事例で、同環境のデモは昨年のET2011にて公開済み。(

関連記事)今回の講演では、「ProtoLink」を利用した背景と合わせて同社の考える理想的なESLフローについて語った。

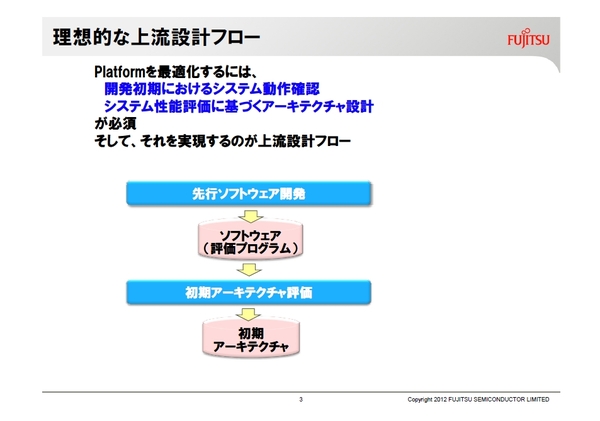

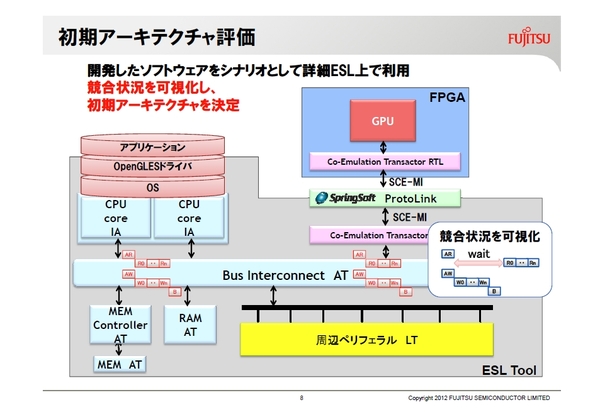

蓮實氏によると、同社では現在主流のIPベースのSoC設計に対して、ユーザー固有のロジック設計に注力してもらうべく、ユーザー・ロジックの開発に最適な仮想プラットフォームの提供に向けて様々な工夫を凝らしている。そのために、SoC初期アーキテクチャー評価用プログラム(ソフトウェア)の作成、次いでそれを用いた初期アーキテクチャー評価と2段階のステップを踏む必要があると考えており、それぞれの作業にはベースは同じだが内容構成の異なる2種類の仮想プラットフォームを使用している。2種類の仮想プラットフォームを使用するのは、シミュレーションの速度と精度という2つのニーズに対応するためであるが、そこに「ProtoLink」を使うのには訳がある。

※画像は富士通セミコンダクター蓮實氏の講演データ

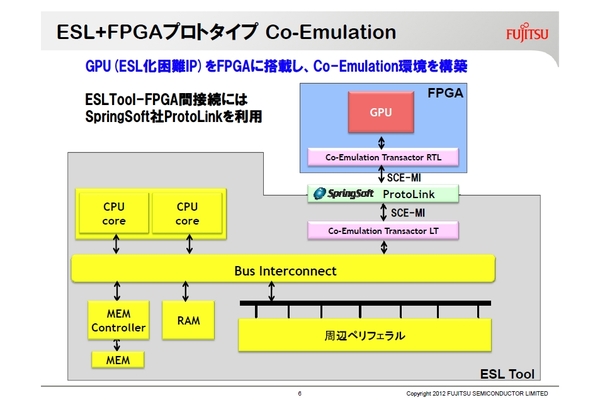

一般的にESLツールで実現される仮想プラットフォームは、ソフトウェアの先行開発やハードウェア・アーキテクチャの評価に向けて用意されるが、その環境構築は簡単に済むものではない。蓮實氏曰く「特にシステム性能を決定する重要なIPのESL化が困難」という事で、本来必要とされている設計の初期段階でフルシステムの仮想プラットフォームを用意することは非常に難しいという現実がある。そこで同社は、ESLモデルの作成が困難なIPをFPGAに搭載し、仮想プラットフォームとFPGAプロトタイプ・ボードとを接続する形を取る事にした。その接続に利用されるのが「ProtoLink」だ。

※画像は富士通セミコンダクター蓮實氏の講演データ

SpringSoftは、「ProtoLink」を用いたESL環境とFPGAプロトタイピング・ボードとの接続ソリューション「CoEmu Verification System」を提供しており、ESL環境側との接続に使うTransactor APIとFPGA側との接続に使うTransactor RTLを用意している。富士通セミでは、このソリューションを用いてS2C社製のFPGAプロトタイプ・ボードとMentor社ESLツール「Vista」ベースの仮想プラットフォームを接続。FPGAボード上にESLモデル化が困難なGPUをマッピングして、ソフトウェア先行開発用および初期アーキテクチャー評価用の2つの協調エミュレーション環境を構築した。

※画像は富士通セミコンダクター蓮實氏の講演データ

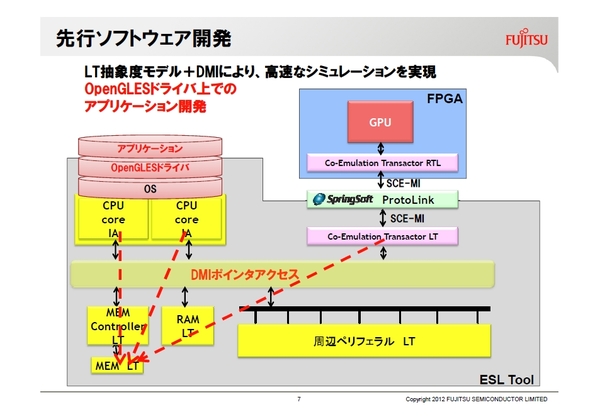

2つの環境の違いは、環境を構成する各種モデルの抽象度で、大きな違いはバスモデル。

ソフトウェア先行開発用の環境では、高抽象度化による高速なシミュレーションを実現すべく、バスはスキップするような形でDMIポインタ・アクセスを用いているのに対し、初期アーキテクチャー評価用の環境ではバスの競合状況を可視化すべく、TLM AT(Approximately-timed)モデルを用いた。両環境で接続に用いるトランザクタはSpringSoftと共同開発した。この2つの環境を用いることで、「まず動くソフト」を開発しGPUの振る舞いを明確化。そして、そのソフトを用いて初期アーキテクチャーの評価を行うという2段階の作業ステップを踏み、設計初期の仕様設計の段階でのプロトタイプ評価を実現した。

※画像は富士通セミコンダクター蓮實氏の講演データ

蓮實氏は、これら環境を使えば、ソフトおよびハードのモデル資産を用いた「モデルを動かしながらの開発」が可能となり、ハードとソフトの整合性のとれた効率的な開発が実現できるとし、更に高位合成ツールを用いればモデルの完成度に応じて開発を加速できるだろうと述べた。

尚、ソフトウェア先行開発と初期アーキテクチャー評価という2ステップの作業は、あくまでも詳細アーキテクチャー評価のための前段の作業で、同社では初期アーキテクチャー評価を完了した後に仮想プラットフォームのモデルを更に詳細化し、サイクル・アキュレートなモデルを用いた評価を経てハードウェア設計を開始しているということ。この評価においてはソフトウェアを用いず擬似モデルで動きを再現しているという。

蓮實氏は講演の中で同社の「Cedar-ESL」で「ProtoLink」を採用した理由を以下のように紹介していた。

【「ProtoLink」の採用理由】

・高速高機能である

・AXI/AHBなどの高速トランザクタをサポートしており、かつリクエストにも対応してくれる

・FPGAボードを選ばない(これが一番大きい)、ESL環境もSCE-MIインタフェースで何にでも繋がる

・Full Visibility機能でFPGA側のバグ解析が可能

・ソフト開発者向けにも提供可能な低価格

・SpringSoftのEDAベンダとしての信頼性、スキルのあるエンジニアによるサポート体制(これも大きい)

2012.05.16

発表によるとAMDは、同社のSoCやIPコアの検証用にSynopsysの検証IPソリューション「Discovery VIP」を選定。USB 3.0、ARM AMBA AXIインターコネクト、SATA 3.0、PCI Express Gen 3、MIPIなどの各種検証IPや、SoC上のプロトコル・トラフィックのデバッグ環境を提供する「Protocol Analyzer」の使用権を含めてSynopsysと複数年のライセンス契約を結んだという。

2012.05.16

2012年5月15日、ハードウェアベースの検証ソリューションを手掛ける仏EVE社は、同社のエミュレーション・システム「ZeBu」を用いた富士通マイクロソリューションズの顧客事例を発表した。

発表によると富士通マイクロソリューションズは、高位合成ツールを用いたCモデルベースの高位設計フローにEVEのエミュレーション・システム「ZeBu」と「ZEMI-3」コンパイラを適用し、トランザクション・ベースのエミュレーションを実現。アルゴリズムのCモデル検証から高位合成を経て合成したRTLのエミュレーション検証を行う一貫したフローを構築した。実際に同フローを無線回路の設計に適用したところ、既存の論理検証手法と比較して最大1300倍の高速化効果があったという。

2012.05.16

2012年5月15日、SystemCからの高位合成ツールを手掛けるForte Design Systemsは、同社の「Cynthesizer」をHighIP Design社が導入したことを発表した。

HighIP Designは2010年設立のIPベンダで、バーチャル・プロトタイプやSoCを実設計で利用可能なSystemCモデルおよびSystemCから合成したVerilogのRTLをIPとして提供している。

発表によるとHighIP Designは、同社初の製品となるUSB 2.0デバイス・コントローラのIPを開発するにあたり、Forteの高位合成ツール「Cynthesizer」を導入。実装用のRTLのIPは「Cynthesizer」を用いて合成している。

尚、ForteとHighIP Designとのライセンス契約には、ForteによるHighIP DesignのIP製品の再販も含まれており、ForteはUSB 2.0デバイス・コントローラのIPを顧客に提供。年内にはUSB 3.0のIPもラインナップされる予定となっている。

2012.05.10

2012年5月8日、Synopsysは、フォトニクス分野の設計およびシミュレーション・ツールを手掛ける米RSoft Design Groupの買収を発表した。

SynopsysによるとRSoft Design Groupの買収は既に完了済。その条件等は明らかにしていない。Synopsysは2010年にOptical Research Associates社を買収し光学市場への参入を果たしており、今回の買収については光導波路のモデリングなど光学市場での展開を広げ、自社既存のTCAD「Sentaurus」のポートフォリオを補うものだとしている。

RSoft Design Groupの提供するツールは、光導波路や光ファイバのシミュレーション、フォトニック部品の設計、LED物理構造の設計、半導体レーザのデバイス・モデリング、光伝送システムの特性解析など、フォトニクス分野の様々な用途に対応している。

2012.05.10

2012年5月9日、ハードウェアベースの検証ソリューションを手掛ける仏EVE社は、同社の製品を用いてTexas Instrumentsが組込みソフト開発を加速させた事例を発表した。

発表によるとTIは、ARMのデュアル・コアCortex-A15 MPを搭載した同社最新のモバイル・プロセッサ「OMAP5430」の組込みソフトウェア開発に、EVEのエミュレーション環境「ZeBu-Server」を使用。「OMAP5430」を「ZeBu-Server」にマッピングし、その上でAndroid OSを立ち上げ開発に利用した。マッピング作業は競合製品の30倍の速さとなる約7分で完了。「OMAP5430」の最初のエンジニアリング ・サンプルが出た2週間後には既に「ZeBu-Server」上でAndroid OSが動いていたという。

TIは「ZeBu-Server」を利用することで「OMAP5430」の組込みソフトウェア開発を6-9ヶ月短縮。そのおかげで今年1月の家電見本市CESで「OMAP5430」のデモを披露できたという事だ。

2012.05.09

2012年5月9日、Cadenceは、同社のチップ見積り環境「Chip Planning System」を富士通セミコンダクターが採用した事を発表した。

発表によると富士通セミコンダクターは世界9ヶ所のデザイン・センターにて共通のインフラとしてCadenceのチップ見積り環境「Chip Planning System」を標準採用。同ツール環境の採用はMCUチップの開発に利用するためで、既に利用していた同ツール環境を今回更に世界的な拠点での利用に拡張したようだ。

Cadenceの「Chip Planning System」は、チップ開発前のアーキテクチャ仕様決定に向けて利用するツールで、搭載するIPの情報や使用するプロセスの情報など各種パラメータを基にチップサイズ、消費電力、タイミングなどを見積る事ができるほか、チップの価格を予測する事も可能。

富士通セミコンダクターは、「Chip Planning System」の技術をベースに自社のASIC顧客向けにウェブ・ベースのチップ見積りソリューション「GA-Estimator」を開発しており、同技術に対する信頼度は非常に高い。

2012.05.09

2012年5月3日、マスクデータの最適化ツールおよびDFMツールを手掛ける、米Sagantecは、オランダのNP-Komplete Technologiesを買収したことを発表した。

NP-Komplete Technologiesは、2次元ダイナミック・コンパクション技術をベースとした、フィジカル・デザインのコンパクション及びマイグレーション・ソリューションを手掛けるスタート・アップで、米Takumi Technologyの開発パートナーとして同社DFMツールの開発を行なっていた。

今回の買収によりNP-Komplete TechnologiesはSaganticの子会社となり、NP-Komplete TechnologiesのチームはSagantecのオランダのエンジニアリング・チームに加わり、既存のDFMソリューションの提供と開発を継続する。

DRCクリーンな結果をもたらすNP-Komplete Technologiesの高度な2次元ダイナミック・コンパクション技術は、複数の大手半導体ベンダで認められており、先端ファウンドリの28nmおよび20nmプロセスで使われた実績があるという。