NEWS

2012.10.19

2012年10月17日、Xilinxは2013会計年度第2四半期(2012年7-9月)の売上を報告した。

Xilinxの2013年Q2(12年7-9月)の売上は、前年同時期比2%減、前期比7%減の5億4390万ドル。営業利益は前年比4%減、前期比10%減の1億4810万ドルという結果だった。これで売上前年割れは5四半期連続。2012年Q4、2013年Q1と2四半期連続で前四半期を上回る業績を残していたが、今期は売上も営業利益も前Q1を下回った。

地域別売上では最大市場のアジアが前年比14%増だったが前期に対しては4%減だった。分野別の売上構成では、売上最大のコミュニケーションおよびデータ・センター分野が唯一前年比、前期比ともに増。売上全体に占める割合を49%に伸ばした。製品別売上では、Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6で構成される新製品カテゴリが好調を維持しており、売上全体に占める割合を前期の17%から20%に伸ばした。

Xilinxは次期2013年Q3(12年10-12月)の売上を今期の1%から5%減になると予測している。

尚、XilinxはこのQ2にて、バックホール向けモデムIPを手掛けるエストニアのModesat Communications社と組込みLinuxを手掛ける米PetaLogix社の2社を買収している。

2012.10.17

2012年10月16日、カリフォルニア州サンノゼにてファンドリ最大手TSMCのイベント「TSMC Open Innovation Platform (OIP) Ecosystem Forum」が開催された。

同イベントの開催に合わせ、TSMCは先日10月9日に、20nmおよびCoWoS (Chip on Wafer on Substrate)、新たな2つのリファレンス・フローの完成を発表。(関連記事)EDA各社はTSMCの新たなリファレンス・フローに含まれる自社製品を相次いで発表した。

現時点で公表されているTSMC新リファレンス・フローのサポート・ツールは以下の通り。

尚、関連するニュースとして、MentorはTSMCのリファレンス・フロー構築に伴い、TSMCより "Partner of the Year 2012"アワードを受賞。"Joint Delivery of the 20nm Reference Flow"および"CoWoS Design Enablement and Test Vehicle Development,"2つのカテゴリにて同賞を受賞したという。プレスリリース文

またTSMCは、Wide I/O mobile DRAM interfaceを用いた3D-ICのテスト・ビークルをテープ・アウトしたことを発表しているが、同テスト・ビークルの設計においては、CadenceおよびMentorのEDAツールのほかに、CadenceのWide I/Oメモリ・コントローラIPとPHY IPが利用されたという。プレスリリース文

2012.10.12

2012年10月10日、ARMは新しいシステムIPとして、キャッシュ・コヒーレント・インターコネクト「CoreLink CCN-504」を発表した。

発表によると「CoreLink CCN-504」は、ARM最新のCortex-A15や次世代の64ビット・プロセッサを用いる、ネットワーク・インフラやサーバーなどのメニーコア・ソリューションに対応するための新たなインターコネクトIPで、帯域幅は最大1Tbps、既存の「CoreLink CCI-400」の倍にあたる最大4クラスタ計16個のプロセサ・コアをサポートする。「CoreLink CCN-504」を用いることで、システム内の各プロセッサが他のプロセッサのキャッシュにアクセスできるようになり、ヘテロジニアス・マルチコアおよびマルチ・クラスタCPU/GPUシステムにおけるシステム・コヒーレンシを実現する。

またARMは「CoreLink CCN-504」と合わせて「CoreLink CCN-504」向けに最適化したダイナミック・メモリ・コントローラ「CoreLink DMC-520」を発表。いずれの製品もサンプル出荷は2013年の予定で先行顧客であるLSI社とCalxeda社には既に提供されている。

2012.10.11

2012年10月10日、コンフィギュラブルなデータプレーン・プロセッサを手掛けるTensilicaは、同社のライセンシーによるTensilicaのIPコアの累計出荷数が20億個を超えたと発表した。

Tensilicaによると、現在同社のIPコアの出荷数は年間8億個ペースで、出荷累計が10億個に到達した2011年6月時点よりも50%増えたという。

当然ながら出荷数の増加と共に売上も伸ばしており、それら売上は将来のロイヤリティ収入に繋がる予定。Tensilicaのコアは、オーディオ以外にベースバンド・モデムや次世代の4G LTE/LTE-A向けにも利用され市場をリードしているという。

2012.10.11

2012年10月10日、オープンなPDKの普及推進団体「IPL Alliance」は、トランジスタレベルの統計的ばらつき解析ソリューションを手掛けるカナダのSolido Design Automationが同団体に加盟した事を発表した。

「IPL(Interoperable PDK Library)Alliance」は、ツール環境に依存しないオープンなPDK仕様「IPL1.0/2.0」の標準化および普及推進団体で、今回加盟したSolido Design Automationも含めて現在31社が加盟している。

今回、Solido Design Automationは「IPL Alliance」への加盟により、自社のソリューションにおいてIPLの「Interoperable Analog Design Constraint Standard 1.1.」をサポートしていく計画。「IPL Alliance」はTSMCのイニシアティブによって発足した組織であり、TSMCと関係の深いSolido Design Automationが同組織に加盟するのは自然な流れに見える。

2012.10.11

2012年10月5日、シーケンシャル・アナリシス技術でEDA製品を展開する米Calypto Design Systemsは、韓国のファブレスCore Logicが同社の消費電力最適化ツール「PowerPro CG」を採用した事を発表した。

Core Logicは、自動車、ホーム・エレクトロニクス、マルチメディア、カメラ、モバイルなど、幅広い分野に向けて各種プロセッサー、画像処理チップなどを展開する韓国有数のファブレス・ベンダ。同社は、Calyptoの消費電力最適化ツール「PowerPro CG」を使用することで、消費電力の最適化だけでなくプロジェクト時間を30%短縮することが出来たとして、同ツールを採用。設計期間と消費電力を合わせて削減出来る唯一のツールとして高く評価した。

「PowerPro CG」はRTLレベルの消費電力最適化ツールで、RTLを読み込みクロック・ゲーティング可能な箇所を見つけ論理回路を自動挿入したり、RTLコード中の既存のクロック・ゲーティングを認識しそれらをより効率化する事が可能。これら作業は全自動またはガイドに沿ったマニュアル作業で処理できる。

2012.10.11

2012年10月2日、マルチCPU対応の論理シミュレーターを手掛けるAxiom Design Automationは、米ファブレスBlueRISCによる同社製品の採用事例を発表した。

BlueRISCはハードウェア・ベースの防衛向けのセキュリティ・ソリューションを手掛けるベンチャーで、独自にセキュリティ・プロセッサを開発している。

発表によるとBlueRISCは、自社開発のプロセッサ「CaptureGUARD」および「TrustGUARD」を含む全てのデザインでAxiomのシミュレーター「MPSim」を使用。同社は数年前まではSynopsysの「VCS」を利用していたが、その高度なデバッグ機能を含む総合的なバリューからAxiomのシミュレーター「MPSim」に乗り換え。その能力に満足しており今後のデザイン・プロジェクトでも引き続き「MPSim」を利用する予定だという。

Axiomは同社の製品を利用すれば、デザインの生産性のみならず検証コストも削減可能と主張しており、今年の49回DACでは固定費用でライセンスを無制限に利用できる新ライセンス「WUL(Worldwide Unlimited Licensing)」を大きくアピール。既に費用100万ドルで1500本近いシミュレーターを利用している大手顧客も存在していると聞いた。ちなみに同社の日本代理店は存在していない。

※写真は49DACでのAxiomのブース

2012.10.11

2012年10月10日、CadenceはSTMicroelectronicsによる同社製品の採用事例を発表した。

発表によるとSTMicroelectronicsは、CadenceのRTL-to-GDSIIフローの採用に伴い、サインオフ・ツールについても既存の他社ツールからCadenceのツールに乗り換え、28nmプロセスを用いたSoCの設計期間を数週間短縮することに成功した。

具体的には、タイミング解析ツールとして「Cadence Encounter Timing System」を寄生抽出ツールとして「Cadence QRC Extraction」を導入した。これらツールをインプリメント・ツール「Encounter Digital Implementation System」と併用することで、設計期間の短縮だけでなくより優れたQoRと生産性を達成できたという。

STMicroelectronicsの担当者は以下の様なコメントを発表に寄せている。

「ケイデンスのサインオフ・ソリューションは、我々の開発スケジュールを数週間も短縮しました。たとえば、以前使用していたサインオフ・テクノロジでは数週間かかっていた作業を、我々は2000万個以上のセルを含む設計において、24時間以内に60以上のモードとコーナーの組み合わせを持つ数千件のホールド違反を修正することができました。」

2012.10.11

2012年10月10日、Cadenceは新製品となるデバッガー「Incisive Debug Analyzer」を発表した。

Cadenceの発表によると「Incisive Debug Analyzer」の主なスペックは以下の通り。

・ハードウェア検証言語とハードウェア記述言語の両方をサポート

・前後両方向へステップ実行によるデバッグが可能

・ソースコードライン実行時や変数値の変更時に対応した直接クリック移動

・スマート・フィルタリング機能

・メッセージのクリック機能を備えたインタラクティブな統合ログファイル解析機能

「Incisive Debug Analyzer」は、2012年末にリリースされる予定で、既存のIncisiveデバッグ・フローにシームレスに統合。既存のデバッガー「SimVision」の機能をフルに活用しているという。

2012.10.10

2012年10月9日、アナログ設計の技術コンサルティングを手掛ける株式会社モーデックは、株式会社エム・イー・エルが開発したPCB向け超高速電磁界シミュレーター「S-NAP PCB Suite」の発売を発表した。※訂正あり

「S-NAP PCB Suite」は、多大な処理時間を要する従来の電磁界シミュレーターの課題を克服するエム・イー・エル独自開発の電磁界シミュレーターで、Windows上でプリント基板全体の電磁界シミュレーションを超高速で実現。他社製品で5日間を要する処理を約30分程度で完了することができる。

この「S-NAP PCB Suite」の高速処理は、パターン解析と実装素子解析の解析エンジンを分割し、パターン解析の結果をパラメータとして保存し、そのデータを使用して素子特性の解析を行うというアプローチによるもので、更に同シミュレーターはプリント基板を3次元的に分割した階層構造として解析することが可能だという。

尚、「S-NAP PCB Suite」の価格は公表されていないが、安価な環境であるとの事。製品は代理店である株式会社モーデックを通じて販売される。

2012.10.10

2012年10月9日、TSMCは20nmおよびCoWoS (Chip on Wafer on Substrate)、2つのデザインフローの完成を発表した。

発表された新しい20nmリファレンス・フローとCoWoSリファレンス・フローは、いずれもTSMCのパートナー・エコシステム「Open Innovation Platform(OIP)」によってサポートされるもので、20nmリファレンス・フローは、ダブル・パターニングを考慮した設計を実現。TSMCとエコシステムのパートナーが提供する20nm IPはダブル・パターニングに対応しており、TSMCの20nmプロセスの採用を促進する。

CoWoSリファレンス・フローは、マルチ・ダイの3D IC設計を実現するもので、既存のメソドロジの変更を最小限に抑えスムーズな3D ICへの移行を可能とする。このフローには、バンプ、パッド、インターコネクトの配置配線管理や、ダイ間の高速インターコネクトのシグナル・インティグリティ解析、サーマル解析、ダイ・レベルおよびスタッキング・レベルでの3Dテスト・メソドロジなどが含まれている。

TSMCはこれらリファレンス・フローと合わせて、20nmカスタム・デザインでのデブル・パターニングを実現するCustom Design Reference Flow、新たな高周波設計ガイドラインを提供するRF Reference Design Kitも用意している。

2012.10.05

2012年10月4日、Synopsysは、エミュレーター製品を手掛ける仏EVE社を買収した事を発表した。

Synopsysは買収額など今回のEVE買収に関する詳細を明らかにしていないが、非上場企業であるEVEの買収手続きは既に完了しており、買収されたEVEは同社のCEOであったLuc Burgun氏をリーダーにSynopsysの検証ビジネス部門の一部になるようだ。

SynopsysがEVEを買収するという話は噂レベルでは数年前からささやかれていたが、今年のDAC以降からその噂はより具体的なものとなり、つい先日、Synopsysがサンノゼの地方裁判所に提出した書類によってEVEの買収が判明し世間を騒がしていた。

Synopsysは60社を超える数々の企業買収により、EDAソリューションの拡張を続けてきていたが、フルカスタム・レイアウト・ツール、エミュレーター、PCB設計ツールについては、最大の競合Cadenceに有ってSynopsysに無いソリューションとして長年その穴を埋めれずにいた。しかし、今年8月にSpringSoftの買収を発表。SpringSoftの買収が完了すれば、フルカスタム・レイアウト・ツール「Laker」が手に入る予定で、今回のEVE買収により、これまで持ちあわせていなかったエミュレータ製品も入手。残るはPCB設計ツールだけとなる。

EVEはここ数年急拡大している半導体大手の検証ニーズを捉え業績を伸ばしており、検証分野では大手3社に続く業界4位、売上規模は年間6000万ドル相当と推測されていた。EVEの製品は半導体大手のほぼ全てで利用されており、中でも最大の顧客はIntelで売上の30%以上を占めていたという話もある。日本国内でも数多くのEVEユーザーが存在しており、そのためMentorがEVEを訴えた特許侵害の裁判は日本でも行われていた。

尚、少々古い話になるが、現在はXilinxのFPGAベースのエミュレーター製品にフォーカスしているEVEだが、同社は2007年にハードウェア・アクセラレータ「Hammer」シリーズを手掛けていた米Tharas社を買収しており、専用プロセッサを用いた「高速コンパイル」、「全ノード観測」を特徴とするアクセラレーション技術も保有していた。

2012.10.03

2012年10月2日、米SIA(Semiconductor Industry Association)は、2012年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年8月の世界半導体売上は前年同時期比約3.2%減、前月比約0.1%増の243億ドルという統計結果となった。これで世界半導体売上の前年割れは15ヶ月連続。今年1月からの売上累計は、1894億6000万ドルで昨年同時期の累計額と比較すると4.6%減となっている。年初の時点の各業界機関の予測では、2012年は前年比数パーセントの成長が見込まれていたが、このまま行くと前年割れの可能性が濃くなってきた。

2012年8月の売上を地域別でみると、北米と欧州市場の落ち込みが大きく、日本とアジアは比較的健闘している。日本市場は前月比、前年比、3ヶ月の移動平均ともに、伸び率は最も良かった。

2012.10.03

9/28に開催した検証セミナー「Verify2012」の講演資料のダウンロードを開始致しました。

ご希望の方は下記ページにアクセスして下さい。

Verify2012 運営事務局

2012.10.03

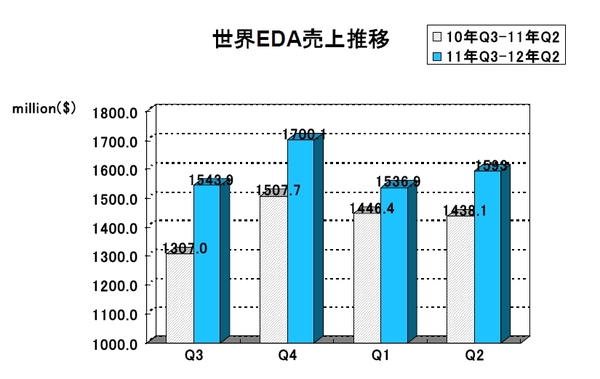

2012年10月2日、米EDA Consortiumは、2012年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

EDACの発表によると、2012年Q2(4月-6月)の世界のEDA売上総額は、前年比10.8%増、前Q1比3.2%増の15億9300万ドルだった。これで10四半期連続で売上前年比増を達成した。

2012年Q2の売上を分野別に見ると、PCB/MCM、サービス分野が前年割れだったのに対し、CAE、IC Physical Design & Verification、IPの3分野は前四半期に続いて前年比2ケタ増を記録した。

2012年Q2の売上を地域別に見ると、全ての地域で前年比増を記録。中でもアジアその他地域が前年比17.5%増と大きく売上を伸ばした。日本市場は2四半期連続で前年割れを記録していたが、今四半期は前年比1.8%増とかろうじて売上を積み上げた。

2012年Q2時点でのEDA業界の従業員数は28205人で、前期Q1比1.3%増となっている。

2012年Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億1840万ドル 12.5%Up

■IC Physical Design & Verification分野 3億2790万ドル 14.3%Up

■IP分野 4億2050万ドル 14.4%Up

■サービス分野 8510万ドル 4.1%Down

■PCB/MCM分野 1億4100万ドル 2.7%Down

2012年Q2地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億720万ドル 13.0%Up

■ヨーロッパ 2億6120万ドル 6.0%Up

■日本 2億5860万ドル 1.8%Up

■アジアその他地域 3億6600万ドル 17.5%Up

2012.09.26

2012年9月24日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のFPGA設計向けのシミュレータ「Active-HDL」のバージョンアップを発表した。

発表によると「Active-HDL」最新のバージョン9.2には、新機能としてファイル管理機能が搭載され、大規模なFPGA設計プロジェクトが容易に管理できるようになった。例えば、FPGA合成・配置配線ツールと互換性があるプロジェクト構造を作り、複数メーカーのツールで同一のプロジェクト構造を共有できるようになる。また、このファイル管理機能にはチームベースの設計機能もあり、複数拠点でのチーム作業においても設計環境を素早く構築できるという。

更に今回のバージョンアップではネット最適化機能も搭載され、ブロックダイアグラム・エディタを用いたネットの自動配線や冗長なネットセグメントの削除も可能となった。また、操作面ではマウスジェスチャーが導入され、よく使用するタスクを簡単なマウス動作で実行できるようになった。

「Active-HDL」に対するこれら複数の機能追加・強化は、先ごろ同社が発表したばかりのASICプロトタイピング・ボード「HES-7」を利用する上でも有用なものとなるだろう。

2012.09.26

2012年9月24日、Synopsysは、新たな設計IP製品としてJEDEC UFS v1.1仕様準拠の「UFSコントローラIP」と、MIPI UniPro v.1.41仕様準拠の「UniProコントローラIP」のリリースを発表した。

今回Synopsysがリリースした2種類のコントローラIPは、Synopsysの提供する6種のチップ間接続プロトコル仕様に対応する「マルチギアMIPI M-PHY IP」と組み合わせて利用する事で、それぞれ「MIPI Alliance UniPro規格」と「JEDEC UFSインターフェイス規格」の実装工数を削減できるという。

「UFSコントローラIP」と「UniProコントローラIP」はいずれも出荷が開始されている。

※画像はSynopsys提供のデータ

2012.09.21

2012年9月19日、Synopsysは、日立製作所のストレージ・ソリューション部門が、同社の検証IP「Discovery VIP」を採用したことを発表した。

発表によると日立製作所のストレージ・ソリューション部門は、同社の仮想化ストレージ・プラットフォームに使用しているSoCの検証にSynopsysのARM AMBA AXI3プロトコル向け検証IPを採用した。

Synopsysは検証IPのアーキテクチャーを刷新し、今年から100% SystemVerilogでコーディングされた高速かつ適用範囲の広い「VIPERアーキテクチャ」の検証IPを提供している。既存の検証IPの全てがVIPERアーキテクチャーに置き換えられているかどうかは定かではないが、USB 3.0、ARM AMBA AXI3、AXI4、ACE、HDMI、MIPI、Ethernet 40G/100G、PCI Express、SATAといったメジャーな規格の検証IPは、VIPERアーキテクチャー化されており、これら検証IPはSystemVerilogベースの検証メソドロジUVM、VMM、OVMの全てで利用することが可能。最大で従来比4倍相当の検証の高速化を実現できる。

また、Synopsysは「VIPERアーキテクチャ」の検証IPと合わせて「Discovery VIP」用のデバッグ環境「Protocol Analyzer」を提供しており、このツールを使えばプロトコル・トラフィックをトランザクション・ベースでGUI上でデバッグする事が可能となる。

2012.09.21

2012年9月14日、フォーマル検証を中心とした検証ツールを手掛ける米Real Intent社は、同社が2012 Best of Sunnyvale Awardを受賞したことを発表した。

Best of Sunnyvale Awardは、毎年サニーベール市の優れた地元企業に贈られるアワードで、U.S. Commerce Associationが主催している。

今回、Real Intentは、2012 Best of Sunnyvale Awardの「Computer Software category」にて受賞した。

Real Intentは、フォーマル検証技術を用いた「Ascent」および「Meridian」の2つの製品ファミリで検証ニーズに応えており、ビジネスも順調の様子だ。

2012.09.21

2012年9月13日、Mentor Graphicsは、同社の提供するリソグラフィ・チェック・ツール「Calibre LFD」がTSMC20nmプロセスで認証されたことを発表した。

「Calibre LFD」は、プロセスの変動をとらえてレイアウトの確実性を高めるリソグラフィ・チェック・ツールで、設計の早期段階でリソグラフィ変動の影響を予測しホットスポットを特定する事が可能。プロセス変動の影響を受けにくい設計を実現出来る。

「Calibre LFD」は、TSMCの28nmプロセスでも認証されているほか、Samsung、GlobalFoundriesの20nmプロセスにおいてもリファレンス・ツールとして認証されている。

2012.09.21

2012年9月11日、Mentor Graphicsは、同社の提供するオープンソース・ライブラリ「UVM Connect」の拡張を発表した。

「UVM Connect」は、Mentorが運営する検証関連のWebサイト「Verification Academy」で無償配布しているUVM準拠のオープンソース・ライブラリで、検証メソドロジUVMのユーザーに向けてSystemCモデルとSystemVerilogモデルのTLM接続を実現するもの。

※画像は「UVM Connect」の説明画像。Mentor社Webサイトより抜粋。

発表によるとMentorはこの「UVM Connect」を拡張し、UVM、SystemCに加えて検証メソドロジOVMもサポート。これによりOVMユーザーは「UVM Connect」を用いることで、SystemCで記述されたモデルとOVM SystemVerilogで記述されたモデルをTLMで接続できるようになる。

OVMはUVMの前身と呼べる検証メソドロジで、MentorとCadenceが共同開発したもの。統合的な検証メソドロジUVMが登場した事によりOVMユーザーのUVMのへの移行も進んでいるようだが、依然OVMを利用し続けるユーザーも存在しており、それらユーザーに対するサポートとして今回Mentorは「UVM Connect」の拡張を実施した。

Mentorは、オープンソース・ライブラリ「UVM Connect」と合わせてUVM導入支援のためのパッケージ「UVM Express」も提供しており、いずれもWebサイト「Verification Academy」で無償で入手できる。

2012.09.18

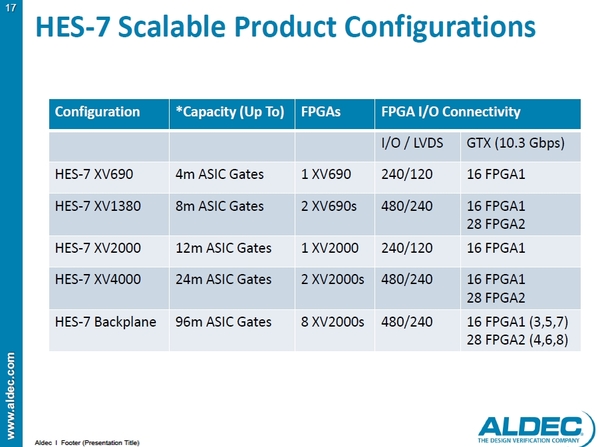

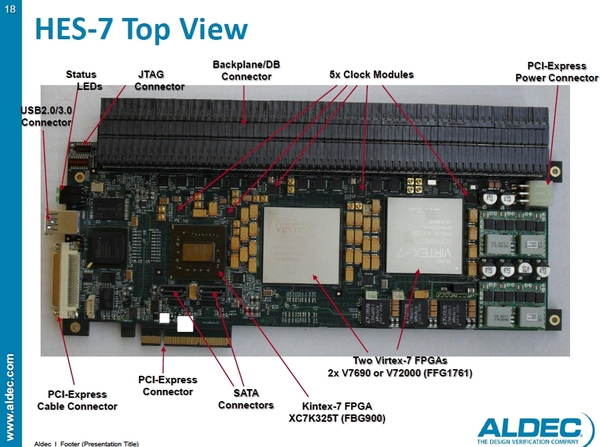

2012年9月17日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、新製品「HES-7」を発表しASICプロトタイピング市場への参入を表明した。

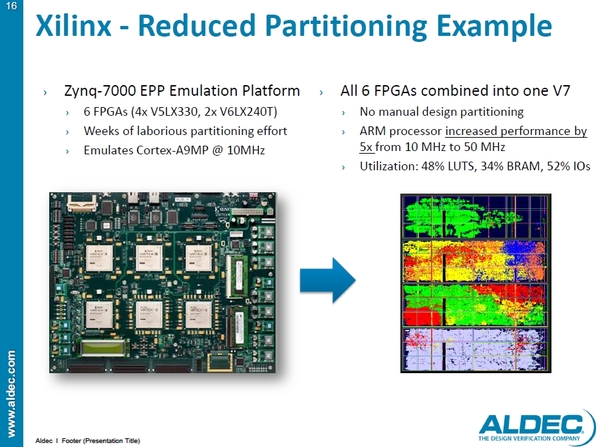

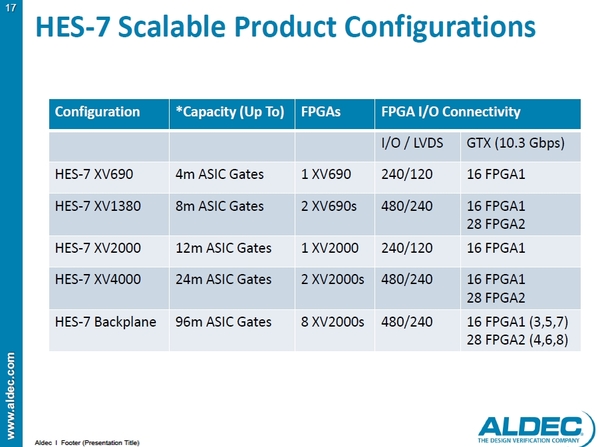

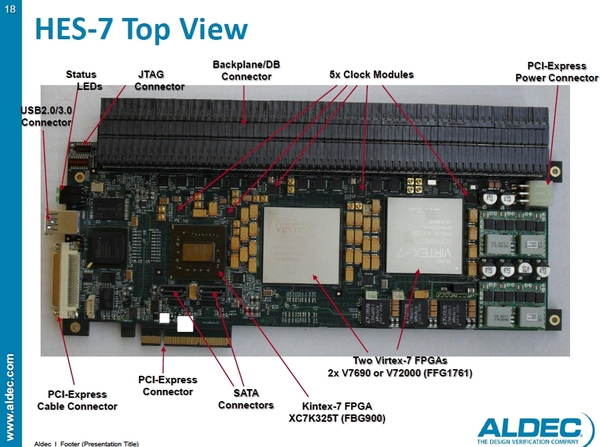

Aldecの新製品「HES-7」は、Xilinxの28nmFPGA「Virtex-7」を搭載するASICプロトタイピング用のFPGAボードで、製品のラインナップは「Virtex-7 690T」を1個または2個搭載するタイプと、Xilinx最大規模の「Virtex-7 2000T」を1個または2個搭載するタイプで計4種類。「Virtex-7 2000T」を2個搭載するタイプは最大400万FPGAロジックセル(実質2400万ASICゲート相当)のデザイン容量を誇り、更に同ボードを4枚繋げて9600万ASICゲートまで対応できる。

「HES-7」へのデザインのインプリメンテーションは、Xilinxの環境「ISE」または「Vivado」を利用し、特に「HES-7」専用の環境を必要としない。また、デバッグ環境も同様でDesignerはXilinxの「ChipScope」を使ってデザインのデバッグを行う形となる。

AldecのVice PresidentであるDavid Rinehart氏によると、「HES-7」は高価なASICプロトタイピング製品をより低価格かつ身近なものにするというコンセプトで開発された製品で、運用面でもシンプルに顧客のユーザビリティを追求。例えば、「HES-7」のインタフェースとして独自仕様ではない高速バックプレーンコネクタ「Molex」を採用しており、これにより顧客はカスタム・ドーターボード等による拡張が容易に可能。Aldecはそのパフォーマンスと供給体制から「Molex」を採用しており、公開されている「Molex」の仕様は誰でもアクセスできる。

※画像はAldecの提供資料

そして何よりもDavid Rinehart氏が強調するのは、「HES-7」を使えばデザインのパーティショニングを無くし、デザインの実装時間短縮とパフォーマンス向上の両方を実現できるという点。現在、市販されている一般的なプロトタイピング・ボードには、通常4?6個の旧世代FPGAが搭載されているが、そこにデザインを実装しようとすると当然ながらデザインの分割作業が必要となる。通常、そのような分割作業は専用ツールで自動処理されるが、それによってパフォーマンスに悪影響を及ぼす事がある。「HES-7」の場合は、大規模FPGAを搭載しているため、デザインを分割することなくダイレクトなインプリメントが可能。複数FPGAを利用する場合は人手作業で分割することになるが、その分割作業は粒度が大きく難易な作業ではないという。

※画像はAldecの提供資料

尚、新製品「HES-7」は既に出荷が開始されており、その価格は最も小さな400万ASIC規模のボードで199万9500円からと市販製品の水準を大きく下回る。また、全ての商品にで1年間の品質保証がつくとの事。David Rinehart氏によると、今後はソフトウェア開発のニーズを意識して各社バーチャル・プラットフォームと「HES-7」の連携に力を入れていくという事だ。

※画像の人物はAldecのDavid Rinehart氏

2012.09.13

2012年9月11日、コンフィギュラブルなデータプレーン・プロセッサを手掛けるTensilicaは、同社のHiFiオーディオDSP製品のライセンス実績を発表した。

発表によると、TensilicaのHiFiオーディオDSPは50社以上にライセンスされた実績があり、SoC向けに提供されているDSPコアとして、最も広くライセンスされたオーディオ・アーキテクチャとなっているとの事。同製品は様々なデバイス向けに、半導体上位20社の半数ならびに複数のセットメーカーに採用されているという。

TensilicaのHiFiオーディオDSPは、その最適化された命令の効率の高さからオーディオおよび音声コーデックの移植を完全にC言語で行うことが可能で、そのパフォーマンスは他のDSPやCPUアーキテクチャのアセンブリを上回るという。TensilicaがHiFiコアをライセンスした企業からは、2015年までに1億コア以上のHiFiコアが出荷される予定。

2012.09.13

2012年9月7日、Mentor Graphicsは、同社のシグナル・インテグリティ(SI)解析ツール「HyperLynx」を富士通セミコンダクターが拡大導入した事を発表した。

発表によると富士通セミコンダクターは、メモリ・インタフェースのLSI-PKG-PCB協調設計のツールとしてMentorの「HyperLynx」を昨年標準採用しており、今回はそれに加えて、5Gbps帯のSerDesシグナル・インテグリティ解析での実績を受けて同ツールを拡大導入することにした。

富士通セミコンダクターは、自社のIBIS-AMIモデルと「HyperLynx」のChannel Analysis技術を組み合わせることにより、5GHz帯のSerDesにおいてもシグナル・インテグリティ解析の精度の確保と解析時間の大幅な短縮を実現。「HyperLynx」上に自社のIBIS-AMIモデルを含む「USB 3.0 Compliance Simulation Kit」を構築したという。

※IBIS-AMI

I/O Buffer Information Specification - Algorithmic Modeling Interface

2012.09.13

2012年9月12日、ESLソリューションを手掛ける米Carbon Design Systemsは、Samsung Venture Investment Corporationから400万ドルの出資を受けた事を発表した。

発表によるとCarbon Design Systemsは今回の出資に伴い、Samsungとの戦略的パートナーシップに加盟。Carbon Design Systemsの提供するESLツールは、Samusungの最先端のコンシューマ製品の開発に利用され、戦略的パートナーシップによってその利用は更に拡大する予定。

Carbon Design Systemsは、現在バーチャル・プロトタイピング・ツール「SoC Designer Plus」とESLモデルの開発環境「Carbon Model Studio」の2つのESLツールを提供中。合わせて、SoCのパフォーマンス解析のための仮想環境キット「Carbon Performance Analysis Kit (CPAK) 」も提供している。Samsungは以前からCarbon Design Systemsのユーザーとして、同社のESLツールを使用していたようだ。

2012.09.10

2012年9月6日、Synopsysは、同社のフィジカル検証ツール「IC Validator」のバージョンアップを発表した。

発表によると最新の「IC Validator」2012.06バージョンでは、最先端プロセス・ノードでのサインオフ・フィジカル検証を可能にする新技術として、ダブルパターンニング・テクノロジ(DPT) に対応した新しいパターン分解性チェック機能と製造性に直結するホットスポットを超高速で特定する特許技術「パターン・マッチング・テクノロジ」が追加されたほか、ランタイムの高速化も図られており、64個もしくはそれ以上のCPU上で「IC Validator」によるDRCを並列実行できるようになったという。

Synopsysの「IC Validator」は、業界トップシェアの配置配線ツール「IC Compiler」と協調したDRC検証が可能な「インデザイン・フィジカル検証」を最大の武器としており、今回の「IC Validator」のバージョンアップにより「IC Compiler」ユーザーはECOを2倍高速に実現することが可能に。「IC Validator」の検証能力は大手ファウンドリの20nmプロセスで認証済で、既に20nmプロセスで多数のテープアウト実績があるという。

2012.09.10

2012年8月28日、ARMとSynopsysは、SynopsysによるARM IPの利用範囲を拡大するための複数年契約の締結を発表した。

発表によると今回の契約は、SynopsysのEDAツールとARM Cortex-A15プロセッサのクロスライセンス契約を発展させたもので、SynopsysはARM Cortexプロセッサ・ベースのSoC設計ソリューションの提供に向けて以下のARMテクノロジを利用できるようになる。

・POP(Processor Optimization Pack)テクノロジ

・CoreLinkインターコネクト

・AMBA 4 ACEシステムIP

・その他、ARM big.LITTLE処理の実装に必要なテクノロジなど

SynopsysがARMの技術を取り込んで提供する設計ソリューションは、デジタル・インプリメント環境のGalaxyツール群がその中心となるが、その他にも仮想プロトタイピング・ソリューション「Virtualizer Design Kit(VDK)」、AMBA 4 ACE仕様検証向けの検証IPおよびProtocol Analyzer、自動化されたチップ設計環境を構築する「Lynx Design System」などが提供される。

2012.09.05

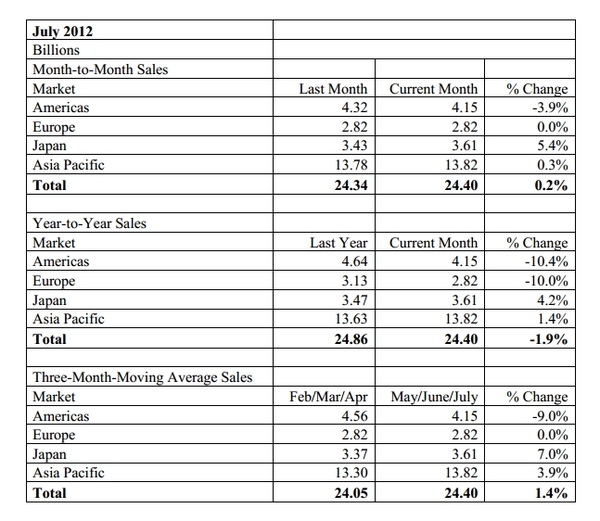

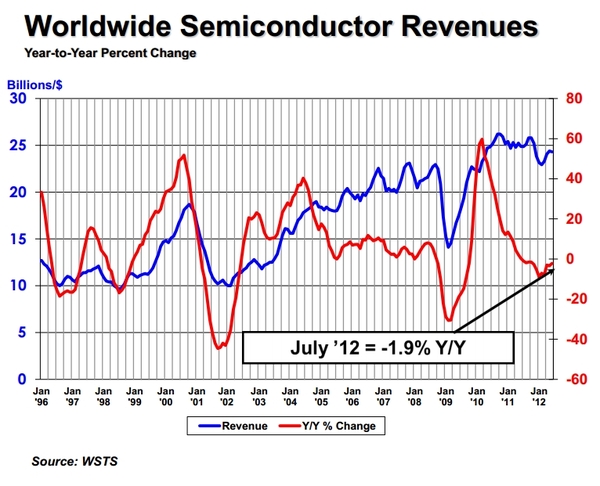

2012年9月5日、米SIA(Semiconductor Industry Association)は、2012年7月の世界半導体売上(3ヶ月移動平均)を発表した。

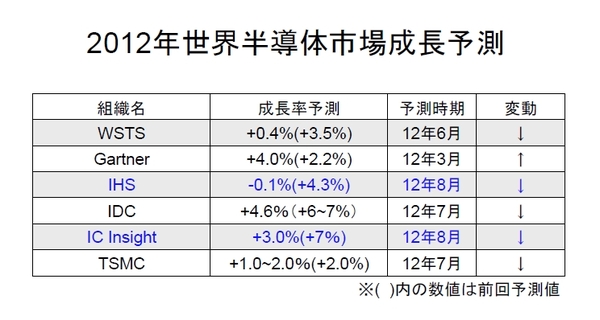

SIAの報告によると、2012年7月の世界半導体売上は前年同時期比約1.9%減、前月比約0.2%増の244億ドルという統計結果となった。これで世界半導体売上の前年割れは14ヶ月連続。当初は7月以降の12年下半期は売上が回復基調に入るとする予測が多かったが、ここにきて企業や各調査機関で年間売上予測を下方修正する動きが加速。遂に12年半導体売上は前年割れとする予測データもで始めた。(市場調査会社IHSは8月時点で12年半導体市場の成長率を-0.1%と予測)

2012年7月の売上を地域別でみると、北米市場の落ち込みが大きく前月比3.9%減、前年比10.4%減。3ヶ月毎の売上平均を見ても2-4月売上に対して5-7月の売上は9%減少した。そんな中、日本市場は前月比、前年比、3ヶ月毎の売上平均の全てにおいて最も高いプラス成長を示した。

2012.09.04

2012年9月4日、ハードウェアベースの検証ソリューションを手掛ける仏EVE社は、富士通九州ネットワークテクノロジーズによる同社製品「ZeBu」の事例を発表した。

発表によると富士通QNETは、検証メソドロジUVMを用いた論理検証の高速化に向けてEVEのエミュレーター「ZeBu」を導入。UVM準拠のテストベンチを論理シミュレータ上で動かし、検証対象(DUT)を「ZeBu」上に実装し、両環境の協調シミュレーションを行うコ・エミュレーション環境の構築を実現した。

富士通QNETシステムロジック開発センター 第一開発部の由利英介氏によると、「ZeBu」のトランザクタ技術によってテストベンチとエミュレータ間の通信オーバーヘッドが最小化され、UVM検証環境を高速化できることを確認。簡単にUVMテストベンチを「ZeBu」に接続する事ができたという。

同事例の詳細については9月28日(金)に新横浜で開催される検証セミナー「Verify2012」にて発表される予定。講演タイトルは「UVMとエミュレータの協調シミュレーションによる検証高速化」。

2012.08.29

2012年8月28日、Xilinxは同社のパートナーである組込みLinuxソリューションのPetaLogix社の買収を発表した。

PetaLogixは、2005年に豪クイーンズランド大学のJohn Williams博士が設立したオーストラリアの会社で、Xilinxの組込みプロセッサ「MicroBlaze」向けの組込みLinux「PetaLinux」とSDK「PetaLinux SDK」を提供。Xilinx Alliance Programのメンバーとして、XilinxのARM搭載FPGA「Zynq-7000 EPP」を使用した非対称型マルチプロセッシング・ソリューションの開発などにも取り組んでいた。

XilinxはPetalogixの買収により独自の組込みLinuxを手に入れ、SoC化の進むFPGAソリューションの更なる拡充を図る。

2012.08.29

2012年8月29日、Cadenceはデンソーによる同社製品採用の成功事例を発表した。

発表によるとデンソーは、車載用のミックスド・シグナルICの設計ツールをCadenceのツールに変更することで、チップの品質向上と生産性改善を実現。デンソーは、デジタル部の設計にCadenceの「Encounter」ベースのRTL-to-GDSIフローを採用することで、既存のフローよりもチップ面積を10%、消費電力を20%削減し、アナログ部の設計においてはCadenceの「Virtuoso」を採用することで設計生産性を30%改善。また、寄生抽出ツールについても従来使用していたツールから「Cadence QRC Extraction」に切り替えたとしている。

本件については、今年7月に開催されたCadenceのユーザー・カンファレンス「CDN Live! Japan」において、「車載用半導体製品設計におけるCadenceツールの適用について」というタイトルでデンソー デバイス事業部 半導体回路開発室 回路開発4課 課長の大石洋一氏が講演したという。

2012.08.24

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2012.08.24

2012年8月23日、Mentor Graphicsは、2013会計年度第2四半期(2012年5月-7月)の売上を報告した。

発表によると、Mentorの2013会計年度Q2の売上は、前年比約12.6%増の約2億4080万ドルで、前年同時期を大きく上回る1816万ドルの純利益を計上した。この結果は前Q1売上報告時点の予測通りで、同社のQ2の四半期売上記録を更新するもの。Mentorは9四半期連続で売上前年比増を継続中で、既に2013会計年度は過去最高のペースで上半期を終えている。(※GAAP基準による会計結果)

Mentorは2013会計年度の売上を11億ドル、次期2013会計年度Q2(12年5-7月)の売上を2億4000万ドルと予測している。

2012.08.24

各組織の発表している2012年8月時点での2012年世界半導体市場成長予測を更新しました。新たにIHSとIC Insightsが予測値を発表しました。

直近発表されている予測値はいずれも下方修正となっています。

2012.08.23

2012年8月23日、Synopsysは、2012会計年度第3四半期(12年5月-7月)の売上を報告した。

発表によると、Synopsysの2012会計年度Q3(12年5月-7月)の売上は、前年同時期比約14.8%増、前期12年Q1比約2.6%増の4億4370万ドル。この実績は前四半期売上報告時の予測に則したもので、前四半期に続いて四半期売上記録を更新した。Synopsysは2012年会計年度に入りQ1,Q2,Q3と四半期売上記録を更新し続けている。また、Synopsysの売上前年超えは今回発表した2012年Q3で8四半期連続となる。

尚、SynopsysはQ3の収支として前年同時期比約45%増の7570万ドルの純利益を計上した。(※GAAP基準による会計結果)

Synopsysは、次期2012会計年度Q4(12年8-10月)の売上をQ3の予測と同じ4億4000-4800万ドルと予測。場合によっては4四半期連続で四半期売上記録を更新する可能性がある。2012会計年度通期の売上予測は、17億4200-5000万ドルと予測幅を狭めた。

2012.08.22

2012年8月21日、Mentor Graphicsは、ネットワークおよびワイヤレス通信向けチップを手掛ける日本のベンチャー株式会社iDが「Questa CDC」を採用した事を発表した。

発表によると株式会社iDは、設計品質の向上と設計期間の短縮に向けて自社の標準メソドロジとしてMentorのCDC検証ツール「Questa CDC」を採用。実際に「Questa CDC」を用いて、多数の非同期クロックを持つ90Mゲート規模の大規模SoCのテープアウトを完了した。「Questa CDC」を使うことでシミュレーション前の設計初期段階でCDCの問題を検出できたという。

株式会社iDは北海道の函館に本拠を置くベンチャーで設立は2005年。通信機器向けのハードウェアおよびソフトウェアの開発を手掛けている。

2012.08.22

2012年8月17日、Mentor Graphicsは、訴訟中のEVEに対して新たな特許侵害訴訟を起こした事を発表した。

発表によるとMentorは、同社の米国特許 6,947,882番「Regionally Time Multiplexed System」をEVEが侵害したとして、米オレゴンの連邦地方裁判所で特許権侵害訴訟を起こした。

Mentorは既に別の保有特許 6,876,962番の侵害を理由に米オレゴンの連邦地方裁判所でEVEを提訴しているほか、東京地方裁判所においても提訴しているが、いずれもEVEのエミュレーター製品がMentorの保有特許を侵害しているとするもの。それに対してEVE側は、今回の新たな訴えを含め一連の訴えは事実無根として裁判で争う構えを見せている。

2012.08.21

2012年8月20日、Mentor Graphicsは、同社の「ICanalyst」デンソーが導入した事を発表した。

Mentorの「ICanalyst」は回路検証のマネジメント環境で、アナログ・セルのキャラクタライゼーションを管理する事も可能。今回デンソーは、アナログ回路の資産を再利用する際に必要となるデータシートの生成作業を削減するために「ICanalyst」を導入。「ICanalyst」のドキュメント自動生成機能を使用し、シミュレーション結果を自動的に集めデータシートを自動生成する形を整えた。これによりデータシート作成に伴う時間的、費用的コストを削減できたという。

2012.08.20

┌─────────────────────────────────┐

■■ Verification Tool のリーティング・ベンダが最先端の検証技術を

■■ お届けする検証技術セミナーの決定版!

■■

■■ 2012年9月28日(金)「 Verify2012 」新横浜で開催!!!

■■

■■【Verify2012の見所】

■■ ・メモリ分野の研究で世界で活躍、中央大学竹内健教授による基調講演

■■ ・検証関連のユーザー事例4件を含む計10セッション

■■ ・検証関連の国内企業10社が参加。各社のソリューションを終日展示

■■

■■ 事前登録制、参加無料!(昼食をご用意)

■■ 定員200名、席に限りがございますので、お早めにご登録下さい!

└─────────────────────────────────┘

Verification Toolのリーティング・ベンダが最先端の検証技術をお届けする検証

技術セミナーの決定版「Verify2012」が今年も開催されます。

Verifyセミナーは、検証ツールを専門的に扱うEDAベンダ各社が集まり、 最新の

検証技術とメソドロジ、検証ツールを使用した事例を紹介する技術セミナーで、

今年で13回目の開催となります。

今年のVerify2012では、主催5社、協賛5社の計10社にて、設計検証の成功に役立つ

技術講演と製品およびサービスの展示デモンストレーションを行います。

また、メモリの研究で世界的に有名な中央大学の竹内健教授による基調講演ほか、

株式会社富士通九州ネットワークテクノロジーズ、株式会社リコー、富士通マイク

ロソリューションズ株式会社、ルネサスエレクトロニクス株式会社の各社様より

検証に関する事例講演を頂く予定です。

-------------------------------------------------------------------------------

■Verify2012 セミナー開催概要

会場:新横浜国際ホテル南館

日時:2012年9月28日(金曜日)

受付開始 9:30 セミナー 10:30?17:30 懇親パーティー 17:50?19:30

参加: 無料(事前登録制)※セミナーでは昼食をご用意させて頂きます。

主催:アルデック・ジャパン株式会社

カーボン・デザイン・システムズ・ジャパン株式会社

日本イヴ株式会社

日本ワンスピン・ソリューションズ株式会社

スプリングソフト株式会社

協賛:株式会社エッチ・ディー・ラボ

株式会社シンコム

日本リアルインテント株式会社

株式会社ベリフォア

ベリフィケーションテクノロジー株式会社

事務局:株式会社EDAエクスプレス

■Verify2012 セミナー内容はこちら

■Verify2012 出展社の展示案内はこちら

■Verify2012 参加お申し込みはこちら

------------------------------------------------------------------------------

■■お問い合わせ

Verify2012に関するお問い合わせは、下記窓口までお願い致します。

Verify2012運営事務局 EDAエクスプレス info@eda-express.com

------------------------------------------------------------------------------

2012.08.17

2012年8月9日、設計データ管理システムを手掛けるIC Manageは、Alteraが同社の「Global Design Platform(GDP)」を採用した事を発表した。

発表によるとAlteraは、設計データ管理システム「Global Design Platform(GDP)」を世界各地の拠点で利用すべくIC Manageと複数年契約を締結。「Global Design Platform(GDP)」には、「IP Central」というIPのデータベースも含まれており、Alteraは設計データやバグ情報の管理と合わせて設計IPの効率的な再利用も進める。

IC Manageの「Global Design Platform(GDP)」は、AppleやNVIDIAなどの大手が採用している事で有名で、Alteraは既に同製品を導入し1ヶ月未満で世界各地の拠点への展開を完了しているという。

ちなみにIC ManageのCEO Dean Drako氏は、9年前にIC Manageの他にBarracuda Networksというセキュリティー・ソリューションの企業も設立しており、現在両社のCEOを兼任。Barracuda Networksの売上は2億5000万ドル規模。

2012.08.17

2012年8月8日、Cadenceは、車載組込みシステムに関する論文コンテストの実施を発表した。

発表によるとコンテストは学生を対象としたもので、車載組込みシステムの設計および検証に関する優れたフローやメソドロジを導き出す事をゴールとしており、今回のコンテストでは、CPU、バス、メモリ、ペリフェラルで構成されるSystemCベースの車載ECUのバーチャル・プラットフォームが命題となっている。論文投稿の締切は2012年9月28日で、コンテストの勝者3名は2013年5月にミュンヘンで開催予定のCadenceのユーザー・セミナー「CDNLive! EMEA」に招待される予定。

EDA業界ではSynopsysが自社のバーチャル・プラットフォーム・ソリューションを積極的に車載ECU開発向けに提案しているが、Cadenceも車載ECUのハードおよびソフトの開発をバーチャル・プラットフォーム・ソリューションのターゲットとして捉えているようだ。

車載ECUソフトの開発に関しては、大手自動車メーカーの集まる欧州においてソリューション開発が活発で、標準プラットフォームAUTOSARをはじめ主要な開発ツールも欧州発のものが多い。今回のコンテストは勝者が「CDNLive! EMEA」で表彰されるようで、欧州市場の自動車メーカーやサプライヤに対するマーケティング戦略の一環とも見て取れる。

2012.08.15

2012年8月9日、ARMとCadenceは、ARM Cortex-AシリーズのプロセッサをベースとしたSoCの実装に関する協業成果を発表した。

発表によると両社は、ARMの提供するPOP(Processor Optimization Pack)を最適化するソリューションを開発。最初のバージョンとして、ARM Cortex-A9プロセッサ向けのPOPをuLVTを含むTSMC40LPプロセス向けに最適化するソリューションを発表した。POPの最適化にはCadenceのデジタルIC設計プラットフォーム「Encounter」が用いられ、Cortex-A9の実装を証明済のPPAベンチマーク結果通りに迅速に実現することができる。

ARMの提供するPOPは、特定プロセスをターゲットにARMコアの最適かつ短期間での実装を実現するもので、フィジカルIP、リファレンス・フロー、各種ベンチマーク・データなどがパッケージ化されている。今回Cadenceが最適化に協力したTSMC40LPプロセス向けのARM Cortex-A9のPOPは今年の4月にリリースされたばかりで、その際に合わせてTSMC28HP/HPM向けのPOPとCortex-A7,A15のPOPもラインナップされた。

Cadenceは、ARMとの協業はTSMC28HPMプロセスでのCortex-A9およびCortex-A15プロセッサのシングル、デュアル、およびクアッド・コアのインプリメンテーションにまで拡張されているとしており、今後はこれらPOPに対応する最適化ソリューションが出てくる様子だ。両社共通の顧客は同ソリューションを利用することで、高品質なARMベースSoC製品を短い開発期間で市場投入できるようになる。

2012.08.05

2012年8月3日、米SIA(Semiconductor Industry Association)は、2012年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年6月の世界半導体売上は前年同時期比約2%減、前月比約0.1%減の243億8000万ドルという統計結果となった。これで世界半導体売上の前年割れは13ヶ月連続。今年に入り3,4,5月と3ヶ月連続して売上前月増を達成し、市場の回復基調が見え初めていたが、不安定な世界経済の影響によりこの6月は5月の売上を下回った。2012年Q2(4-6月)の実績を踏まえ、企業や各調査機関で年間売上予測を下方修正する動きが出始めている。

2012年6月の売上を地域別でみると、日本およびアジアは前月比、前年比ともにプラス成長であるのに対し、北米と欧州は前月比、前年比ともにマイナス成長となっている。

2012.08.04

2012年8月3日、SynopsysはSpringSoftの買収を発表した。

発表によるとSynopsysは、SpringSoftの発行株式の公開買付によりSpringSoftを買収する予定で、その買収金額は総額約4億600万USドル(122億台湾ドル)、現金資産を差し引いた実質金額は約3億500万USドル(92億台湾ドル)となる。買収は、2013会計年度の第一4半期中に完了する予定とされている。

2012.08.02

2012年8月2日、Synopsysはルネサス エレクトロニクスと共同でルネサス製マイコン向けのソフトウェア開発キットを開発する事を発表した。

発表によると両社が共同開発するソフトウェア開発キット「VDK(Virtualizer Development Kits)」は、Synopsysのバーチャル・プロトタイピング・ツール「Virtualizer」で使用する仮想ハードウェア環境で、ルネサスの次世代車載マイコン「RH850ファミリ」を始めとする各種マイコンをサポートする予定。開発は両社混合のチームによって開発される。

ルネサスの「RH850ファミリ」は、車載向けマイコンとして様々な自動車向けアプリケーションへの利用が期待されており、「RH850ファミリ」をサポートする「VDK」が完成すれば、各種車載アプリケーションのソフトウェア先行開発を実現する事が可能となる。

自動車メーカーは、バーチャル・プロトタイピング・ツールの有力なポテンシャル・ユーザーと言えるが、これまではモデルの供給・流通体制が整っておらず、ツールを使いたくてもモデルの用意など環境構築に手間取り、上手く使いこなせないという状況が続いていた。

Synopsysの提供する「VDK」はバーチャル・プロトタイピングの核となるマイコン・モデル他、ペリフェラル・モデルなど必要なモデル一式をキットとして供給するもので、これを利用すればユーザーは環境構築に手間取ること無くバーチャル・プロトタイプを用いたソフトウェア開発を実践できるようになる。また、これらキットがマイコン・ベンダとの共同開発で供給されるという点がモデルの信頼性という意味で非常に大きい。

Synopsysは既にARMの低消費電力化技術「big.LITTLE」向けのVDKや、ARM Cortex-A15 MPCoreベースのデザイン向けVDKを提供しており、今回発表されたルネサスのマイコン向けVDKのように順次VDKのラインナップを増やしていく戦略と思われる。

尚、ルネサス RH850マイコンのVDKは、2012年の第四4半期に提供が開始される予定との事。

2012.08.02

2012年7月30日、Synopsysはアナログ/カスタムIC向け自動レイアウトツールを手掛ける米Ciranova社を買収した事を発表した。

Ciranovaは2006年設立のベンチャーで、OpenAccessベースのPCell作成環境「PyCell Studio」、PCellの運用性を高める「PCell Xtreme」、そしてアナログ/カスタムIC向け自動レイアウトツール「Helix」の提供を中心にビジネスを進めていた。

「Helix」は業界初のアナログ自動レイアウトツールとして注目されており、TSMCのアナログ/ミックスド・シグナル設計向けの「AMSリファレンス・フロー2.0」で採用されているほか、昨年はファブレス大手2社が新規導入するなど、Ciranovaのビジネスをドライブしていた。

Ciranovaには2008年にSynopsysとMentorが、2010年にはIntelが出資していた。

SynopsysとCiranovaは共にInteroperable PDK Libraries (IPL) Allianceの創立メンバーで、SynopsysはIPL Allianceのエコシステム拡張に向けて今後も「PyCell Studio」およびCiranovaが提供するOpenAccessベースのパラメトリック セル「PyCell」の使用ノウハウを提供し続けるだろうとしている。

尚、Synopsysは今回のCiranova買収に関する条件を明らかにしていない。

2012.08.01

2012年7月17日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の論理シミュレーター「Riviera-PRO」の顧客利用事例を発表した。

発表された事例は、Aldecのユーザー英Test and Verification Solutions社(TVS)のもので、検証サービスを手掛ける同社が顧客向けに提供しているUVMベースの検証IPを「Riviera-PRO」で検証しているというもの。

TVSはAldecの「Unite IP Partner Program」のメンバーで、そのエコシステムを通じて自社開発したSPI, I2C, SDCARD, UART, AHB, AXI-4, USB等の検証IPを提供しており、イギリスの他にフランスとインドにも拠点を持っている。

2012.08.01

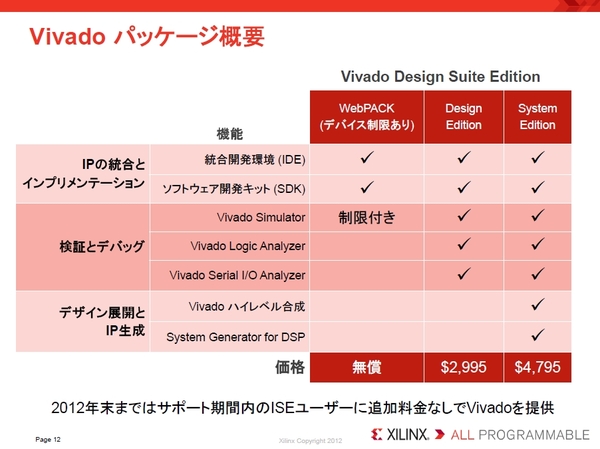

2012年7月27日、Xilinxは、今年4月に発表し特定顧客向けにβリリースしていた同社の次世代設計環境「Vivado」の一般リリースを発表した。

Xilinxによると今回一般ユーザー向けにリリースされた「Vivado Design Suite 2012.2 」は、2つのフェーズに分けて展開されるうちの最初のリリースで、「Vivado」の大きな特徴と言える高位合成エンジンと高度なインプリメント機能の両方が搭載されており、これを用いることでC/C++/SystemCからの高位合成機能や新たな論理合成、配置配線など、「Vivado」の最新機能を駆使した設計を実現できる。

「Vivado」は、「System Edition」、「Design Edition」、「Web Pack」と3つのパッケージが用意されており、「ISE」 の「Logic Edition」および「Embedded Edition」のユーザーは「Vivado Design Edition」を、「ISE Design Suite DSP」および「System Edition」のユーザーは「Vivado System Edition」をライセンス期限内であれば無償で利用することが可能。

新規ユーザーが「Vivado」を購入する際の価格は、高位合成付きの最上位パッケージ「System Edition」が米国販売価格4,795ドル、その下の「Design Edition」が米国販売価格2,995ドルとなっている。無償の「Web Pack」も提供されるが、サポートするデバイスや一部機能に制限がかかる。

※画像はXilinx提供のデータ

Xilinxは来年早々に「Vivado」の2つ目のフェーズとして、IP-XACTの技術を用いたシステムレベルのIPの接続機能「IP インテグレーター」やインタラクティブなデザインおよび検証環境、IPの利用を容易化する「IP パッケージャー」を提供する予定としている。

2012.07.26

2012年7月25日、ARMは、2012会計年度第2四半期(2012年4-6月)の売上を報告した。

ARMの2012会計年度Q2の売上は、前年比12%増、前期比1.7%増の2億1300万ドルで営業利益は前年比約28%増の約1億300万ドルだった。売上の内訳を見るとライセンスの売上が前年比12%増の7860万ドル、ロイヤリティの売上が前年比15%増の1億1000万ドルだった。ARMは2010年Q1より四半期売上の前年増を継続しており、今期Q2で10四半期連続で売上前年増となった。

ARMはこのQ2で計23件のプロセッサ・ライセンスを獲得(前Q1では22件)。その内5件は新規顧客で製品別では6件がCortex-Aシリーズ、11件がCortex-Mシリーズのライセンス、3件がGPU Maliのライセンス契約だった。Cortex-Aシリーズのライセンス契約には、ARMの低消費電力化技術「big.LITTLE technology」を実現するCortex-A15およびA7の両方のライセンス契約を行った顧客も含まれており、現在のところ「big.LITTLE technology」を利用可能な企業が12社存在しているという。

また、ARMv8アーキテキチャーのネットワーキング製品への適用も進んでおり、このQ2ではFreescaleが同社初のARMベースのネットワーク向けチップを発表。Freescale以外にもHiSilicon, LSI, Texas Instruments, Xilinxがネットワーキング製品向けにARMを使用している。

※画像はARM発表資料より抜粋

2012Q1で出荷されたARM搭載チップの総数は約20億個で前年比9%増、うち約11億はスマートフォンなどのモバイルデバイス向けに、約8.4億個はコンシューマーおよびクルマ向けに出荷されている。プロセッサの種類別で見ると、出荷数の70%はARM7,9,11のv6アーキテクチャ製品で残りの30%がCortex-A,R,Mのv7アーキテクチャ製品となっており、徐々にCortexシリーズの出荷数が増加している。

※画像はARM発表資料より抜粋

2012.07.26

2012年7月25日、Cadenceは、2012会計年度第2四半期(2012年4-6月)の売上を報告した。

Cadenceの2012年Q2売上は、前年同時期比約15%増、前期Q1(12年1-3月)と比較して約3%増の3億2600万ドル。純利益は3600万ドルで前年比33%増だった。(※GAAP基準による会計結果)

Cadenceは業績好調を維持し続けており、このQ2で10四半期連続で売上前年比増を記録。2年半に渡り売上を伸ばし続けている事になる。

Cadenceは次期2012年Q3売上を今期同等以上の3億2500-3500万ドルと予測。2012年の年間売上予測を12億9500-13億1500ドルと上方修正している。