NEWS

2012.12.04

2012年12月2日、Cadenceに在籍するStan Krolikoski氏がIEEEの「Ron Waxman Award」を受賞した。

Richard Goering氏が書いたCadenceのBlog記事によると、今回Stan氏は1980年台に関わったVHDLの標準化活動を始めとする、IEEEにおける数々の標準化活動への貢献が讃えられ「Ron Waxman Award」を受賞。同賞は、IEEEのDesign Automation Standards Committee (DASC)を立ち上げたRon Waxman氏の名前に由来する賞で、DASCにおける貢献者を2007年より毎年1名表彰している。

Stan氏は現在、EDA及び設計言語関連の標準化団体Accellera Systems Initiativeにセクレタリーとして従事しているほか、IEEE P1666 SystemCワーキング・グループのチェアも務めており、Cadenceに在籍しながら現役でデザイン・オートメーション関連の標準化活動に携わっているが、これまで以下のような標準化活動関連の経歴があるという。

・IEEE 1076 VHDLのワーキング・グループで標準化活動に参加

・IEEE 1076 VHDL Analysis and Standardization Group (VASG) のチェアを務める

・VHDLの普及推進団体VHDL InternationalのボードメンバーでPresidentを務める

・Verilogの普及推進団体Open Verilog Internationalのボードメンバー

・Accelleraのファウンダー、AccelleraとSPIRIT Consortium、AccelleraとOpen SystemC Initiativeの統合に貢献

※写真の人物がStan氏、IEEEのドキュメントより抜粋

※写真の人物がStan氏、IEEEのドキュメントより抜粋

2012.12.04

2012年12月3日、業界標準ツール「SpyGlass」をはじめとしたRTL解析ソリューションを手掛けるAtrentaは、SpyGlass Platformのバージョン・アップを発表した。

Atrentaによると今回のバージョン・アップは、初めてRTL解析環境「SpyGlass Platform」とチップのプランニング及びアセンブリ環境「GenSys Platform」が同時に改版され、ユーザーのフィードバックを受けてツールのパフォーマンス、解析精度、ユーザビリティなど包括的なツールのエンハンスが実施された。

具体的には、「SpyGlass Platform」において、「GuideWareリファレンス・メソドロジ」の強化、Tclのサポートの強化、CDC解析機能の改善、テスタビリティ解析の速度および精度の改善、配線密集度解析の速度および精度の改善、RTLフィジカル解析機能における先端プロセス・ノードのサポート、RTL 3D ICプランニング・ツールの追加などが行われた。RTL 3D ICプランニング・ツールは、複数顧客と共同で開発しているツールで、今回のバージョンアップに含まれるものは、限定リリース・バージョンとなっている。

また、「GenSys Platform」においては、よりフレキシブルなロジカルおよびフィジカルなポート・マッピング、オート・コネクト機能の改善、RTLヘルス・チェック・レポートの強化などが実現された。

2012.12.04

各組織の発表している2012年12月時点での2012年世界半導体市場成長予測を更新しました。新たにWSTS,Gartner,IHSが予測値を発表しました。IC Insightsも2013年以降の市場予測レポートにて2012年の成長率について触れています。

期待されていた下半期の景気高揚が実現せず、直近発表されている予測値はいずれも下方修正で2-3%のマイナス成長となっています。今年1月時点では、各組織軒並み2-3%のプラス成長を予測していました。

2012.12.04

2012年12月3日、Synopsysは、SpringSoftの買収が完了した事を発表した。

発表によるとSynopsysは、2012年8月のSpringSoftの買収発表後、10月1日の時点でSpringSoft社の発行済み株式の約91.64%の買収を完了していたが、11月30日までに残りの株式を全て買収し同社の株式を100%取得。台湾証券取引所に上場していたSpringSoftは上場廃止となった。

Synopsysによると今回の買収総額は、約4億1700万USドル(122億台湾ドル)、現金資産を差し引いた実質金額は約3億2000万USドル(94億台湾ドル)だという。

Synopsysは2012年の間に今回のSpringSoft以外に、Magma Design Automation、フォトニクス関連ツールの米RSoft Design Group、アナログ/カスタムIC向け自動レイアウトツールの米Ciranova、エミュレーター製品の仏EVEを買収している。

2012.11.30

2012年11月29日、Mentor Graphicsは、2013会計年度第3四半期(2012年8月-10月)の売上を報告した。

発表によると、Mentorの2013会計年度Q3の売上は、前年比約7.3%増、前Q2比約11.6%増の2億6876万ドルで、前年比約27%増の3064万ドルの純利益を計上した。この結果は前Q2売上報告時点の予測を若干上回るもので、Mentorはこれで10四半期連続で売上前年比増を達成した。尚、2013会計年度の売上累計は7億5748万ドルで、昨年実績の9.1%増となっている。(※GAAP基準による会計結果)

Mentorは、次期2013会計年度Q4(12年11-13年1月)の売上を3億4300万ドルと予測しており、このまま行けば2013会計年度の売上合計は11億ドルに達し、同社過去最高記録を更新しそうだ。

2012.11.29

2012年11月28日、Cadenceは、車載用イーサーネット・コントローラ向けの設計IP、および検証IPのリリースを発表した。

発表によるとCadenceがリリースした車載用イーサーネット・コントローラ向けの設計IPと検証IPは、車載用イーサネットの標準化団体「OPEN Alliance SIG」が策定した車載向けのイーサーネット規格をサポート。同IPを利用すれば、車載用イーサーネットをベースとした車載向けICの開発や車載用イーサーネット・プロトコルに対する検証を加速できる。Cadenceは「OPEN Alliance SIG」のメンバーとして、車載用イーサネット規格の標準化推進に参画。同団体に名を連ねるEDAベンダは今のところCadenceだけである。

2012.11.27

2012年11月27日、Cadenceは、同社の論理合成ツール「RTL Compiler」をルネサス マイクロシステム株式会社が採用した事を発表した。

発表によるとルネサス マイクロシステムは、Cadenceの論理合成ツール「Encounter RTL Compiler」を活用することで、チップ実装率の15%改善、チップ面積の8.4%削減といった効果を実プロジェクトで実現。設計期間の短縮とコスト削減を達成したととの事。

その理由として、設計の早期段階でネットリストの構造解析環境を提供するという「Encounter RTL Compiler」の独特な機能が挙げられており、この機能により、配置・配線前に前に設計上問題となる回路構造の検出や回路修正提案が可能に。複数回の配置・配線が不要となり、設計品質の向上とTAT短縮に繋がったという。

2012.11.22

2012年11月14-16日、パシフィコ横浜で開催されたEDSFair2012にて訪れた各社のブース、その他聴講したセッションの内容など簡単にレポートします。

今年9月に発表した新製品のFPGAボード「HES-7」を展示。「Virtex-7 2000T」を2個搭載するタイプで2400万ASICゲート相当のデザインに対応できる「HES-7 XV4000」の実物が展示されていた。そのコスト・パフォーマンスの高さから、やはり国内でも引き合い多数との事。海外では既に導入実績が出始めているようだ。

※画像は「HES-7 XV4000」

FPGA設計向けのソリューション「SpyGlass for FPGA」を展示。こちらは始めて耳にしたソリューション。RTLとネットリストでデザイン・ルール・チェックとCDC検証を行う。FPGA設計を狙ったEDAソリューションはにわかに増えてきている。また、「SpyGlass」関連では、TSMCも利用するIPの品質チェック・ソリューション「Atrenta IP Kit」を展示。その他、今年6月に買収を発表したNextOp社のアサーション・シンセシス・ツールも紹介されていた。最近のニュースでは、同社がRTLパワー解析分野で業界2位のEDAベンダになったという発表があった。尚、同社の展示の様子は海外サイト「SemiWiki」でも紹介されていた。

※画像はアトレンタのブースの展示パネル

※関連ニュース

同社は、SystemCのモデリング・サービスに力を入れるインドの設計サービス会社。OCP-IPの提供するツール環境の開発なども手掛けている。日本国内にも複数のクライアントが存在することの事で、日本に限らず北米企業向けにもサービスを展開している。ブースでは、同社が開発した仮想プロトタイピング環境向けのIPパッケージ「Quick Start Package」を紹介。同パッケージはARM Cortex-A9を用いたシステムの仮想プロトタイピングを狙ったもので、SystemC TLMでモデリングされた各種ペリフェラル・モデルがパッケージ化されている。イメージング向けやオーディオ向けなど各種アプリケーションに特化したパッケージを複数用意しているようだ。尚、同社はTLMでモデリングしたIPの単品販売も行なっている。

※画像はCEOのUmesh Sisodia氏

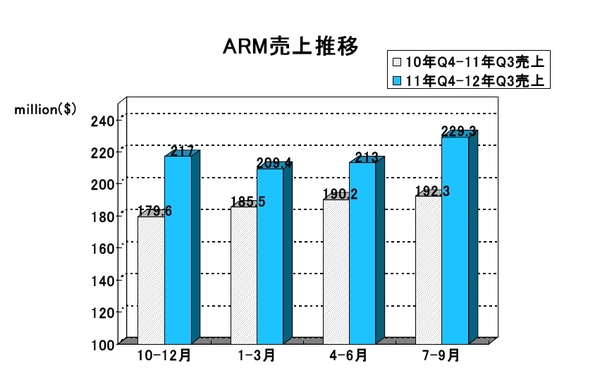

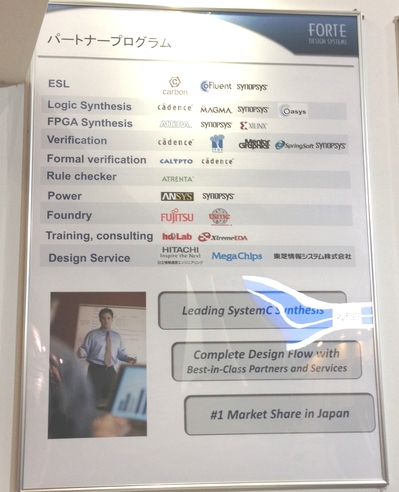

同社は11/14に日立情報通信エンジニアリングによる採用事例を発表。話を聞いたところ、その他にも東芝情報システム、メガチップスも同社の高位合成ツール「Cynthsizer」を以前からデザイン・サービス用に採用しているとの事だった。高位合成ツール「Cynthsizer」は今年8月に新バージョン4.3をリリース。ツールの各種合成機能や解析機能、合成用IPなどのエンハンスが行われたようだ。

※画像はフォルテのブースの展示パネル

※関連ニュース

同社の今年の展示は組込みソフト開発ソリューション、ESLソリューション、自動車向けソリューションに集約。ハードウェア設計関連の主力ソリューションの展示は基本的に無かった。目を引いたのは車載ECUソフトの共通コンポーネント「AUTOSAR」対応の開発環境「Volcanoファミリ」や、組込みソフト統合開発環境「Sourcery CodeBench」関連のソリューション。UMLベースのモデル・ベース開発環境「BridgePoint」なども展示されていた。また、展示会前には、同社の提供する2つのRTOS「Mentor Embedded Linux」と「Nucleus」に関する発表が相次いだ。「Nucleus Innovate Program」に関する発表によると、Mentorは年間売上100万ドル未満の企業に対して、「Nucleus RTOS」と「Sourcery CodeBench」を無償提供するという。

※画像はメンター・グラフィックスのブース

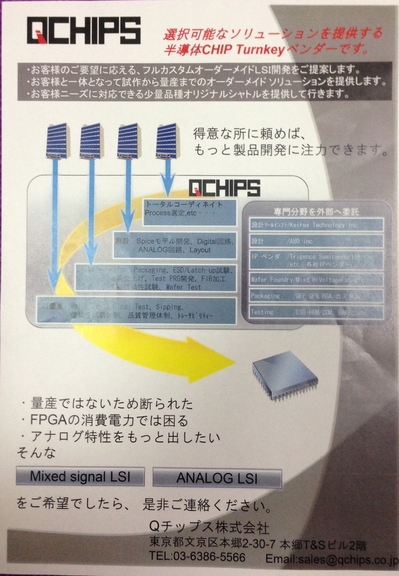

同社は昨年10月に設立されたばかりのLSIターンキー・サービスを手掛けるベンチャー。設計環境のカスタム・サービスや設計サービスを手掛けるケイレックス・テクノロジーと共同でブースを構えていた。社長の内田氏によると、アナログ/ミックスド・シグナルLSIの製造にフォーカスしており、小ロットのニッチなニーズにも細かく対応。顧客の要望に応じて設計サービスにも対応する。使用するファブは海外のファブで、スタートアップながら既に国内顧客からの受注実績もあるという話。ケイレックス・テクノロジーが営業面でサポートしているようだ。

※画像はQチップス社のブローシャ

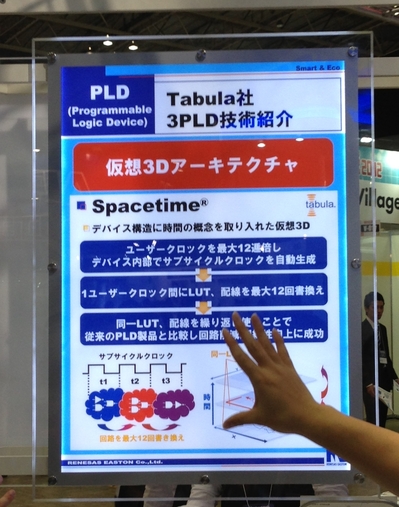

動的再構成技術を用いた「3PLD」を手掛けるTabula社、同社の製品を国内代理店のルネサス・イーストンが併催のET2012で展示していた。Intelの22nmプロセスで製品を出すという事で話題になっている同社は、来年7月に22nmの「3PLD」のESを出す予定との事。「3PLD」は、ユーザー・クロックの最大12倍速でサブ・サイクル・クロックを内部生成。ユーザー・サイクル1回で最大12回の動的回路再構成を実行する。そのパフォーマンスの秘訣は、最大12ポートのマルチ・ポートRAM、最大2GHzのRAM動作速度、最大2GHzの配線切り替え速度にあるとしている。尚、同社の「3PLD」の開発環境は、以前までクラウド上に構築された環境を用いるスタイルであったが、現在ではスタンド・アローンのツールで設計者のデスクトップ上で作業が可能となっていると聞いた。

※画像はルネサス・イーストンの展示パネル

「消費増税よりこっちの方が待った無し!仮想ECU環境を利用した車載ソフトウェアの開発検証!」

セッションの前半部のみを聴講。会場は100名は超えていると思われるかなりの人の入り様であった。日頃耳にする機会の少ない自動車メーカー、サプライヤの仮想ECU環境を用いたソフト開発の取り組みが聞けた。同講演資料の一部は、今年11月に公開されたという、国内のVECU-MBDワーキンググループのホームページからダウンロード可能。同団体は、業界を横断する組織で仮想ECU環境を用いたソフト開発に関する共通のガイドラインの策定を目指している。尚、セッションの前半部を聞いた限りでは、仮想ECU環境を用いた設計手法のネックはやはり「モデルの供給」にあるとの話。これについてはVECU-MBDワーキンググループに参画するSynopsysなどツールベンダーに期待するという声もあったが、マイコン・ベンダが動かなければ話は到底進まない。コンスーマ・エレクトロニクスの世界で仮想ECU環境を用いた開発が浸透しつつあるのは、ARMをはじめとするIPベンダがモデル供給に積極的に協力しているからに他ならない。

2012.11.21

2012年11月19日、Alteraは同社の専用開発環境「Quartus II」のバージョンアップを発表した。

発表によると、最新の「Quartus II v12.1」 では、先日リリースが発表された「OpenCL 向けSDK」 のデザイン・フローがサポートされたほか、システム統合ツール「Qsys」、DSP開発ツール「DSP Builder」がエンハンスされ、更に28nm FPGA「Stratix V」向けの部分再構成機能であるパーシャル・リコンフィギュレーションを可能とする設計フローもサポートされた。

またデバイスとしては、28nm FPGA「Arria V GZ」がフル・サポートされ、その他の28nm FPGA「Stratix V」、「Arria V」、「Cyclone V」 ファミリとARM搭載FPGA「SoC FPGA」 のいくつかの製品が新たにサポートされた。

既に「Quartus II v12.1」のサブスクリプション・エディション、無償のウェブ・エディションはAlteraのWebサイトからダウンロード可能で、ライセンスの価格はノードロックの年間ライセンスで2995ドルとなっている。(米国販売価格)

2012.11.20

2012年11月20日、Mentor Graphicsは、同社の運営する検証ナレッジ・サイト「Verification Academy」上で新たなコンテンツ「Coverage Cookbook」をリリースした事を発表した。

発表によると「Coverage Cookbook」のリリースは、サイト「Verification Academy」のリニューアルに伴うもので、検証メソドロジUVMを補完するもの。同コンテンツを利用する事で、カバレッジ・ドリブン検証フローを効果的に導入するための、メソドロジとプロセスを学習可能で、具体的には以下の様な記事がオンラインで提供されている。※UVM:Universal Verification Methodology

・現在どのような種類のカバレッジメトリクスが使用されているかについての基本的な知識と効果的な利用法

・仕様から機能カバレッジモデルを抽出するための繰り返し可能なプロセス

・機能カバレッジモデリングのプロセスを示す実例によるデモンストレーション

尚、「Coverage Cookbook」の追加以外にも「Verification Academy」では、様々な機能検証関連のコンテンツが拡充されたほか、サイト自体、HTML5が導入されビデオ講座コンテンツが視聴しやすくなるなどユーザビリティが高められたようだ。

2012.11.20

2012年11月14-16日、パシフィコ横浜で開催されたEDSFair2012にて、株式会社シンコムのブースを覗いてみた。

同社は今年からJasper Design Automationの日本代理店として、Jasperの手掛ける各種フォーマル検証ツールを取り扱っている。

ブースでは先ごろ発表された新製品、「Structural Property Synthesis App」と「Behavioral Property Synthesis App」が展示されていた。※関連ニュース

※画像はシンコムの出展社セミナー資料の抜粋

聞いたところによると、これまでの統合的なフォーマル検証ツールの提供から、「JasperGold Apps」という検証項目毎のアプリケーション群の提供に変更した事で、各検証ニーズに対応するソリューションが明確になり、ユーザーの関心も更に高まったとの事。中でも新製品の2種類のプロパティ自動生成ツールは来場者の注目を集めていた様子だった。

フォーマル検証を利用する上で大きな壁となるのが、プロパティ(アサーション)の記述であり、ここ数年、これを自動化しようとする取り組みが各社によって進められている。Jasper以外にもAtrenta(NextOp)やMentor Graphicsがアプローチは違うが同種のソリューションを提供しており、業界としては「如何に容易に扱えるか」がフォーマル検証ツールの導入の鍵となっている。

Jasperのフォーマル検証ツールはARMで正式採用されている事で有名で、ARMでは、ARM AMBA4 AXI Coherency Extensions(ACE)プロトコルのproposal specificationの検証や、キャッシュコヒーレンシーとDeadlock問題の検証などに利用されている。

2012.11.20

2012年11月19日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、Berkeley Design Automationは、同社がDeloitte社の北米成長企業ランキング「2012 Technology Fast 500」に選出された事を発表した。

Deloitte社の北米成長企業ランキング「2012 Technology Fast 500」は、成長率を基準に北米における優良企業をリストアップしたもので、今回発表された2012年版のリストは、2007年から2011年までの売上の成長率によってランキングされている。

業界デファクトとなりつつある「Analog FastSPICE」を手掛ける、Berkeley Design Automationは、2007年から2011年までの売上の成長率が302%で同リストにて262位にランクされた。同社は確実にSPICE市場におけるシェアを拡大しており、業界で数少ない中堅ベンダとして勢いを維持している。つい先日も新製品「Analog FastSPICE AMS」を発表したばかり。※関連ニュース

2012.11.15

2012年11月14日、SystemCからの高位合成ツールを手掛けるForte Design Systemsは、同社の「Cynthesizer」を日立情報通信エンジニアリングが導入したことを発表した。

発表によると、日立情報通信エンジニアリングは、同社のLSI論理設計サービス・ビジネスにForteの高位合成ツール「Cynthesizer」を採用したとの事。同社は古くからC言語ベースの開発ソリューションを設計サービスとして提供しており、「Cynthesizer」が入力とするSystemC言語の教育サービスなども手掛けている。

同じグループで親会社の日立製作所では、Forteの「Cynthesizer」の他に、BluespecやNEC、Calyptoの高位合成ツールも利用しているようだが、日立情報通信エンジニアリングがLSI論理設計サービス用に採用を公表したのは今回のForteの高位合成ツール「Cynthesizer」だけである。

2012.11.14

2012年11月12日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、Berkeley Design Automationは、新製品「Analog FastSPICE AMS(AFS AMS)」のリリースを発表した。

発表によると新製品の「Analog FastSPICE AMS(AFS AMS)」は、同社の業界デファクトツール「Analog FastSPICE」と市販のVerilogシミュレータを組み合わせて利用することで高速なミックスドシグナル・シミュレーションを実現するもので、Verilog-AMS言語をフルサポートし、アナログ設計者/デジタル設計者の双方にシンプルなAMSフローを提供する。

Berkeley Design Automationによると、既存のAMSシミュレータが全てのアナログ回路をVerilog-AMS言語に変換してシミュレーションを行うところ、「AFS AMS」は強力なコンフィギュレーションサポートにより、Verilog-AMS、Verilog-D、Verilog-Aおよび主要なSPICEネットリストフォーマットを任意の構成でネスティングし、全てを変換すること無くシミュレーションすることが可能。これによりアナログ回路のシミュレーションにおける「Analog FastSPICE」の優れたパフォーマンスが生かされ、既存のAMSシミュレータよりもはるかに高速なミックスドシグナル・シミュレーションが実現できる。

また、既存のAMSシミュレータのアプローチように、全てのアナログ回路をVerilog-AMSに変換してしまうと、アナログ設計者はそれを理解できず、検証体制を整えるまでに数週間にも及ぶ時間を浪費する事になるが、「AFS AMS」のアプローチであれば容易なセットアップかつシンプルなフローで数時間ですぐに検証を実現可能。これまで利用してきたアナログ設計環境やコマンドラインをそのまま使え、コンフィギュレーションの指定だけで、アナログ設計者はオリジナルのネットリストを、デジタル設計者はオリジナルのソースを既存の環境で使うことができるという。

尚、富士通セミコンダクターでは既に「AFS AMS」を導入しており、「AFS AMS」は既存のAMSシミュレータよりも10倍以上高速で導入も容易であるとコメントしている。

2012.11.13

2012年11月12日、業界標準ツール「SpyGlass」をはじめとしたRTL解析ソリューションを手掛けるAtrentaは、同社の市場シェアについて発表した。

Atrentaの発表によると、EDA業界の調査会社であるGarySmithEDA社の2012年の市場動向レポートによって、AtrentaはRTLパワー解析ツール分野で業界二位の座にあると報告された。同分野の首位はSynopsysでそのシェアの差は7%であるとの事。同調査レポートによると、RTLパワー解析の分野は市場成長率18%でEDAにおける急成長分野の一つだという。

Atrentaの提供するパワー解析ツールは、同社のRTL解析ツール「SpyGlass」ファミリ製品の一つ「SpyGlass Power」で、同ツールはパワー解析と合わせて最適化(デザインの修正)も可能でその結果をフォーマル検証で確認できる。また、同ツールはパワー・フォーマットUPFおよびCPFをサポートしており、これらフォーマットで記述されたPower Intentを検証することもできる。

首位のSynopsysは、RTLレベルのパワー最適化ツール「Power Compiler」を提供しているほか、マルチ・ボルテージ・シRTLミュレータ「MVSIM」も提供、その他にもPower解析/最適化のためのESLソリューションも提供している。

Synopsys,Atrenta以外では、Ansys(Apache)が旧Sequence DesignのRTLパワー解析ツール「PowerArtist-XP」を提供、Calypto Design SystemsもRTLパワー解析および最適化ツール「PowerPro」を提供している。

2012.11.08

2012年11月1日、LSIの第三者検証サービスやコンサルティングを手掛ける国内ベンチャーのベリフォアは、自社開発のクロス・カバレッジ・ビューワーをオープンソースとして公開した。

発表によると今回公開したのは「VeriClear」と呼ぶツールで、同社が検証業務(機能カバレッジの確認)で実際に使用しているもの。そもそも、カバレッジ結果をより見易い形で確認したいというモチベーションで開発されたという同ツールは、検証エンジニアの観点で構築されており、カバレッジ・ホールの解析、すなわちカバレッジ・ホールの根本原因の発見を容易にする事が可能。

「VeriClear」は、Accellera標準となったカバレッジ・データベースの標準規格UCDBおよびUCAPIに対応しており、ベリフォアではSynopsysの「VCS」とMentorの「Questa」にて動作を確認しているという。

ベリフォアのクロス・カバレッジ・ビューワー「VeriClear」は、現在下記URLよりダウンロード可能。

https://bitbucket.org/tomoiida/vericlear

2012.11.07

2012年11月6日、Cadenceは、米ファブレス・ベンダのOpen-Silicon社がCadenceのツールフローで28nm ARM搭載チップをテープアウトした事を発表した。

発表によるとOpen-Siliconが開発したのは、モバイル・コンピューティングをターゲットとしたARMデュアル・コア Cortex-A9プロセッサを搭載したSoCで、論理合成を含むインプリメント・フローをCadenceのツールで実施。同フローには、論理合成ツール「RTL Compiler-Physical」、配置配線ツール「Encounter Digital Implementation(EDI)」、寄生抽出ツール「Cadence QRC Extraction」、タイミング解析ツール「Encounter Timing SystemSystem」が含まれている。

Cadenceによると、「Encounter Digital Implementation」には、「GigaOpt」、「Clock Concurrent Optimization」の2つの最適化機能が搭載されており、Open-Siliconはこれら機能を「RTL Compiler-Physical」と併用することでデザインのクロージングを2週間短縮し、従来フローよりも回路面積を10%、クロックツリーの消費電力を33%、回路全体のリーク電力を27%削減、、完成したチップは2.2GHzの性能を達成した。この成果はCadenceによる設計フローの最適化によるもので、これを受けてOpen-Siliconは、研究拠点におけるARM搭載SoCのハードニング向けに、Cadenceのフローを標準採用したという。

2012.11.07

2012年11月6日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、Berkeley Design Automationは、台湾のEpisil Technology社が同社の回路シミュレータ「AFS Nano」を採用したことを発表した。

Episil Technologyは、パワーおよびアナログ半導体とエピタキシャル ウェハを手掛けるファウンドリで、今回アナログおよびパワーデバイスのキャラクタライゼーションにBerkeley DAの「AFS Nano」を採用した。

「AFS Nano」は、年間ライセンスの費用が1900米ドルの低コストな回路シミュレーターで、最高5000素子というキャパシティ上の制限があるため、主にブロック単位のアナログ・シミュレーションをターゲットに利用されている。しかしながら、シミュレーションの精度は上位製品の「Analog FastSPICE」と同じで正確なSPICE精度の高速シミュレーションが可能。Episil Technologyの担当者は、「AFS Nanoは従来ツールに対し10倍以上の価格性能比をもたらす」とコメントしている。

2012.11.07

2012年11月6日、Mentor Graphicsは、PCB設計ツール「PADS」のバージョンアップを発表した。

「PADS」は、Mentorの提供する小規模から中規模のシステム設計に対応するPCB設計ツールで、同社の提供する大規模システム対応のPCB設計ツール「Expedition Enterprise」よりも低コストであり、日本語にも対応。Mentorは世界で最も利用実績のあるPCB設計ツールと謳っている。

今回リリースされた最新の「PADS 9.5」では、ユーザビリティが強化されたほか、対話型配線機能がアップデートされ、簡体字中国語が新たにサポートされた。また、DDRx設計で必要な、スターポイントおよびブランチポイントと呼ばれる仮想ピンが用意され、DDRx設計における配線能力が高められた。更に、「PADS」フローに統合されている回路設計ツール「DxDesigner」のGUIも改善されたという。

2012.11.07

2012年11月6日、レイアウト表示プラットフォーム「LAVIS」を手掛ける日本のEDAベンダTOOL社は、新製品となる「高速抵抗値計算エンジン」の評価版の提供について発表した。

TOOLの発表によると、新製品「高速抵抗値計算エンジン」は、設計データを用いて指定したネットの寄生抵抗の抽出や合成抵抗の計算を行うもので、マルチスレッドにより高速に計算を行うことが可能。設計の早い段階で、PADとブロックの間やESD保護素子と内部回路の寄生抵抗などを見積ることができる。

また、「高速抵抗値計算エンジン」は、TOOL社の提供するレイアウト表示プラットフォーム「LAVIS-plus」と連携可能で、「LAVIS-plus」の等電位追跡を高速に処理できるほか、「LAVIS-plus」上で寄生抵抗ネットリストの出力(SPICE)や、合成抵抗の計算結果の視覚表示なども行う事ができるという。

尚、「高速抵抗値計算エンジン」は、「LAVIS-plus(またはLAVIS)」が無くても単体製品として利用することが可能。正式版のリリースは来春の予定で評価版の提供は今年12月より開始される予定。来週14日から開催される「Electronic Design and Solution Fair 2012 (EDSFair2012)」にて展示される。

2012.11.07

2012年11月6日、米SIA(Semiconductor Industry Association)は、2012年9月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年9月の世界半導体売上は前年同時期比約3.9%減、前月比約2.0%増の247.9億ドルという統計結果となった。これで世界半導体売上の前年割れは16ヶ月連続。今年1月からの売上累計は、2142億5000万ドルで昨年同時期の累計額と比較すると4.7%減となっている。当初の各業界機関の予測に反し2012年下半期も市場の停滞が続いており、四半期単位で見るとQ2(4-6月)売上よりもQ3(7-9月)売上が1.8%増となっているが、Q4(10-12月)も前年割れの可能性が高い。

2012年9月の売上を地域別でみると、北米が8月よりも5.8%増と回復。この数値は2010年5月以来の好結果となる。しかし、全ての市場において売上は前年割れとなっている。

2012.11.07

2012年11月6日、Alteraは、業界初となるOpenCLを用いたFPGAベース・システム開発用のSDK(Software Development Kit)を発表した。

AlteraのOpenCL向けSDKは、CPUとFPGAを用いたヘテロジニアス・システムを開発するための環境で、C言語ベースのOpenCLを用いたFPGAの設計を実現するもの。利点としては、C言語を扱うソフトウェア開発者にも容易にFPGAを用いたシステムを開発できる点、FPGAをCPUのアクセラレータとして利用することで、他のハードウェアを用いるよりも低い消費電力でシステムの処理能力を向上できる点などが挙げられる。

通常、FPGAの設計にはVerilog-HDLやVHDLといったハードウエア記述言語を用いるが、AlteraのOpenCL向けSDKは、HDLによるFPGAの実装を不要とするもので、OpenCLで記述されたC言語から高速化の対象となる並列化可能な関数を自動的にFPGAハードウェア・アクセラレータに変換、FPGA外部へのインターフェースやインターコネクト・ロジックを追加した形でFPGAのコンフィギュレーション・ファイルを自動生成する事が可能。CPU上のホスト・プログラムとFPGAの通信用にOpenCL APIコールにリンクするライブラリも用意されている。

Alteraの実施したベンチマーク結果によると、このOpenCL向けSDKを用いることでビデオ処理アプリケーションの開発期間を数ヶ月短縮した例や、金融アプリケーションの開発において、単一CPUを使用する場合より9倍の性能向上に成功した例などがあるとの事。消費電力に関しては、FPGAベースのソリューションは他のハードウェアに比べて5倍以上の電力効率(1ワット当りの性能)を実現可能としている。

尚、AlteraのOpenCL向けSDKは既に量産移行できる段階にあり、現在、早期アクセス・プログラムの参加企業に提供されているとの事。来週14日から開催される「Embedded Technology/組込み総合技術展 2012」にてデモが披露される予定となっている。

2012.11.06

2012年11月5日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の論理シミュレータ「Riviera-PRO」のバージョンアップを発表した。

発表によると論理シミュレータ「Riviera-PRO」の最新バージョン2012.10では、VHDLのシミュレーション速度が20%向上したほか、SystemVerilog 2009、VHDL 2008の新言語構造、UVM 1.1c、SystemC 2.3.0、OS-VVMのライブラリの最新バージョンがサポートされた。

また、デバッグ機能も強化され、Mathworks社の「Matlab」、Xilinx社の「Vivado」、SpringSoft社の「Verdi」など、各種サードパーティー・ツールとのインタフェースが拡張された。

2012.11.05

2012年9月28日、今回で13回目の開催となるLSI検証技術セミナー「Verify 2012」が新横浜のホテルで開催された。

ここでは、同セミナーでユーザー事例として紹介された「UVMとエミュレータの協調シミュレーションによる検証高速化」について紹介する。同講演を行ったのは、富士通九州ネットワークテクノロジーズ株式会社 システムロジック開発センター 第一開発部の由利英介氏である。

由利氏はハードウェアの開発手法の研究・構築を行い、それを社内に展開する立場の人物で、今回はSystemVerilogベースの検証メソドロジ「UVM」の導入事例ならびに、UVMテストベンチとEVE社のエミュレーターの接続事例について語ってくれた。

※画像は由利氏の講演の様子

由利氏の話によると、QNETでは元々検証メソドロジ「OVM」を利用していたようで(少なくとも由利氏は利用していた)、「UVM」の導入はある意味自然の流れと言える。由利氏が「UVM」を実際使ってみた分かった良い所として挙げたのは大きく下記3点。

・テストベンチがきれいに書ける

・規則性があるのでスクリプトで自動化出来る

・クラスの拡張と置き換えの利便性

由利氏が最も強調していたのは、テストベンチがきれいに書けるという点で、仮に他人が書いたテストベンチであっても整理された記述スタイルにより、テストベンチのバグ原因を突き止めやすい等のメリットがあるとの事。ディレクトリ構成や命名規則などローカルルールを作って運用するのがおすすめと語った。

またQNETでは、規則的な部分をスクリプトで自動化し、検証フレームワークやローカル・ルールで作ったディレクトリ構成などを自動生成することで検証環境の立ち上げ期間を短縮しているほか、DPI(Direct Programming Interface)を用いて検証対象のC言語のリファレンス・モデルを叩き、ダイナイックに期待値を生成することで論理的な期待値一致を完全に自動化。従来手法と比較して検証工数を30%程削減し、現場の検証エンジニアからも「理想の検証環境」と評価を得ているという。

※画像は由利氏の講演データ(以下、全て同様)

しかし便利な「UVM」の導入にも障壁はあると由利氏。

出来るだけ過去の資産を流用したいという設計現場の考えは厚い壁で、仮にそれを乗り越えたとしても、オブジェクト指向に対する「先入観」が「UVM」導入の更なる壁として立ちはだかるとの事。こんな現状に対し由利氏は、「UVM」はオブジェクト指向で難しい「分析と設計」を不要とする業界のノウハウの集大成であるため、オブジェクト指向を恐れることなく利用して欲しいと語った。

続いてUVMテストベンチとEVE社のエミュレーター「ZeBu」との接続に関する話。

由利氏は、検証時間の短縮という誰もが目指す目的の延長線上で、「UVM」の利便性と「ZeBu」の高速性を融合させたいと両環境の接続に挑戦。本来であれば、DUTとテストベンチを全て「ZeBu」に実装する方法が一番高速化が見込めるが、「複雑なテストベンチをZeBuに実装するのは手間がかかる」と、シミュレーター上のテストベンチとDUTを実装した「ZeBu」で協調シミュレーションする形を選んだ。

協調シミュレーションを行うにあたり幾つか必要な作業があった。まず、「ZeBu」ではFPGAのマクロを実装出来ないため、評価対象のデザインからマクロを抜き出す作業を行った。これらの作業は工数にして約3日(1名)で完了し、この状態で信号レベルの協調シミュレーションは容易に実現できた。続いて、トランザクション・ベースのシミュレーションを行うためにトランザクタの設計とテストベンチの修正を行った。

トランザクタの設計には、EVEの用意する合成ツール「ZEMI-3」を用いて合成する方法とEVEの用意するマクロを用いて手設計する方法があるが、前者の場合マルチスレッドの動作制約があるため、今回はマクロ・ベースでトランザクタを設計。具体的にはマクロを制御するFSMとDUTとのI/Fを設計した。これらの作業はFPGAのマクロ対策に加えて更に5日を要した。テストベンチの修正は通信手段の合わせこみとモニタとドライバの修正のみで1日で完了。これらの準備により、シミュレーターと「ZeBu」とシミュレーション・エンジンを簡単に切り替える環境を構築出来た。(あくまでも静的な切り替え)

環境が整ったところで評価を実施。論理シミュレーターと協調シミュレーションとで信号レベル、トランザクション・レベルでのシミュレーション時間をそれぞれ比較してみたところ、当初の想定ほど高速化は実現できなかった。(※下の図を参照)

しかし、「ZeBu」の処理時間を0時間と仮定して高速化の限界値を算出してみたところ、協調シミュレーションによる高速化の結果がさほど悪くないという事が分かった。(※下の図を参照)

また、シミュレーター側のアサーション(SVA)を「ZeBu」に実装した場合でも高速化にに成功。更にトランザクション・レベルのシミュレーションにおいて、1回当たりのデータ転送量を増やすことで高速化が実現できる事も確認した。(※下の図を参照)

由利氏はこれら協調シミュレーションの評価にあたり、高速化のためのテクニックとして、テストベンチとZebu間の通信回数を減らすのがポイントと指摘。具体的な手法として、通信でトランザクタの「Message Inport」を使用せずDPIとZeBu-APIを利用してバックドアでRAMを介して通信する方法を紹介。更にテストベンチの負荷を下げることも高速化のカギとした上で、下記4つのヒントを示した。

・トランザクションの転送量を減らす/転送量を増やす

・できる限りUnTimedにする

・DUTに対するアサーションは出来る限り多い方が良い

・無駄なランダマイズを減らす

2012.11.05

2012年10月31日、LSI機能検証ソリューションを手掛けるCMエンジニアリングは、検証キット「SAQuT!」の新製品「SAQuT!-PCI Express」のリリースを発表した。

今回リリースされた「SAQuT!-PCI Express」は、PCI Express向けの検証環境を構築するための検証キットで、既存の「SAQuT!」シリーズ製品と同様に検証メソドロジ「UVM」に対応しており、再利用可能なSystemVerilogベースの検証環境を短期間で構築し、PCI Expressの単体検証や、PCI Expressインタフェースを持つシステムの検証を効率化できる。CMエンジニアリングの実証データによると、「SAQuT!-PCI Express」を用いる事で検証環境の構築期間を約70%削減できたという。

検証キット「SAQuT!-PCI Express」として提供されるのは、テストシーケンスを作成するためのシーケンスライブラリとサンプルコードで、PCI Expressのレイヤー毎に分けられたエージェントそれぞれに、シーケンサ/ドライバ/モニタ/機能カバレッジモデルが備わっているとの事。また、これら検証モデルと検証環境は全てソースコードで提供され、日本語のユーザガイドが付属。パラメータの設定によりレーン数、データバス幅などユーザー個別のカスタマイズも可能となっている。

※画像は「SAQuT!-PCI Express」の利用例

尚、CMエンジニアリングの提供する「SAQuT!」シリーズ製品は、今回の「SAQuT!-PCI Express」以外に「SAQuT!-AXI3/AXI4(UVM対応版)」や「SAQuT! AMS」などの製品がラインナップされている。「SAQuT!-PCI Express」の詳細については、2012年11月14日より開催されるET/EDSFにて紹介される予定。

2012.11.02

2012年10月31日、業界標準ツール「SpyGlass」をはじめとしたRTL解析ソリューションを手掛けるAtrentaとTSMCは、TSMCの「ソフトIPアライアンス・プログラム」に対するソフトIPの認証キット「IP Kit 2.0」のリリースを発表した。

発表によると「IP Kit 2.0」は、フィジカル・インプリメンテーションの情報やLintチェックの内容などがエンハンスされており、既にTSMCのソフトIPアライアンス・パートナーのDigital Media Professionals、Dolphin Integration、Sonics、Vivanteによって評価が完了済。TSMCは来月11月20日からソフトIPアライアンス・パートナー向けにオンラインで同キットのサポートを開始する予定となっている。

既に両社が開発したソフトIP認証キットの利用ベンダは15社にのぼるという事だが、このキットを用いてTSMCの認証を受けたIPの各種コード解析データは、TSMCのオンライン・ライブラリで公開されている。

2012.11.02

2012年10月30日、測定器メーカーのTektronixは同社のソフトウェア・ツール「Certus」をバージョンアップを発表した。

Tektronixの提供する「Certus」は、同社が2011年に買収したVaridaeSystems社が開発したASICおよびFPGAのデバッグ・ツールで、RTLにプローブを挿入することで完成したチップ内の信号の観測を可能とするもの。

Tektronixの発表によると、最新の「Certus」バージョン2.0は、シミュレーターと同等の視覚化環境でRTLのレベルでFPGA内部の信号を観測可能。一つのFPGA当たり10万の信号を動作速度で観測可能で、各信号の種類を自動的に識別する事もできる。また、特に対象とするFPGAデバイスやFPGAボードの種類、動作周波数は問わず、複数のFPGAを搭載したボードにも対応しており、特別な拡張ボードや専用ケーブルも不要でFPGAのI/Oリソースを食う事もない。

Tektronixは、発表した「Certus」の最新バージョンをASICプロトタイピングのデバッグ・フローを変えるソリューションとしてアピールしており、ASICプロトタイピング・ボードを手掛けるDiniグループ社のMike Dini社長も「Certus」を利用することで、をASICプロトタイピングのデバッグ作業を数分の1に短縮できるとコメントしている。

Tektronixの「Certus」は、1年間のフローティング・ライセンスで19,500ドル。(米国内の販売価格)日本国内での取り扱いについては不明。

2012.11.01

2012年11月1日、Cadenceは、ARM,IBMとの協業により、IBMの14nm FinFETプロセス・テクノロジを使用し、ARMのCortex-M0プロセッサを実装したテストチップのテープアウトしたことを発表した。

発表によるとARM,Cadence,IBMの3社は、14nm以下の先端プロセス・ノードを用いたSoC開発に向けた複数年契約を交わしており、今回のテストチップのテープアウトは、その重要なマイルストーンの一つ。

テストチップは、14nm設計向けに構築された基礎IPブロックを実証するために開発されたもので、Cadenceの「Encounter Digital Implementation System」と「Virtuoso」で設計した「ARM 8-track 14nm FinFETスタンダードセル・ライブラリ」を使用してインプリメントされた。テストチップには、ARM Cortex-M0プロセッサの他にSRAMメモリ・ブロックなど幾つかのブロックが実装されており、テストチップから得られる各種キャラクタライゼーション・データは今後ARMのフジカルIP「Artisan」の開発に活かされる。

今回のテストチップの開発にあたり、CadenceとARMは、IBMのFinFETテクノロジをベースとした設計メソドロジを共同で構築。14nm FinFETプロセスを用いるチップの設計を行うためには、プロセスのサポートの他にFinFET向けのルール・デッキやタイミング解析の強化が必要でCadenceのツール群がこれに対応。具体的には「Encounter Digital Implementation System」、「Encounter Power System」、「Encounter Timing System」、「Cadence QRC Extraction」が設計メソドロジの構築に利用された。同設計メソドロジには、FinFETテクノロジがもたらす消費電力と性能を実現するための新しいGigaOpt最適化テクノロジ、製造で実証済のダブルパターニング修正機能、14nm FinFET構造をサポートするタイミングおよび消費電力のサインオフ機能が含まれているという。

2012.11.01

2012年10月31日、SoCインターコネクト設計ソリューションを手掛ける仏Arterisは、日本のジョイント・ベンチャー、アクセスネットワークテクノロジ株式会社が同社のインターコネクトIP「C2C」を採用した事を発表した。

発表によるとアクセスネットワークテクノロジは、アプリケーション・プロセッサとLTEモデムをターゲットとするスマートフォン向けのSoC開発にArterisのインターコネクトIP「C2C」を採用。アクセスネットワークテクノロジの坂田 稔社長はその採用理由を「プロセッサ-モデム間接続のデファクトだから」とコメントしている。

Arterisの「C2C」はチップ間接続IPとして携帯関連各社が採用しており、同IPを用いることで、プロセッサとモデムのメモリの共有化を図り、SoCの低コスト化と少面積化を実現できる。

アクセスネットワークテクノロジは、今年8月に富士通が設立した携帯向けのモデムチップを開発するファブレス・ベンダで、NTTドコモ、NEC、富士通セミコンダクターの3社が出資している。

2012.11.01

2012年10月30日、SoCインターコネクト設計ソリューションを手掛ける仏Arterisは、ルネサス エレクトロニクス・ヨーロッパ社が同社のインターコネクトIP「FlexNoC」を採用した事を発表した。

発表によるとルネサス・ヨーロッパは、複数の産業用SoCにArterisのインターコネクトIP「FlexNoC」を採用。今回の採用は、SoCのパフォーマンス向上と、SoCに搭載するIPの増加に伴うインプリメント及びデバッグ工数の削減を目的としたものだったという。

尚、Arterisによると、同社はその業績の伸びの高さから、San Jose Business Journal誌のシリコンバレー成長企業ランキングで4位にランキングされたとの事。10月16日に発表されたプレスリリースによると、同社の2009年から2011年の売上成長率は861.1%、調査会社Gartnerの調べでは、Arterisは世界IPベンダ・ランキングで11位、IPベンダTOP20の中でインターコネクトIPを手掛けるのはArterisだけだという。

2012.10.31

2012年10月25日、e/SystemVerilogも扱えるフロントエンド環境を手掛けるルーマニアのEDAベンダAMIQは、同社のIDE「DVT」の機能強化を発表した。

AMIQの発表によると、今回の機能強化で「DVT」で複数言語を用いたデザイン・プロジェクトを取り扱う事が可能に。「DVT」は元々e/SystemVerilog/Verilog/VHDLの4種の設計および検証言語をサポートしており、複数言語を用いたデザインを扱う事が出来たが、一部の編集およびナビゲーション機能に関しては、そのサポート範囲が単一言語に限定されていた。

AMIQが今回公表した新機能としては、SystemVerilog/Verilog/VHDLの混合ソースにおける言語を跨いだハイパーリンク、デザイン階層のブラウジング、信号トレースなどがあり、例えばあるVerilogの中のモジュール・インスタンスをクリックして、VHDLの定義にジャンプしたりできるという。

AMIQはレガシー・コードと新たな言語が存在する現在の設計を考慮し、引き続きクロス・ランゲージ機能の強化に取り組み続けるとしている。

2012.10.31

2012年10月16日、TSMCはカリフォルニア州サンノゼにて「TSMC Open Innovation Platform (OIP) Ecosystem Forum」を開催し、20nmおよびCoWoS (Chip on Wafer on Substrate)、新たな2つのリファレンス・フローの詳細を発表(関連記事)。それに伴い同社のパートナー企業を称える「TSMC Partner of the Year 2012」を発表した。

現時点でアナウンスされている「TSMC Partner of the Year 2012」の受賞企業および受賞部門は以下の通り。

・Ansys(Apache)

-「Joint Delivery of the 20-Nanometer Reference Flow」部門

・Cadence

-「CoWoS Design Enablement and Test Vehicle Development」部門

-「Joint Delivery of the 20-Nanometer Reference Flow」部門

・Mentor Graphics

-「CoWoS Design Enablement and Test Vehicle Development」部門

-「Joint Delivery of the 20-Nanometer Reference Flow」部門

・Synopsys

-「Joint Delivery of the 20-Nanometer Reference Flow」部門

※Synopsysは、「TSMC Interface IP Partner of the Year」も合わせて受賞している

2012.10.31

2012年10月30日、Synopsysは、同社のARM AMBA 検証IP向けの新機能「Performance Checker」のリリースを発表した。※訂正あり

Synopsysによると、今回リリースした「Performance Checker」は「ARM AMBA AXI4」向けの文字通り性能解析ツールで、インターコネクト上で発生するレイテンシのトラッキングを行う事で、システム・アーキテクチャ定義の段階で設定された性能指標に対して実際のデザインが性能を満たすかどうかチェックし、性能に影響を及ぼすボトルネックを特定する事ができる。アウトプットとしてはレポートが出力され、デザイン中の問題箇所はSynopsysが検証IP用に提供しているプロトコル考慮のデバッグ環境「Protocol Analyzer」上でハイライト表示する事が可能、デバッグ作業に生かすことができる。

また、「Performance Checker」の利用にあたり、Synopsysのバーチャル・プロトタイピング・ツール「Platform Architect」で見積もった性能指標を制約条件として検証IPに渡す事が可能で、同制約条件をベースに「Performance Checker」を利用すれば、システム性能の一貫性を維持した形の設計フローを実現できる。

2012.10.31

2012年10月26日、Cadenceは自社の提供するARM AMBA 検証IPの実績をアナウンスした。

Cadenceのアナウンスは、10/30よりカリフォルニア州サンタクララで開催されたARMのイベント「ARM TechCon 2012」に合わせたものと思われるが、Cadenceによると、同社の検証IPソリューション「VIP Catalog」にラインナップされている「ARM AMBA プロトコル用検証IP」を使用して、CEVA、Faraday Technology、HiSiliconなどの複数の企業が検証期間の短縮に成功。CEVAの例では、これまで6か月要していた検証期間を3週間にまで短縮できたとの事。

CadenceはARMとの密接な協業により、既に最新のAMBA 4プロトコルを使用したARM CoreLinkインターコネクトIP向けの検証IPを提供しており、同検証IPを含むCadenceのARM AMBA プロトコル用検証IPファミリはシミュレーション、アサーション、ハードウェアエミュレーションなど各種検証メソドロジに対応している。

2012.10.30

2012年10月26日、Mentor Graphicsは、同社の組込みソフトウェア開発環境「Sourcery CodeBench」によるQualcomm「Hexagon」アーキテクチャーのサポートを発表した。

Mentorの「Sourcery CodeBench」は、GNUツールベースのC/C++開発環境で組込みソフト開発の世界では最も採用数の多い開発環境とされている。今回その「Sourcery CodeBench」がQualcommの「Hexagon DSPアーキテクチャ」のコード生成をサポート。これは商用GNUツールチェーンとして業界初となるという事で、半導体ベンダとして世界5位、ファブレス半導体ベンダとしては業界トップのQualcommが提供する、Snapdragonプロセッサに搭載される「Hexagon DSP」の開発を支援する。

また、MentorはHexagonを採用する顧客に対して、コンサルティングを含む商用サービスも提供するようだ。

2012.10.30

2012年10月29日、フォーマル検証ツールを手掛ける米Jasper Design Automation社は、新たな「JasperGold Apps」として、2つのプロパティ生成アプリのリリースを発表した。

Jasperは、論理検証における様々な個別の問題に特化した専用ツールとして6種類の「JasperGold Apps」を今年5月にリリース(※関連記事)していたが、今回新たにリリースしたのは、「Structural Property Synthesis App」と「Behavioral Property Synthesis App」の2つ。

「Structural Property Synthesis App」は、よくある機能的なエラーを自動的にチェックするツールで、必要となるのはVerilogまたはVHDLで記述されたRTLのみ。ツールがRTLを解析し、内蔵するデッドコードチェック、FSMチェック、アリスメティックオーバーフローチェックといった数種類の機能チェックを行い、デザインの構造的なプロパティを自動生成する。生成されるプロパティは、ランキングや分類分けされ、SVAで出力されるため、Jasperのフォーマル検証環境に限らず市販のシミュレーターやエミュレーターでも利用可能。デザイン初期のデバッグだけでなく、RTLサインオフ時にも利用効果を得る事ができるという。

「Behavioral Property Synthesis App」は、RTLとシミュレーション結果(FSDB/VCD)から、デザイン中のカバレッジ・ホールを抽出し、機能カバレッジを向上させるための、アサーション、制約、カバーといったプロパティを自動生成するツールで、複数のサイクルにまたがる時系列的なプロパティや異なる階層の異なるモジュール間の信号関係についてプロパティを生成することが可能。「Structural Property Synthesis App」と同じく生成されるプロパティはランキングや分類分けされるため、効率的なフォーマル検証を実現し、機能カバレッジの向上、検証の収束に寄与する。

発表によるとSTARC(株式会社半導体理工学研究センター)は、既に今回リリースされた2種類の「JasperGold Apps」を評価しており、同ツールは「デザインに役立ち、シミュレーションだけでは難しい検証環境の質的向上を実現する」とコメントしている。

2012.10.29

2012年10月25日、バーチャル・プラットフォーム「OVP」を手掛ける英Imperasは、新たなARM製プロセッサ・モデルのリリースを発表した。

Imperasが発表した新たなプロセッサ・モデルは、ARM Cortex-A15, Cortex-R4, Cortex-R4F, ARM1176の4種類。これらモデルはImperasの提供するTLM2.0ベースのバーチャル・プラットフォーム「OVP」上で利用する事が可能。バーチャル・プラットフォーム用のプロセッサ・モデルはEDAベンダ各社が提供しているが、ARM Cortex-A15、ARM Cortex-R4、Cortex-R4Fモデルの全てを提供するのは、現時点でImperasとSynopsysだけとなっている。(関連各社Webサイト上の情報から推測)

ちなみに、業界で一番初めにARM Cortex-A15モデルを提供開始したのは、Carbon Design Systemsである。

2012.10.29

2012年10月24日、SoCのテストケース自動生成ツールを手掛けるBreker Verification Systemsは、同社ツール「TrekSoC」がヘテロジニアス・マルチコア・プロセッサをサポートしたことを発表した。

「TrekSoC」は、SoC向けにセルフ・チェック用のCのテストケースを自動生成するツールで、今回同ツールがヘテロジニアス・マルチコア・プロセッサ向けのテストケースの生成をサポートした。この新機能は10/30からサンタクララで開催される「ARM TechCon 2012 」にて展示される予定。

Breker Verification Systemsは売上好調で2011年は前年比150%増を達成。ユーザーとしては、NVIDIA、STMicroelectronics、IBM、Broadcom、Qualcommら大手が名を連ねている。また同社は今年7月に、アジアの投資会社Astor Capital Groupから500万ドルの出資を受けている。

2012.10.29

2012年10月25日、Xilinxは同社の提供する専用設計ツール「Vivado Design Suite」のバージョンアップを発表した。

発表によると「Vivado Design Suite」の最新バージョン2012.3は、28nmFPGAのミッドレンジ製品「Kintex-7」の新たなリファレンス・デザインが4種類追加された他、マルチコア・プロセッサ・ワークステーションでの実行がサポートされ、新技術「マルチスレッド・プレース・アンド・ルート」によって、配置配線処理のランタイムがデュアルコアで1.3倍、クワッドコアで1.6倍高速になった。

2012.10.29

2012年10月23日SoCインターコネクトIPを手掛ける米Sonicsは、NoCの新製品「SonicsGN」のリリースを発表した。

プレスリリース文

http://sonicsinc.com/blog/2012/10/sonics-unveils-next-generation-sonicsgn/

発表によると「SonicsGN」は、Sonic4世代目の製品となるネットワーク・オン・チップIPで、I/Oコヒーレンシ、マルチチャネル・メモリ・インターリービング、セキュリティ・ファイアウォールといった特徴をアピール。「クラウドに繋がるデバイスのSoCに向けたNoC」と謳われる同NoCは、業界初かつ業界最高のGhzクラスの動作周波数を実現しており、モバイル・デバイスで圧倒的なシェアを誇るARMのTrustZoneのセキュリティ・ポリシーをベースとしたファイアウォール機能を備えているという。

尚、Sonicsは、先日10月16日に発表されたSonicsのプレスリリースによると、同社のNoCを使ったチップの出荷数は累計20億個に到達したという事だ。

2012.10.26

2012年10月22日、Synopsysは、同社の「IC Validator」がUMC 28nmプロセスのフィジカル検証サインオフ・ツールとして認定されたことを発表した。

UMCは28nmプロセスのリファレンス・フローにおいてSynopsysの配置配線ツール「IC Compiler」と寄生抽出ツール「StarRC Extraction」を既に認定しており、今回新たに「IC Validator」を認定。「IC Validator」は、「IC Compiler」と協調したDRC検証「インデザイン・フィジカル検証」が可能で両ツールをセットで利用するユーザー例は少なくない。

また、「IC Validator」は、DRCで用いるランセットの作成や維持・管理において独自のプログラマブルな言語「PXL」を用いる事で効率化を測っており、UMCは同メリットについても評価。「IC Validator」によって記録的な速さで28nmプロセスのランセットを作成出来たとコメントしている。

尚、UMCは、28nmプロセス向けの組込みメモリやロジックIPの開発でコラボレーションするなど、Synopsysとは強力な協業体制を敷いている。

2012.10.26

2012年10月25日、Mentor Graphicsは、新製品「HyperLynx DRC」のリリースを発表した。

発表によると「HyperLynx DRC」は、Mentorの伝送線路解析ツール「HyperLynx」ファミリ製品の主要ラインナップに位置づけられる新製品で、PCBレイアウト・データのデザインルール・チェックを行うツール。同ツールには、コード化された標準ルールが装備されており、ハイスピード設計に共通するレイアウトの問題をチェックする事が可能。標準ルールは、パラメータの変更によってユーザーがカスタマイズできる。

また「HyperLynx DRC」はPCBレイアウトの作業中に実行可能で、Mentorの提供する「Expedition Enterprise」、「Board Station」、「PADS」、Cadenceの「Allegro」、図研の「CRシリーズ製品」など市販の主要PCBレイアウト・ツールとの互換性を備えている。

2012.10.25

2012年10月19日、Mentor Graphicsは、同社の機能検証プラットフォーム「Questa」におけるフォーマル検証技術の強化を発表した。

発表によるとMentorは今回、2004年に買収した0-in社の技術をベースとした複数のフォーマル技術の最新版を機能検証プラットフォーム「Questa」に追加した。

そのうちの一つ、「Questa CoverCheck」は、フォーマル技術を用いて100%のコード・カバレッジを達成できるビンと達成できないビンを自動的に識別する機能で、コード・カバレッジの収束を高速化するだけでなく、コード・カバレッジのビンが誤って検証プロセスから漏れてしまうミスを防ぐ事ができるという事。また「Questa CoverCheck」は、何百ものリグレッションのカバレッジをマージしたカバレッジのデータベース「UCDB」を読み込み、その中からカバーできていない部分を見つけ、そこをカバーするためのパターンを半自動で生成するという機能もあり、これら機能を用いればコード・カバレッジにおける人手の作業を大幅に削減できる。

「Questa AutoCheck」は、フォーマル検証ツール「Questa Formal」に新たに搭載された機能で、検証対象のデザイン(RTL)のみを読み込んでアサーションを生成し、テストパターンに依存せずにデッドロックなどの一般的な機能エラーを検証する事が可能。テストパターンやアサーションを必要としないため、RTLを書いたその場ですぐに利用可能で、網羅的にコーナーケースのバグを検出する本格的なフォーマル検証を行う前に、デザインの基本的なバグをチェックできる。(※同機能は元々0-in Formalに搭載されていた)

Mentorによると、その他にも「Questa Formal Multi-Core」と呼ぶフォーマル検証作業を複数のコアやコンピュータに分散できる新しい機能が「Questa」プラットフォームに追加されたほか、CDC(Clock-Domain Crossing)検証ツール「Questa CDC」もエンハンスされ「Questa」プラットフォームに追加された。「Questa CDC」は性能向上によりチップ・レベルのCDC検証も可能となっており、そのキャパシティは無制限だという。

Mentorは、昨年まで各種フォーマル検証ツールを「0-in」シリーズ製品として販売していたが、それら各ツールおよび各機能を全て「Questa」プラットフォームに統合し、より包括的な機能検証プラットフォームを実現したというのが今回のリリースの主旨であろう。

※メンター・グラフィックス・ジャパン株式会社

2012.10.25

2012年10月24日、Cadenceは、2012会計年度第3四半期(2012年7-9月)の売上を報告した。

Cadenceの2012年Q3売上は、前年同時期比約16%増、前期Q2(12年4-6月)と比較して約4%増の3億3900万ドル。純利益は5900万ドルで前年比60%増だった。(※GAAP基準による会計結果)

Cadenceはこれで11四半期連続で売上前年比増を記録。Q3の純利益はこの2年間で最も大きかった。

Cadenceの好調な業績は継続される見通しで、Cadenceは次期2012年Q4の売上を今期実績を更に上回る3億3500-4500万ドルと予測。前期Q2に続いてまたしても2012年の年間売上予測を13億1500-13億2500ドルと上方修正した。

2012.10.24

2012年10月23日、Mentor Graphicsは、フランスのファブレス半導体ベンダKALRAY社が同社のEDAツールを用いて256コア、1億6000万ゲートの28nmSoCを設計した事を発表した。

発表によるとKALRAYの開発したSoC「MPPA-256」は、256個のコア、47MBのメモリを搭載する30億トランジスタのプロセッサで28nmプロセス技術で実装。複数のコアが高速/低遅延のNoCで接続されており、並列処理を行いながら互いに通信しあうシステムとなっている。同SoCのターゲットは、画像処理、信号処理をはじめとする様々な分野の組込みコンピューティング市場で、Interlakenインタフェースで複数の「MPPA-256」をPCBレベルで相互接続し処理性能を向上させることもできる。

KALRAYはこの「MPPA-256」の設計にあたり、下記数種のMentor製ツールを使用した。

・機能検証プラットフォーム「Questa」および「Questa Verification IP Library」

→Questaを使用してOVMベースの機能検証メソドロジを実現

・配置配線ツール「Olympus-SoC」

・物理検証ツール「Calibre nmDRC」、「Calibre nmLVS」

→最大で160個のCPUを稼働したマルチスレッド・モードでDRCを実行

・DFTツール「Tessent」

2012.10.24

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2012.10.24

2012年10月23日、Alteraは2012会計年度第3四半期(12年7-9月)の売上を報告した。

発表によるとAlteraの2012年Q3(12年7-9月)売上は、前年比約5%減、前期Q2比約6%増の4億9500万ドル、営業利益は前年比約14%減、前期Q2比11%増の1億7715万ドルだった。これでAlteraは5四半期連続で売上前年比2ケタ減となったが、2四半期連続で売上、営業利益共に前四半期実績を上回り業績回復の兆しを強めた。

AlteraのQ3売上を地域別で見ると北米および欧州市場が持ち直した形で、日本市場だけは前Q2よりも売上が落ちた。製品カテゴリ別では新製品と主力の旧世代製品がそれぞれ伸びを見せた。分野別では各分野がそれぞれ前四半期よりも売上を伸ばした。

Alteraは28nm製品を計画通り出荷しており、9月には次世代の20nm製品における新技術についてアナウンスを行った。また、Alteraは昨年に続きForbes社の100 most innovative companies 2012に選出されている。

2012.10.23

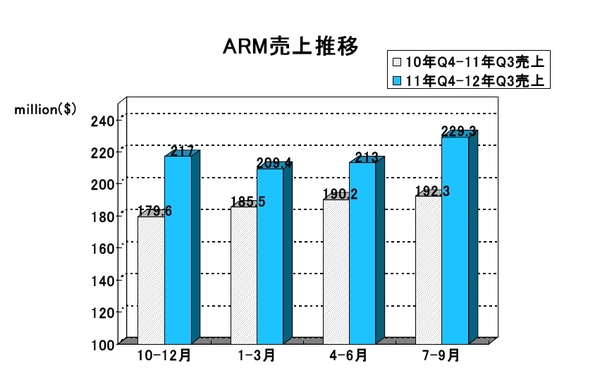

2012年10月23日、ARMは、2012会計年度第3四半期(2012年7-9月)の売上を報告した。

ARMの2012会計年度Q3の売上は、前年比18%増、前期比7.6%増の2億1300万ドルで営業利益は前年比約22%増の約1億920万ドルだった。売上の内訳を見るとライセンスの売上が前年比約15%増の8340万ドル、ロイヤリティの売上が前年比約25%増の1億2110万ドルだった。ARMは2010年Q1より四半期売上の前年増を継続しており、今期Q3で11四半期連続で売上前年増となった。

ARMはこのQ3で前Q2を上回る計29件のプロセッサ・ライセンスを獲得。その内10件は新規顧客によるライセンス契約であり、29件の契約には次世代 64ビットARMv8アーキテクチャ・ライセンス、ARMv8プロセッサー・ライセンス、現ハイエンドCortex-A15プロセッサー・ライセンスが各1件、GPU Maliのライセンスが3件含まれていたという。また、フィジカルIPのPOP(Processor Optimisation Packs)の契約も4件あった。

※画像はARM発表資料より抜粋

2012年Q3で出荷されたARM搭載チップの総数は約22億個で、うち半数はスマートフォンなどのモバイルデバイス向けだった。プロセッサの種類別で見ると、前出荷数に対するCortexシリーズの出荷数が計34%と前Q2の30%より4ポイント増えた。また、新たにGLOBALFOUNDRIESが20nmおよび14nm FinFETプロセスにて契約を行い、半導体ファウンドリとの各種プロセス・ノード別のプラットフォーム・ライセンスの総数は計96となった。

※画像はARM発表資料より抜粋

2012.10.23

2012年10月23日、Cadenceは、同社のICパッケージ・ツール「Allegro Package Designer(APD)」、および「Cadence System-in-Package Layout(SiP)」の機能強化を発表した。

発表によると今回Cadenceは、スマートフォン、タブレット端末、超薄型ノートパソコンなどコンシューマ用携帯端末製品の開発ニーズを睨み、「Allegro 16.6 Package Designer」および「Cadence SiP Layout」に新機能を追加。更に、今年7月に買収したSigrity社の各種パッケージ設計技術も統合し、包括的なICパッケージ設計・解析ソリューションを実現した。これらソリューションにより、ICパッケージ設計とPCB設計のより効率的な協調設計が実現できるという。

「Allegro 16.6 Package Designer」および「Cadence SiP Layout」で実現した主な新機能、強化機能は以下の通り。

・ダイ配置のためのオープン・キャビティ・サポート

・新しいワイヤーボンド・アプリケーション・モードによる設計効率の改善

・wafer-level-chip-scale-package (WLCSP)機能の強化

・Sigrityの技術をベースとしたパッケージ自動配線機能の統合

・Sigrityの技術をベースとしたパッケージ評価、モデル抽出、シグナル/パワー・インテグリティ解析機能の統合

新しい「Allegro 16.6 IC パッケージ・ソリューション」は、2012年の第四半期に提供が開始される予定。

2012.10.23

この度、ystemC Japan 公式サイトの活性化ならびに、SystemCを取り巻くユーザーコミュニティの拡大を目指し、「SystemC Japan公式サイト流会」と称した懇親会を開催することになりました。

これまでは年1回、SystemC Japan 開催時のみの懇親会でしたが、後は四半期に1回程度懇親会を開催し、国内の幅広いSystemCーザーの皆様の交流にお役に立てればと考えております。

つきましては、以下の通り第一回交流会を開催致しますので、SystemCを中心とした業界内の交流にご興味お持ちの方は是非ふるってご参加下さい。

※処々の事情により、ご案内が遅くなりました事をこの場をお借りしてお詫び申し上げます。

------------------------------------------------------------------------------

■SystemC Japan 公式サイト交流会

日時:2012年11月2日(金)

19:00?21:00

会場:新横浜:ELVIS CAFE エルビス カフェ

http://kingcreole.jp/

会費:4000円(料理+2時間飲み放題)

参加:SystemC Japan講演者様、SystemC Japan公式サイト運営会社、

SystemC Japan公式サイト一般登録者様ほか、SystemCに興味をお持ちの方等

先着40名程度(予定)

幹事:事務局菰田

※参加をご希望の場合はその旨 info@systemcjapan.com までメールでご連絡お願い致します。

SystemC Japan 公式サイト 運営事務局

※写真の人物がStan氏、IEEEのドキュメントより抜粋

※写真の人物がStan氏、IEEEのドキュメントより抜粋 ※写真の人物がStan氏、IEEEのドキュメントより抜粋

※写真の人物がStan氏、IEEEのドキュメントより抜粋

-thumb-600x408-2306.jpg)

-thumb-600x417-2308.jpg)

-thumb-600x383-2300.jpg)