NEWS

2013.01.31

2013年1月29日、SoCインターコネクト設計ソリューションを手掛ける米Arterisは、同社のインターコネクトIP「FlexNoC」を日本のファブレス・ベンダであるメガチップスがライセンスしたことを発表した。

発表によるとメガチップスは、最新の画像処理SoCの開発でArterisのインターコネクトIP「FlexNoC」を採用。同社は以前、2つの異なるチップを1つの共有メモリに接続するArterisのインターコネクトIP「C2C(Chip to Chip Link)」を採用した経験を持つが、今回の「FlexNoC」の採用は、画像処理SoCの面積ならびに消費電力の要件を満たすために決定されたもので、低電力かつリアルタイムなレスポンスを実現する唯一の選択肢だったという。

また、メガチップスはパフォーマンスだけでなく、「FlexNoC」に内蔵されるシミュレーション・モジュール「FlexExplorer」についても高く評価。同モジュールから出力されるSystemCモデルをSynopsysのバーチャル・プラットフォーム「Platform Architect MCO」で利用し、システムレベルの解析や社内および顧客とのコミュニケーションに活かしているという。

2013.01.30

2013年1月28日、FPGAベースのプロトタイピング・ソリューションを手掛ける米S2Cは、同社の提供するプロトタイピング・ボードのオプション・製品として、新たに13種類のインタフェース・カードとアクセサリをリリースした。

「Prototype Ready Library」と呼ばれるS2Cのインタフェース・カードとアクセサリは、同社の最新のVirtex-7搭載プロトタイピング・ボード「Virtex-7 TAI Logic Module Series」で利用可能なオプション製品で、これらを利用する事で様々なインタフェースを備えたSoCのプロトタイピング環境を迅速に構築することが可能。具体的なラインナップは以下の通り。

・2 Channel Gigabit Ethernet PHY Interface Module

・4-Lane PCIe Gen2 GTX Module

・4 Channel Transceivers on SMA GTX Module

・Xilinx Zynq ZC702 Interface Module

・2 Channel 1GB DDR3 on SO-DIMM Memory Module

・HDMI Transmitter Interface Module

・Embedded Peripheral Interface Module Type A

・Embedded Peripheral Interface Module Type B

・Interconnection Module Type V

・Interconnection Module Type HQ

・I/O Level Shifting Module Type D

・GTX I/O Testing Module

・Power Expansion Module

S2Cでは今回リリースの製品を含めて計60種類以上の「Prototype Ready Library」を提供しており、それらは世代を問わずS2Cのプロトタイピング・ボードで利用できる。

2013.01.29

2013年1月28日、Cadenceは、Cadenceが20nm以降の先端プロセスに特化したカスタム/アナログ設計環境「Virtuoso Advanced Node」を発表した。

発表によると、新製品「Virtuoso Advanced Node」は、20nm以降の先端プロセスに特化して開発されたカスタム/アナログ設計ツールで、Cadenceの「Virtuoso」上に構築される個別の製品。当然ながらCadenceのデジタル・インプリメント・ツール「Encounter」、「寄生抽出ツール「Cadence QRC Extraction」、フィジカル検証ツール「Cadence Physical Verification System」と併用する事で先端ミックスシグナル・チップの開発を実現可能。

「Virtuoso Advanced Node」の大きな特徴の一つとして挙げられるのが、「LDE(レイアウト依存効果)解析」と呼ばれる解析機能で、同機能を用いることで設計の進捗に応じたフィジカル・チェックが可能。部分的に完成されたレイアウトを設計者が使用できる機能により、設計の後半の最終的なチェックを待たずに、設計の早期段階でストレスによる影響、ポリおよび拡散の領域や長さ、ウェル近接効果、そして寄生素子などのレイアウト依存効果を検出できるという。

また、「Virtuoso Advanced Node」はダブルパターニングとそれに伴うカラーを考慮したレイアウトが可能なほか、ファウンドリの個別の複雑なローカル・インターコネクトのルールに対応した配線も可能だという。

Cadenceは先端プロセス向けのデジタル・インプリメント・ソリューションで巻き返しを図っており、ここ最近その成果着々と積み上げているように見受けられる。同社の牙城とも言えるカスタム/アナログ設計ソリューション「Virtuoso」ファミリに新たに加わった今回発表の「Virtuoso Advanced Node」は、先端プロセス向けソリューションとして強力な武器になるであろう。

2013.01.29

2013年1月28日、EDAツール用の各種機能コンポーネントを手掛ける米Verific Design Automationは、同社の2012年の業績を発表した。

Verificによると同社は2012年、前年比20%増の売上を達成。その金額については非公開。2012年を通じてIDMおよびEDAベンダなど6社の新規顧客を獲得したとの事で、現在同社のアクティブな顧客数は52社。主力製品のSystemVerilog、VerilogおよびVHDLのパーサー、中でもSystemVerilogのパーサーが売上増に大きく貢献していると思われる。

同社のHDLパーサーは、パワー・フォーマットUPFもサポートしており、C++およびPerlのAPIが提供される。

2013.01.29

2013年1月22日、Synopsysは、同社のPCell (PyCell) API技術をIPL Allianceに寄贈したことを発表した。

今回Synopsysが寄贈した技術は、同社が昨年7月に買収したCiranova社が開発した技術で、OpenAccessベースのパラメトリック・セル「PyCell」のAPIに関するもの。IPL Allianceは、ツール環境に依存しないオープンかつインターオペラビリティなPDK標準「iPDK」に同技術を活かす。

CiranovaはOpenAccessベースのPCell作成環境「PyCell Studio」を提供していたEDAベンダで、Synopsysと共にInteroperable PDK Libraries (IPL) Allianceの創立メンバーの一員として名を連ねていた。Synopsysは「PyCell」の作成環境であるCiranovaの開発したツール「PyCell Studio」についても無償提供しており、同ツールはSynopsysのWebサイトから無料でダウンロードできる。

2013.01.29

2013年1月24日、フォーマル検証技術をベースとした検証ツールを手掛ける米Real Intent社は、SDCのマネジメント及び検証ツール「Meridian Constraints」のバージョンアップを発表した。

発表によると「Meridian Constraints」の最新版ではSDC(タイミング制約)の等価性がトップ・レベルとブロック・レベルで比較検証できるようになったほか、検証エンジンのエンハンスにより処理速度が向上、更にSystemVerilogもサポートされた。また、Synopsysのデバッグ環境「Verdi」とのインテグレーションも実現された。

「Meridian Constraints」の最新版は既に利用可能な状態にある。

2013.01.25

2013年1月22日、アナログ/ミックスドシグナル設計統合環境およびMEMS向け設計環境を手掛ける、Tanner Research社のEDA事業部Tanner EDAは、スタートアップ企業向けの特別支援プログラムの開始を発表した。

発表によるとTanner EDAは、自社製品を開発するスタートアップ企業を対象に、同社のアナログ/ミックスシグナルICおよびMEMS向け統合設計環境「HiPer Silicon」の1年間タイムベースライセンスを特別価格で提供。スタートアップの製品開発を支援する。

Tanner EDAの「HiPer Silicon」には、回路図エディタ、SPICEシミュレータ、波形表示ビューア、レイアウトエディタ、パラメトリックセル、スケマティックドリブンレイアウト、オンラインDRC、ノードハイライト、DRC、LVSといった各設計機能が包括的にパッケージされており、アナログ/ミックスシグナルICおよびMEMSの設計を一通り行うことができる。

尚、同支援プログラムの有効期間は2013年6月30日まで。公的な組織やデザインハウス、ジョイントベンチャー・スピンアウトなどは利用できない。

2013.01.25

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2013.01.25

2013年1月23日、Alteraは2012会計年度第4四半期(12年10-12月)の売上を報告した。

発表によるとAlteraの2012年Q4(12年10-12月)売上は、前年比約4%減、前期Q3比約11%減の4億3940万ドル、営業利益は前年比約14%減、前期Q3比22%減の1億3781万ドルだった。これでAlteraは6四半期連続で売上前年比2ケタ減。2012会計年度はQ2,Q3と業績回復の兆しを見せていたが、他の大手半導体の業績と同様にこのQ4は売上を落とした。

最終的にAlteraの2012年度の売上合計は12億4151万ドルで前年比約15%減、営業利益は5億9123万ドルで前年比約30%減となった。

AlteraのQ4売上を地域別で見ると北米、欧州、日本、アジアと全ての市場で売上前年割れで、中でも最大市場のアジアの売上が前年比21%減と大きく落ち込んだ。2012年全体で見ると欧州以外の地域は全て前年割れで一番落ち込んだ日本は前年比19%減だった。

製品カテゴリ別では全体的に売上を落とす中、新製品だけはQ4で前年比11%増、2012年全体で前年比39%増と大きな伸びを見せた。これは最新の28nm製品の売上、中でも低消費電力のミッドレンジFPGA「Arria V」の売上が大きく寄与しているようだ。

Alteraは次期2013年Q1(1-3月)の売上を2012年Q4の4-8%減と予測している。

2013.01.24

2013年1月23日、Caenceは、Avago Technologiesによる同社製品の採用事例を発表した。

発表によるとAvago Technologiesは、Cadenceのインプリメント・ツール「Encounter Digital Implementation (EDI) System」を用いて大規模な28nmネットワーク用チップを設計。「EDI System」を利用する事で設計期間を短縮するだけでなく、チップのパフォーマンス向上を実現。これまで使用していたツールと比較して57%の性能向上となる1GHzの性能を達成できたという。

Avago Technologiesの担当者は、「EDI System」に搭載されるフィジカル考慮の最適化機能「GigaOptテクノロジ」によって設計生産性を高めることが出来たとコメントしており、現在Avago Technologiesは、Cadenceと協業して1億5000万ゲート規模の次世代高速ネットワークチップ設計に取り組んでいるという。

2013.01.24

2013年1月22日、ESLソリューションを手掛ける米Carbon Design Systemsは、同社の2012年度の業績を発表した。

Carbonは具体的な売上金額を公表していないが、発表によると同社は6年連続で売上増を達成。2012年は新規顧客を14件獲得し、9月にはSamsungから400万ドルの出資も受けた。Carbonによると、同社が昨年5月に発表した「CPAK」が顧客の支持を得て売上増加に貢献しているとの事で、バーチャル・プラットフォームの最大の壁といえる環境構築の手間を大きく省くソリューションが顧客のニーズにマッチした。「CPAK」はバーチャル・プラットフォームを迅速に立ち上げるためのキットで、ARMベース・サブシステム向けのキットをはじめ30種類のキットがCarbonのWebポータル「IP Exchange」上に用意されている。

2013.01.24

2013年1月22日、SoCインターコネクト設計ソリューションを手掛ける米Arterisは、同社のインターコネクトIP「FlexNoC」を米ASICベンダのOpen-Silicon社がライセンスしたことを発表した。

Open-SiliconによるArterisのインターコネクトIPのライセンスは2011年、2012年に続くもので、今回はARM Cortex-A9ベースのネットワーキングSoCの設計で利用した。昨年はメディア・ゲートウェイSoCの設計で「FlexNoC」を利用していた。Open-Siliconの担当者は、ARMベース・サブシステムの消費電力とパフォーマンスの最適化のためにArterisの「FlexNoC」を採用しており、設計におけるタイミング収束も楽であるとしている。

2013.01.24

2013年1月23日、Cadenceは、同社の検証プラットフォーム「Incisive」のバージョン・アップを発表した。

発表によると「Incisive」の最新バージョン 12.2は、シミュレータ・エンジンの性能が約2倍に高められたほか、複数の新機能の実装により検証の生産性を倍に引き上げることが可能となった。

新機能としては、「Incisive Debug Analyzer」と呼ぶデバッグ機能、「Incisive Metrics Center」と呼ぶカバレッジ・データ解析機能、低消費電力モデル機能、フォーマル解析による自動化されたレジスタマップ検証機能などがあり、これら機能追加と合わせてミックスシグナル検証の性能向上や、エミュレータ「Palladium XP」のサポート機能の強化も合わせて実施されたという。

2013.01.24

2013年1月23日、Mentor Graphicsは、ARM Cortex-A9 MPCore向けのエミュレーション・ソリューションを発表した。

今回Mentorが発表したのは、ARM Cortex-A9 MPCore向けの「iSolve」と呼ぶハードウェアおよびソフトウェアのICEで、同社の提供するエミュレーター「Veloce」と組み合わせて使用するもの。「iSolve」はプラグ&プレイで「Veloce」に接続可能で同製品を利用することで、ARM Cortex MPCore-A9を搭載したSoCのエミュレーションを容易に実現できるようになる。Mentorは、ARMプロセッサ以外にもUSB,PCI Express,Ethernet,SATAなど様々な「iSolve」ソリューションを用意している。

2013.01.24

2013年1月23日、Synopsysは、3次元構造のFinFETトランジスタを用いた半導体設計用のEDAツールの提供開始を発表した。

発表によると、今回発表されたSynopsysのFinFETテクノロジ向けのEDAツールは、主要ファウンドリ、研究機関、FinFET早期適用企業各社との5年以上に及ぶ共同開発によって生まれたもので、その中にはFinFETテクノロジの開発者として知られるUCバークレー、Chenming Hu博士も含まれている。

具体的に今回SynopsysがFinFETテクノロジ向けのEDAツールとして紹介したのは、下記のツールおよびIP。

・フィジカル設計ツール「IC Compiler」

・フィジカル検証ツール「IC Validator」

・RC抽出ツール「StarRC」

・キャラクタライズ・ツール「SiliconSmart」

・ファーストSPICEシミュレータ「CustomSim」、「FineSim」

・回路シミュレータ「HSPICE」

・TCAD「Sentaurus」

・マスク・シンセシス・ツール「Proteus」

・設計IP「DesignWare Embedded Memory」、「DesignWare Logic Library IP」

発表には、Global Foundries,Samusung Electoronicsがユーザーとしてコメントを寄せている。

2013.01.22

2013年1月21日、FPGAベースのプロトタイピング・ソリューションを手掛ける米S2Cは、新製品のプロトタイピング・ボード「Quad TAI Logic Module」の発売を発表した。

「Quad TAI Logic Module」は、Xilinxの最新の28nm FPGA「Virtex-7 2000T」を搭載するプロトタイピング・ボードで、同社の「V7 TAI Logic Module」シリーズの3番目の製品。既存の製品が「Virtex-7 2000T」を1個(Single V7 TAI Logic Module)または2個(Dual V7 TAI Logic Module)搭載していたのに対し、今回発売された「Quad TAI Logic Module」はその名の通り4個「Virtex-7 2000T」を搭載し、最大8000万ASICゲートのデザインに対応する事が可能。既に受注を開始している。

S2Cによると、「Quad TAI Logic Module」には、専用LVDSピンを用いた多重接続回路、専用リファレンス・クロックとリセット回路が用意されており、LVDSを用いたピン多重化により任意の二つのFPGA間を最大800MHz以上、10,000以上で相互接続する事が可能。大規模なFPGAの容量とこれらFPGA間接続技術を用いる事で殆ど全てのデザインを「Quad TAI Logic Module」に分割実装する事が可能で、S2Cは例えば複数ARM Cortex-A15コアと複数GPUコアが搭載されたSoCなども実装できるとする。

「Quad TAI Logic Module」へのデザインの分割実装には、S2Cの提供する「TAI Player Proソフトウェア」の他にサード・パーティー製のツールを利用することが可能。Xilinxの提供する専用設計ツール「Vivado」や「ChipScope Pro」もあわせて利用することができる。

※画像はS2C社発表資料およびWeb掲載のデータ。

2013.01.18

2013年1月17日、Xilinxは2013会計年度第3四半期(2012年10-12月)の売上を報告した。

Xilinxの2013年Q3(12年10-12月)の売上は、前年同時期とほぼ同一で前期比6%減の5億980万ドル。営業利益は前年比12%減、前期比18%減の1億2080万ドルという結果だった。厳密に言うと売上は前年同時期を若干下回っており、Xilinxの売上前年割れはこれで6四半期連続となる。

地域別売上では、北米市場がQ2よりも6%伸びたが、最大市場のアジアの売上がQ2に対して11%落ちた。アジア以上に売上を落としたのが欧州で前年比は1%増だったが、Q2に対しては15%も売上を落とした。日本は前年比5%増、前期Q2比4%減だった。

分野別の売上構成では、稼ぎ頭のコミュニケーションおよびデータ・センター分野が前年比2%増、前Q2比11%減、産業および宇宙航空、防衛分野は前年比、前期比ともに売上増となった。

製品別売上では、Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6で構成される新製品カテゴリの売上がとても好調で前Q2に対して17%増を記録、売上全体に占める割合を25%にまで伸ばした。

Xilinxは次期2013年Q4(13年1-3月)の売上を今期の2-6%増と予測している。

2013.01.16

2013年1月15日、業界最速と称する高速RTLフィジカル合成ツールを手掛ける、米Oasys Design Systemsは、好調だった2012年の業績を発表した。

発表によるとOasys Design Systemsは、2012年にランキング上位の半導体ベンダやIPベンダによる新規オーダーにより、前年比114%増の受注を獲得。28nm以降の先端プロセスを用いたデザインのニーズに応えた。

同社の高速フィジカル合成ツール「RealTime Designer」は既に複数の顧客の28nmデザインで利用されており、現在はそれら顧客と共に20nmおよび14nmのRTLデザイン・フローに取り組んでいるとの事。

2013.01.16

2013年1月15日、SystemCからの高位合成ツールを手掛けるForte Design Systemsは、同社の2012年の業績について発表した。

発表によるとForteの2012年売上は前年比22%増を達成、7年連続の売上前年超えとなった。同社の提供するSystemCからの高位合成ツール「Cynthesizer」のユーザーの多くは、競合のC言語からの合成ツールを使用していたユーザーで、ヨーロッパ、日本、韓国、台湾、米国の各地に存在。2012年は米国、韓国、日本の大手半導体企業においてその導入が拡大されたようで、EDAツールに特化した調査会社GarySmithEDA社は、Forteを高位合成ツール市場のトップ・ベンダとしてランクしている。

尚、Forteによると、2012年は高位合成ツール「Cynthesizer」に限らず、同社のIP製品「CynWare」、「CellMath」もGPUやカスタム・プロセッサ向けに事業が拡大。国内でもグラフィックスLSIのAXELLやグラフィックスIPのDMPなどで実績のある演算器IP「CellMath」は、2012年にOpen CL準拠にエンハンスされたという。

2013.01.16

2013年1月15日、フォーマル検証ツールを手掛けるドイツのEDAベンダOneSpin Solutionsは、同社の2012年の業績と今後の事業計画を発表した。

尚、OneSpinはベンチャー・キャピタルからの資金調達により技術チーム、セールスおよびAE人員を増強。東ヨーロッパとイスラエルに新たに代理店を設置し、本社をドイツから米国(サンタクララ)に移転したという。

2013.01.10

2013年1月9日、業界最速と称する高速RTLフィジカル合成ツールを手掛ける、米Oasys Design Systemsは、新製品「RealTime Explorer」を発表した。

発表によるとOasysの新製品「RealTime Explorer」は、設計の早期段階でRTLデザイナーがタイミング、パワー、面積、配線混雑度などを確認、分析するためのツールで、インプリメントを考慮したデザインの最適化を実現するもの。

「RealTime Explorer」には、既に先端デザインなどでも実績のある同社の高速フィジカル合成ツール「RealTime Designer」の合成エンジンが組み込まれており、論理設計データと物理設計データのクロス・プロービングが可能。「RealTime Explorer」の解析結果と「RealTime Designer」の合成結果には相関性があり、RTLデザイナーはレイアウト・デザイナーに依存することなくRTLレベルでデザインを最適化できるようになる。

Oasysによると、「RealTime Explorer」はRTL設計とレイアウト設計のイタレーションを無くし、設計期間を短縮すると同時に設計品質の向上を実現するために開発されたツールで、同社は「RealTime Explorer」をRTLデザイナーが求める論理設計から物理設計までの全てのデザイン・ビューを提供する、業界唯一の単一RTL合成プラットフォームだと主張。これまではRTL合成ツールの制限により最適化に限度があったが、大規模デザインに対応可能でかつ高速な「RealTime Designer」の合成エンジンにより、RTLデザイナーは複雑なRTLを数時間で変更およびチェック可能となる。

尚、実際に「RealTime Explorer」を用いてデザインを成功させた先行ユーザーが存在しているようで、デザインの収束期間を1-2か月短縮した例もあるという。

※画像はOasys Design SystemsのWeb掲載のスクリーン・ショット

2013.01.10

2013年1月9日、国内のEDA大手ジーダットは、自社開発した新製品「Cforce」の販売開始を発表した。

ジーダットの新製品「Cforce」は、同社が自社開発したアナログ回路向けのSPICEシミュレータで、高速、高精度、そしてコストパフォーマンスがうり。「Cforce」の処理速度と精度の高さは、マルチスレッド、高収束技術、高精度ソルバなどの技術により実現されており、実行速度は他社製品比2-3倍、既存のSPICEシミュレータを「Cforce」に置き換えれば、他社製品比20-30倍のコストパフォーマンスを実現できるという。

また、コストパフォーマンスの高さを生かし複数のライセンスを活用すれば、網羅的な回路特性のばらつき検証、回路最適化環境における解析、テスト回路の対象ICを含めた検証などにも「Cforce」を活用できるとジーダットは主張する。

発表に記載された「Cforce」の特徴は以下の通り。

・トップクラスの実行速度(他社比 2?3倍)

・マルチスレッド対応による解析時間の短縮

・疑似過渡解析による高い収束性

・高精度ソルバによる高精度シミュレーション

・Verilog-Aを標準サポート

・他社シミュレータ互換による既存設計環境、フローへの容易な統合

・回路設計統合環境 <回路入力,解析環境,波形ビューア>との連携による回路設計の高効率化

2013.01.08

2013年1月7日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のLintツール「ALINT」を日立電線がFPGA開発で採用した事を発表した。

発表によると日立電線は、単発の設計プロジェクトではなく、社内の情報ネットワーク機器向けFPGAデザインフローにてAldecの「ALINT」を採用。バグの早期検出、自動コードレビュー、RTLコーディングスタイルの徹底などの要求を満たせるRTLレビューおよび検証ツールとして「ALINT」をFPGAデザインフローに組み込んだ。

既に日立電線では「ALINT」を用いたFPGA開発を進めており、致命的なバグの発見など効果を上げているとの事。ツールの運用にあたっては、STARCルールに基づく自動コードレビューや日立電線独自のデザインポリシーの適用など、Aldecのチームが協力したという。

Aldecの「ALINT」は昨年末にバージョンアップしており、FPGA配線リソースを最適化する新たなプレミアムルール・ライブラリを追加している。

2013.01.08

2013年1月7日、オープンなPDKの普及推進団体「IPL Alliance」は、半導体ファウンドリ台湾UMC社が同団体に加盟した事を発表した。

「IPL(Interoperable PDK Library)Alliance」は、ツール環境に依存しないオープンなPDK仕様「IPL1.0/2.0」の標準化および普及推進団体で、今回のUMCの加盟により、そのメンバーは計32社となる。

UMCはIPLへの加盟により、「IPL1.0/2.0」準拠のオープンPDK「iPDK」をサポートするとしている。

2013.01.08

2013年1月7日、米EDA Consortiumは、2012年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

EDACの発表によると、2012年Q3(7月-9月)の世界のEDA売上総額は、前年比4.9%増、前Q2比約1.7%増の16億1990万ドルだった。これで四半期ごとの世界EDA売上総額は、11四半期連続で売上前年比増を達成した。

2012年Q3の売上を分野別に見ると、主力のCAE分野が前年比2ケタ増を維持したものの、IP分野は前年比1ケタ増に留まり、IC Physical Design & Verification分野は10四半期ぶりに前年割れとなった。

2012年Q3の売上を地域別に見ると、アジアその他地域が前Q2を上回る前年比21.8%増と大きく成長したが、北米、ヨーロッパは微増に留まり、日本市場だけは前年割れを記録した。

これまで約2年半に渡り右肩上がりの成長を見せてきたEDA市場だが、今期の成長率はこの2年間で最も低いもので緩やかな成長に落ち着いた。しかしながら、引き続きQ4も売上前年比増を達成する見通しで、2012年の世界EDA売上は過去最高の65億ドル以上に到達する可能性が高い。

2012年Q3時点でのEDA業界の従業員数は28877人で、前期Q2比2.4%増となっている。

2012年Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億3250万ドル 11.6%Up

■IC Physical Design & Verification分野 3億2670万ドル 3.4%Down

■IP分野 4億2300万ドル 3.2%Up

■サービス分野 8470万ドル 4.6%Down

■PCB/MCM分野 1億5300万ドル 9.0%Up

2012年Q3地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億1570万ドル 1.3%Up

■ヨーロッパ 2億6750万ドル 3.8%Up

■日本 2億4390万ドル 5.1%Down

■アジアその他地域 3億9280万ドル 21.8%Up

2013.01.07

2013年1月2日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の製品が台湾国立交通大学に採用された事を発表した。

発表によると台湾国立交通大学は、修士課程のESL教育プログラム向けにAldecの論理シミュレータ「Riviera-PRO」とFPGAボードベースの検証ソリューション「HES」を採用した。この両製品の教育向けの導入は、2011年にUCサンディエゴも発表している。

Aldecは、論理シミュレータ「Active-HDL」の無料学生版 (Student Edition)のほか、「EDU Edition」と呼ぶ教育版の製品を提供しており、高機能シミュレータ「Riviera-PRO」の場合、その教育版価格は1ライセンスあたり年間60ドルからとなっている。

2013.01.04

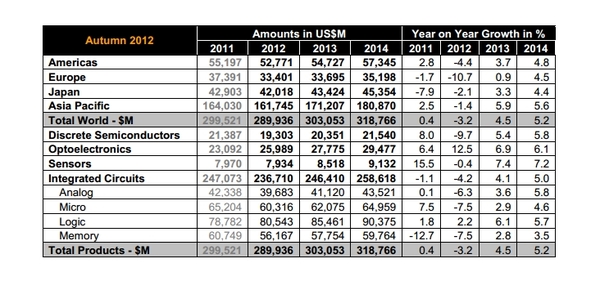

2013年1月3日、米SIA(Semiconductor Industry Association)は、2012年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年11月の世界半導体売上は前年同月比、前月比ともに2%増の257.3億ドルだった。この金額は2012年の統計で最も高いもので、17ヶ月連続していた売上前年割れ記録をようやく止めた。

今年1月からの売上累計は、2652億ドルで昨年同時期の累計額と比較すると約4.3%減となっており、12月の売上で更に前年との差を縮めると予測されているが、最終的に2012年の世界半導体売上は前年比3.2%減の2899億ドルと予測されている。(WSTSによる予測)

※WSTS:World Semiconductor Trade Statistics

2012年11月の売上を地域別でみると、北米が9月、10月に続いて力強い回復を見せ前年比9.7%増、アジアもこれに続いた。しかし日本市場の売上は欧州市場と共に依然前年割れの状態となっており、北米・アジアの好調を日本・欧州が足を引っ張る格好となっている。

2012.12.28

各組織の発表している2012年12月時点での2013年世界半導体市場成長予測。

現時点ではいずれの予測もプラス成長を見込んでいます。

2012.12.28

各組織の発表している2012年12月時点での2012年世界半導体市場成長予測を更新しました。新たにIDCが予測値を発表しました。IDCの予測は唯一1%弱のプラス成長としています。

2012.12.25

2012年12月20日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のLintツール「ALINT」のバージョンアップを発表した。

発表によると「ALINT」の最新バージョン2012.12では、Lintチェック用の新たなプレミアムルール・ライブラリが用意され、FPGA配線リソースの最適化が可能となった。同ライブラリは配線を考慮したRTLを実現するもので、Aldecは具体的に以下の問題を解決できるとしている。

1. 異なるレベルのデザイン階層へのロジック配置 (階層的デザイン)

2. ファンアウトを増やす準最適な階層間インターコネクト

3. I/Oポートにおけるレジスタの問題

2012.12.25

2012年12月21日、Mentor Graphicsは、同社オリジナルのリアルタイムOS「Nucleus RTOS」のバージョン・アップを発表した。

発表によると「Nucleus RTOS」の最新リリースでは、mDNSおよびDNS-SD(DNS Service Discovery)に新たに対応し、ネットワーク・サーバや手作業によるコンフィギュレーションを介さず、デバイスとネットワークを自動的に接続できるようになった。この機能は、M2Mおよびスマートエネルギー用アプリケーションを搭載したネットワーク機器の開発に役立つという。

また、「Nucleus RTOS」の最新リリースには、デバッグやカスタマイズに利用可能なシステムトレース機能、最適化された「Nucleus RTOS」のコンフィギュレーションを作成できるグラフィカルなカーネル・コンフィギュレーション・ユーティリティなど、「Nucleus RTOS」のチューニングに役立つ機能が追加された。

2012.12.21

2012年12月20日、ARMとCadenceは、ARM Cortex-A7プロセッサを搭載した14nm テストチップをテープアウトしたことを発表した。

発表によると今回テープアウトされたテストチップは、Samsungの14nm FinFETプロセスをターゲットとしたもので、同プロセスをターゲットとしたチップのテープアウトは業界初。ARM Cortex-A7プロセッサを搭載したテストチップは、CadenceのRTL to GDSIIフローによって設計され、具体的には以下のCadenceツールが利用された。

・Encounter RTL Compiler

・Encounter Test

・Encounter Digital Implementation System

・Cadence QRC Extraction

・Encounter Timing System

・Encounter Power System

Cadenceは、今年11月にIBMの14nm FinFETプロセスでARM Cortex-M0プロセッサ搭載のテスト・チップをテープアウトしており、IBM、GlobalFoundries、Samsungの「Common Platform」の14nm FinFETプロセス立ち上げに向けて、ARMも交えて密接に連携している様子が伺える。

※関連ニュース

2012.12.21

2012年12月19日、Xilinxは同社のFPGA専用設計環境「Vivado Design Suite」の「WebPACK エディション」のリリースを発表した。

今回Xilinxがリリースした「Vivado Design Suite WebPACK エディション」は、XilinxのWebサイトからダウンロードして利用できる無償のツールで、今回「Vivado Design Suite」のバージョンアップと合わせて利用が可能となった。

「Vivado Design Suite」は、今年4月に発表されたXilinxの次世代設計環境で、次の10年を見据えて開発されたもの。7月にバージョン2012.2が一般リリースされた後、この11月にはバージョン2012.3がリリースされ、マルチコア対応などエンハンスが施されていた。今回リリースされたバージョン2012.4ではサポートデバイスの拡張などが実施されている。

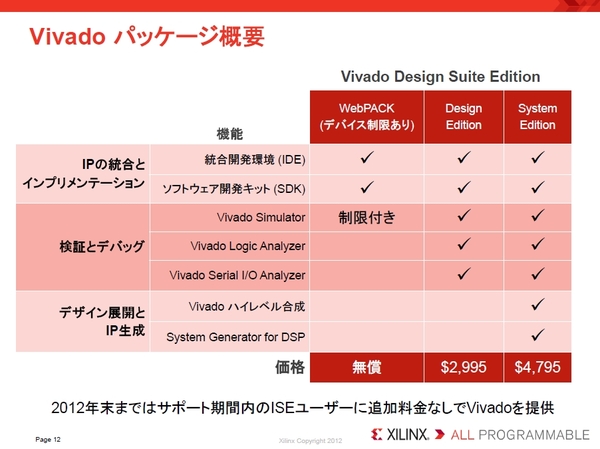

Xilinxは、「Vivado Design Suite」に「System Edition」、「Design Edition」、「Web Pack エディション」と3つのパッケージを用意しており、IPの統合とインプリメンテーションに関する機能については、無償の「Web Pack エディション」でも有償の「System Edition」、「Design Edition」と同じものが提供される。

Xilinxは、一つ前の世代の設計環境「ISE」においても無償のWeb Packを提供しているが、そのダウンロード件数は四半期あたり2万件に達するという。

※画像はXilinx提供のデータ

2012.12.21

2012年12月20、Mentor Graphicsは、同社のカスタムIC設計環境「Pyxis」をHPが社内標準ツールとして採用していることを発表した。

発表によるとHPはMentorのカスタムIC設計環境「Pyxis」を継続的に採用しているようで、その理由は、常時追加される新機能やMentorの優れた顧客向けサービスおよびサポートにあるとの事。両社は、CMOSとMEMSの設計メソドロジの統合に関して、長年に渡りパートナーシップを組んでいるという。

尚、Mentorはつい先日、HPによるCDC検証ツール「Questa CDC」の全社採用を発表したばかり。

※関連ニュース

2012.12.19

四半期毎のEDA地域別売上推移を更新しました。※数値はEDAC統計ベース

2012.12.19

2012年12月18日、アナログ/RFおよびミックスシグナル設計向けの検証ソリューションを手掛ける、Berkeley Design Automationは、同社の「Analog FastSPICE AMS」を台湾の設計サービス会社IC Plus社が採用した事を発表した。

発表によるとIC Plusは、高速ミックスシグナル設計検証向けにBerkeley Design Automationの「Analog FastSPICE AMS(AFS AMS)」を採用。IC Plusの担当者は、「AFS AMS」は既存の並列SPICEミックスシグナルシミュレータよりも最大4倍高速、また、「AFS AMS」はセットアップが非常に簡単で数時間のうちにに利用可能だったとコメントしている。同社では、ADCやPLLのデバイスノイズ解析も含めたポストレイアウト検証に「AFS AMS」を利用しているようだ。

「AFS AMS」は、今年11月にリリースされたばかりの新製品で、同社の業界デファクトツール「Analog FastSPICE」と市販のVerilogシミュレータを組み合わせて利用することで高速なミックスドシグナル・シミュレーションを実現するもの。日本国内では既に富士通セミコンダクターが採用している。

※関連ニュース

Berkeley Design Automationは、「Analog FastSPICE」の成功により安定した成長を維持しており、今年11月にDeloitte社の北米成長企業ランキング「2012 Technology Fast 500」に優良企業として262位にランクされた。同社の2007年から2011年までの売上の成長率は302%だという。

2012.12.19

2012年12月17日、Synopsysは、同社の検証IPをセキュリティ向けIPを手掛けるElliptic Technologies社が採用した事を発表した。

発表によると、Elliptic Technologiesは同社のセキュリティ向けIPの新製品「Multi-Packet Manager security protocol accelerator (CLP-630)」の開発にて、SynopsysのARM AMBA 検証IPを採用。然るべき製品評価を実施した後に、その使い易さ、サポート体制などから採用を決定し、ARMベースの製品開発に適用した。

SynopsysはIP製品の拡張を進める中で検証IPの機能強化にも注力しており、今年2月に検証IPのアーキテクチャ刷新を発表。新しいVIPERアーキテクチャーに基いた100% SystemVerilogベースの検証IPで他社の検証IPとの差別化を図っている。ARM AMBA 検証IPに関しては、今年10月に新機能「Performance Checker」をリリースしている。

※関連ニュース

2012.12.19

2012年11月17日、フォーマル検証ツールを手掛けるドイツのEDAベンダOneSpin Solutionsは、同社の「OneSpin 360 MV」をMaximが採用した事を発表した。

発表によるとMaximは、マイクロコントローラのデザインを用いてOneSpinのフォーマル検証ツール「OneSpin 360 MV」を3ヶ月に渡り評価。「OneSpin 360 MV」は、他社のフォーマル検証ツールが見逃したコーナー・ケースのバグや新たなバグを発見できたことから、HPに採用される事になった。HPは、「OneSpin 360 MV」を社内3つの事業部の世界各地のデザイン・センターで利用するという。

OneSpinは今年5月に増資を行い、社長が交代している。

2012.12.19

2012年11月18日、Mentor Graphicsは、同社のCDC検証ツール「Questa CDC」をHewlett-Packardが全社採用した事を発表した。

発表によるとHPは、「Questa CDC」を社内のCDC検証向けの標準ツールとして全社採用。MentorはHPが「Questa CDC」によるCDC検証メソドロジを導入するにあたり、HPの設計スタイルに合わせてメソドロジの定義をカスタマイズするなどのコンサルティング対応も実施。同メソドロジは既にHP社内で利用されており、複数のプロジェクトで成功を収めているという。

「Questa CDC」は、以前はフォーマル検証ツール「0-in」シリーズの製品として提供されていたが、「Questa」プラットフォームに追加され、更なる機能強化が今年10月に発表されたばかり。最新の「Questa CDC」は、性能向上によりキャパシティの制限は無くチップ・レベルのCDC検証も可能となっている。

※関連ニュース

2012.12.19

2012年12月17日、Cadenceは、会津大学と共同で高位合成技術を取り入れた教育プログラムを開発した事を発表した。

発表によると今回開発された教育プログラムは、システムレベル(ESL)設計者の育成を目的とした大学院レベルの教育プログラムで、既に会津大学大学院、コンピュータ構築学講座において同プログラムの授業が開始されているとの事。授業では、Cadenceの「TLM-Driven Design and Verification Methodology」の日本語テキストと高位合成ツール「C-to-Silicon Compiler」ならびに論理合成ツール「Encounter RTL Compiler」が使用され、SystemCのコーディングを起点に高位合成、論理合成を行いゲートレベルのネットリストを生成するという一連の設計フローを体験しながら学習可能。このような高位合成技術を本格的に取り入れた授業は日本初だという。

2012.12.14

2012年12月6日、フォーマル検証を中心とした検証ツールを手掛ける米Real Intent社は、同社のLintツール「Ascent」のバージョンアップを発表した。

発表によると、Lintツール「Ascent」の最新バージョン2.0では、新たにFSMチェックを含む60の包括的なルールが追加されたほか、ツールの解析スピードが向上され、450Mゲートのデザインを1時間以内で解析可能となった。また、Synopsysのデバッグ・ツール「Verdi3」とのインテグレーションも実現し、ツールによる言語サポートも強化され、複数言語の混在デザインにも対応可能となった。更にツールのユーザビリティやレポート機能も向上したようだ。

更にReal Intentは12月10日に同社の2012年の売上実績を発表。プレスリリース文

2011年11月から2012年10月末までの会計年度の売上は、前年比倍増を達成。プレスリリースでは具体的な売上金額は明らかにされていないが、Webサイト「DeepChip」の情報によると、同社の売上は約450万ドルから約900万ドルに倍増したとの事。顧客数は前年の1.6倍に増えたという。

2012.12.14

2012年12月13日、RTL解析を中心とした各種EDAツールを手掛ける、米Blue Pearl Softwareは、同社の日本オフィスを開設した事を発表した。

発表によると、新宿の野村ビルに開設されたBlue Pearl Software日本オフィスの代表には、業界での経験豊富な坂野勝彦氏がセールスダイレクターとして就任。同氏は最近までフォーマル検証ツールのReal Intent社の日本法人の代表を務めていた人物で、SpringSoftやCadenceにも在籍していた経歴を持つ。

Blue Pearl Softwareは、フォーマルエンジンを用いたRTL解析ツール「Analyze RTL」 とSDC自動生成ツール「Create Timing Constraints」の2種類を提供しており、ここ最近はFPGA設計にフォーカスしたRTLサインオフ・ソリューションとして営業を展開。同社のツールはSynopsysやXilinxのFPGA設計フローをサポートしている。

2012.12.14

2012年12月11日、高速処理をうりとしたRTLフィジカル合成ツールを手掛ける、米Oasys Design Systemsは、同社の新社長就任を発表した。

発表によると今回新たにOasys Design Systemsの社長兼CEOに就任したのは、業界のベテランScott Seaton氏で、元のCEOである創業者のPaul van Besouw氏は、会長兼CTOとして同社の役員に留まっている。

Scott Seaton氏はEDA関連の営業・マーケティング職の経験が豊富な人物で、元々はAMDのエンジニアであり、Valid Logic SystemsでFAE、Viewlogic Systemsでチャネル・セールスVP、直近はESLツールのCarbon Design Systemsのセールス及びマーケティングVPを務めていた。

Oasys Design Systemsは、大規模デザイン対応で高速処理を特徴とするフィジカル考慮の論理合成ツール「Real-Time Designer」で一定の成功を収めており、同社にはIntelとXilinxが出資しているほか、STmicroelectoronics、TI、Juniper Networks、NetLogicなどの大手が「Real-Time Designer」を採用済。現在も半導体上位10社の複数の顧客が28nmチップの設計で「Real-Time Designer」を利用しているという。また、公式にアナウンスされている情報ではないが、Xilinxの新たな設計環境「Vivado」ではOasys Design Systemsの合成エンジンが使用されているらしい。

※画像は今年の49回DACでのOasysブースの様子

※画像は今年の49回DACでのOasysブースの様子

2012.12.13

2012年12月12日、Alteraは、ARM搭載FPGA「Cyclone V SoC FPGA」のサンプル出荷開始を発表した。

今回サンプル出荷が開始された「Cyclone V SoC FPGA」は、ARMの「Cortex-A9 MPCore」が搭載される28nm FPGAで、Alteraが「SoC FPGA」と呼ぶ製品の第一弾となるもの。Alteraの「SoC FPGA」には「Cyclone V SoC FPGA」の他に「Arria V SoC FPGA」がある。

「Cyclone V SoC FPGA」は現在、11万ロジック・エレメント相当のロジック集積度を備える「Cyclone V SoC FPGA (5CSXA6)」のサンプルが出荷されており、その他のラインナップも2013年第1四半期にサンプルが出荷され、2013年中に量産開始の予定となっている。

尚、ARMを搭載する「Cyclone V SoC FPGA」の開発環境は、Alteraの専用開発環境「Quartus II」の最新バージョン v12.1が用意されているほか、Synopsysと共同開発したSoC FPGA向けのソフトウェア開発環境「Virtual Target」を利用する事が可能。そして今回更に新たにARMと共同開発したソフトウェア開発環境が発表された。

AlteraとARMがSoC FPGA向けに共同開発したのは、ARMの開発環境「DS-5」をAlteraのSoC FPGA向けにカスタマイズしたもので、正式名称は「ARM Development Studio 5 (DS-5) Altera Edition」。同ツールは、Alteraの「SoC エンベデッド・デザイン・スイート」に含まれる形で2013年早々に米国内販売価格995ドルで提供が開始される予定。

「ARM DS-5 Altera Edition」は、ARMプロセッサ上のソフトウェアとFPGAのデバッグの壁を取り除くもので、一元化されたCPUおよびFPGAドメインからのあらゆるソフトウェア・デバッグ情報を、「DS-5」ユーザ・インタフェースを通じて取り扱う事が可能。単一のツール環境でハードウェアとソフトウェアの境界にまたがったデバッグを行うことができるという。

※画像はARM DS-5 Altera EditionのGUI画面(Altera社Web掲載画像)

2012.12.12

2012年12月11日、米SIA(Semiconductor Industry Association)は、米国内の半導体産業の就労者状況について発表した。

アメリカ政府の米国労働統計局が発表した2011年の就業統計分析データによると、米国内の半導体産業の労働者数は前年比3.7%増を記録しており、米国内のほぼ全域でアメリカ人を雇用、その労働者数のTOP5は以下の通りとなっている。

1:カリフォルニア州 47100人

2:テキサス州 28800人

3:オレゴン州 23400人

4:アリゾナ州 18800人

5:マサチチューセッツ州 10100人

今年11月にSIAが発表したデータによると、米国内の半導体産業の労働者数は合計24万4800人と見積もられており、この数にはファブレス半導体企業の労働者数も含まれている。

SIAのCEOは、半導体産業の拡大は政府の有効な政策で、米国の経済、防衛力、国際競争力を押し上げるものだとコメントしている。

2012.12.11

2012年12月10日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のASICプロトタイピング用FPGAボード「HES-7」による「ARM Cortex-A9」のサポートを発表した。

今回発表された「HES-7」による「ARM Cortex-A9」のサポートとはどのような事かと言うと、「HES-7」用のオプションとして新たにXilinxのARM搭載FPGA「Zynq-7000」を搭載したドータ・ボードが用意され、同ドータ・ボードを用いる事で「ARM Cortex-A9」ベースのSoC開発にも「HES-7」が利用可能となったという話。このXilinxの「Zynq-7000」を搭載したドータ・ボードは各種ペリフェラル、メモリおよびコネクタが備えられており、既に「HES-7」を利用している顧客には、なんとAldecから無償で提供されるという。

2012.12.06

2012年12月5日、Synopsysは、2012会計年度第4四半期(12年8月-10月)の売上を報告した。

発表によると、Synopsysの2012会計年度Q4(12年8月-10月)の売上は、前年同時期比約16.3%増、前期12年Q3比約2.3%増の4億5420万ドル。純利益は前年同時期比約27%減の2910万ドルだった。(※GAAP基準による会計結果)

この売上実績は前四半期売上報告時の予測を上回るもので、前Q3に続いて四半期売上記録を更新。Synopsysは2012年会計年度に入り全ての四半期で売上げ記録を更新し続けた事になる。尚、Synopsysの売上実績前年超えは今回発表した2012年Q4で9四半期連続となる。

最終的にSynopsysの2012会計年度(2011年11月-2012年10月)の売上合計は、17億5600万ドルで前年比14.3%増と同社過去最高を記録、純利益は前年よりも約18%減の1億8240万ドルだった。(※GAAP基準による会計結果)

Synopsysは、次期2013会計年度Q1(12年11-13年1月)の売上を4億6800-7800万ドル、2013会計年度の売上合計は今期を更に上回る19億5500-5700万ドルと予測している。

2012.12.06

2012年12月5日、米SIA(Semiconductor Industry Association)は、2012年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2012年10月の世界半導体売上は前年同時期比約3.7%減、前月比約1.7%増の252.2億ドルという統計結果となった。これで世界半導体売上の前年割れは17ヶ月連続。売上合計が250億ドルを超えたのは今年に入り始めて。

今年1月からの売上累計は、2394億7000万ドルで昨年同時期の累計額と比較すると4.9%減となっており、このほどWSTSが発表した予測によると、2012年の世界半導体売上は前年比3.2%減の2899億ドルとされている。

2012年10月の売上を地域別でみると、北米が9月に続いて回復基調を鮮明に示しており、前月比8.1%増と大きな伸びを見せた。北米市場は前年比、直近の四半期ごとの売上推移のいずれもプラス成長を示している。一方で日本市場は前月比、前年比、直近の四半期ごとの売上推移のいずれもマイナス成長で状況は9月よりも悪化した。

尚、WSTSは2012年の売上を前年比3.2%減と予測しているが、その地域別の内訳は以下の通り。

北米:4.4減、欧州:10.7%減、日本:2.1%減、アジア:1.4%減

2012.12.05

2012年12月4日、EDAソリューションとEMSサービスを手掛ける独PRO DESIGNは、同社の新製品となるFPGAベースのプロトタイピング・システム「proFPGA」を発表した。

PRO DESIGNは、以前、「CHIPit」と呼ぶFPGAベースのプロトタイピング・システムを手掛けていたが、2008年に同事業をSynopsysに売却。今回発表した「proFPGA」は、「CHIPit」とは異なる新たなアーキテクチャーを用いたプロトタイピング・システムで、Xilinxの28nm FPGA 「Virtex-7 XCV2000T」を搭載するマザー・ボードとケーブル、32種類のドータ・ボードとソフトウェア環境で構築されている。

まず先にリリースされるのは、「Virtex-7 XCV2000T」を4個搭載する「proFPGA quad V7」という製品で、既に今年9月から先行ユーザーに提供されており、正式リリースは来年の第一四半期の予定。同ボードは4800万ASICゲートのキャパシティを持ち、複数のボードを接続してより大きなデザインに対応する事が可能。ユーザーはほぼ100%FPGAのI/Oピンをアクセス可能で、独自の高速コネクタ仕様によりボード間のデータ転送速度は1.2Gb/秒、FPGA上のトランシーバーのデータ転送速度は12.5Gb/秒を実現する。ドータ・ボードは、DDR3メモリ・ボードやPCIe, USB 3.0, Gigabit Ethernetなどインタフェース・ボード、「Vertex-7」とは異なる種類のFPGAボード(Xilinx/Altera)などが用意されているという。

尚、PRO DESIGNは、「Virtex-7 XCV2000T」を2個搭載し2400万ASICゲートのキャパシティを持つ「proFPGA duo V7」という製品もリリースする予定で、既に同製品の仕様やスペックは同社のWebサイト上で公開されている。

今年6月に開催された第49回DACにて同社ブースで聞いた話では、同社はXilinx以外にAlteraのFPGAを搭載したプロトタイピング・ボードも製品化を計画中との事。また、未だ日本には販売ルートが無く代理店を募集中との事だった。

※写真は49DACでProDesignが展示していたプロトタイプ

2012.12.05

2012年12月4日、Tensilicaは、同社のDPU/DSP IPのライセンシーが200社に達した事を発表した。

発表によると、TensilicaがDPU(dataplane processor unit)と呼ぶ同社のプロセッサIPならびにDSP IPのライセンス数は、200のライセンシーで500ライセンスを超えており、Tensilica提供の標準品ならびにライセンシーによるカスタム品合わせて数千種のDPUがシリコン化されているとの事。

Tensilicaのライセンス収入は、昨年の7月末から今年の7月末までの1年間4四半期において競合を平均25%上回っており、今年10月には同社IPコアの出荷数が20億に達している。

TensilicaのIPは、スマートフォン、タブレット、ノートPCなどのモバイル端末の他に、デジタルTVやストレージ、ネットワーク・アプリケーション等でも量産採用されているほか、3G/HSPA+やLTE、LTE-Advancedをはじめとする標準規格のモデム開発にも多用されている。

-thumb-600x422-2435.jpg)