NEWS

2013.05.28

2013年5月22日および23日、ATopTechとCadenceは、それぞれ自社のEDAツールがTSMCの先端プロセス向けツールとして認証されたことを発表した。

両社の発表によると、ATopTechの配置配線ソリューション「Aprisa」と「Apogee」がTSMC 16nm FinFET プロセス向けの設計ツールに、Cadenceの新しいSTA「Tempus」がTSMC 20nmプロセス向けの設計ツールにそれぞれ認証された。

ATopTechのツールは既にTSMC 20nmプロセスのリファレンス・フローに採用されており、今回更にその先の16nm FinFET プロセス向けに認証。配置配線ツール「Aprisa」は先端プロセス設計向けに顧客を増やしており、デザインによっては「Aprisa」無しではインプリできないと顧客に言わせるほどとか。

Cadenceは先端プロセスを用いたARMの実装でTSMCと強固なパートナーシップを築いており、今回STA「Tempus」が認証されたのは20nmプロセス向けだが、16nm FinFET プロセス向けの認証も時間の問題だと思われる。

来週から開催される第50回DACを前に、更に他社からもTSMCによるEDAツール認証のニュースが続くだろう。

2013.05.28

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

2013.05.28

2013年5月24日、Synopsysは、ルネサス製マイコンRH850向けの仮想プロトタイプ開発キット「VDK」のリリースを発表した。

Synopsysの「VDK(Virtualizer Development Kits)」は、特定マイコン向けに用意されるソフトウェア開発キットで、同社のバーチャル・プロトタイピング・ツール「Virtualizer」で使用するソフトウェア開発用の仮想プロトタイプ環境をあらかじめキットとしてパッケージしたもの。既にARMv7/v8 プロセッサ向けの「VDK」がリリースされているほか、先日Freescale社の車載マイコン「Qorivva」ファミリ向けにも提供が開始された。(※関連ニュース)

今回Synopsysがリリースしたのは、ルネサス製の車載マイコン「RH850」向けの「VDK」でSynopsysとルネサスの協業により開発されたもの。昨年時点でその開発計画はアナウンスされていた。(※関連ニュース)

Synopsysによると「RH850」向けの「VDK」は、最初のバージョンとしてRH850ファミリのF1xマイコン向けの仮想プロトタイプ環境がパッケージされており、RH850 F1xのシングル/マルチコア構成、タイマー、メモリー、LIN/CAN/Ethernetなどの通信ブロック、アナログ・モジュール、エラー制御モジュールなどのモデルがリファレンスの仮想プロトタイプ環境に搭載されている。同仮想環境は、バーチャル・プロトタイピング・ツール「Virtualizer」を用いて他のRH850マイコン向けにモディファイすることも可能で、Freescale「Qorivva」向けの「VDK」と同じく、アナログ-デジタル混在シミュレーター「Saber」、Mathworksの「Simulink」、Vectorのネットワーク・シミュレータ「CANoe」といったサードパーティー・ツールと連係できるという。

自動車に搭載される電子制御ユニット(ECU)の開発では、マイコンの選定やソフトウェアの仕様検証/実装検証、実機では不可能な故障注入シミュレーションといった様々な用途でバーチャル・プロトタイピング・ツールが使用されつつあり、大手国内自動車メーカーがECUで数多く採用しているルネサス製マイコン向けの仮想プロトタイプ環境は、開発現場でのニーズが高い。今回の「RH850」向けの「VDK」のリリースは、ルネサスとSynopsysが協力して国内自動車メーカーのニーズに応えた格好だ。

2013.05.24

2013年5月23日、ARMは同社のオフィシャルデジタルマガジン「Signum日本語版」の発行を発表した。

ARMのオフィシャルデジタルマガジン「Signum日本語版」は、2011年まで発行されていたARMオフィシャル情報誌 「IQマガジン日本語版」の後を継ぐ電子媒体で、約半年前から英語版が発刊されていた。「Signum日本語版」は英語版同様に登録のみで無料購読可能で、ページ毎または媒体一式をPDFファイルでダウンロードする事ができる。同電子媒体は、今後は年2回、春・秋に発行される予定だという。

2013.05.24

2013年5月15日、Mentor Graphicsは、韓国のファブレス半導体ベンダMagnaChip社が、同社のカスタムIC設計環境「Pyxis」とPDK自動生成プロセスを採用したことを発表した。

発表によるとMagnaChipは、MentorのカスタムIC設計環境「Pyxis」によって実現される、高精度なPDK自動生成プロセスを自社の設計フローに取り込む事を重視して「Pyxis」を採用。MagnaChipの担当者は、同ツールを採用したことで、その定評のあるPDK自動生成プロセスを複数ベンダのツールで活用できるようになったとコメントしている。

2013.05.24

2013年5月24日、Mentor Graphicsは、2014会計年度第1四半期(2013年2月-4月)の売上を報告した。

発表によると、Mentorの2014会計年度Q1の売上は、前年比約8.6%減の2億2650万ドル、収支は約42万ドルの赤字だった。Mentorは前2013会計年度Q4まで11四半期連続で売上前年増を記録していたが、今四半期で約3年ぶりに売上前年割れとなった。(※GAAP基準による会計結果)

この結果は前Q4売上報告時点の予測通りで、当期売上は前年割れとなったが受注は各製品分野で好調のようで、Mentorは次期2014会計年度Q2(13年6-8月)の売上を前年実績を上回る2億4500万ドルと予測している。

2013.05.23

2013年5月22日、Synopsysは、2013会計年度第2四半期(13年2-4月)の売上を報告した。

発表によると、Synopsysの2013会計年度Q2の売上は、前年同時期比約15%増、前期13年Q1比約5%増の4億9930万ドル。純利益は前年同時期の約3倍強となる6870万ドルだった。(※GAAP基準による会計結果)

この売上実績は前四半期売上報告時の予測通りで、12年Q1から更新し続けている四半期売上記録をまたもや更新した。Synopsysの売上実績前年超えは今回発表した2013年Q2で11四半期連続となる。

Synopsysは、次期2013会計年度Q3(13年2-4月)の売上を4億7500-8500万ドルと予測。2013会計年度の売上予測については19億5500-7500万ドルと特に変更はない。

2013.05.23

各組織が公に発表している2013年5月時点での2013年世界半導体市場成長予測。

今回IDCが最新の予測を発表しました。現時点ではいずれの予測もプラス成長を見込んでいますが、昨年末時点よりも抑え気味な予測となってきています。

2013.05.22

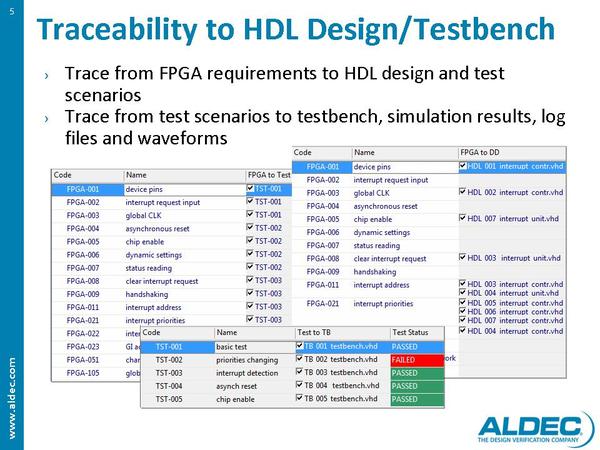

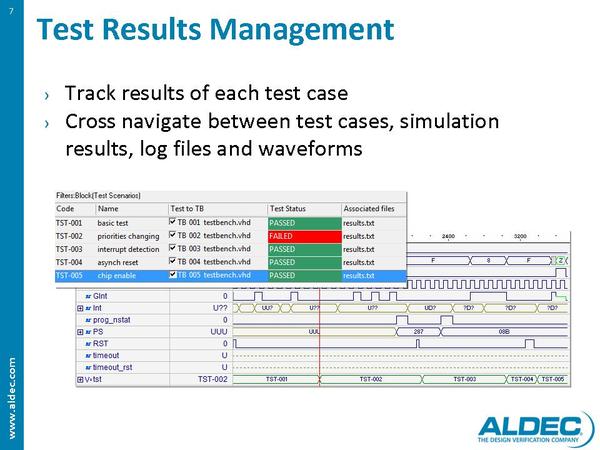

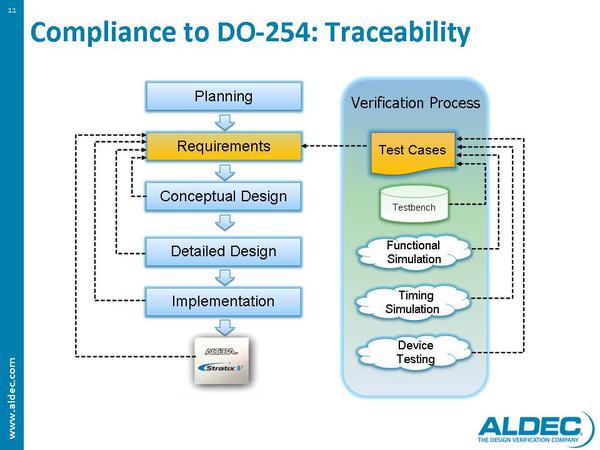

2013年5月20日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、新製品「Spec-TRACER」を発表した。

発表によると「Spec-TRACER」は、ASIC/FPGA設計における設計要求を管理・追跡するツールで、設計に対する要求を取り込み、それら要求がどのようにハードウェアに実装・テストされているかを管理、分析、追跡、レポートする事が可能。これら機能をWindowsベースのAldecのHDL設計ツールやシミュレータと統合することができる。

近年、航空宇宙業界、自動車業界をはじめ様々な業界において安全基準の認証規格に関する要求が高まっており、組込みソフトウェアの開発と同じようにハードウェア設計においても、その開発過程、要求の実装経路などを明確にし、管理、ドキュメント化する事が求められるようになってきている。

今回Aldecが発表した「Spec-TRACER」はそのような要求に対応するツールで、ハードウェア設計におけるトレーサビリティ管理を実現。要求仕様をインポートし 、デザインおよびテストに対して各要求がどのように実装されているかをキャプチャ。要求仕様の変更の影響分析や要求カバレッジ分析なども可能で、トレーサビリティレポートを自動生成する事ができる。

ハードウェア設計においては、設計の要求仕様がどのようにHDLコードやテスト・シナリオに実装されているかを管理・追跡できるほか、テスト・シナリオからテストベンチ、シミュレーション結果へのトレースも可能。それら関係性をナビゲートしてくれる機能もある。

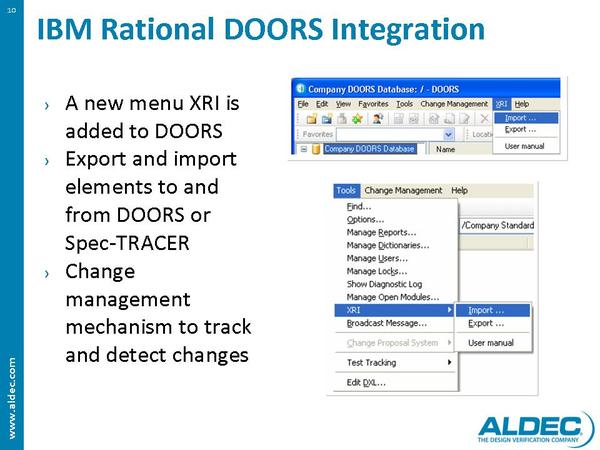

尚、「Spec-TRACER」は、IBMの提供する組込みソフト開発向けの要求管理ツール「Rational DOORS」とのインテグレーションを実現しており、ツール間で相互に要求仕様のインポート/エクスポートが可能。認証規格としては航空宇宙業界の「DO-254」に準拠した要求トレーサビリティをサポートしている。

※画像は全てAldec提供のデータ

2013.05.21

2013年5月15日、SystemCからの高位合成ツールを手掛けるForte Design Systemsは、韓国LG Electronicsが同社の高位合成ツール「Cynthesizer」を採用したことを発表した。

発表によるとLG Electronicsは、社内のデジタルテレビ向けSoCの開発部門において、Forteの「Cynthesizer」を採用。複数の高位合成ツールを評価した結果、生産性の向上、TAT短縮、合成回路の品質(手書きコードより優れた品質)、ローパワー合成機能などから「Cynthsizer」の採用を決定。LGでは既に次世代デジタルテレビ向けSoCの開発プロジェクトに「Cynthsizer」を利用しており、早くも生産性向上と設計期間の短縮効果を得られているという

Forteの「Cynthesizer」は、先日製品の最新バージョン「Cynthesizer 5」を発表したばかりで、合成品質と合わせてローパワー合成機能が大幅に強化された。公にされている情報ではないが、ここのところForteの「Cynthesizer」は北米やアジアのファブレス大手において、先端チップの開発向けに利用されているようだ。

2013.05.21

2013年5月8日、Synopsysは、FPGAベンダAchronixによる同社のEDAツールの成功事例を発表した。

Achronixは、Intelの先端プロセスを用いて製造する高速FPGAで知られる新興FPGAベンダで、既に顧客への出荷を開始しているIntel 22nm FinFETプロセスを用いた高速FPGA「Speedster22i」を、Synopsysの配置配線ツール「IC Compiler」および物理検証ツール「IC Validator」を使ってテープアウト。両ツールを社内設計フローにおける標準設計ツールに採用した。

Achronixは、顧客に提供する自社デバイスの設計環境にSynopsysのFPGA向け論理合成ツール「Synplify Pro」を採用しOEM供給を受けており、両社の関係は元々深いものがあるが、Intel 22nm FinFETプロセスで実績のあるSynopsysのEDAツールは、同じくIntelプロセスを利用するTabula、Netronomeなどにも採用されている可能性が高い。

2013.05.21

2013年5月8日、Synopsysは、Huaweiの半導体部門子会社であるHiSiliconによる配置配線ツール「IC Compiler」の成功事例を発表した。

発表によるとHiSiliconは、ARMのハイエンド・コア「ARM Cortex-A15 processor」を複数搭載したワイヤレス向けのSoC設計でSysnopsysの配置配線ツール「IC Compiler」を使用。5000万インスタンス以上の同デザインを予定通りに実装し、クロックスキューを40%低減し、クロック周波数の向上とパワー・センシティブなブロックのリーク電流削減に成功した。

これらの成功は、フィジカル設計結果との高い相関性を実現する論理合成ツール「Design Compiler」のGraphical physical guidances機能、「IC Compiler」のクロック・ツリー合成機能、タイミング解析ツール「PrimeTime」のECO guidance機能などによってもたらされたという。

2013.05.16

2013年5月14日、Cadenceは、ヤマハによる同社キャラクタライゼーション・ツールの導入事例を発表した。

発表によるとヤマハはモバイル・コンシューマ製品向けのASIC開発において、Cadenceのキャラクタライゼーション・ツール「Virtuoso Liberate」および「Virtuoso Spectre Circuit Simulator」を導入。それにより、ASICに必要なクロック・ネットワークへのダイナミック・パワーを10パーセント削減すると同時にTATを短縮し、従来手法よりもキャラクタライゼーション期間を半減させた。

ヤマハによると、同社の複雑なマルチビットのフリップ・フロップ・セルをキャラクタライズできたのは、Cadenceのツールだけであったとの事で、既存ツールからの置き換えを暗に示している。。

Cadenceのキャラクタライゼーション・ツール「Virtuoso Liberate」には、特許取得済みの「Inside View」という技術が備えられており、ユーザはセル機能の記述やワースト・ケースの定義をすることなくセルのキャラクタライゼーションを自動化できるという。

2013.05.16

2013年5月13日、業界最速と称する高速RTLフィジカル合成ツールを手掛ける、米Oasys Design Systemsは、新ツール「Oasys RealTime Parallel EC (equivalency checking)」を発表した。

発表によると「Oasys RealTime Parallel EC」は、複数プロセッサによる分割処理に対応した等価性検証ツールで、デザインの自動分割技術とマルチ・プロセッシング技術により、その処理速度をリニアに向上可能。階層的なRTLを読み込み、同社の合成ツール「RealTime Designer」の合成したネットリストと論理的な等価性を検証することができる。

同ツールは、合成ツール「RealTime Designer」のアドオン・オプションとして提供されるもので、論理合成後にプッシュボタン式で等価性検証を実行可能。にその階層的トップダウン・アプローチにより、階層構造の大規模デザインを一度に読み込みサブ・ブロックに分割し、使用するプロセッサの数に応じて高速に等価性検証を処理できる。

Oasys Design Systemsによると、「Oasys RealTime Parallel EC」を用いて約1900万ゲートのデザインを10個のプロセッサで約2時間、約600万ゲートのデザインを10個のプロセッサで約20分で処理するなどのベンチマーク・データがあるとの事で、合成ツール「RealTime Designer」と同じくその処理の速さを強調。既存の等価性検証ツールを上回る速さ、容量、シンプルさをアピールする。

2013.05.15

2013年5月14日、SystemCからの高位合成ツールを手掛けるForte Design Systemsは、「Cynthesizer」の最新バージョン「Cynthesizer 5」を発表した。

発表によると「Cynthesizer 5」では、その合成コアが刷新され、スケジューリングとアロケーションを組み合わせる新たなアーキテクチャを採用。「ローパワー合成機能」が大幅に強化されたほか、スケジューリング・アルゴリズムの改良により合成する回路の面積を前バージョンよりも平均9%削減可能となった。

Forteによると、新機能「ローパワー合成機能」は、ユーザーの指定によりdatapath power, register power, clock tree power, の3種類の消費電力を最適化する事が可能。これらはForteが特許出願中の高位合成向けのクロック・ゲーティング機能、ステート・マシン最適化機能などにより実現されている。また、memory powerに関しても、メモリ・アクセスの最適化によりローパワー化する事が可能だという事で、これらパワー最適化機能を組み合わせて利用する事で消費電力を60%またはそれ以上削減する事ができるという。

また、「Cynthesizer 5」では、搭載されるGUI「Cynthesizer Workbench」も改良され、SystemC Integrated Development Environment (IDE)が用意された。同SystemC IDEに付属する「kick-starters」と呼ばれるテンプレートを利用すれば、SystemCモデルの作成などSystemC設計作業を効率化できるという。

「Cynthesizer 5」は既に提供が開始されており、6月2日からAustinで開催される第50回DACにて披露される予定。

2013.05.13

2013年5月9日、フォーマル検証ツールを手掛けるJasper Design Automationは、同社が「2013 Red Herring Top 100 North America」のファイナリストに選出された事を発表した。

「Red Herring 100 North America」は、革新的なテクノロジーと優れたビジネスモデルを持つ北米ハイテク企業に贈られる権威ある賞で、毎年北米企業100社を選出。2006年には、SPICEシミュレータのBerkeley Design Automationが同賞を受賞している。

Jasperは、フォーマル検証ツールを提供するEDAベンダとしては老舗の企業と言える存在だが、ツールの機能エンハンスとラインナップの拡張に力を注ぎ続け、IPベンダの最大手ARMのほかにBloadcommやNVIDIAなど先端プロセス製品を展開するファブレス各社に製品が採用されており、公表されていないが半導体最大手のIntelも採用している様子。今回の「2013 Red Herring Top 100 North America」のファイナリスト選出は、ここ最近の同社の活況の表れと言える。※「2013 Red Herring Top 100 North America」の受賞企業は5月23日に発表される予定。

※株式会社シンコム(Jasper Design Automation社製品国内代理店)

2013.05.13

2013年4月29日、Synopsysは、SynopsysがFreescaleの車載マイコン「Qorivva」ファミリ向けのバーチャル・プラットフォーム開発キット「VDK」のリリースを発表した。

Synopsysの「VDK(Virtualizer Development Kits)」は、同社のバーチャル・プロトタイピング・ツール「Virtualizer」で使用するソフトウェア開発用の仮想ハードウェア環境をあらかじめキットとしてパッケージしたもの。既にARMv7/v8 プロセッサ向けの「VDK」がリリースされているほか、「RH850ファミリ」を始めとする各種ルネサス製車載マイコンの「VDK」も開発がアナウンスされている。(※関連ニュース)

今回Synopsysが発表したFreescaleの車載マイコン「Qorivva」ファミリ向けの「VDK」は、自動車の制御アプリケーションの開発をターゲットとするもので、マイコン型番「MPC5643L」をベースに構成されているが他の「Qorivva」ファミリ製品向けにも拡張可能。「VDK」には、マルチCPUコア、タイマ、メモリ、LIN/CANなどの通信ブロック、アナログ部、エラー制御モジュールなどの各モデルが含まれており、同キットを用いることですぐにソフトウェアの開発が可能。Synopsysは例えばこのキットを利用すれば、自動車向けの機能安全規格であるISO 26262向けのテストを効率化できるとする。

また、同「VDK」には、自動車向けソフトウェア開発向けのユース・ケースとなるサンプル・コードやスクリプトが用意されているほか、同社のアナログ-デジタル混在シミュレーター「Saber」、Mathworksの「Simulink」、Vectorのネットワーク・シミュレータ「CANoe」といったサードパーティー・ツールとのインテグレーション用のインタフェースも埋め込まれているという事で、車載ECU向けのソフトウェア開発のバーチャル・プラットフォームとして包括的なソリューションに仕立て上げられている。

2013.05.13

2013年4月25日、Synopsysは、画像認識向けのASIP(特定用途向けプロセッサ)開発をターゲットとした「Embedded Vision Development System」を発表した。

発表によると「Embedded Vision Development System」は、同社のカスタム・プロセッサ開発環境「Processor Designer」とプロトタイピング・システム「HAPS」をベースとしたもので、「Processor Designer」で開発したASIP(RTL)を迅速に「HAPS」に実装できるだけでなく、画像認識向けのASIP開発用に検証済のデザイン例も用意されており、それらを利用してASIP開発を効率的に進める事ができる。また、「Processor Designer」はもともとC/C++で記述された既存資産や機能をサポートしているが、同「Embedded Vision Development System」に付属するモディファイ可能なプロセッサ(デザイン例)では、OpenCVライブラリによって提供される機能を全てサポートしているという。

Synopsysによると「Embedded Vision Development System」は、ADAS(先進運転支援システム)、AR(augmented reality)、ロボティクス、 advanced driver assistance systems (ADAS), augmented reality (AR), robotics, 監視システム、ジェスチャー・コントロールといったアプリケーション向けのASIP開発を想定したもので、既に製品パッケージとしてリリースされている。

2013.05.09

2013年5月1日、SoC設計のESLサービスを手掛けるインドのCircuitSutra Technologies社は、バーチャル・プラットフォーム開発のためのソリューションを発表した。

今回CircuitSutra Technologiesが発表したのは、「CSTML(CircuitSutra Modeling Library)」と呼ぶSystemCモデル・ライブラリと、「VP-QSP(Virtual Platform - Quick Start Package)」と呼ぶバーチャル・プラットフォーム開発のためのモデル・セットで、いずれも独自に開発したSystemC準拠の各種モデルを製品化したもの。

モデル単体として販売するのが「CSTML」、用途に応じてバーチャル・プラットフォーム向けにパッケージ販売するのが「VP-QSP」という位置付けで、これらをバーチャル・プラットフォームの開発で利用すれば、その開発期間を80%短縮できるとCircuitSutraは主張する。いずれのモデルも市販のESLツールで利用可能で、「VP-QSP」は現在以下のラインナップを用意している。

VP-QSP-ARMCoreTile

VP-QSP-AUDIO

VP-QSP-UART

VP-QSP-SPI

VP-QSP-ETHERNET

VP-QSP-USB

※画像はCircuitSutra TechnologiesのWeb上の画像

尚、CircuitSutra Technologies社の製品・サービスは、現在、REVSONIC株式会社が国内代理店として取り扱っている。

2013.05.08

2013年5月7日、Cadenceは、ポーランドのEvatronix社のIP事業部を買収することを発表した。

Evatronixは、1991年にCAD/EDA/CAM製品の販売代理店として設立された会社で、本拠はポーランドにある。AutodeskやAltiumなどの製品を販売する傍ら、オリジナルのIP開発を手掛け、Intel 8051互換のIPコアの成功を皮切りにIPビジネスを拡張させた経緯を持つ。

現在Evatronixは、8051コアの他にSuperSpeed USB 3.0/2.0, NAND Flash/SD/SDIO/eMMCの各種コントローラ、JPEG 2000、4Kディスプレイ。コントローラ、MIPI SLIMbusなどのIPを提供しており、その顧客数は600。USBコントローラのライセンス提供数は200近くあるようで、NANDフラッシュのコントローラーは東芝にも採用されているようだ。

CadenceはこれらEvatronixのIP事業を事業を買収し、同社のIPポートフォリオを更に拡張。買収は2013年第2四半期中に完了し、EvatronixのIP事業はCadenceの一部として事業を継続する。

CadenceはIP事業の拡大に力を注いでおり、今年に入りインドのCosmic Circuits、米Tensilica、そして今回のEvatronixとIP事業関連の買収は3件目。調査会社Gartnerの調べによると、2012年の世界IP売上ランキングでは16位となっているが、Tensilicaほか2社の売上を合計すると2013年には5位に浮上する計算となる。(首位はARM、2位Synopsys、3位Imagination Technology、4位CEVA)

2013.05.08

2013年5月7日、Alteraは、同社デバイス向けの専用設計ツール「Quartus II」の最新版v13.0のリリースを発表した。

発表によると最新の「Quartus II v13.0」では、コンパイル時間の改善が図られ、SoC FPGAを含む28nm FPGAをターゲットとするデザインでコンパイル時間を平均25%短縮可能。ハイエンドの28nm FPGA「Stratix® V」をターゲットにしたデザインの場合、従来バージョンよりもコンパイル時間を平均50%短縮することができるという。

またAlteraは、今回のバージョンアップと合わせて昨年11月に発表した、OpenCLを用いたFPGAベース・システム開発用のSDK(SDK for OpenCL)を一般向けにリリース。システム統合ツール「Qsys」、DSP開発ツール「DSP Builder」もそれぞれサポートするデバイスや機能を拡張した。

2013.05.07

システム記述言語「SystemC」にフォーカスした技術セミナー「SystemC Japan」。

8回目の開催となる今年のSystemC Japan 2013では、Accellera Systems Inisiative主催の下、国内外16社のスポンサー企業が協力し、過去最大級の規模で開催致します。

セミナー終了後のレセプション・パーティーでは、スポンサー企業14社のソリューションを展示し、恒例のプレゼント抽選会も実施致します。

SystemCの最新技術、最新動向が分かる「SystemC Japan 2013」に是非足をお運び下さい。

SysmteC Japan 2013運営事務局

2013.05.06

2013年5月3日、米SIA(Semiconductor Industry Association)は、2013年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年3月の世界半導体売上は、前年同月比0.9%増、前月比1.1%増の234.8億ドルで、昨年11月より5ヶ月連続で前年売上実績を上回った。2013年Q1(1-3月)の売上累計と昨年同時期の売上を比較すると、今年は現時点で前年比0.9%増となっている。

2013年2月の売上を地域別でみると、北米、日本市場が前年比、前月比共に売上を落としたのに対し、欧州およびアジア市場が伸び、欧州は前月比で5.7%増、アジアは前年比で6.9%増という結果を残した。日本市場は前年比18%減と5ヶ月連続で2ケタ減となっており、市場の低迷が深刻化している。日本市場は昨年8月から8ヶ月連続で売上前年割れとなっており、アベノミクス効果は未だ半導体売上に現れていない。

2013.04.30

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2013.04.30

2013年4月25日、Alteraは2013会計年度第1四半期(13年1-3月)の売上を報告した。

発表によるとAlteraの2013年Q1(13年1-3月)売上は、前年比約7%増、前期Q4比約7%減の4億1050万ドル、営業利益は前年とほぼ同一、前期Q4比約3.7%増の1億2020万ドルだった。Alteraが四半期売上で前年実績を超えるのは7四半期ぶりとなる。

AlteraのQ1売上を地域別で見ると、全ての市場で前Q4の売上を超える事は出来なかったが、北米およびアジア市場において前年比20%増を超える大きな伸びを示した。

Q1売上を分野別で見ると、全てのカテゴリで前年増を達成。中でも主力のテレコム/ワイヤレス分野とネットワーキング/ストレージ分野が好調だった。

製品別では、Stratix V、Arria V、Cyclone Vといった最新の28nm製品を含む新製品カテゴリの売上が前年比68%増と大きな伸びを見せた。尚、AlteraはこのQ1において、Intelの14nmプロセスを用いたFPGAの製造計画を発表している。

Alteraは次期2013年Q1(1-3月)の売上を2013年Q1の4%増と予測している。

2013.04.30

2013年4月24日、Xilinxは2013会計年度第4四半期(2013年1-3月)の売上を報告した。

Xilinxの2013年Q4(13年1-3月)の売上は、前年同時期比5%減、前期Q3比4%増の5億3220万ドル。営業利益は前年比とほぼ同一、前期Q3比22%増の1億4720万ドルという結果だった。

Xilinxの2013会計年度(12年4月-13年3月)の売上合計は、21億7000万ドルで前年比3%減、純利益は前年比8%減の4億8750万ドルであった。結果として売上は前年度を下回ったが、粗利益率は、前年度の65%から1ポイント上昇し66%となった。

Xilinxは2011会計年度に売上23億7000万ドルを叩きだし過去最高を更新して以来、これで2年連続の売上減少。四半期ごとの売上を見ても調子が振るわず、ここのところ7四半期連続で売上前年割れとなっている。

Q4売上を地域別でみると、前年増となったのはアジアのみで、北米、欧州、日本と軒並み前年割れで各市場で7-10%売上を落とした。

Q4売上を分野別でみると、メインのコミュニケーションおよびデータ・センター分野、産業および宇宙航空/防衛分野が揃って前年割れ、放送、民生機器/車載分野だけが前年比3%増の伸びを示した。

製品別売上では、Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6で構成される新製品カテゴリの売上が好調で前Q3に対して12%増を記録、売上全体に占める割合を27%にまで伸ばした。

Xilinxは次期2014年Q1(13年4-6月)の売上を今期の1-5%増と予測している。

2013.04.25

2013年4月24日、Cadenceは、2013会計年度第1四半期(2013年1-3月)の売上を報告した。

Cadenceの2013年Q1売上は、前年同時期比約12%増、前期Q4(12年10-12月)と比較して約2%増の3億5400万ドル。純利益は前年の倍位以上となる7900万ドルだった。(※GAAP基準による会計結果)

CadenceQ1実績は前Q4実績報告時の予測を上回る好調なもので、これで13四半期連続で売上前年比増を記録。同社の社長兼CEOであるLip-Bu Tan氏は、売上好調の要因の一つとしてエミュレータ「Palladium XP」のリピート・オーダーを挙げている。

尚、Cadenceは3月に発表したTensilicaの買収が完了した事を合わせて発表。これにより2013年は約5700万ドルの売上増を見込んでいるという。

Cadenceは次期2013年Q2の売上を今期実績を更に上回る3億5500-6500万ドル、2013年の年間売上予測を14億4000万-14億4700万ドルと予測している。

2013.04.24

2013年4月23日、ARMは、2013会計年度第1四半期(2013年1-3月)の売上を報告した。

ARMの2013年Q1の売上は、前年比26%増、前期比0.4%増の2億6390万ドルで過去最高、営業利益は前年比約44%増の8940万ドルだった。売上の内訳を見るとライセンスの売上が前年比約24%増の9490万ドル、ロイヤリティの売上が前年比約32%増の1億4000万ドルだった。前期のQ4に対してライセンスの売上は落としたが、ロイヤリティの売上が増え、結果的に前期を上回る売上を達成した。ARMは2010年Q1より四半期売上の前年増を継続しており、今期で13四半期連続で売上前年増となった。

ARMはこのQ1で計22件のプロセッサ・ライセンスを獲得(前Q4は36件)。その内最も多かったのがCortex-Aプロセッサのライセンスで9件、その他にbig.LITTLE技術の採用に伴うARMv8アーキテクチャー・ライセンス1件、GPU Maliのライセンス3件などが含まれていた。

また、半導体ファウンドリとの各種プロセス・ノード別のプラットフォーム・ライセンスとして40nmプロセスの契約が1件増え、の総数は計100件となった。フィジカルIPであるPOP IPのライセンス契約は2件増え、うち1件は初となるGPU MaliのPOP IPであったという。

※画像はARM発表資料より抜粋

2013年Q1で出荷されたARM搭載チップの総数は前年比35%増の約26億個で前Q4よりも1億個増えた。その半数以上はモバイルデバイス向けで前年比25%増、組み込み向けは全体の25%で個数としては前年比50%増の伸びを示した。出荷されたプロセッサの個数を種類別で見ると、Cortexシリーズの出荷数が全体の45%に到達し、前期Q4の40%を上回った。

※画像はARM発表資料より抜粋

2013.04.19

2013年4月17日、ARMは、同社の省電力技術「big.LITTLE」の普及に向け新たなライセンス・モデルを発表した。

発表によるとARMは、2つのプロセッサ・コアを用いて実現する省電力技術「big.LITTLE」を採用する顧客向けに、「big.LITTLE」処理を実現するパッケージ化された単一の「使いきり」ライセンスを用意。同ライセンスには、プロセッサ・コア「Cortex-A15」、「Cortex-A7」、キャッシュ・コヒーレント・インターコネクト「CCI-400」、ジェネリック・インタラプト・コントローラ「GIC-400」、AMBAドメイン・ブリッジ「ADB-400」がパッケージされており、一つの「big.LITTLE」システムの開発に対してのみ利用可能。要望に応じてGPU「Mali-T600」やフィジカルIP「POP(Processor Optimization. Package)」も追加できる。

ARMによると同社の「big.LITTLE」技術を採用した顧客は、Samsung, Renesas, CSR, Fujitsu, MediaTekなどをはじめ既に世界で17社。今回発表された新ライセンスは、はこの「big.LITTLE」技術の採用を更に拡大するために用意されたもので、オプションとして永久ライセンスも用意される。

2013.04.19

2013年4月17日、PCB設計用の回路図キャプチャとハード設計者向けのWebサイトを手掛けるAspen Labsは、無料のオンラインPCB設計ツールの提供を発表した。

発表によるとAspen Labsの提供するPCB設計ツール「PCBWeb」は、電子部品オンライン販売の最大手Digi-Keyとのコラボレーションによって開発されたもので、Digi-Keyの取り扱う電子部品のライブラリを備えており、それら電子部品をPCB設計環境で取り扱う事が可能。部品データの管理機能も備えられている。

設計機能としては、マルチシート対応の回路図キャプチャ、多層基板対応のDRC付きPCBレイアウト、シンボル/フットプリント作成用のコンポート・エディタが統合されており、一通りのPCB設計作業が可能。無料のオンライン・ツールとして専用サイト上で誰でも利用することができる。(現在はベータ版という扱い)

Aspen LabsとDigi-Keyは、以前から提携によりオンラインの無償設計ツールを手掛けており、今回発表した「PCBWeb」が3つめのソリューション。その他に、回路図キャプチャ「Scheme-It」とSPICEエンジン、回路図キャプチャ、波形ビューワからなるオンライン・ツール「PartSim」も提供している。

2013.04.18

2013年4月17日、ARMとArterisは、両社の複数年に渡るパートナーシップ契約について発表した。

発表によるとArterisとARMは、ArterisによるARMプロセッサコアIPの利用を拡張する複数年契約を締結。これによりArterisは、ARMの最新コア「Cortex-A15」および「Cortex-A7」を利用する事が可能となった。今回の契約はARM/Arterisの顧客であるSoC設計者に更なるインターコネクト・オプションを提供するためのもので、ArterisはARMとの協力関係を拡張し今後のコヒーレント・インターコネクトIPの開発を進める。

2013.04.18

2013年4月16日、ハード設計/EDA関連規格の標準化組織米Accellera Systems Initiativeは、IPのトラッキングに関する新たな標準規格「Soft IP Tagging 1.0」のリリースを発表した。

Accelleraの策定した標準規格「Soft IP Tagging 1.0」は、チップ設計で用いられるソフトウェアIPにタグ付け行う事で、設計プロセス全体に渡ってソフトウェアIPをトラッキングするためのもので、IPのロイヤリティ管理、バージョン管理、再利用などを目的に作られた規格。チップ設計の現場に加え、半導体ファウンドリー、IPベンダ、EDAツール・ベンダなどの利用が想定されている。

2年前の2011年4月に当時のAccellera内に「IP Tagging Technical Subcommittee」が立ち上げられ、その後規格の策定作業が進められていたが、ようやく最初のバージョンとなる「Soft IP Tagging 1.0」が公開された。

「Soft IP Tagging 1.0」は、オープン・ソース・ライセンスとしてAccelleraのWebページから誰もが無償でダウンロードする事ができる。

2013.04.18

2013年4月9日、Mentor Graphicsは、SAS(Serial Attached SCSI)Gen2向けの検証ソリューションとして、「iSolve SAS」と検証IPを発表した

今回Mentorが発表した「iSolve SAS」は、同社のエミュレータ「Veloce」に接続して用いるオプションのハードウェア・ユニットで、SAS Gen2設計の検証に役立てる事が可能。もう一つのSAS検証IPは、トランザクションベースの検証IPとして、シミュレータ「Questa」およびエミュレータ「Veloce」の双方で利用する事ができる。これらSAS Gen2向けの検証ソリューションは、SAS Gen1とも完全な互換性を備えているという。

2013.04.18

2013年4月15日、Synopsysは、LG Electronicsが同社の物理検証ツール「IC Validator」を採用した事を発表した。

発表によるとLGは、Synopsysの「IC Validator」をARMベース・デザインのインプリメント・フローにて採用。同フローで利用しているSynopsysの配置配線ツール「IC Compiler」と「IC Validator」を統合運用することで、既存の物理検証ツールを用いた手法よりもフィジカル・サインオフ検証を2週間短縮する事が出来たとしている。

Synopsysの「IC Validator」の最大の特徴は、フィジカル設計とフィジカル検証を別々の作業工程とすることなく「設計しながらの検証」を実現できる点にあり、設計と検証との間のイタレーションを無くし、DRCやメタル・フィルをワンパスで実行する事が可能。「IC Compiler」と連携してDRCエラーの自動修正を実行できるなど、フィジカル検証の時間を大幅に削減できる。

2013.04.12

2013年4月10日、WebサイトSemiWikiが報じたところによると、CadenceはBerkeley Design Automationを著作権の侵害で提訴した。

SemiWikiの記事によると、Berkeley DAは、かつてCadenceのアライアンス・プログラム「Cadence Connections program」のメンバーとして、Cadenceのアナログ設計環境「Virtuoso Analog Design Environment(ADE)」に同社のSPICEシミュレータ「Analog FastSPICE(AFS)」を接続するインタフェースを開発できる立場にあったが、その契約条項に反する形でツールの接続インタフェースを開発したため、著作権の侵害を理由にCadenceに提訴された。

具体的には、CadenceのAFSへのインタフェースの開発は、CadenceのOasisインタフェースを通じてAFSとのインタフェースをとらなければならず、その使用にあたってはエンドユーザーがCadenceのOasisのライセンスを保有していなければならないが、Berkeley DAの開発したインタフェースは、Oasisを通じたものではなく、Oasisライセンスを持たないユーザーでも利用できるものであったとCadenceは主張。この事実は単なる契約違反に留まらず著作権侵害にあたるとして、CadenceはBerkeley DAを提訴した。

Cadenceは、提訴する前にBerkeley DAに対して契約違反の是正を繰り返し求めたが、Berkeley DAがこれに応ずる事が無かったため、同社とのアライアンス・プログラムの更新を行わず、提訴に踏み切ったとしている。

これに対しBerkeley DAは、Cadenceとの契約に反した事実は無く、Cadenceの著作権も侵害していないとして、法廷で争う構えを見せているという。

2013.04.12

2013年4月9日、バーチャル・プラットフォーム「OVP」を手掛ける英Imperasは、新たなARM製プロセッサ・モデルのリリースを発表した。

Imperasが今回リリースしたのは、ARMの低消費電力コア「Cortex-A7 MPCore」のプロセッサ・モデルで、同モデルはImperasの提供するTLM2.0ベースのバーチャル・プラットフォーム「OVP」上で利用する事が可能。Imperasのシミュレータ「OVPsim」でシミュレーションできる。

Imperaは既に「Cortex-A7 MPCore」モデルとサンプルのバーチャル・プラットフォームの提供を開始しており、これらは www.OVPworld.org から無償で入手可能。ImperasのOVP環境で提供されるモデルは全て無償でシミュレータとソフト開発環境は有償となっている。

尚、バーチャル・プラットフォーム用の「Cortex-A7 MPCore」モデルは、SynopsysとCarbon Design Systemsも既に提供している。

2013.04.11

2013年4月9日、ARMは、同社最新のプロセッサ・コア「Cortex-A50」シリーズのフィジカルIPのリリースを発表した。

今回発表されたのは64ビット対応、ARMv8アーキテクチャのプロセッサ・コア「Cortex-A57」および「Cortex-A53」のPOP(Processor Optimization. Package)でTSMC 28nm HPMおよび16nm FinFETプロセスをターゲットとしたもの。28nm HPMバージョンは既に出荷されており、16nm FinFETバージョンは今年Q4のリリースを予定しているという。同フィジカルIPを利用すれば短期間で最適なプロセッサ・コアの実装を実現できる。

ARMは、SamsungやGlobalFoundriesのプロセス向けのPOPも提供しているが、Cortex-A57/A53のPOPのリリースは今回が初。Cortex-A15/A7の時と同じくARM最新コアのPOPはTSMCのプロセスからという形となっている。

2013.04.11

2013年4月10日、Synopsysは、富士通セミコンダクターが同社のIPを用いて2G/3G/4Gベースバンド・プロセッサを設計したことを発表した。

発表によると富士通セミコンダクターは、顧客向けの2G/3G/4Gベースバンド・プロセッサの設計にSynopsysの設計IP「DesignWare DigRFv4 M-PHY」と「DesignWare DigRF 3G PHY」を使用。自社のRFトランシーバLSIと開発対象のベースバンド・プロセッサのインターオペラビリティを確保するために、ターゲットとしていた28nmプロセスに対応するMIPI規格のインタフェースIPを必要としており、SynopsysのIPを採用した。これにより低消費電力のベースバンド・プロセッサをスケジュール通りにテープアウトし、量産立ち上げに成功したという。

2013.04.10

2013年4月5日、Mentor Graphicsは、パワー記述フォーマットの標準規格IEEE 1801 UPFをベースとしたローパワー検証フローを発表した。

IEEE 1801 UPFは、消費電力に関する設計意図を記述するためのフォーマットで、ローパワー設計の効率化とツールの互換性の促進を狙うもの。今回Mentor Graphicsは、同社の機能検証プラットフォーム「Questa」とエミュレータ「Veloce」の2つの製品により、IPレベルからシステム・レベルに対応する包括的なローパワー検証フローを確立した。

具体的には、「Questa」の最新バージョンにてUPFベースのローパワー設計関連の機能を大幅に拡充。UPFシミュレーション性能を最大6倍にまで引き上げたほか、新たにローパワー設計向けの視覚化機能をGUIに追加、UPFによる影響を検証・デバッグ可能なローパワーの自動チェック機能も備えた。更にローパワーのカバレッジ指標を自動化する機能、ローパワー設計用テストプラン生成機能も追加し、ローパワー設計のカバレッジ収束の効率化が図られている。

また、Questaファミリ製品のCDC検証ツール「Questa CDC」においてもパワー記述フォーマットUPF向けの機能拡張が図られており、「Questa CDC」の最新バージョンでは、UPFを読み込み、複数のクロックドメインにわたるパスに挿入された、ローパワー設計意図のロジックに起因するエラーを自動的に検出することが出来るという。

尚、エミュレータ「Veloce」に関しては、Mentor曰くUPFを最も幅広くサポートしており、UPFでローパワー設計意図が記述されたロジックを実装し、エミュレーションによってローパワーの機能を動的にチェックする事が可能。Veloceでは、消費電力管理がクリティカルな動作シナリオをアプリケーションレベルのソフトウェアとして実行し、電力制御のステートマシンを検証することが出来るという。

2013.04.09

2013年4月5日、ARMとCadenceは、TSMC 16nm FinFETプロセスを用いたARM Cortex-A57の設計に関する両社の協業を発表した。

発表によるとARMとCadenceは、TSMCも含めた形で業界初となるARM Cortex-A57プロセッサ搭載チップのテープアウトに向けて協業。CadenceはEDAツールベンダとして、ARMアーキテクチャやTSMCのライブラリを考慮して設計ツールを最適化し、テスト・チップのテープアウトに貢献した。(関連ニュース)

今回ARM Cortex-A57プロセッサ搭載のテスト・チップの設計に用いられたのは、Cadenceのインプリメント環境「Encounter」を中心とするRTL-to-signoffフロー、カスタム設計プラットフォーム「Virtuoso」、ARM Artisanスタンダードセル・ライブラリ、TSMCのI/Oライブラリ、メモリ、PLLマクロで、CadenceはTSMC 16nm FinFETをターゲットとした設計を実現するために、以下の課題を解決したとしている。

・新しい設計ルール

・3DトランジスタのRC抽出

・インターコネクトとビア向け抵抗モデルのさらなる複雑化

・量子化されたセル・ライブラリ

・多層にまたがる新しいトランジスタ・モデルやダブル・パターニングをサポートするライブラリ・キャラクタライゼーション

尚、Cadenceのツールは、2011年10月にARMとTSMCが初めてTSMC 20nmプロセスで「Cortex-A15」をテープアウトした際にも利用されており(関連ニュース)、TSMCの先端プロセスを用いたARM最新コアの実装においては、直近の2世代においてARM,Cadence,TSMCの強力な三つ巴のコラボレーションが確立されている。ちなみに、TSMCが2010年に28nmプロセスでテストチップを設計した際に利用されていたのはMagma,Synopsysのツールであった。(関連ニュース)

2013.04.08

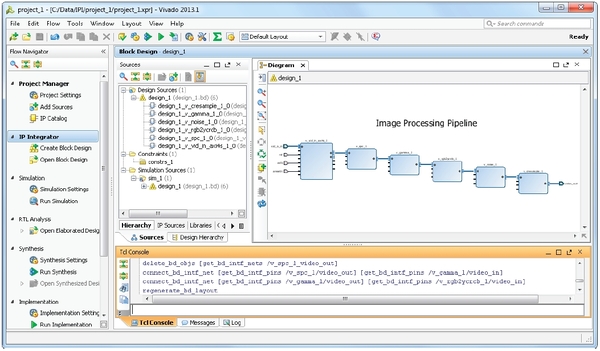

2013年4月4日、Xilinxは、同社の設計環境「Vivado Design Suite」のバージョンアップを発表した。

発表によると今回のバージョン・アップによる機能向上は大きく2つ。

まず、昨年6月の「Vivado」発表時点からロードマップに掲げていた、システムレベルのIPインテグレーション機能「IP Integrator」を実装した。同機能はTCLベースの対話型の環境で、デザインにおけるIPブロックのインテグレーションを容易化するもの。グラフィカルな環境上でARM AXIバスなど主要なインタフェースにIPを自動接続する事が可能なほか、 IPサブシステムの構築、複雑なIPインタフェースを含むシステムのDRC検証、IPインタフェースのトレードオフ、デバッグなど、インタフェース・レベルでのIPベース・システム設計機能を一通り包含しており、新規アルゴリスムやIP、RTL資産などをベースに組み上げたシステムを「Vivado」、「Vivado HLS」、「System Generator」を用いてそのままFPGAに実装する事ができる。

「IP Integrator」によるIPの接続は信号レベルではなく、インタフェース・レベルでの接続で、IPのパラメーターは自動的に設定および伝搬される仕組み。また、「IP Integrator」は、プロセッサ・ベースであるか否かに関わらずデザイン作成が可能で、作成したIPサブシステムを再利用する事も可能となっている。

※画像はIP IntegratorのGUI画面。Xilinx社Web上のブローシャから抜粋。

この「IP Integrator」は、メタデータの記述フォーマットIEEE 1685(IP-XACT)標準の技術を用いた機能で、ユーザーは「IP Packager」と呼ばれる機能を用いて、HDLで記述されたRTL、C/C++/SystemCモデル、MATLAB/Simulinkのアルゴリズム・モデルをパッケージ化し「IP Integrator」で使用する事が可能。それらパッケージ化されたIPは「IP Catalog」と呼ばれるレポジトリ機能で登録・管理することができ、FPGA設計用のデザイン・ライブラリとして共有できる。

今回追加された「IP Integrator」は、高位合成機能「Vivado HLS」と合わせて、より複雑化、大規模化、IPベース化するFPGAデザインの抽象度をシステム・レベルに引き上げるもので、Xilinxは設計生産性を4倍向上と謳うが、設計の効率面だけでなくFPGA設計における社内の資産管理などの面においてもその利用効果は高いと思われる。

今回のバージョンアップのもう一つの目玉は、高位合成機能「Vivado HLS」のライブラリ拡張で、Xilinxは「Vivado HLS」の合成用のライブラリとして新たに浮動小数点演算「math.h」とリアルタイム・ビデオ・プロセッシング機能を追加した。ユーザーはこれらライブラリを用いる事でビデオ・プロセッシング・アプリケーションの開発とそのパフォーマンスを同時に加速できるようになる。

かつてXilinxは、各種アライアンスなどを通じて社外のEDAベンダとの連携により自社FPGAの開発環境を拡充する戦略を展開していたが、その後独自の環境構築強化に方針を変更。結果的にこの判断が「Vivado」の開発に繋がり、SoC/ASIC開発の世界で理想とされる、高い抽象レベルでのIPベースのシステム設計とその実装を実現するに至っている。

2013.04.04

2013年4月4日、ハード設計/EDA関連規格の標準化組織米Accellera Systems Initiativeは、新たな規格の標準化を目指す「Multi-language Working Group」の発足を発表した。

発表によるとAccellera Systems Initiativeの「Multi-language Working Group(MLWG)」は、複数の設計言語による検証環境ならびに検証コンポーネントの相互運用を実現するための標準規格の策定を目的に発足したもので、Accelleraは同グループへの参加を呼びかけている。

MLWGは、異なる設計言語で構築された検証環境を組み合わせる手段と合わせ、検証メソドロジ UVM (Universal Verification Methodology) のコンセプトの導入も想定しており、UVMを拡張し既存の検証IP資産を再利用できる形を目指すとしている。

2013.04.03

2013年4月2日、ARMとTSMCは、両社の協業によりTSMC 16nm FinFETプロセスで「ARM Cortex-A57」をテープアウトした事を発表した。

ARMの「Cortex-A57」プロセッサは、昨年10月に発表されたARMの次世代ハイエンド・プロセッサで、ARMv8アーキテクチャをベースに開発された既存のハイエンド・プロセッサ「Cortex-A15」の後継品。ARMコアとして初めて64ビット命令にも対応し、20nm以下のプロセスでの製造をターゲットとしている。

今回、ARMとTSMCは共同でTSMCの16nm FinFETプロセス・テクノロジーを使用して初となる「Cortex-A57」プロセッサをテープアウト。両社はTSMCの16nm FinFETプロセスに対する「Cortex-A57」プロセッサの最適化に取り組み、ARM ArtisanフィジカルIP、TSMCのメモリ・マクロ、TSMCの設計エコシステム「Open Innovation Platform」の提供するEDAツールを利用し、6ヶ月という短期間でRTLからのテープアウトを完了した。

尚、今回の「Cortex-A57」プロセッサの実装に使用した具体的なEDAツール名は明らかにされていないが、2011年10月にARMとTSMCが初めてTSMC20nmプロセスで「Cortex-A15」をテープアウトした際は、Cadenceのアナログ/カスタム環境「Virtuoso」やデジタル・インプリメント環境「Encounter」が利用されていた。(関連ニュース)TSMCは、昨年10月に20nmプロセスのリファレンス・フローを発表したばかりで、16nm FinFETプロセスに関しては今年の秋以降にリファレンス・フローが発表される可能性が高い。

「Cortex-A57」プロセッサは、今のところ2013年末から2014年にかけて市場に投入される予定で、製品の普及に向け物理IPの最適化を目指すARMと、自社プロセスでの受注拡大を目指すTSMCの狙いが両社の協業体制を強固なものにしている。

2013.04.02

2013年4月1日、米SIA(Semiconductor Industry Association)は、2013年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年2月の世界半導体売上は前年同月比1.4%増、前月比3.8%減の232.5億ドルで昨年11月より4ヶ月連続で前年売上を上回った。

2013年2月の売上を地域別でみると、アジア市場が1月に続いて好調を維持し前年比6.7%増、1月に前年比10.5%増と好調だった北米は微増に留まった。日本市場は前年比15.7%減と4ヶ月連続の2ケタ減で未だ立ち直る兆しが見えない。日本市場は昨年8月から7ヶ月連続で売上前年割れとなっている。

2013.04.02

2013年4月1日、米EDA Consortiumは、2012年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

EDACの発表によると、2012年Q4(10月-12月)の世界のEDA売上総額は、前年比4.6%増、前Q3比約9.8%増の17億7910万ドルだった。これで四半期ごとの世界EDA売上総額は、12四半期連続で売上前年比増を達成。2012年の世界EDA売上総計は前年比約6.6%増の65億2890万ドルで過去最高となった。

2012年Q4の売上を分野別に見ると、IC Physical Design & Verification分野以外のみ前期Q3に続いて売上前年割れ。その他の分野は売上前年比増を達成し、中でもPCB分野が前Q3に続いて前年比19.5%増と大きな伸びを示した。

2012年Q3の売上を地域別に見ると、全ての地域で売上前年比増を達成。最も伸びたのは欧州で前年比8.1%増、日本は前年比4.4%増だった。Q2,Q3と2ケタ成長を見せたアジアその他地域は前年比0.5%増と微増に留まった。年間を通した動きとしては、日本市場以外は各地域ともに売上前年増を達成。日本の年間売上は前年比約3%減だった。

世界EDA市場は約3年に渡り右肩上がりの成長を見せており、2009年の年間売上に対して2012年売上は37.5%増と大きく成長。しかし、その成長率は徐々に緩やかになりつつあり、今4半期の成長率はこの2年間で最も低いものとなった。

2012年Q4時点でのEDA業界の従業員数は29578人で、前年比7.1%増、前期Q3比2.4%増となっている。

2012年Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億9300万ドル 7.5%Up

■IC Physical Design & Verification分野 3億6040万ドル 8.2%Down

■IP分野 4億6740万ドル 8.1%Up

■サービス分野 9130万ドル 0.5%Up

■PCB/MCM分野 1億6700万ドル 19.5%Up

2012年Q4地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億6710万ドル 5.6%Up

■ヨーロッパ 3億3100万ドル 8.1%Up

■日本 2億5910万ドル 4.4%Up

■アジアその他地域 4億2180万ドル 0.5%Up

2013.03.28

2013年3月26日、Synopsysは、スタティック・タイミング解析ツール「PrimeTime」の新技術「PrimeTime ADV」の提供開始を発表した。

発表によると「PrimeTime ADV」は、リーク電流削減とECOの加速を目的とした新技術で、同社のデジタル配置配線ツール「IC Compiler」と連携してタイミング収束への最短パスと最小リーク電流を実現するもの。

今回の発表と合わせて先ずリリースされたのは「PrimeTime ADV」のリーク電流削減機能で、同機能は「IC Compiler」の低消費電力化機能、リーク電流削減機能を補完し、多様な動作モードやプロセスコーナーのシナリオに渡ってサインオフ品質のタイミング精度を維持しながらタイミング収束を実現する。

もう一つのECO機能「フィジカル・アウェアECOガイダンス機能」は今年6月にリリースされる予定で、同機能を利用すれば「PrimeTime」が把握できるフィジカル設計情報から最適なECOガイダンスが「IC Compiler」に渡され、より優れた配置配線を実行可能。これによりECOの影響を最小化でき、設計のやり直しを最小限に抑えることが可能になるという。尚、いずれの機能も特許取得済みの「PrimeTime ECOテクノロジ」をベースに実現されているとの事。

2013.03.28

2013年3月26日、Synopsysは、自動カスタム配線ツール「Galaxy Custom Router」を発表した。

発表によるとSynopsysの新ツール「Galaxy Custom Router」は、先端プロセスを用いたデザインなど、複雑なデジタル/ミックスド・シグナル・デザインに対応するシェイプベースの自動カスタム配線ツールで、シールド配線、差動ペア配線、等長(RC)配線、リバー配線、ポイント間のコーキシャル配線といったカスタム配線タスクを自動化。ダブルパターニングを含め、20nm以降のプロセス・テクノロジをサポートしている。

「Galaxy Custom Router」は、デジタル配置配線ツール「IC Compiler」との協調設計によるりデジタル/ミックスド・シグナル・デザイン設計を実現するもので、デフォルト/デフォルト以外のデザインルールや配線グリッド、配線禁止領域、配線ガイドといった「IC Compiler」で定義された制約条件も実行可能。Synopsysは「Galaxy Custom Router」を用いることで、従来の手作業での設計手法よりも設計生産性を2-5倍向上できるとしている。

海外のEDA関連情報サイト「SemiWiki」に掲載された情報によると、「Galaxy Custom Router」は、Synopsysが買収したMagmaのアナログ/ミックスドシグナル設計環境「Titan」の機能と自社開発した機能を組み合わせて実現したもので、「IC Compiler」のオプションとして提供され「IC Compiler」の環境上で動作。既にSynopsysの特定顧客において利用実績があり「Galaxy Custom Router」を用いて幾つかのチップがテープアウトされているという。

2013.03.27

2013年3月21日、ARMとSynopsysは、TSMC 28HPMプロセス・テクノロジ向けに最適化した「シノプシス・リファレンス・インプリメンテーション」の提供開始を発表した。

発表によると今回提供が開始された「シノプシス・リファレンス・インプリメンテーション」は、ARMベースのデザインの実装を加速するために用意されたもので、ARM Cortex-A15 MPCoreTM/Cortex-A7 MPCoreプロセッサ・クラスターとCoreLink CCI-400TMインターコネクトを用いたデザインの実装期間を短縮する事が可能。ARMの高性能化および低消費電力化のための技術である「big.LITTLE処理」ベースのシステム開発にも活用できる。

この「シノプシス・リファレンス・インプリメンテーション」は、Synopsysのインプリメント環境「Galaxyデザイン・プラットフォーム」と、ARMの「ARM Artisanスタンダードセル・ライブラリ」、「組込みメモリー」、「ARM POPテクノロジ」を用いて、TSMC 28HPMプロセス・テクノロジ向けに最適化されており、具体的な提供物としては、実装ツール向けのスクリプト、基準となるフロアプラン、設計制約条件、参照ドキュメントが用意され、Synopsysのツールをメンテナンス契約しているARMv7ライセンシー向けに提供される。

またARMとSynopsysは、ARM AMBA 4 ACEプロトコル、CCI-400インターコネクトをサポートするSynopsysの「Discovery Verification IP」をベースにした「リファレンス・ベリフィケーション・プラットフォーム」も用意。同プラットフォームを活用するとキャッシュ・コヒーレント・デザインのための効率の高い検証環境を迅速に構築できるという。

2013.03.26

2013年3月26日、カスタムIC向けのレイアウト自動化ソリューションを手掛ける英Pulsic社は、同社のアナログ専用自動配線ツール「Unity Analog Router」がSTARCのミックス・シグナル設計フローで認証された事を発表した。

発表によると、STARCは同社の策定する次世代ミックスド・シグナル設計フロー「STARCAD-AMS」でアナログIPリユース設計手法を確立し、設計期間を半減させる事を目指す中でPulsicのアナログ専用自動配線ツール「Unity Analog Router」を評価。「Switched Capacitor Filter」をモチーフに評価したところ、設計期間を約6割削減することができたという。

「Unity Analog Router」は、2011年にSTARCの「STARCAD-AMS」で認証されたカスタムLSI向け自動配線ツール「UniRoute」をベースに開発されたシェイプ・ベースのアナログ自動配線ツールで、レイアウト設計者による人で作業に近い配線を実現する事が可能。配線の制約や形状をデバイスの配置位置、配置状況から自動的に抽出する機能があり、ユーザーはあらかじめ配線制約を設定する必要がなく、ツールが自動抽出した配線制約を再利用する事ができる。STARCはこれら機能がもたらすTAT削減効果を評価し、「Unity Analog Router」を「STARCAD-AMS」で認証した。

2013.03.22

2013年3月19日、業界最速と称する高速RTLフィジカル合成ツールを手掛ける、米Oasys Design Systemsは、同社EDAツールの合成エンジンに「レジスタ・リタイミング」機能を追加した事を発表した。

「レジスタ・リタイミング」機能は、文字通りレジスタのリタイミングにより、回路の機能を変更すること無く自動的にパフォーマンス、エリア、消費電力を改善する機能で、同社の提供するRTLフィジカル合成ツール「RealTime Designer」およびRTL最適化ツール「RealTime Explorer」で共通で使用されている合成エンジンに追加される。同機能は既に提供されており、「RealTime Designer」ならびに「RealTime Explorer」のユーザーは使用可能との事。

-thumb-600x398-2512.jpg)