NEWS

2013.09.10

2013年9月8日、Synopsysは、同社のカスタム設計環境「Laker」がTSMCによって16nm FinFETプロセス向けツールとして認定された事を発表した。

発表によるとTSMCは同社の16nm FinFET process Design Rule Manual (DRM) V0.5にて、Synopsysのカスタム設計環境「Laker」(旧SpringSoft社製品)を認定。合わせて同16nmプロセスのPDK(プロセス・デザイン・キット)を用意した。このPDKは「iPDK」と呼ばれるツール環境に依存しない相互運用性の高いPDKでSynopsysの「Laker」をはじめとする各種EDAツールで使用可能。Synopsysは、TSMCと共に「iPDK」の利用促進にも力を注いでいる。

「Laker」はTSMC 16nm FinFETプロセスのサポートにあたり、レイアウト機能などFinFETデバイス向けの各種機能追加、機能強化を実施。最新の「Laker」は、TSMCの180nm-16nmまでの幅広いプロセスに対応している。

2013.09.09

2013年9月6日、Cadenceは、通信インタフェースHDMI 2.0に準拠した検証IPのリリースを発表した。

発表によるとCadenceのHDMI 2.0向け検証IPは、主要なシミュレータ、検証言語、UVMをはじめとする検証メソドロジをサポートしており、同検証IPを用いる事で設計したSoCがAV機器向けの次世代インタフェース規格「HDMI 2.0」に準拠しているかどうか確認することが可能。製品の市場投入を加速することができる。

「HDMI 2.0」規格はつい先日HDMI FORUMより正式発表されたばかりで、Cadenceも同団体のメンバーとして規格の策定に関与している。既にSynopsysから「HDMI 2.0」準拠の設計IPがリリースされているが、検証IPのリリースはCadenceの製品が業界初。Cadenceの発表には既に同検証IPを採用したSTMicroelectronicsがコメントを寄せている。

2013.09.09

2013年9月5日、Synopsysは、通信インタフェースHDMI 2.0に準拠した設計IPのリリースを発表した。

HDMI 2.0はAV機器向けの次世代インタフェース規格で、つい先日9/1にHDMI規格の策定をまとめているHDMI FORUMより正式発表されたばかり。当然、Synopsysも同団体のメンバーとして規格の策定に関与している。

今回業界に先駆けてSynopsysがリリースしたのは、HDMI 2.0仕様準拠のトランスミッター/レシーバー・コントローラーIP、PHY IP、Linuxドライバからなる「DesignWare HDMI 2.0 IP」で、HDMI 2.0で定義される全ての仕様ならびにファウンドリ各社の28nmプロセスをサポートしており、コンフィギュラビリティが高くチップ設計後もソフトウェアの更新による機能変更が可能でSoCの旧式化を防ぐことが可能。HDMI 2.0 PHY IPは、従来よりも消費電力を33%、面積を25%削減している。

また、ソフトウェア開発向けに用意される各種LinuxカーネルHDMI 2.0ドライバ(HDCP、EDID、CECなど)を利用することで、ソフトウェアの開発期間を数週間単位から数時間単位にまで短縮できるという。

発表には中国のファブレスAmlogic社がコメントを寄せており、既に同IPを4K HDTV向けSoCに採用した企業もあるようだ。

2013.09.06

2013年9月5日、SystemVerilogベースのESL合成ツールを手掛ける、米Bluespec社は、同社のDesktop Emulation向けソフト「semu」がXilinxの7シリーズFPGAをサポートした事を発表した。

Bluespecの「semu」は、市販のXilinx製ボードを用いて安価なエミュレーションを実現するためのソフトウェア・パッケージで、大規模デザイン全体ではなく、IPサブシステムやブロックレベルのデザインをターゲットにシミュレーターよりも高速な検証を目指すもの。そのエミュレーション速度は最大50Mhzに達する。

「semu」特に同社の提供するESL合成ツール「BSV」を必要とすること無く、RTL(Verilog)入力によりスタンドアロンで利用する事が可能で、ホストマシン上でFPGAを制御するCのAPIを自動生成し、専用のデバッグ環境を提供する。デバッグ能力としては再コンパイルを必要としない動的なデバッグが可能でブレークポイントの設定や、シミュレーション結果のVDCを読み込みエミュレーション結果と比較する機能も備えている。デザインのFPGAへの実装はXilinxの専用ツールを利用する。

※画像は全てBluespec提供のデータ

この「semu」は、今年3月にXilinxのFPGA「Virtex-6」を搭載する評価ボード「ML605」をサポートする形でリリースされたが、今回、そのサポート範囲が拡大されXilinx最新の28nmFPGA「Kintex-7」を搭載する評価ボード「KC705」および「Virtex-7」を搭載する「VC707」ボード、ならびにXilinxの専用環境「Vivado」も利用可能となった。これにより、 「semu」を用いたエミュレーションは最大350万ゲートのデザインに対応可能となる。

尚、「semu」の国内販売価格は年間100万円以下で、複数ライセンス購入にあたってはボリューム・ディスカウントも可能との事。同製品はサイバネットシステムが代理店販売を行っている。

2013.09.06

2013年9月4日、Mentor Graphicsは、台湾の半導体ファウンドリAdvanced Wireless Semiconductor Company(AWSC)による製品の導入事例を発表した。

AWSCは、高周波デバイスの製造を専門とするICファウンドリで、今回Mentorの「Calibre nmDRC」および「Calibre nmLVS」をGaAs IC向けのサインオフ物理検証ツールとして採用した。同社は新規のファウンドリ業務で「Calibre」を使用していく予定で、顧客にCalibreデザインルールデックを提供するという。

AWSCでは、元々TSMCとMentorが共同開発した「eqDRC(equation-based DRC)」と呼ばれる、歩留まり向上を目的としたDFM考慮のDRC機能なども活用していくようだ。

2013.09.05

2013年9月4日、Cadenceは、同社のRTL-GDSIIフローが中国の半導体ファンドリSMICの40nmプロセス向けリファレンス・フローに採用された事を発表した。

発表によるとSMICは、同社の40nm Reference Flow 5.1にてCadenceのローパワー設計向けデジタル・デザイン・フローを採用。同フローにはCadenceの以下のツールが含まれている。

-RTL Compiler

-Encounter Digital Implementation System

-Encounter Conformal Low Power

-Cadence QRC Extraction

-Tempus Timing Signoff Solution

-Encounter Power System

-Physical Verification System

-Cadence CMP Predictor

SMICの新しい40nm Reference Flow 5.1では、「Encounter Digital Implementation System」に含まれるクロック・ツリー・合成機能「CCOpt(Clock Concurrent Optimization)」もサポートされており、同機能をSMICの40nmプロセスで用いると既存のソリューションと比較して消費電力を14%、面積を11%、パフォーマンスを4%改善できるという。

この「CCOpt」は、Cadenceが2011年7月にAzuro社を買収して獲得した技術で、「Encounter Digital Implementation System」の中心的な技術の一つとなっている。(※関連ニュース)

2013.09.05

2013年9月3日、SynopsysはSamsung Electronicsによる論理合成ツール「Design Compiler Graphical」を大規模採用を発表した。

発表によるとSamsungは、同社のモバイルSoCの消費電力と面積の削減に向けてSysnopsysの論理合成ツール「Design Compiler Graphical」を採用。社内にて広範囲に同ツールを配備した。「Design Compiler Graphical」は、Synopsysの配置配線ツール「IC Compiler」との高い相関性により論理合成の段階で配線混雑度などフィジカル・インプリメントを考慮する事が可能。レイアウト設計とのイタレーションを大幅に減らし、消費電力と面積だけでなく設計期間も削減できる。

2013.09.04

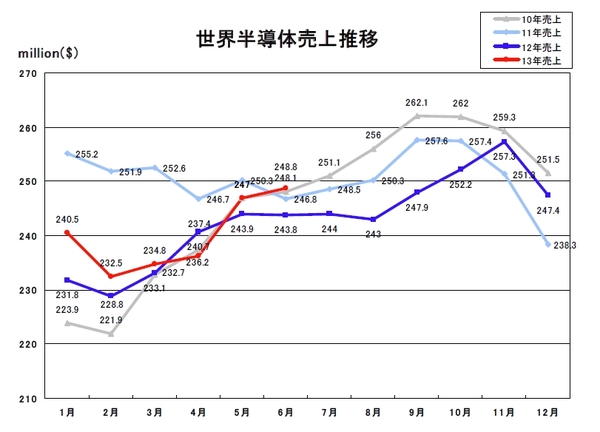

2013年9月3日、米SIA(Semiconductor Industry Association)は、2013年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年7月の世界半導体売上は前年同月比5.1%増、前月比2.6%増の255.3億ドルで6月に記録した今年の最高売上額を更新。7月の売上としては過去最高を記録した。これで売上前年比増は3ヶ月連続で、2-4月の売上平均額に対して5-7月の売上平均額は8.1%増となっている。

2013年7月の売上を地域別でみると、北米市場が前年比21.5%増と大きな伸びを示し、最大市場のアジア・パシフィックも7.2%伸ばした。日本市場は6月よりも売上を7.7%伸ばしたが、前年比では18.6%減。日本市場の売上前年比2ケタ減は9ヶ月連続となっている。

2013.09.03

2013年8月13日、クラウドベースのEDAソリューションを手掛ける日本のEDAベンチャーQuadcept株式会社は、同社の旗艦製品「Quadcept」の新サービスを発表した。

「Quadcept」は、回路図設計、PCB設計、3Dエレメカ協調設計に対応するクラウド・ベースのEDAソリューションで、クラウド上に用意される共通のデータベース、ライブラリ、モデルを利用して設計作業を行うことで設計の効率化が可能。更に設計データの管理システムも用意されており、設計のみならず設計データの管理や部品管理などもクラウド・ベースで実現できる。

今回発表された新たなサービスプランでは、ツールの運用プランの選択肢が拡張され、同社の提供するクラウドインフラに限らず、企業独自のプライベートクラウド(オフライン環境)でも「Quadcept」の利用が可能となった。

同社のソリューションは価格設定が低く、導入コストの安さもウリの一つで、既に5,000ダウンロードを達成しているという。

2013.09.03

2013年8月27日、GPUコア「PowerVRシリーズ」を手掛ける英Imagination Technologiesは、Mentor Graphicsとのパートナーシップの拡大を発表した。

発表によるとImagination TechnologiesとMentor Graphicsの両社は、Imagination Technologiesが2012年に買収したMIPS CPUコアの開発環境の提供に絡んで協業体制を拡大。具体的には、Mentorの提供するCNUツール・チェーンをベースとしたオープンソースの組込みソフト開発環境「Sourcery CodeBench」が、MIPSの次世代CPUコア「Warrior」を含む 全てのMIPS CPUコア・ファミリーの主要なCPUをサポート、両社の協業によりMIPSコア向けに「Sourcery CodeBench」が最適化された。これにより、Imagination Technologiesの顧客は、「Sourcery CodeBench」を用いてMIPSコアに最適な組込みソフトウェアのプログラミングが可能となる。

2013.09.02

2013年8月26日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、中国にて同社の論理シミュレータ「Active-HDL」が「2013 Excellence Award FPGA tools」を受賞したことを発表した。

今回Aldecが受賞した「2013 Excellence Award FPGA tools」は、中国の業界誌「Chinese Electronics News」が主催する「FPGA Industry Development Forum」で発表されたアワードで、Aldecの受賞はこれで4年連続。FPGA設計向けのシミュレータとして、Aldecの「Active-HDL」は名の通った製品として中国で受け入れられているようだ。

ちなみに中国を中心とするアジア・パシフィック地域のEDAの売上は、世界EDA売上の約25%を占めており(EDAC発表の2013Q1実績)、北米に次ぐEDAの主力市場となっている。

2013.08.29

2013年8月29日、Cadenceはルネサスエレクトロニクスが同社のTensilica DSPコアを採用したことを発表した。

発表によるとルネサスエレクトロニクスは、IoT(Internet of Things)アプリケーシン向けの次世代チップの開発にCadenceのDSPコア「ConnX D2 DSP」を採用。同DSPコアには、「アクセラレーション・パッケージ」と呼ぶカスタム・オプションが用意されているようで、それを用いることで標準性能の10倍以上の性能と低電力化が実現できるという。

ルネサスエレクトロニクスはこれまでにもTensilicaの各種DSPコアをモバイル・ワイヤレス通信、車載、デジタル放送レシーバ等で採用しており、今回の採用は複数のモデム規格に対応する通信LSI向けのようだ。

2013.08.28

――PR――

┌─────────────────────────────────┐

■■ Verification Tool のリーティング・ベンダと設計現場のエンジニア

■■ が最先端の検証技術をお届けする検証技術セミナーの決定版!

■■

■■ 2013年9月27日(金)「 Verify2013 」新横浜で開催!!!

■■

■■【Verify2013の見所】

■■ ・トライジェンス・セミコンダクターCTO岡村氏による基調講演

■■ ・検証関連のユーザー事例3件を含む計12セッション

■■ ・検証関連の国内企業12社が参加。各社のソリューションを終日展示

■■

■■ 事前登録制、参加無料!(昼食をご用意)

■■ 定員200名、席に限りがございますので、お早めにご登録下さい!

■■ https://www.eda-express.com/verify2013/index.html

└─────────────────────────────────┘

Verify セミナーは、検証ツールを専門的に扱うEDAベンダ各社ならびに設計現場の

エンジニアが集まり、 最新の検証技術とメソドロジ、検証ツールを使用した事例を

紹介する技術セミナーで、 今年で14回目の開催となります。

今年のVerify2013は、昨年を上回る主催8社、協賛4社の計12社にて、設計検証の実務

に役立つ講演と製品/サービスの展示を行います。

また、オーディオ向けのデジタル信号処理ICを手掛けるファブレス・ベンチャー

Trigence SemiconductorのCTO岡村淳一氏による基調講演の他に、株式会社リコー、

ルネサスエレクトロニクス株式会社の各社より計3件の事例講演を予定しています。

-------------------------------------------------------------------------------

■Verify2013 セミナー開催概要

会場:新横浜国際ホテル南館

日時:2013年9月27日(金曜日)

受付開始 9:30? セミナー 10:30?17:30 懇親パーティー 17:50?19:30

参加: 無料(事前登録制)※セミナーでは昼食をご用意させて頂きます。

WEB:https://www.eda-express.com/verify2013/index.html

主催:アルデック・ジャパン株式会社

カーボン・デザイン・システムズ・ジャパン株式会社

日本ワンスピン・ソリューションズ株式会社

株式会社シンコム

株式会社日本サーキット

日本リアルインテント株式会社

ミラビリス・デザイン社

マジレム・デザイン・サービス社

協賛:株式会社エッチ・ディー・ラボ

株式会社ベリフォア

MathWorks Japan

東京ナノファーム合同会社

事務局:株式会社EDAエクスプレス

■Verify2013 セミナー内容はこちら

→ https://www.eda-express.com/verify2013/seminar.html

■Verify2013 出展社の展示案内はこちら

→ https://www.eda-express.com/verify2013

■Verify2012 参加お申し込みはこちら

https://www.eda-express.com/verify2013/entry-form.html

------------------------------------------------------------------------------

■■お問い合わせ

Verify2013に関するお問い合わせは、下記窓口までお願い致します。

Verify2013運営事務局 ?EDAエクスプレス info@eda-express.com

------------------------------------------------------------------------------

2013.08.23

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

2013.08.23

2013年8月22日、Mentor Graphicsは、2014会計年度第2四半期(2013年5月-7月)の売上を報告した。

発表によると、Mentorの2014会計年度Q2の売上は、前年比約5.1%増の2億5320万ドル、営業利益は前年比33.5%増の2657万ドルで、この売上額は前Q1売上報告時点の予測を上回り、同社のQ2売上記録として過去最高の結果だった。(※GAAP基準による会計結果)

Mentorは前四半期(2月-4月)の売上が約3年ぶりに前年割れに終わっていたが、今期は再び前年を上回る売上を達成。主力となる先端プロセス向けの物理検証ツール「Calibre」ファミリ製品やエミュレータ「Veloce」を中心とした検証ツールが好調のようだ。

Mentorは次期2014会計年度Q3(13年8-10月)の売上を前年実績を上回る2億6000万ドルと予測している。

2013.08.22

2013年8月21日、Synopsysは、2013会計年度第3四半期(13年5-7月)の売上を報告した。

発表によると、Synopsysの2013会計年度Q3の売上は、前年同時期比約8.8%増、前期13年Q1比約3.3%減の4億8290万ドル。純利益は前年同時期の約31%減の5230万ドルだった。(※GAAP基準による会計結果)

Synopsysの四半期売上が前四半期実績を下回るのは11年Q4以来。今四半期で12年Q1から更新し続けていた四半期売上記録の更新は一旦ストップしたが、売上の前年実績超えは12四半期連続で継続中。

Synopsysは、次期2013会計年度Q4(13年8-10月)の売上を5億-5億1000万ドルと予測。2013会計年度の売上予測については19億5700-6700万ドルと予測の幅を狭めた。

2013.08.21

2013年8月7日、Cadenceは、最新のメモリ規格向けの検証IPのリリースを発表した

発表によると今回Caenceがリリースを発表したのは、LPDDR4、WideI/O 2、eMMC 5.0、HMC、DDR4 LRDIMM、以上5種類のメモリ標準規格向けの検証IPで、いずれも業界に先駆けての提供開始となる。

メモリ・インタフェースの検証IPのラインナップに関して、Cadenceは業界随一。IPポートフォリオを拡張し続ける中で、同分野への取り組みを更に強めているように見える。

※Cadence VIP

2013.08.21

2013年8月16日、Cadenceは、Freescale Semiconductorが同社のツール環境で最先端の通信SoCをテープアウトした事を発表した。

発表によるとFreescaleは、Power Architecture 64-bitプロセッサコアを12個搭載した1.8GHz動作のネットワーク・アプリケーション向けSoC「QorIQ T4240」をCadenceのツール環境でテープアウト。具体的には、Cadenceの「Encounter Digital Implementation System」を利用してデザインのインプリメントを実施。最新の「Encounter Digital Implementation System」に搭載されるマルチスレッドの物理最適化技術「GigaOpt」によって、設計期間を大幅に短縮できたとしている。

2013.08.08

2013年6月28日、フォーマル検証ソリューションを手掛ける米Jasper Design Automationは、新横浜のホテルで「Real-World Applicationセミナー」と題したプライベート・セミナーを開催した。

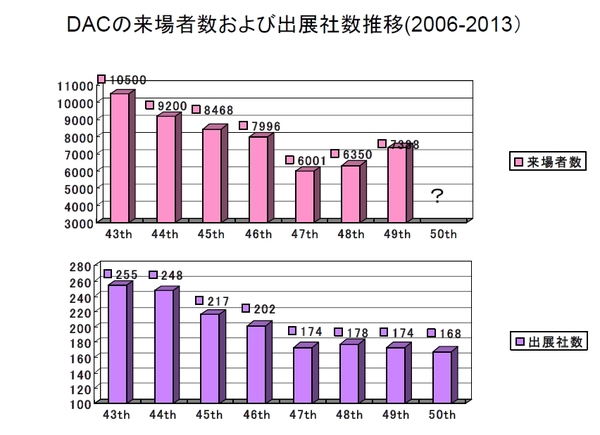

ここでは6月の第50回DACで聞いた話も踏まえ、同社の最新のソリューションについてレポートする。

ツールの話の前にまず同社の業績について紹介しておこう。

日本でのセミナーでも紹介されていたが、同社の売上は3年前の2010年頃から急伸しており、2007年以降の平均成長率は35%とEDA業界全体の成長を凌ぐ勢い。3年前に打ち出した個別の検証要求にフォーカスした自動化アプリ「Jasper Apps」の戦略があたり、大きく成長したとの事で、現在は半導体上位15社のうち10社が顧客。日本国内でも複数の大手メーカーが長らく同社のフォーマル検証ツールを利用している。同社の成長ぶりは本拠地米国で高く評価されており、今年5月には有望なハイテク・ベンチャーを称える「2013 Red Herring Top 100 North America」のファイナリストに選出された。(関連ニュース)

そんな成長著しいJasperが今年のイチ押し製品として5月にリリースしたのが、「Jasper Apps」の一つとなる新製品「Low Power Apps」。同ツールは複数のパワードメインを持つSOCの設計をターゲットにしたフォーマル検証ツールで、ローパワー設計が意図通り実現されているか、また設計におけるパワー最適化化手法が回路本来の機能を損ねていないかなどをRTLの段階で網羅検証することができる。

具体的には、RTLおよびパワー仕様記述言語UPFまたはCPFで記述されたパワー仕様を読み込み、パワー分割仕様に従いパワーを取り扱えるフォーマル・モデルをツール内部で生成。同時にパワー最適化の構造チェックを行う検査項目とパワー制御を検証するためのアサーションを生成し、それを基にフォーマル検証を実行する。

「Low Power Apps」は、Power-Awareの状態でパワー・シーケンスの検証やパワー・マネジメント回路の検証などフォーマル検証技術による機能検証が可能なため、パワー・マネジメントの導入がファンクションに与える影響を確認することが可能。このようなローパワー設計ソリューションはこれまで無かったとJasperのマーケティングおよび事業開発VPのOz Levia氏は言う。

※画像は全てJasper提供のデータ

確かに既存のソリューションとしては、RTLとパワー仕様の整合性をチェックするツールやパワー最適化の電力面の影響を見積るツールは存在しているが、UPFおよびCPFの機能を考慮して機能検証するソリューションは、テストケースを用いたダイナミック・シミュレーション以外無かった。網羅検証を行うフォーマル検証は、デザインの品質向上という面でシミュレーションより分があると言える。

尚、Jasperの新製品「Low Power Apps」は、既にSTMicroelectronicsとBroadcomが先行して実際のプロジェクトに使用しているという話で、この両社は第50回DACにてJasperブースで事例を紹介していた。

※株式会社シンコム(Jasper Design Automation社製品国内代理店)

2013.08.07

2013年8月6日、米EDA Consortiumは、2013年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

EDACの発表によると、2013年Q1(1月-3月)の世界のEDA売上総額は、前年比8.1%増の16億6850万ドルだった。EDAの売上は年間を通じてQ4が最も高いため、前四半期の売上を超えることは無かったが、四半期ごとの世界EDA売上総額は13四半期連続で売上前年比増を達成した。ここ数年に渡る右肩上がりの売上増は、ツールの売上増もさることながら、買収戦略などにより各社IPの売上が大きく伸びた結果で、現在のEDAの市場ではIPが一つの成長エンジンになっている。

2013年Q1の売上を分野別に見ると、IC Physical Design & Verification分野だけが売上前年割れで、これで3四半期連続となる。その他の分野は全て売上前年比増を達成し、中でもIP分野が20.2%増と大きく伸びた。ちなみにこの売上統計には、Cadenceが買収したTensilica製品の売上は時期的にまだ反映されていない。

2013年Q1の売上を地域別に見ると、日本を除く全ての地域で売上前年比増を達成。最も伸びたのはアジアその他地域で前年比20.5%と大幅増、日本の売上額の減少は2013年Q1から大きく変動した為替レートの影響も大きい。

2013年Q1時点でのEDA業界の従業員数は29360人で、前年比5.41%増、前期Q4比0.7%減となっている。

2013年Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 5億9910万ドル 4.7%Up

■IC Physical Design & Verification分野 3億4010万ドル 3.1%Down

■IP分野 4億7030万ドル 20.2%Up

■サービス分野 1億190万ドル 23.8%Up

■PCB/MCM分野 1億5720万ドル 6.7%Up

2013年Q1地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億6100万ドル 6.2%Up

■ヨーロッパ 2億7620万ドル 4.8%Up

■日本 2億5980万ドル 0.6%Down

■アジアその他地域 4億2200万ドル 20.5%Up

2013.08.06

2013年8月5日、米SIA(Semiconductor Industry Association)は、2013年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年6月の世界半導体売上は前年同月比2.1%増、前月比0.8%増の248.8億ドルで、5月に続いて市場の復調を示した。この6月の売上額は過去三年間で最高の数字で、直近最も年間売上が高かった2010年の実績を上回るものとなっている。四半期実績でみると、2013年Q2(4-6月)の売上は前年比6%増の746.5億ドルとなっている。

2013年6月の売上を地域別でみると、最大市場のアジア市場、それに次ぐ北米市場が伸びを示し、伸び率では北米市場が前年比10.6%増と目立った。逆の意味で目立ったのは日本市場の縮小で、前年比20.8%減と5月の18.4%減に続いて大きく売上を落とした。日本市場はこれで8ヶ月連続で売上前年比2ケタ減となっている。

2013.08.01

2013年7月31日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、NECの手掛ける高位合成ツール「CyberWorkBench」の販売代理店権を獲得した事を発表した。

Aldecによる「CyberWorkBench」の販売について、その対象地域などの詳細は明らかにされていないが、NECは2011年よりEDATechForce社と契約していた北米市場における販売代理店契約をAldecに切り替えた様子。日本国内での製品販売は、これまで通り図研エルミックが代理店として継続すると思われる。

NECは、先ごろ6月にオースティンで開催された第50回DACにて、Aldecブース内で製品を展示しており、既に提携関係にあった。コストパフォーマンスの高いシミュレータを中心に多数の顧客を抱えるAldecが代理店になることにより、国産高位合成ツール「CyberWorkBench」のユーザーは確実に増えていくことになるだろう。

2013.07.31

2013年7月29日、STMicroelectronics, ARM, Cadenceの3社がバーチャル・プロトタイプにおけるモデルとツールの相互運用性を高める3種類の標準インタフェースを開発したことを発表した。

発表によると3社は、システム記述言語SystemCのTLMをベースとした以下の3種類の標準インタフェースを共同開発し、これをハード設計/EDA関連規格の標準化組織米Accellera Systems InitiativeのSystemC Language Working Groupに提供。同インタフェースは Apache 2.0 open-source licenseの下でAccelleraのWebサイトでダウンロード可能となっている。

・割り込みモデリング用インタフェース

異なる企業が作成したモデルをシームレスにインテグレーション

・レジスタ監視用API

ツール環境を問わずレジスタ値の更新および表示が可能

・メモリマップ モデリング用インタフェース

バーチャル・プラットフォームでのデバッグ効率を改善

Accelleraはインタフェースを開発したSTMicroelectronics, ARM, Cadenceの3社と共に、これらインタフェースの完全な標準化に向けて活動を進める計画だという。

2013.07.31

各組織が公に発表している2013年7月時点での2013年世界半導体市場成長予測。

昨日、調査会社IDC最新の予測を発表しました。同予測値は前回予測値の情報修正で、直近発表された各組織の予測値の中で最も高いものとなっています。

ちなみにIDCは2014年の世界半導体市場を2.9%の成長と予測。2012年から2017年までの市場の平均成長率を4.2%と予測しています。

2013.07.25

2013年7月24日、ARMは、2013会計年度第2四半期(2013年4-6月)の売上を報告した。

ARMの2013年Q2の売上は、前年比24%増、前期比0.15%増の2億6430万ドルで過去最高、営業利益は前年比約30%増の約1億3370万ドルだった。売上の内訳を見るとライセンスの売上が前年比約30%増の1億260万ドル、ロイヤリティの売上が前年比約23%増の1億3530万ドルだった。ARMは2010年Q1より四半期売上の前年増を継続しており、今期で14四半期連続で売上前年増となった。

ARMはこのQ2で前Q1を上回る計25件のプロセッサ・ライセンスを獲得。その内訳はCortexシリーズのプロセッサ・ライセンスが計17件で、この中には新型のプロセッサCortex-A12のライセンスが2件含まれている。GPU Maliのライセンスは前Q1の倍以上の7件だった。また、プロセッサの最適化のフィジカルIPパッケージ「POP IP」のライセンスは5件だった。

※画像はARM発表資料より抜粋

2013年Q2で出荷されたARM搭載チップの総数は前年比20%増の約24億個で、その半数以上はモバイルデバイス向け、組込み向けは28%、エンタープライズ向けは18%だった。出荷されたプロセッサの個数を種類別で見ると、遂にCortexシリーズの出荷数が全体の50%に到達した。(前期Q1は45%)

※画像はARM発表資料より抜粋

2013.07.25

2013年7月24日、Cadenceは、2013会計年度第2四半期(2013年4-6月)の売上を報告した.

Cadenceの2013年Q2売上は、前年同時期比約11%増、前期Q1(13年1-3月)と比較して約2.2%増の3億6200万ドル。純利益は前年3600万ドルに対し今期は900万ドルだった。(※GAAP基準による会計結果)

CadenceQ2売上実績は前Q1売上報告時の予測通りのもので、同社の売上はこれで14四半期連続で前年比増を記録。ここ3年、世界の半導体市場の成長が鈍化している中で右肩上がりの成長を遂げている。

Cadenceは次期2013年Q3の売上を今期実績を更に上回る3億6000-7000万ドルと予測。2013年の年間売上予測を14億4500万-14億6500万ドルと上方修正している。

2013.07.25

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2013.07.25

2013年7月23日、Alteraは2013会計年度第2四半期(13年4-6月)の売上を報告した。

発表によるとAlteraの2013年Q2(13年4-6月)売上は、前年比約9%減、前期Q1比約3%増の4億2190万ドル、営業利益は前年比約30%減、前期Q1比約4.7%減の1億1238万ドルだった。Alteraは前期Q1で7四半期ぶりに前年実績を上回る売上を記録していたが、今期は再び前年割れとなった。

AlteraのQ2売上を地域別で見ると、前Q1で大きな伸びを示した北米およびアジア市場が一転前年割れとなり、大きなマイナス要因に。欧州、日本は前年比増を記録した。Q2売上を分野別で見ると、産業向けおよびミリタリー、クルマ分野のみ前年微増を記録、その他の分野は主力のテレコム/ワイヤレス分野とネットワーキング/ストレージ分野を含め全て前年割れとなった。

製品別では、Stratix V、Arria V、Cyclone Vといった最新の28nm製品を含む新製品カテゴリの売上のみ前年比20%増を記録したが、その他の製品売上は全て前年実績を下回った。

Alteraは次期2013年Q3(7-9月)の売上を2013年Q2の5-9%増と予測している。

2013.07.19

各組織が公に発表している2013年7月時点での2013年世界半導体市場成長予測。

先頃、TSMCのMorris Chang会長が最新の予測を発表しました。4月以降に発表された各組織の予測はいずれも前回予測の下方修正となっています。

2013.07.18

2013年7月18日、Xilinxは2014会計年度第1四半期(2013年4-6月)の売上を報告した。

Xilinxの2014会計年度Q1(13年4-6月)の売上は、前年同時期比1%減、前期Q4比9%増の5億7900万ドル。営業利益は前年比17%増、前期Q4比31%増の1億9290万ドルで、前期Q4に更新した粗利益率の記録を今期も更新し過去最高の69%に達した。(※GAAP基準による会計結果)

Xilinxは前期までアジア地域以外の不調により、7四半期連続で売上前年割れとなっていたが、今期はようやく昨年並みの売上高に回復し財務状況も改善させた。

Q1売上を地域別でみると、前期に対しては全ての地域で売上増を記録。前年比ではアジアに加え北米もプラスに転じた。分野別の売上では、メインのコミュニケーションおよびデータ・センター分野をはじめ全ての分野で前期に対して売上増を記録した。

製品別売上では、発売以来伸び続けている新製品カテゴリ(Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6)の売上が続伸中で、同カテゴリの売上は前期Q4よりも24%増加し、売上全体に占める割合を遂に3割の大台に乗せた。Xilinxはこの新製品の売上の勢いを維持しつつ、新たに発表したUltraScale アーキテクチャの20nm FPGA(2013年Q4)、16nm FPGA(2014年)を市場へと投入していく計画だ。

Xilinxは次期2014年Q2(13年7-9月)の売上を今期同等もしくは3%増程度と予測している。

2013.07.18

2013年7月10日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の論理シミュレータ「Riviera-PRO」のバージョンアップを発表した。

発表によると、「Riviera-PRO」の最新バージョン2013.06の目玉は、UVMベース検証環境を利用するユーザー向けに搭載された「クラス階層可視化機能」で、新たに用意された「クラス・ウィンドウ」を用いることで、SystemVerilogクラスを階層ツリーの形式で表示し、クラスの継承、メソッド、プロパティなどUVM検証環境の動作に関する情報を確認できるようになった。また同機能は、サードパーティのIDEと連携したクロス・プロービングやナビゲーションにも対応するという。

また、その他にも今回のバージョンアップに伴い各種機能強化が図られており、シミュレーション実行時間が従来比2-3倍(コードカバレッジを有効にした状態で)と高速化されたほか、高性能のSystemVerilogランダム制約ソルバと新型のUVM対応デバッギングツールにより、シミュレーション容量もアップしたとの事。

2013.07.17

2013年7月11日、Cadenceは、同社の配置配線ツールとDFM検証ツールを用いてTSMCの設計子会社Global Unichipが20nm SoCのテストチップをテープアウトした事を発表した。

Global Unichipが20nm SoCの設計に使用したのは、Cadenceの配置配線ツール「Encounter Digital Implementation System」とDFM検証ツール「Cadence Litho Physical Analyzer」で、Cadenceはダブルパターニングを含む複雑な20nm配置配線フローの全てのステップをサポート。Global Unichipの担当者は、「Cadence Litho Physical Analyzer」により設計期間を短縮できたとコメントしている。

2013.07.17

2013年7月9日、Cadenceは、アナログ/カスタム設計におけるTSMCとの協業拡張を発表した。

発表によると、今回の両社の協業拡張はCadenceのVirtuosoカスタム/アナログ設計プラットフォームに関するもので、TSMCは「Virtuoso」ファミリ製品の「Schematic Editor」、「Analog Design Environment」、「Virtuoso Layout Suite XL」など主要ツールを採用すると同時に、Virtuosoの専用言語であるSKILLベースのPDK(process design kit)を16nmまでに拡張した。

TSMCは、Cadence以外の複数のEDAベンダと開発した、特定のEDAベンダのツール環境に依存しないOpenAccesベースの「iPDK」を提供しているが、やはり先端プロセスにおけるCadenceの技術とCadenceツールを利用する顧客のニーズは自社のビジネス戦略上重要という事でSKILLベースのPDKを16nmまでに拡張した格好だろう。

ちなみにカスタム/アナログ設計におけるCadenceの牙城を切り崩そうと一致団結して「iPDK」の普及に力を注いだEDAのベンダの多く(Ciranova,SpringSoft,Magmaなど)は、その後次々とSynopsysに買収されており、現在同分野は完全にCadenceにSynopsysが対抗する構図となっている。

2013.07.08

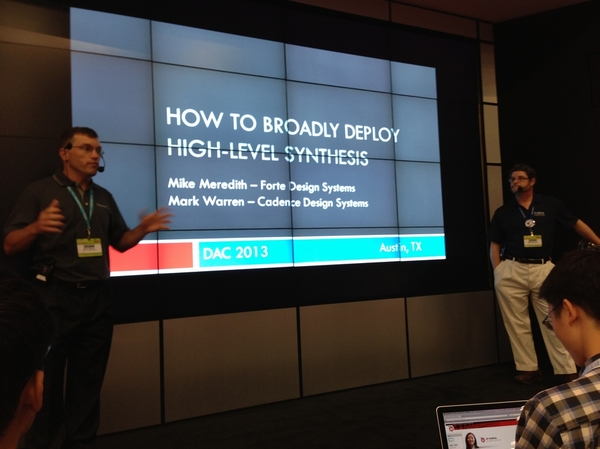

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

Cadenceはここ数年、DACの展示会会期を通じて連日自社のステージでユーザー企業やパートナー企業による、ツールの活用事例や利用法のショート・プレゼンテーションを実施している。

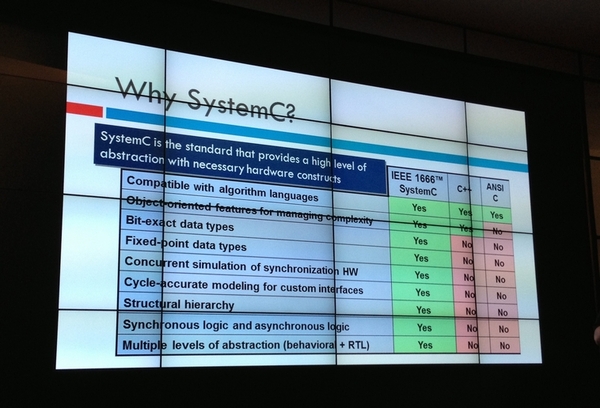

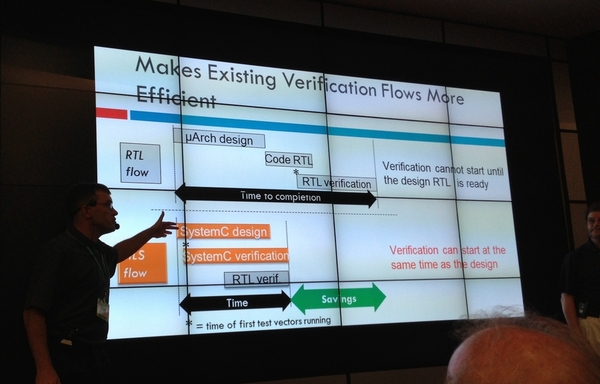

今年は異例となる高位合成ツールの競合企業Forte Design Automationとのコラボレーション・プレゼンを行なっていた。タイトルは、「How to broadly deploy High Level Synthesis」。登壇したのは、CadenceのSystem Level Design groupのディレクターMark Warren氏とForteのテクニカル・マーケティングVPのMike Meredith氏の両名。

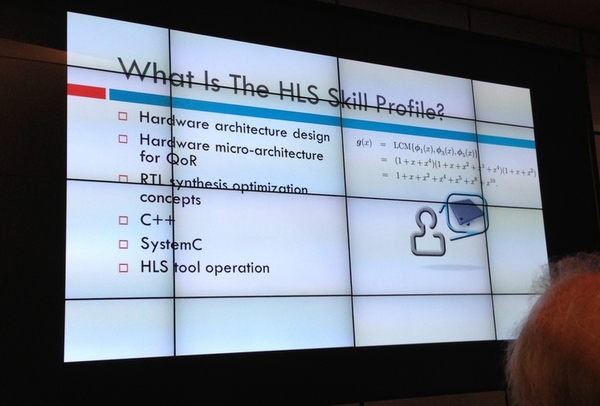

高位合成ツールの販売では競合関係にある両社だが、ツールの入力言語がSystemCという共通点があり、話は「なぜSystemCなのか?」というところから入っていった。CadenceのMark Warren氏は、C/C++に対するSystemCの優位点を幾つか並べ、ビット精度が指定できない言語はハードウェア設計に向かないとした。

また、Mark Warren氏は、高位合成ツールを用いたハードウェア設計に必要なスキルについても幾つか挙げ、中でも重要なのはRTL設計のスキルとC++言語のスキルであるとし、SystemCベースの高位合成ツールを用いた設計フローのメリットとしては、設計と検証を同時にスタートできる事を挙げ、SystemCを用いる事でアーキテクチャ設計とRTL設計の2ステップを要する既存のフローを一本化できると説明した。ForteのMike Meredith氏は、これらいずれの点についても同意した。

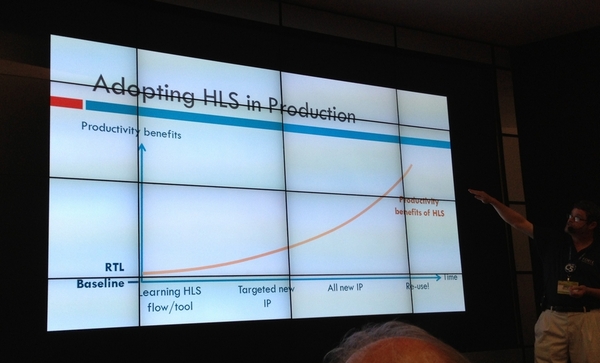

高位合成ツールを用いる事で設計生産性をどの程度向上できるかについては、ForteのMike Meredith氏が説明し、高位合成の導入→部分的なIP設計→新規IP設計→再利用設計と時間を費やしその利用範囲を拡大する事で設計生産性は大きく向上すると語った。

最後にCadenceのMark Warren氏が、高位合成の導入効果は明確でおり、あとはより良いツールを如何に使いこなすかが重要として締めくくった。

同プレゼンテーションは好評で、多数の展示会来場者が訪れ立ち見客も多かったが、第50回DACを通じて、高位合成の利用事例はテクニカルセッションやユーザートラックなど、いたるところで語られており、日本市場がその立ち上げに一役買った高位合成ツールが、世界で浸透している現状を再認識させられた。

2013.07.08

2013年6月21日に開催されたセミナー「SystemC Japan 2013」の講演資料がSystemC Japan オフィシャル・サイト上で公開されました。

サイトに登録すると無料で資料をダウンロード出来ます。

2013.07.02

各組織が公に発表している2013年6月時点での2013年世界半導体市場成長予測。

先月WSTS(World Semiconductor Trade Statistics)が最新の予測を発表しました。現時点ではいずれの予測もプラス成長を見込んでおり、直近の予測値は2-4%増に集中しています。

2013.07.02

2013年7月1日、米SIA(Semiconductor Industry Association)は、2013年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年5月の世界半導体売上は前年同月比1.3%増、前月比4.6%増の247億ドルで、4月の半年ぶりの前年割れを跳ね返し市場の回復基調を示した。2012年実績と比較すると、2013年5月時点での売上累計は前年比1.5%増となっている。

2013年5月の売上を地域別でみると、最大市場のアジア市場が前年比5.8%増と好調な伸びを示し、市場シェア2位の北米市場も前年比3.0%増とこれに続いた。欧州市場はほぼ前年同等の実績で、日本市場のみ前年比18.4%減と大きく売上を落とした。日本市場はこれで7ヶ月連続で売上前年比2ケタ減という悲惨な状況。世界の半導体市場の中で完全に孤立した形で衰退している。

2013.06.27

2013年6月21日、今年で8回目の開催となるセミナー「SystemC Japan 2013」が開催された。

同セミナーは、設計言語IEEE 1666 SystemCにフォーカスした技術セミナーで、主催はSystemCの仕様策定および普及活動を推進する業界団体米Accellera Systems Initiative。SystemC関連のセミナーとしては世界最大の開催規模を誇っている。

ここでは、SystemC Japan 2013で発表されたルネサス エレクトロニクスのユーザー事例の内容を紹介する。

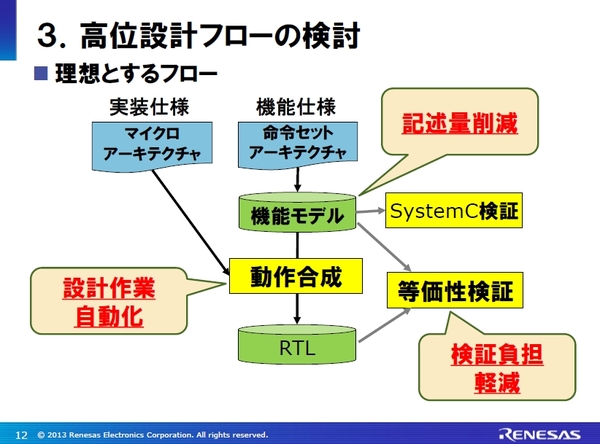

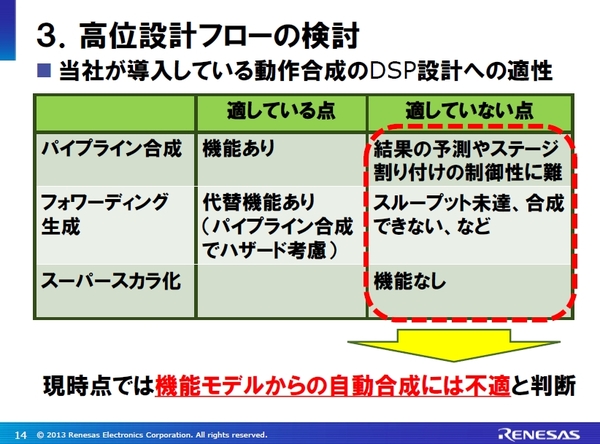

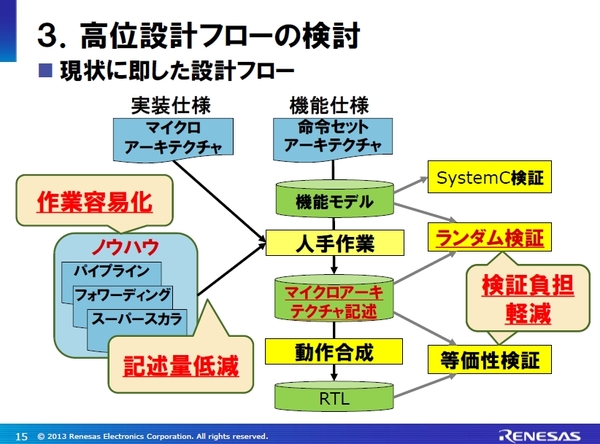

■ルネサス エレクトロニクス「高位設計技術によるDSP設計効率化の取り組み」

ルネサス エレクトロニクスの講演は、第一事業本部 システムインテグレーション事業統括部 FE設計技術開発部 主任技師の大坪 基秀氏。今回大坪氏が紹介してくれたのは、DSP設計における高位合成ツールの適用例で、使用したツールはCadenceの「C to Silicon Compiler」。ルネサスでは既にデータパス系の回路の設計で高位合成の利用が定着しており、制御系の回路に関しても適用フェーズに入っている状況で、データパスと制御が混在するDSP設計への高位合成の適用は新たなチャレンジだった。

大坪氏が示したDSP設計のポイントは3つ。

1.スループット向上のためのパイプライン処理

2.パイプライン処理によるデータハザード解消のためのフォワーディング処理

3.リアルタイム性向上のためのスーパースカラ化

これらを設計で実現しようとすると、デザインが複雑となり記述量も増大、検証も難しくなるため、一連の問題を高位合成と等価性検証を用いて解決しようと設計フローを検討したが、現時点では機能仕様(からおこしたSystemCの機能モデル)からの自動合成は無理と判断。DSPのマイクロ・アーキテクチャを人手で作りこんだSystemC記述から合成することにした。

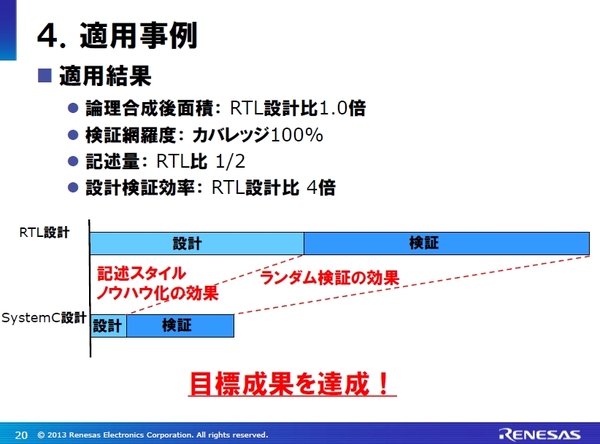

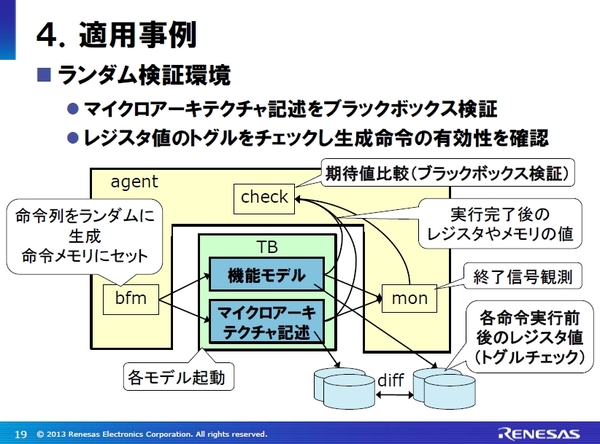

実際に高位合成を適用したのは、2Wayスーパースカラ構成、3ステージパイプラインのプロセッサ部で、合成用のマイクロ・アーキテクチャ記述のコーディングは、記述パターンをノウハウ化して作業を効率化。その検証にはCadenceのランダム検証「Specman」を適用し、合成結果との等価性検証にはCalypto社の「SLEC」を使用した。

その結果、回路面積、検証網羅度、コード記述量、設計検証効率の全てにおいて当初目標を達成(下図参照)。設計検証効率の大幅な向上には、SystemCコーディング・スタイルのノウハウ化とランダム検証が大きく貢献した。(ちなみに、コーディング・スタイルのノウハウ化には2週間程度の工数を費やしたとの事。)

ランダム検証では、元の機能モデルと人手でリファインメントしたマイクロ・アーキテクチャ記述のそれぞれのランダム検証結果を比較し動作を確認。特にフォワーディングの箇所についてはカバレッジを取り100%のカバレッジを確認した。また、レジスタの更新状況を確実に確認するために、各命令前後のレジスタ値の履歴を取りトグルチェックを行った。

※スライド資料は全てルネサス提供のデータ

大坪氏は、今後の課題として、理想的なフローと考える機能モデルからの合成の実現を挙げ、これにはEDAベンダのツール強化に期待するとした。講演の最後には、高位合成の適用拡大に向けては社内へのプロモーションやエバンジェリストの育成も重要とコメントし、将来的には高位合成によるインターコネクト生成にも取り組みたいと抱負を語った。

2013.06.26

2013年6月21日、今年で8回目の開催となるセミナー「SystemC Japan 2013」が開催された。

同セミナーは、設計言語IEEE 1666 SystemCにフォーカスした技術セミナーで、主催はSystemCの仕様策定および普及活動を推進する業界団体米Accellera Systems Initiative。SystemC関連のセミナーとしては世界最大の開催規模を誇っている。

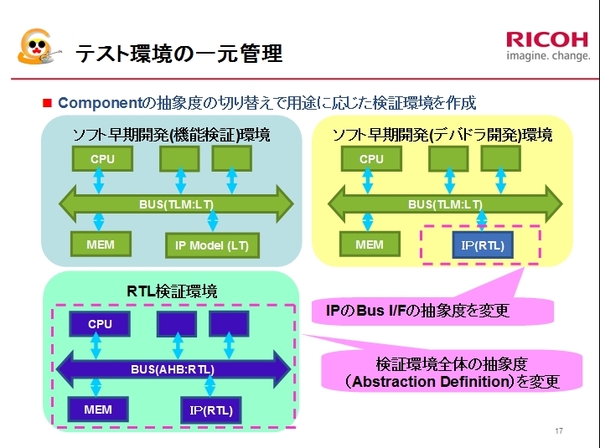

ここでは、SystemC Japan 2013で発表されたリコーによるユーザー事例の内容を紹介する。

■リコー「IP-XACTで"つなぐ"仕様の一元管理」

リコーによるSystemC Japanでの発表は今年で5年連続。今年はワーク・ソリューション開発本部 第六開発室 開発一グループの小澤 賢一氏が、IEEE 1685 IP-XACT標準を利用して設計仕様の一元管理を行った事例を発表した。IP-XACTは、SystemCと同じくAccellera Systems Initiativeが仕様策定および普及活動を推進している。

リコーではSystemCをベースとした設計プラットフォームを共有することで、上流設計におけるアーキテクチャ探索、ソフトウェア開発、RTL検証の連携と効率化を図っているが、TAT短縮を図るために、最終FIXする前の仕様書を元に個々のモジュール設計(RTL設計)やSW開発環境の作成などを並列して進めているため、仕様変更へすぐに対応可能な仕様の一元管理手法を模索していた。そこでその手段として選んだのがIP-XACTの利用。具体的にはIP-XACTベースの設計ソリューションを提供する仏Magillem社のツールを導入することで、仕様の一元管理に取り組んだ。

今回小澤氏が発表したのは、ソフト早期開発、RTL検証、高位合成における仕様一元管理の例で、Magillem社のツール上でゴールデンな仕様をIP-XACT形式で管理。その仕様からMagillemツールのコンフィギュレーション機能を用いて各種テスト環境を自動生成した。

例えば、ソフトの機能検証環境としてSystemC TLM-LTベースの環境を、デバドラ開発用として一部のIP部の抽象度をRTLに切り替えた環境を同じ仕様から生成した。その元となるIP-XACTデータは、HDLで記述された既存のRTLやSystemCモデルなどをMagillemのツールに入力する事で自動生成したもので、小澤氏曰く、Magillemのツールは IP-XACTを知らなくても使えたとの事。

ちなみに、ソフト機能検証環境からデバドラ開発用検証環境への移行は僅か2時間程度で済んだとの事で、実際に仕様変更が発生したケースでIP-XACTベースの一元管理で対応したところ、従来手法と比較してIP検証の工数を半減。品質向上にも一定の成果をもたらすはず(仕様の一貫性からインタフェースやレジスタ周りの不整合が排除できる)という話だった。

※スライド資料は全てリコー提供のデータ

また、高位合成向けには、Magillemツールにレジスタ情報をインポートし、そこから高位合成可能なレジスタ・テンプレートを作成するという形でIP-XACTを活用したとの事。その他にも、ドキュメント管理や設計データのバージョン管理にもIP-XACTベースのMagillemツールを利用しているという事だった。

2013.06.19

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

カナダのモントリオール理工科大学発のベンチャーであるSpace Codesignは、ARMのブース内にパートナーとして展示していた。同社は社名の通り宇宙向けシステムの開発を一つのターゲットとしているが、2011年にARMのプロセッサ・モデルをサポートしてからは、コンシューマ・エレクトロニクス向けにもソリューションの展開に力を入れている。

同社のGeneral Manager Gary Dare氏に話を聞いたところ、現在同社のESLツール「SpaceStudio」では、ARM Cortex-A9 DualCore,Xilinx MicroBlaze,そして宇宙システム向けのプロセッサLeon3のプロセッサ・モデルをサポートしており、C/C++/SystemCをベースとした環境でシステムのアーキテクチャ探索ならびにパフォーマンス解析が可能。FPGAをターゲットに高位合成向けの実装用HWコードとプロセッサ向けのSWコードを出力する事も出来る。(※高位合成は市販ツールまたはFPGAベンダのツールを利用する想定。ASIC向けの実装コードも出力できるとしている。)

最新のバージョンでは、「アーキテクト・ダッシュボード」と呼ぶグラフィカルなアーキテクチャ探索機能が用意され、システムを構成する各種コンポーネントをドラッグ&ドロップで置き換え、様々なアーキテクチャのパフォーマンス、パワーを容易に解析する事が可能に。実際に試したMotion JPEGのビデオ・デコーダのアーキテクチャ探索の例では、設計者1名でアーキテクチャ全26パターンを僅か2.5日でチェックし終えたという。ブースではXilinxのFPGA SoC「Zynq」のバーチャル・プラットフォームを用いたデモを行なっていた。

※画像は全てSpace Codesign提供のデータ

ちなみに「SpaceStudio」のリストプライスは、年間ライセンスで6000ドル(モデル・ライブラリ込み)とかなり値頃感があり、ニーズにマッチすればかなりの低コストでARM Cortex-A9ベースのESL環境を手にできる。

2013.06.19

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

ESLツールを提供するCarbonはスイートでの展示のみ。たまたまARMブースを通りかかった際に人だかりが出来ていたので、どこのプレゼンかと覗いてみるとCarbonのプレゼンだった。

Carbonは、DAC50開催前にARM Cortex-A57,A53,ARMのシステムIP CoreLink CCN-504のESLモデルのサポートをアナウンスしており、DAC50後の6月12日には、高速モデルと高精度モデルを切り替えるバーチャル・プラットフォームのシミュレーション技術「Swap&Play」の拡張をアナウンスした。これまで制限のあった「Swap&Play」技術が、Arterisのインターコネクト・モデルやCadenceのメモリ・モデルなど各種ファブリック・モデルに対しても利用可能なったという。

2013.06.18

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

Intelのブースでは、買収により傘下に収めた仏CoFluent社のESLツール「CoFluent Studio」を展示していた。

話によると「CoFluent Studio」の最新バージョンでは高位合成ツールとの連携を強化。「CoFluent Studio」のグラフィカルなモデリング環境でSystemCのモデルを生成し、特定の高位合成ツール向けに特化した合成用コードが出力可能になったとの事。高位合成ツールに渡されるコードはタイミング情報の無いアンタイムドなコードでSystemCのTLM形式になるという。ブースではCadenceの「CtoS」との連携デモを披露していた。

また、同じくIntel傘下のWindriverが提供する仮想プロトタイピング・ツール「Simics」では、「CoFluent Studio」で作成した各種デバイスモデルを「Simics」にインポートできるようになったという話で、既にIntel社内ユーザーが活用していると聞いた。

Intelでは、

「CoFluent Studio」を積極的に外販するというよりも、社内のソフトウェア開発やSoC設計などに活かすべく、社内設計インフラとしての整備を進めているようだ。

2013.06.18

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

Calyptoのブースでは、日本から参加したルネサス・エレクトロニクスの今村 慎太郎氏(第一事業本部 システムインテグレーション事業統括部 FE設計技術開発部)がユーザーとして、Calyptoの等価性検証ツール「SLEC」の採用事例を発表していた。

今村氏によると、ルネサスが「SLEC」の使い所として考えたのは、高位合成前後の等価性検証で、出来ればRTL検証をしないで済む高位合成フローを構築したいと「SLEC」の利用を試みた。

高位合成前後の等価性検証、すなわち入力するCモデルと高位合成結果のRTLとの機能等価性の検証に「SLEC」を利用するのは比較的ポピュラーな手法で、「SLEC」はCalyptoの高位合成ツール「Catapult」に限らず、Forteの「Cynthesizer」やCadenceの「CtoS」とも連携するパスを持っており、高位合成ツールとセットで「SLEC」を利用しているユーザーは多い。

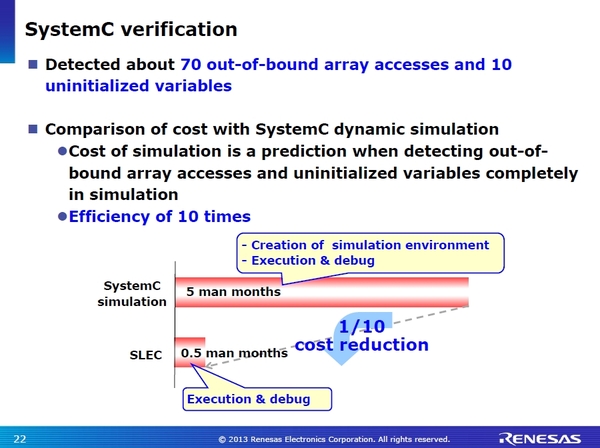

今回の今村氏の発表で面白かったのは、高位合成前のSystemCコードのプロパティ・チェックを「SLEC」で実施したという例で、ルネサスでは実際のビデオIPの開発において「SLEC」に予め用意されているアサーションを用いて、高位合成用のSystemCコード中の配列外アクセスと未初期化変数のチェックを実施した。その結果、約70の配列外アクセスと10の未初期化変数を検出。同プロパティ・チェックとデバッグに要した工数は約0.5人月で、シミュレーションで実施した場合の見積もり工数約5人月の10分の1の工数で済んだ。これはまさにフォーマル検証の一番シンプルかつ効果の出る使い方であり、当然ながらユーザー独自のアサーションを利用した検証も可能だという。

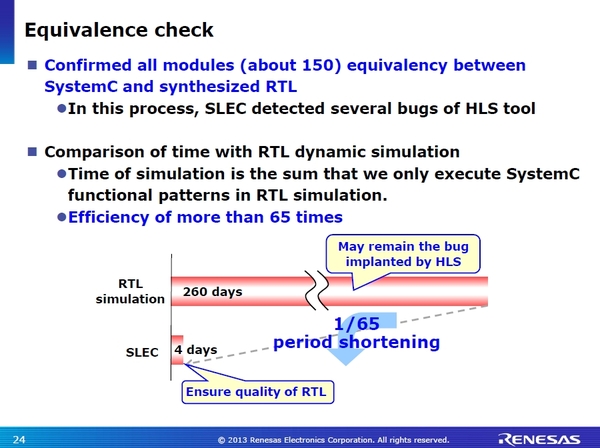

尚、同ビデオIP開発の約150のモジュール設計全てに「SLEC」を利用し高位合成前後の等価性検証を実施したところ、幾つかのモジュールについてはスタックしてしまい検証出来なかった。そこでルネサスとCalyptoは共同で「Blackboxing Function」および「State-encoding map」という2つの新機能を開発した。「Blackboxing Function」は大きな関数を文字通りブラックボックス化する機能で、「State-encoding map」は、高位合成の合成情報をヒントにステート・マシンの等価性検証を容易化するもので、いずれの機能も網羅検証のキャパシティの問題を解決。これにより全約150モジュールの等価性検証を完了できた。この検証に要した工数は僅か4日間で、RTLシミュレーションの約65分の1の工数で済んだという。

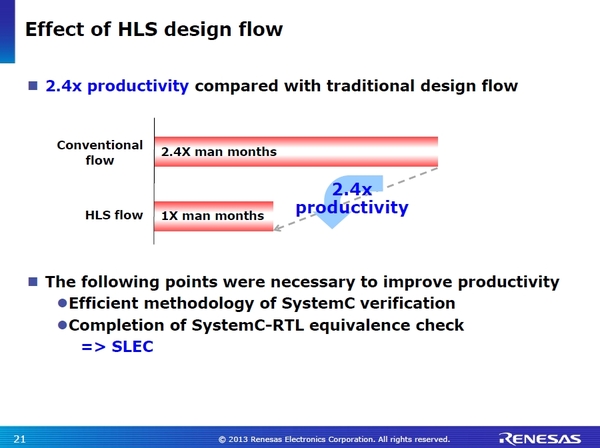

今村氏によると、「SLEC」は高位合成ツールを用いた社内のIP開発フローに標準ツールとして採用したという話で、事例で紹介したビデオIPの開発では、高位合成ツールならびにSLECを用いた設計フローを適用することで、最終的に人手設計の2.4倍の効率化を実現したという事だった。

※記事中のスライド資料は全てルネサス提供のデータ

今村氏の講演の後にCalyptoのマーケティングVPのShawn McCloud氏に話を聞いたところ、同社は業績好調で既にその顧客数は120社以上、中でも「Catapult」の売上強いという事で、2012年には同社の歴史に残るかなり大きな受注を2件獲得したという話。

ツールのアップデートとして今回のDACでは大きなアナウンスは無かったが、「Catapult」はSystemCのサポートやアーキテクチャ・レベルでのローパワー化、インクリメンタル合成、ECO機能など、様々なエンハンスを実施中。この秋口に新たなニュースが出てくるという事だった。ローパワー化ツール「PowerPro」は、RTLパワー解析の速度と精度が高められているほか、パワー記述フォーマット「UPF」もサポートされたとの事、話によると既に「PowerPro」を用いたデザインのテープアウト実績は100件を超えたという。

2013.06.14

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

Forteのブースでは、5月にバージョンアップを発表した高位合成ツール「Cynthesizer」を大々的にアピールしていた。Forteは、新たな合成エンジン「C5」を搭載する最新の製品を「Cynthsizer 5」という名称で呼んでおり、同製品にかける意気込みを感じる。

Forteの説明によると、最新の「Cynthsizer 5」では、高位合成の主要機能であるスケジューリングとアロケーションが改良され、より品質の高い回路合成が可能に。既存の合成エンジンよりも回路面積を削減出来るようになった。

また、ローパワー化の合成機能も大きく強化され、例えばRTLレベルではなく、入力するSystemCのレベルでクロック・ゲーティングの可能性を探るようなローパワー化機能や、ローパワーを意識したFSMの最適化機能やメモリアクセスの最適化機能も実装されたという。

更にSystemCのモデリングおよび解析環境として提供される「Cynthesizer Workbench」も改版され、SystemC IDEとしてSystemCのデバッグ環境が用意された。同IDEを利用するとGUI上でSystemCコードと合成したRTLのクロス・プロービングも可能だという。また、「Cynthesizer Workbench」には、デザイン・サンプルやオンライン・ドキュメント等も豊富に用意されており、HLSの新規ユーザーに対する教育環境としても利用できると聞いた。ちなみにこの「Cynthesizer Workbench」は単体製品として、「Cynthsizer 5」とは別にバラ売りも行なっているとの事。

尚、DAC50を通じて「Cynthsizer 5」の活用事例を耳にする機会が何度かあった。一つは、Qualcommの設計者がデザイナー・トラックで発表していた、高位合成をベースとしたIPサブシシステムのHW-SW協調設計の事例、もう一つは日本のNTTのチームがユーザー・トラックで発表していた、高位合成を用いたビデオ・コーデックLSIの設計事例。いずれの事例においても、既存の設計フローにおいて高位合成を利用し設計生産性の向上を図っているという話だった。

2013.06.14

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

S2Cは、FPGAプロトタイピング・ボードを手掛けるベンダ。DAC直前に発表したプロトタイピング・ボード「K7 TAI Logic Module」を展示していた。

「K7 TAI Logic Module」は同社の第5世代製品ファミリの新製品で、Xilinxの28nm FPGA「Kintex-7」を1個搭載しており、およそ400万ASICゲートのデザインに対応可能。432の外部IO端子、最大10Gbps動作の16チャネル・ギガビット・トランシーバを備えている。

S2CのCEOである中間氏によると、「K7 TAI Logic Module」は、ブロック単位のデザイン検証などに手軽に使ってもらうために用意した低コスト・ボードという事で、その北米販売価格は数千ドル。複数の「K7 TAI Logic Module」をスタックしてより大規模デザインにも対応可能で、同じ同社の第5世代製品で「Virtex-7 2000T」を搭載する「V7 TAI Logic Module」と同じソフトウェア環境(FPGA実装ツール)が提供されるため「V7 TAI Logic Module」へのデザインの移植も容易。当然、S2Cの用意している豊富なインタフェース・カードも利用できるという事だ。

同社の「V7 TAI Logic Module」は、「Virtex-7 2000T」搭載のプロトタイピング・ボードとしていち早く市場に登場し、先行者メリットで顧客の開拓に成功。今年1月には「Virtex-7 2000T」が4個搭載され8000万ASICゲートに対応する「Quad TAI Logic Module」をリリースしている。中間氏によると、製品投入が早かっただけではなく、最新の製品も旧世代の製品もコネクタ形状が同一であるため、製品の世代を超えてインタフェース・カードを共通利用できるなど、ユーザーは利便性の高さを良く理解してS2Cの製品を選択しているという。

2013.06.13

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

例年日本から出展していたNEC、今年は論理シミュレータ他検証ソリューションを提供するAldecのブース内に、パートナーとしてスイートを構えていた。AldecとNECはツールの連携に限らず、ビジネス面においても様々なコラボレーションの可能性を探っているという。

「CWB(CyberWorkBench)」開発責任者の若林に最新の「CWB」について聞いたところ、ビジネスはなかなか順調のようで、EDAの市場が停滞、縮小している日本市場においても昨年はツールビジネスとして黒字を達成。国内企業との比較的大きな契約を獲得出来たとの事で、ユーザーの中には8K スーパー・ハイビジョンのデコーダ設計に「CWB」を用いた例もあると聞いた。

更に驚いた事に、北米においてもネットーワーク系の某大手が「CWB」を採用。その顧客のターゲットはFPGAであったようだが、FPGAベンダの純正高位合成ツールでは所望の回路を実現できないと判断し、評価した結果あえてFPGA純正ツールよりも高価な「CWB」を選んだという。同社はこれに弾みをつけ、ESLの盛り上がる北米、欧州さらにはインド市場まで視野に入れて営業展開を推し進めていく計画のようだ。

「CWB」の機能アップデートとしては、まずSystemC v2.3のフルサポートを完了したほか、ANSI-CベースでC++の機能を取り込む方向で力を入れており、新たにC++のテンプレートやメソッドも利用できるようになった。既存のC++コードから合成したいというユーザーのニーズが増えているという背景があるようだ。

また、FPGA向けの合成機能の強化に力を注いでいるという事で、例えば、LUTをメモリとして利用する(配列をLUTにマッピング)などFPGAのリソースに合わせた「気の利く合成」が可能となった。同機能は劇的なレイテンシの削減効果を生み出すと同時に面積の削減効果もあるという事で、ツール側に自動処理させる事もユーザーが個別にチューニングする事も可能。他にもFPGA向けには多数の機能強化が施されており、その結果としてFPGA向けの合成に関しては、「パフォーマンスを求めるならCWB」と絶対の自信を持っているという事だった。

その他にもCベースならではの、より高い抽象度からのゲーテッド・クロック機能の実装や、ループのマージ機能の強化、リソースの割り当て/共有機能の強化など、パワー削減や細かなパフォーマンスの削減効果を追求しており、合成後に回路のレイテンシ指標を出力する機能なども備えられたと聞いた。

2013.06.13

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

日本から出展したTOOLは、昨年11に発表した「高速抵抗値計算エンジン」の製品版を展示していた。

「RSCALC/RSVIEW」という名称で展開する同製品は、同社のICデザイン視覚検証システム「LAVIS-puls」と連携して動く言わばオプション・ツールで、レイアウト・データ(GDSまたはOASIS)を読み込み「RSCALC/RSVIEW」独自の解析エンジンを使用して、PAD-ブロック間やESD保護素子と内部回路の寄生抵抗などを見積もることができる。

同ツールは、「LAVIS-plus」の等電位追跡機能が使う内部データベースを利用するため高速に解析が可能で、「LAVIS-plus」上のグラフィカルな環境で様々な表示機能を用いて抵抗値を解析、その結果を視覚的に表示できるというのが一つの特徴である。

※画像はLAVIS-plus上でのビューイングの様子

「RSCALC/RSVIEW」は、ネットリスト不要でイージーに抵抗値を解析できるツールとして好評で、既に日本国内では顧客が使用中との事。

尚、同社の旗艦製品であるICデザイン視覚検証システム「LAVIS-plus」は、最新バージョン2.0にてマルチスレッド処理やOASISデータ・ベースをサポート。台湾市場などでライセンス数を増やしていると聞いた。

2013.06.13

6月2日-6日テキサス州オースティンで開催された第50回Design Automation Conferenceの展示会レポート。

日本から出展したジーダットは、発表したばかりのアナログ設計ツールの新製品「Anchor/RVT」と「Anchor/TXA」を展示していた。

「Anchor/RVT」は、既存の回路図をリユースできるアナログ自動レイアウト・ツールで、オリジナルの設計データからトポロジを自動抽出、ターゲット・プロセス向けにPDKの変換を行い、自動的に配置配線を行う。同ツールには回路の最適化機能も備えられており、波形ビューワから回路の最適化箇所を絞込み指定可能という特徴的な機能がある。「Anchor/RVT」は業界標準のデータベース形式「OpenAccess」ベースで開発されており、TSMCのiPDK(interoperable process design kit)をサポートしている。

「Anchor/TXA」は、先端プロセスで発生するLDE(レイアウト依存効果)やばらつきの問題に対応するアナログ自動レイアウト・ツールで、同じサイズでデバイスを作成しアレイ状に並べる「レギュラー・ストラクチャー」という規則的なレイアウトを行う事で、LDEやばらつきの影響を均一化する。同ツールは北九州大学の中武教授の研究成果を利用したものとの事で、回路の性能予測の向上と合わせて手戻り削減によるTAT短縮効果も得られるという。

尚、JEDATは昨年に続き今年もGary Smith EDA社の「WHAT TO SEE @ DAC 2013」リストにその名が掲載された。同社は海外企業も顧客に持つと聞いたが、その大半は日本国内ユーザーと思われ、今後は日本のEDAベンダとして更に知名度を上げ海外展開も頑張って頂きたいところ。ちなみに、「Anchor/TXA」は、先端プロセス向けという事で日本国内よりも海外企業をターゲットに営業を展開していくようだ。

「Anchor/TXA」と「Anchor/RVT」はいずれも現在ベータ版のリリースで、年内に正式リリースを予定している。

2013.06.10

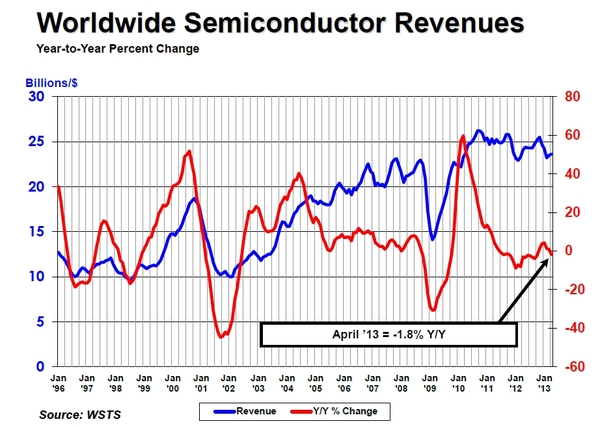

2013年6月5日、米SIA(Semiconductor Industry Association)は、2013年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年4月の世界半導体売上は、前年同月比1.8%減、前月比0.6%増の236.2億ドルで、昨年10月より半年ぶりに前年の売上実績を下回った。

2013年4月の売上を地域別でみると、北米、日本市場が不調で北米は前年比4.4%減、日本は前年比19.4%減と大きく売上を落とした。日本市場は6ヶ月連続で売上2ケタ減の前年割れという深刻な状況に陥っている。

尚、時同じくしてWSTSが発表した2013年春季の世界半導体売上予測は、前年比2.1%増の2978億ドルで、2月時点の予測4.5%増を下方修正した。急激な円安により、日本市場の成長率が見かけ上、世界市場の成長率を押し下げたというのも下方修正の要因の一つであるようだ。

※WSTS:World Semiconductor Trade Statistics

2013.05.31

2013年6月2日より、テキサス州オースティンにて第50回Design Automation Conferenceが開催される。

50回という節目となる今年のDACの開催地オースティンは、半導体関連の企業が多数集まる土地で、半導体売上トップのIntel、2位のSamsungをはじめ、IBM、Freescale、Apple、AMDなどの大手が数千人単位でハード設計/検証エンジニアを抱えており、その数は3万人以上にのぼると言われている。(※WebサイトDeepChipの記事データ参照)

主催者の発表によると、今年の50回DACで採択された論文数は計158本。ベスト・ペーパー候補となっているのは下記8本の論文。今年も昨年に続いてESS関連(組込みシステムおよびソフトウェア関連)の論文が多く、採択された論文の35%はESS関連。ワークショップ、チュートリアル、スペシャル・セッションなどにおいてもESS関連のものが含まれており、カンファレンスにおけるESSの取り込みは継続されている。

・ベスト・ペーパー候補の論文タイトル

-Aging-Aware Compiler-Directed VLIW Assignment for GPGPU Architectures

-An ATE Assisted DFD Technique for Volume Diagnosis of Scan Chains

-Proactive Circuit Allocation in Multiplane NoCs

-A High-Level Synthesis Flow for the Implementation of Iterative Stencil Loop Algorithms on FPGA Devices

-ABCD-L: Approximating Continuous Linear Systems Using Boolean Models

-Scalable Vectorless Power Grid Current Integrity Verification

-Spacer-Is-Dielectric-Compliant Detailed Routing for Self-Aligned Double Patterning Lithography

-Rapid Exploration of Processing and Design Guidelines to Overcome Carbon Nanotube Variations

今年のキーノートには、Freescale, National Instruments, Samsung, Qualcomm, TI, UC Berkeleyからのスピーカーが登壇。FreescaleはIoT(Internet of Things)分野、Samsung, Qualcomm, TIはモバイル分野の話をする予定で、初日はNational InstrumentsのCEOから、そして最終日は業界の重鎮であるUC BerkeleyのAlberto Sangiovanni-Vincentelli氏から、DAC50周年にふさわしいEDAと設計コミュニティの進むべき未来について語られる予定となっている。

また今年は、「Sky Talk」というテクニカル・セッションの新カテゴリが設けられ、Barcelona Supercomputing Center, Cadence, DARPA, D.E. Shaw Research, IBM, NVIDIAおよびStanford Universityより計6講演、30分間のショート・キーノートが行われる。

今回のDACには展示会の出展企業が175社という事だが、重複を除いた実数は168社で昨年より微減。(EDA-EX調べ)うち、実質的に初出展となる企業は計21社で昨年と同数。ちなみに日本からの出展は、TOOLおよびジーダットの2社で毎年出展していたNECは今年はAldecのブースにパートナーとして参加するという。

DACの来場者数は昨年7388人を数え2年連続で上昇に転じたが、今年はどう推移するか予測するのは難しいところ。上述したように設計者の多い土地柄であり、DAC50週年記念という事でカンファレンス自体、様々な企画に力が入っているのがプラス要因と言えるが、シリコンバレーを離れた開催地では集客数が減るという傾向もあり、どの程度人が集まるかは蓋を空けてみないと分からない。

但し、ただ一つ高い確度で言えるのは、日本からの参加者は過去最低の数十名程度であろうという事。かつては大手企業1社から20名以上のエンジニアをDACに送り込むような時期もあったが、今年は大手レベルでも各社から数名程度の参加で、中には人を出さない企業もある。これは国内の半導体業界の現状を表したものと思われるが、国内の設計スタイルが時代に取り残された悪い意味での「ガラパゴス設計」とならないよう願いたい。

今年のDACの展示会で注目したいのは、やはり各社の新製品で、DACでのアピールを狙いEDA各社が直近発表した新製品としては、以下の様な製品がある。

・Forte 高位合成ツール「Cynthesizer 5」

・Oasys Design Systems 等価性検証ツール「Oasys RealTime Parallel EC (equivalency checking)」

・Oasys Design Systems フロアプラン自動生成ツール「Floorplan Compiler」

・Aldec 設計要求管理ツール「Spec-TRACER」

・Cadence タイミング解析ツール「Tempus」

・Jasper Design Automation 複数パワードメイン対応のフォーマル検証ツール「JasperGold(R) Low Power Verification App」

・Sage Design Automation DRCデック開発自動支援するツール「iDRM (integrated design rule management)」

・OneSpin Solutions クラウドベースのフォーマル検証ソリューション

・Real IntentおよびDeFacTo CDC検証とDFTソリューションを組み合わせたRTLサインオフ・フロー

・Berkeley Design Automation アナログ・キャラクタライゼーション環境「ACE」

・Berkeley Design Automation メモリ・CMOSイメージ・センサー向けSPICE 「Analog FastSPICE Mega」

・Intel ESLツール「CoFluent Studio」※高位合成ツール向けのSystemCコードを出力機能

・ジーダット 先端アナログプロセス向け回路・レイアウト自動生成ツール「Anchor/TXA 」および「Anchor/RVT」

・G-Analog Design Automation GPUベースのキャラクタライゼーション・ツール「GChar」

尚、毎年恒例となっているGary Smith EDA社の「DAC要チェックリスト2013年版」は既に公開済みで、計34社がリストアップされている。これらリストに挙げられた企業

の製品については、Gary Smith氏の月曜日のセッション「Gary Smith on EDA: Trends and What's Hot at DAC」にてトレンド解説と合わせて紹介されるだろう。ちなみに、日本のEDAベンダ、ジーダットは昨年に続き今年も同リストにリストアップされている。

当サイトでは、50回DACの現地の状況を取り急ぎTwitterで配信するほか、各種レポート記事を順次アップしていく予定です。