NEWS

2014.04.16

2014年4月15日、Cadenceは、中国のファブレス半導体ベンダSpreadtrumがモバイルSoCの開発用に同社のエミュレータ/アクセラレータ「Palladium XP II」を採用した事を発表した。

発表によるとSpreadtrumは、モバイルSoCの検証およびシステムレベルの妥当性確認向けにCadenceのエミュレータ/アクセラレータ「Palladium XP II」を導入。機能検証プラットフォーム「Incisive」など元々Cadenceの検証環境のユーザーだったSpreadtrumは、製品の市場投入期間の短縮を一つの理由に「Palladium XP II」を導入した。Spreadtrumは、台湾MediaTekに対抗する中国ファブレスの一角としてモバイルSoCの分野でシェアを拡大し続けている。

2014.04.07

2014年4月4日、米SIA(Semiconductor Industry Association)は、2014年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年2月の世界半導体売上は前年同月比11.4%増、前月比1.5%減の258.7億ドルで2月の売上としては過去最高。前年比11.4%増という成長率は過去3年で最も高いものになる。単月の売上記録の更新は昨年9月以来6ヶ月連続で、単月売上が前年実績を上回るのはこれで10ヶ月連続となる。ちなみにこれまでの2月の売上記録は3年前の2011年時点での251.9億ドルだった。

今年の世界半導体市場は概ね前年比5%増の3200億ドル程度と予測されているが、1月は前年比8.8%増、2月は前年比11.4%増と順調な滑り出しとなっている。

売上を地域別に見ると、北米市場が前年比18%増と大きく成長、アジアその他地域、欧州もこれに続き2ケタ前後の伸びを示し、日本市場もほぼ前年と同水準の微減に抑えた。

2014.04.04

2014年3月31日、フォーマル検証ツールを手掛けるJasper Design Automationは、新製品「Sequential Equivalency Checking App」のリリースを発表した。

Jasperは、特定の検証ニーズに特化したフォーマル検証ツールを「Jasper Apps」として展開しているが、今回発表した「Sequential Equivalency Checking App」も「Jasper Apps」の一つで、異なる2つのRTLの機能等価性を検証するもの。

クロック・ゲーティングによるローパワー化など、既存のRTLに手を加えた場合に元のRTLと変更後のRTLの機能等価性をチェックする必要があるが、それをフォーマル検証技術で網羅的に行うのが「Sequential Equivalency Checking App」で、等価性の検証と同時にGUIベースのデバッグの環境も提供する。

同種の製品としてはCalypto Design Systemsが古くから「SLEC RTL」という製品を提供しているが、「Sequential Equivalency Checking App」の強みは高速な処理性能で、新規開発した専用エンジンにより同社の通常のフォーマル検証よりも遥かに高速な検証が可能。市販の他社ツールと比較しても高速で、ある例では他社ツールで2日かけても証明しきれなかったデザインを数時間で証明したという。

Jasperによると「Sequential Equivalency Checking App」は、同社の大手顧客の要求で開発したもので、欧米では既にベータ版から複数の企業が利用。昨年のJasperユーザー・ミーティングでは、NVIDIAが「Sequential Equivalency Checking App」を使った事例を発表している。日本国内においても複数の企業が先行ユーザーとして同ツールを利用しているようだ。

※画像は全てJasper提供のデータ

※株式会社シンコム(Jasper Design Automation社製品国内代理店)

2014.04.03

2014年3月27日、Synopsysは、ソフトウェア開発向けのバーチャル・プロトタイプ本「Better Software. Faster!」の出版を発表した。

Synopsysによると「Better Software. Faster!」は、バーチャル・プロトタイプを活用したソフトウェア開発に関する技術指南書で、実機完成前からのソフトウェア/ハードウェア並行開発、テスト、デバッグを実行するための実践的なガイドラインを約200ページにわたって解説。モバイル機器、コンシューマ機器、産業機器、車載機器など主要な製品分野を網羅した10社以上の顧客事例も収録されているという。

Synopsysは、ソフトウェア開発向けの市販バーチャル・プロトタイピング環境のシェアでは間違いなく首位で競合を大きく突き放している状況。先日はソフトウェア静的解析のCoverity社の買収を完了し、組込みソフト開発へ向けたソリューションの強化と展開を加速しているように見える。

「Better Software. Faster!」は、無料の電子版を下記URLより入手可能。

http://www.synopsys.com/Systems/VirtualPrototyping/vp-book/Pages/default.aspx

2014.04.03

2014年4月2日、Mentor Graphicsは、機能検証プラットフォーム「Questa」に新たにX値検証機能を搭載した事を発表した。

発表によると「Questa」で実現されるX値(不定値)検証機能は、シミュレーション機能とフォーマル解析機能の連携によって実現されるもので、X値伝搬の解析と不定のように見えてしまう信号の特定が可能。X値伝搬の解析機能は市販のフォーマル検証ツール等で様々な形でサポートされているが、悲観的なX値を排除できる機能も備えているのが「Questa」の特徴。この機能によりゲートレベル・シミュレーションで大きな問題となる悲観的なX値に起因するシミュレーションのFAILを防ぎ、無駄なデバッグ作業や過剰設計を減らすことができるという。

2014.04.02

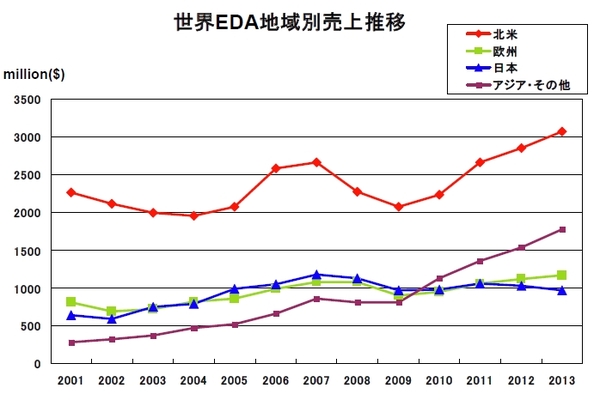

2014年4月2日、米EDA Consortiumは、2013年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

EDACの発表によると、2013年Q4の世界のEDA売上総額は、前年比5.7%増、前Q3比8.7%増の18億8805万ドルで、四半期の売上記録として過去最高を達成。合わせて16四半期連続で売上前年比増を達成した。

2013年の世界EDA売上合計は前年比6.1%増の69億3170万ドルで過去最高を記録した。このペースで行くと今年2014年の世界EDA売上は70億ドルを超えるのは確実である。

2013年Q4の売上を製品分野別に見ると、全ての分野で売上前年比増を達成しており、中でも前Q3で唯一前年比減だったPCB/MCM分野が前年比14.2%増と大きく売上を伸ばした。

2013年Q4の売上を地域別に見ると、北米とアジアその他地域が好調で今四半期も最も売上を伸ばしたのはアジアその他地域。一方、日本と欧州は微減でそれぞれ前年比1%弱売上を落とした。

2013年Q4時点でのEDA業界の従業員数は29880人で、前年比1%増、前期Q3比0.3%減となっている。

2013年Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 7億2170万ドル 4.1%Up

■IC Physical Design & Verification分野 3億8440万ドル 6.6%Up

■IP分野 4億8680万ドル 4.2%Up

■サービス分野 9680万ドル 6.1%Up

■PCB/MCM分野 1億9080万ドル 14.2%Up

2013年Q4地域別の売上と昨年同時期との比較は以下の通り。

■北米 8億2210万ドル 7.2%Up

■ヨーロッパ 3億2890万ドル 0.7%Down

■日本 2億5690万ドル 0.9%Down

■アジアその他地域 4億7270万ドル 12.1%Up

2014.03.26

2014年3月25日、Synopsysは主力のインプリメント・ツール「IC Compiler」の新製品、「IC Compiler II」を発表した。

Synopsysの提供する「IC Compiler」は、フロアプランニングと配置配線を主体としたIC物理設計のインプリメント・ツールで、同社を業界トップに押し上げた原動力となる主力製品の一つ。現在ワールドワイドで約3分の2の市場シェアを持つとされている*「IC Compiler」の最初の製品リリースは2005年で9年振りに新製品のお目見えとなった。

*Synopsysのユーザー調査による予測

新製品「IC Compiler II」は、その処理能力が大きく高められており、今回の新製品発表におけるキーワードは「処理能力10倍」。その意味するところは、フロアプラン、配置配線ともに処理の高速化とメモリ使用量の削減が実現されており、総合的なインプリメントの処理能力として従来製品比10倍の処理能力があるというもの。これにより、より多くのフロアプランを検討できるなど品質面の向上も期待できる。

新製品「IC Compiler II」が既存の「IC Compiler」に対して大きく変わった点は2つ。まず、これまでベースとしていたデータベース「MilkyWay」に代わり「IC Compiler II」では新たなデータベース構造を採用。また、マルチ・スレッド処理の技術をスクラッチから再構築するなど、ツールのインフラ面が大きく進化・変更された。

更に配置配線処理を支えるタイマー、エクストラクター、デザイン・プランニング、最適化エンジン、クロック生成、配線後の最適化機能など、既存の「IC Compiler」でクリティカル・ポイントとなっていた各種処理・機能を改善した。これにより例えばデザイン・プランニングの容量が500Mセルにまで拡張され、「APS」と呼ばれる最適化エンジンにより複数パスのグローバルな解析が可能となった。

※画像は全てSynopsys提供のデータ

逆に既存の「IC Compiler」と「IC Compiler II」が同じ点は、配置および配線のコア機能で、「IC Compiler」で利用されているプレーサー「CGPL Placer」とラウター「Zroute」はそのまま「IC Compiler II」でも使われている。

尚、「IC Compiler II」の製品リリースは2014年中旬の予定で、「IC Compiler II」リリース後も「IC Compiler」は継続的に提供される。既に先行顧客数社が「IC Compiler II」を使用しており、テープアトウトに成功した実績もある。各社共にその処理能力の向上を確認済で、デザインのインプリメントが速くなるだけでなく消費電力の削減効果も出ているとの事。今回の「IC Compiler II」の発表に対して、Imagination Technologies, LSI, Panasonic, Renesas, Samsung, STMicroelectronicsがコメントを寄せている。

2014.03.24

2014年3月21日、Mentor Graphicsは、高速回路シミュレータ「Analog FastSPICE」を手掛けるBerkeley Design Automation社の買収を発表した。

Berkeley Design Automationは、2003年に社長兼CEOだったRavi Subramanian氏が設立したEDAベンダで、2006年に「PLL Noise Analyzer」をリリースし一定の顧客を確保。その後市場投入したSPICE精度の高速回路シミュレータ「Analog FastSPICE」が大ヒット製品となり同社の成長の大きな原動力となった。

同社にはパナソニックやNTTも出資しており、日本国内にも東芝、富士通、パナソニックなど大手を含む多数のユーザーが存在。Mentorの発表によるとワールドワイドで100社以上の顧客がいたという。2012年には、Deloitte社の北米成長企業ランキング「2012 Technology Fast 500」にランキングされたが、当時の実績としては2007年から2011年までの売上の成長率が302%だった。

Berkeley DAの「Analog FastSPICE」は、高精度で高速、しかも大容量と3拍子揃った製品でユーザーの評価も高く、ここ最近のTSMCの先端プロセスでは28nm以降の全てのプロセスで認定ツールとして承認されており、2013年にはTSMCの16nm FinFETプロセスを開発したパートナーとしてTSMCから表彰を受けている。

中小EDAベンダが次々に大手EDAベンダに買収される中で、勢いのある中堅EDAベンダとして存在感を示していたBerkeley DAだったが、今回の買収によりその資産はMentorへと移行。Mentorは、Berkeley DAの買収はアナログ/ミックスド・シグナル検証の強化につながるとしている。

ちなみに、MentorはBerkeley DAの「Analog FastSPICE」の競合にあたる製品「Eldo Premier」*を既に持っているが、ツールとしての実績は「Analog FastSPICE」の方がはるかに多いと推測され、今回の買収はその製品技術と合わせてTSMCなどを含む大きな顧客基盤の獲得を狙ったものと想像できる。

*「Eldo Premier」のエンジンはのBerkeley SPICEとは異なっている。

2014.03.07

2014年2月25日、Cadenceは検証マネジメント・ツールの新製品「Incisive vManager」を発表した。

Cadenceによると、新製品「Incisive vManager」は既存の製品「Incisive Enterprise Manager」の後継製品で、機能検証のプランニングとマネジメントを効率化し、機能検証の品質向上とコスト削減を実現するもの。Cadenceの提唱する制約付きランダム検証をベースとした「メトリクス・ドリブン検証(MDV)」を支援するマネジメント・ツールとして、「Incisive Enterprise Manager」をクライアント・サーバー・タイプに進化させたものが「Incisive vManager」だ。

「Incisive vManager」が狙うのは徹底した検証の「見える化」で、プロジェクト単位あるいは設計ブロック単位で検証の進捗やその中身の詳細を様々な視点、様々なロケーションから確認することが可能。シミュレータ「Incisive」に限らずフォーマル検証ツール「Incisive Formal」、エミュレータ/アクセラレータ「Palladium XP」にも対応しており、シミュレーション、フォーマル検証、アクセラレーションを組み合わせたMDV検証の生産性を2倍に引き上げる事ができるとする。

デザインの大規模化が進み、多拠点、多人数によるチーム設計が広がり、それと合わせて検証のマネジメントがより困難かつ重要になってきている状況受けて用意されたソリューションが「Incisive vManager」で、マルチ・ユーザー、マルチ・ロケーション、更にマルチ・プロジェクトに効率的に対応するために、「Incisive vManager」では新しくSQLデータ・ベースを採用しキャパシティと信頼性を向上。「Incisive vManager」をインストールした環境で行われた検証作業の結果はリアルタイムでサーバーへ送られ、チームあるいはマネージャーと情報共有できる仕組みとなっている。

また「Incisive vManager」では、検証プロセスや進捗の見える化を促進するトラッキング機能の追加をはじめ、各種MDV検証の解析機能が拡張されており、例えば検証対象における機能毎のPass/Failやカバレッジ、設計ブロック毎の検証の進捗、テスト・パターン毎のカバレッジ効果など様々な軸で検証の状況を確認できるようになった。これら機能は一般的にプロジェクトのマネージャーやリーダー向けのものとなるが、単体のツールには無い様々な解析機能は個別のブロックを担当する検証エンジニアにとっても有用なものと言える。

※画像は全てCadence提供のデータ

Cadenceは数年前からMDV検証の有用性をアピールしているが、それに高度なマネジメント環境を組み合わせれば、より検証の生産性を上げることが出来るというのが今回の新製品「Incisive vManager」に込めたメッセージ。裏を返せば今日の大規模設計の検証は、昔ながらのExcelベースのマネジメントではリスクが高いという警鐘とも言える。

※日本ケイデンス・デザイン・システムズ社

2014.03.06

2014年3月5日、Synopsysは機能検証向けの新製品「Verification Compiler」を発表した。

新製品「Verification Compiler」はどのような製品かと言うと、機能検証に包括的に対応するためのワンストップ製品で、シミュレーション、フォーマル検証、デバッグ、という一連の作業を単一環境で完結させるもの。そこには検証で用いる検証IPや検証のカバレッジ解析という要素も含まれている。

一般的な検証作業においては、シミュレータ、フォーマル検証ツール、デバッグ・ツールと個々の市販ツールを使い分けるケースが多いが、その理由の多くは、個別の優れた製品を選択したいという現場ニーズと各ツールを統合したソリューションが存在しないという2点に集約される。

シミュレータはさておき、フォーマル検証ツールに関しては大手EDAベンダ以外の製品が市場をリードする格好となっており、デバッグ・ツールに関してはSynopsysが一昨年買収したSpringSoftの「Verdi」がデファクト・ツールとして君臨していたため、「色々なEDAベンダの色々なツールで検証」という状況が当たり前だった。

今回Synopsysが発表した「Verification Compiler」は、これまでの当たり前の状況を見直すもので、自社のシミュレータ「VCS」、デバッグのデファクト・ツール「Verdi」、そして新たなフォーマル検証エンジンを密接に統合。シミュレーション、フォーマル検証、デバッグ、カバレッジ解析を単一環境で実行可能で、Synopsysの提供する全ての検証IPがこの環境上で利用できる。

この「Verification Compiler」の大きな特徴の一つは、その新たなフォーマル検証エンジンで、これまで提供していたフォーマル検証ツール「Magellan」とは別のエンジンを新たに開発。Synopsysによると同エンジンは他の既存記述よりも3-5倍の速度とキャパシティを誇り、プロパティベースのフォーマル検証に加え、静的なローパワー検証、CDC検証、SoCコネクティビティ検証、シーケンシャル等価性検証、リント・チェックといった包括的な検証機能を提供するという。

またSynopsysは「Verification Compiler」の開発にあたり既存のシミュレーション・エンジンにも手を加えており、制約付きランダム検証のパターン生成時間や、デザインのコンパイル時間、ローパワー・シミュレーションの実行時間などを改善。合わせて検証IPの実行速度やデバッグ用データベース・サイズの最適化を図ることで、Synopsysは総体的な検証パフォーマンスを5倍に改善できるとしている。

尚、「Verification Compiler」は、一つのライセンスで同時並列的にシミュレーション、フォーマル検証、デバッグを実行可能であり、Synopsysはそのコンカレントなツール機能の運用と各ツール機能のシームレスな相互運用性により、検証全体の生産性を約3倍向上できるとしている。

今回「Verification Compiler」の発表にあたり、NVIDIA,Cavium,Alteraの3社が先行ユーザーとしてコメントを寄せているが、同製品の正式リリースは今年12月の予定となっている。

2014.03.05

2014年3月3日、米SIA(Semiconductor Industry Association)は、2014年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年1月の世界半導体売上は前年同月比8.8%増、前月比1.4%減の262.8億ドルで1月の売上記録を更新した。単月の売上記録の更新は昨年9月以来5ヶ月連続で、単月売上が前年実績を上回るのはこれで9ヶ月連続となる。ちなみにこれまでの1月の売上記録は3年前の2011年時点での255.2億ドルだった。

2014年1月の売上を地域別でみると、北米市場が前年比17.3%増と大きく増加。欧州、アジアもこれに続く成長を見せた。日本市場だけは前年比4.7%減だった。

調査会社ほか各種関係機関は、今年の半導体市場の成長率を概ね5%前後と予測しており、1月はそれに向けて幸先の良いスタートを切った形となる。

※SIA

2014.03.04

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2014.03.04

2014年2月27日、Mentor Graphicsは、2014会計年度第4四半期(2013年11月-14年1月)の売上を報告した。

発表によると、Mentorの2014会計年度Q4の売上は、前年比約21%増の4億100万ドル、営業利益は1億1700万ドルで前年比65%増だった。Mentorが四半期売上において4億ドルを超えるのは史上初。(※GAAP基準による会計結果)

最終的にMentorの2014会計年度(2013年2月-2014年1月)の売上合計は前年比6.2%増の11億5600万ドルで過去最高。営業利益は前年比13.6%増の1億8300万ドルだった。

Mentorの今期Q4の売上を市場別で見ると、日本国内の売上は全体の15%で2014会計年度を通じて最も良かった。

Mentorは次期2015会計年度Q1(14年2-4月)の売上2億4500万ドル、2015会計年度の売上合計を12億4700万ドルと予測している。

2014.02.27

2014年2月26日、Synopsysは、新製品となるエミュレーション・システム「ZeBu Server-3」を発表した。

Synopsysが発表した「ZeBu Server-3」は、エミュレーション・システム「ZeBu」シリーズの最高峰に位置する製品で、既存製品の初代「ZeBu Server」がVirtex-5ベースだったのに対して、「ZeBu Server-3」ではXilinxの最新の28nm FPGA Virtex-7 XC7V2000Tをベースとしている。

Synopsysに2012年に買収された旧EVE社が開発した「ZeBu」シリーズ製品は、FPGAのテクノロジの進化と共に新製品の投入を進めてきており、今回の「ZeBu Server-3」はEVE社の時代から数えて8世代目の製品となる。ちなみに6世代目のVirtex-5ベースの初代「ZeBu Server」が投入されたのが2009年、7世代目のVirtex-6ベースの「ZeBu-Blade2」が投入されたのが2011年である。

※画像はZeBu Server-3、Synopsys Webサイト掲載。50cm2、70kgとその小ささも特徴の一つ。

※画像はZeBu Server-3、Synopsys Webサイト掲載。50cm2、70kgとその小ささも特徴の一つ。

今回発表された「ZeBu Server-3」は、FPGAの進化の恩恵を受け実行スピードは初代「ZeBu Server」よりも最大4倍の高速化を実現したという事で、ビリオン・クラスの大規模デザインを数Mhzで実行できる計算(デザイン・クロック)。デザイン容量は「ZeBu Server-3」1台で3億ASICゲートで、10台接続することで最大30億ASICゲートのデザインに対応できるという。

今回の新製品においては、特に大きな機能面での強化は施されていないようだが、既存の使い勝手のままでソフトとハードを入れ替えれば4倍高速で容量3倍というのは、ユーザーにとって大きな魅力と映るだろう。

2014.02.26

2014年2月19日、インターコネクトIPを手掛けるArterisは、Freescaleへ同社のインターコネクトIP「FlexNoC」をライセンスした事を発表した。※追記あり

Arterisの発表によるとFreescaleは、Powerアーキテクチャ・ベースのプロセッサ「QorIQ」シリーズのSoC向けにArterisのインターコネクトIP「FlexNoC」のライセンスを獲得。Freescaleは2011年からArterisの顧客であり、今回のライセンス契約により複数品種のチップ開発で「FlexNoC」を使用するという。

Arterisは昨年10月にQualcommへのインターコネクト技術をはじめとする技術資産の売却を発表したが(※関連ニュース)、主力製品のインターコネクトIP「FlexNoC」の販売、エンハンス、サポートは引き続き継続する方針としており、実際にそのような形でビジネスが進められている様子。

2月18日には、元AppleのエンジニアリングVPでiPhoneのアプリケーション・プロセッサの半導体設計チームを立ち上げたCraig Forrest氏ほか2名の入社を発表し、技術陣営の強化をアピールした。発表によるとCraig Forrest氏はArterisのCTOに就任したとの事だ。(プレスリリース文)

Qualcommとの一件が報じられた後にArterisによってユーザーの採用事例がアナウンスされるのは、フランスの家電大手Schneider Electricに続いて今回Freescaleが2件目。

※Arteris

2014.02.21

2014年2月19日、Synopsysは、2014会計年度第1四半期(13年11-14年1月)の四半期決算を報告した。

発表によると、Synopsysの2014会計年度Q1の売上は、前年同時期比約0.8%増、前期13年Q4比約5%減の4億7900万ドルで前Q4決算報告時の予測通り。純利益は前年同時期より微減の6770万ドルだった。(※GAAP基準による会計結果)

Synopsysは僅かながらQ1も売上前年実績超えを達成し、14四半期連続の成長を記録。若干成長率が緩やかになりつつあるが、来期Q2売上を5億500-1500万ドルと予測しており、またしても四半期売上記録を塗り替える可能性がある。

また、昨年は企業買収の発表が無かったが、Synopsysはこの2月にTarget Compiler TechnologiesとCoverityの買収を立て続けに発表しており、今年は従来の半導体設計以外の分野への投資や事業展開が加速しそうだ。

Synopsysは、2014会計年度の売上を前年を上回る20億ドル以上と予測している。

2014.02.21

2014年2月19日、Synopsysはソフトウェア静的解析ツールを手がける米Coverity社を買収する事を発表した。

Synopsysの発表によると、Coverityの買収金額はおよそ3億7500万ドルで2014年第2四半期中(4-6月)に買収手続きが完了する予定。

Coverityは、2002年に米スタンフォード大の研究成果をベースに設立された企業で、組込みソフトやアプリケーションソフトのソースコード解析を行う静的解析ツール「Coverity Static Analysis Verification Engine(Coverity SAVE)」を中心にビジネスを展開し、ソフトウェアの品質とセキュリティの向上をターゲットに急速にシェアを伸ばしていた。

「Coverity SAVE」は、複数の解析技術を用いてソースコードの全実行可能パスを網羅的に解析する事が可能で、誤検知率が低い高精度なバグ検出が可能とされている。

Synopsysによると、世界のソフトウェア企業上位10社のうち9社、宇宙航空・防衛企業上位10社のうち7社、グローバル・ブランド企業上位10社のうち8社、半導体上位10社のうち6社が既にCoverityの顧客であるとの事で、その顧客総数は世界1100社以上だという。

Synopsysは2006年に仮想プロトタイピング・ツールを手掛けるVirtio社を買収した後、2010年に同じく仮想プロトタイピングを手掛けるCoWareとVaSTの2社を買収。この辺りが同社のソフトウェア開発分野への参入の第一歩であったが、今回買収を発表したCoverityのソリューションは、あらゆるソフトウェアの品質とセキュリティを対象とした明確なソフトウェア開発ソリューションであり、ソフトウェア開発分野への事業展開という意味で今回の買収はSynopsysのM&A史に残る大きな案件となるだろう。

※日本シノプシス合同会社

※Coverity

2014.02.20

2014年2月、Cadenceは同社の主力IP、Tensilica製品に関する6つのプレス発表を行った。発表順に紹介すると以下の様な内容となる。

「Tensilica HiFi Audio Tunneling for Android」は、Androidの最新バージョン「Kit Kat」のオーディオ・トンネリング機能を活用したもので、オーディオ処理に必要な電力を最大で14分の1までに削減。KitKatの機能自体、Tensilicaが提案したアイデアをベースに開発されているとの事。

MoveaはIntelが出資しているフランスベンチャー企業で、同社の「SmartMotion」は、スマホやタブレットなどのモバイル端末に使用される動作認識ソフトで、STMicroelectronicsがセンサ・ハブ・コントローラに組み込んだりもしている。

Rubidiumは、音声合成、音声認識、話者認識などの組込み音声技術を提供するイスラエルのベンチャー企業。英ファブレスのCSRとのコラボレーションの実績がある。

SensoryはCadenceに買収される前からTensilicaと共同した超低消費電力の音声起動技術を提供していたが、同技術の更なる低電力化を実現。実行時の平均電力消費量が既存のソリューションよりも約3割減の17μWとなった。

最初のXbox-oneの発表以外は、来週からバルセロナで開催されるMobile World Congressで初披露される技術やソリューションに関するもので、Tensilicaの買収によりモバイル向けDSPコアを手に入れたCadenceの鼻息の荒さが感じられる。

2014.02.20

2014年2月14日、Cadenceは、通信インフラ向け半導体を手掛けるTranSwitch社の保有する高速インタフェースIPの資産を買収した事を発表した。

Cadenceは今回の買収に関する取引条件を明らかにしていないが、買収によって獲得したのは、HDMI、DisplayPort、MHL、EthernetのIP(コントローラとPHY)で同IP製品の開発チームも受け入れた。WebメディアSemiWikiの記事によると、Cadenceの買収したTranSwitch社のIP資産の事業規模は数百万ドル規模との事。

Cadenceは今回獲得したIP資産により、同社IPビジネスの強みであるEthernet IPソリューションを更に強化。HDMIについては既に提供している検証IPに加えて設計IPも提供可能となる。CadenceのIP事業は、ARM,Synopsys,Imagination Technologyに次ぐ市場シェア4位の規模と推測されている。

2014.02.12

2014年2月3日、Mentor Graphicsは、スウェーデンのMecel AB社からECUソフトの開発ツールを買収した事を発表した。

発表によると、MentorはMecel AB社からAUTOSAR対応のECUソフトの開発スイート「Mecel Picea」を含むAUTOSAR関連資産を買収した。同社は2005年からAUTOSARのワーキングに参加している企業で、AUTOSAR関連の各種開発サービスなども提供していた。また同社はUTOSARソリューションの他に、ECUのソフトウェア・コンポーネント、自動車向けのBluetoothプラットフォーム、自動車向けのHMI (Human Machine Interfaces)開発プラットフォームなど様々な自動車向けのソリューションを展開している。

Mentorは以前から取り扱っていたワイヤ・ハーネス設計ツールをベースに、自動車向けソリューションへの投資を続けており、電装システム設計、車載電子システム設計へとそのソリューションを拡大させている。今回買収した「Mecel Picea」を含むAUTOSAR関連資産は、2005年に買収した「Volcano」の提供するAUTOSARソリューションを補完するものであるという。

2014.02.12

2014年2月7日、Synopsysは、ベルギーのEDAベンダTarget Compiler Technologies社の買収を発表した。

発表によると、Synopsys社によるTarget Compiler Technologiesの買収は既に完了済。その取引条件などの詳細は明らかにされていない。

Target Compiler Technologies社は1996年に設立されたEDAベンチャーで、創立メンバーはベルギーの研究機関IMECからのスピン・アウト組。同社は、独自のプロセッサ記述言語「nML」を使ってプロセッサのアーキテクチャを定義することにより、合成可能なASIP(特定用途向けプロセッサ)のHDLコードやソフトウェア開発ツール環境(Cコンパイラ、命令セット・シミュレータなど)を自動生成するカスタム・プロセッサ開発用のツールセット「IP Designer」、「IP Programmer」、「MP Designer」を提供していた。

同社の製品は、Philips、STMicroelectronics、Nokiaといった欧州大手で採用実績があり、国内ではイノテックが代理店として販売。日本にも顧客が存在している。

EDA市場で一定の実績を残しているASIP開発ツールは、Target Compiler Technologies社の提供していた製品と、Synopsysが旧CoWare社の買収によって獲得した「Processor Designer」のみで、Synopsysは今回の買収により同分野の市場を独占する事になる。

2014.02.08

SystemC Japan 2014

2014年6月20日(金)/新横浜国際ホテル

事例講演の公募について

今年の「SystemC Japan 2014」では、ユーザー事例セッションの発表を以下の通り募集致します。

| ■ |

発表内容: |

SystemCを用いた設計・開発手法の紹介 |

| ■ |

募集開始: |

2014年2月14日(金) |

| ■ |

募集期限: |

2014年3月14日(金) |

| ■ |

申込方法: |

所定の申し込みフォームに必要事項、発表の概要を記述し、pdfファイル にてinfo@systemcjapan.comにメール添付でご提出下さい。 |

| ■ |

審 査: |

2014年3月末日までに発表者を決定(予定) |

| ■ |

審査基準: |

1.IEEE標準の一つであるSystemCを使うことのメリットが分かりやすい

2.システムとソフトウェア、半導体の融合等により、高付加価値の設計のチャレンジを支援すると思われる手法や適用事例

|

| ■ |

講演資料提出期限: |

2014年5月30日(金) |

| ■ |

その他: |

採用された講演者様には賞品として「MacBook Air 11インチ 128GBモデル」を進呈致します。

その他、応募内容により、特別賞などのご用意する予定です |

| ■ |

申し込みフォーム: |

http://www.systemcjapan.com/Img/SCJ2014_entry_form.doc |

■■お問い合わせ■■

SystemC Japan 2014に関するお問い合わせは、下記窓口までお願い致します。

SystemC Japan 2014運営事務局 ?EDAエクスプレス info@eda-express.com

2014.02.06

2014年2月5日、Cadenceは、SystemCからの高位合成ツールを手がける、Forte Design Systemsを買収することを発表した。

発表によると、今回の買収についてCadenceとForteの両社は正式契約を済ませ、30日以内に買収手続きを完了させる予定。その買収金額などの詳細については明らかにされていない。

Cadenceは、買収するForteの高位合成ツール「Cynthesizer」と同じSystemCを入力とした高位合成ツール「C-to-Silicon Compiler」を自社製品として提供しており、これまでForteとは競合の関係にあったが、今回の買収でForteの高位合成ツールを取り込み、システムレベル設計ソリューションを大きく強化する構え。

Forteは、2001年の時点で既に高位合成ツール「Cynthesizer」をリリースしていた業界の老舗で、ここ数年は北米を中心とした高位合成ニーズの増加の波に乗り業績は好調。日本国内でも多くのユーザーを抱えており、EDA専門の調査会社の調べでは業界トップシェアを誇るとされている。(※関連ニュース)

Cadenceが高位合成ツール「C-to-Silicon Compiler」を市場投入したのは2008年と比較的日が浅いが、自社論理合成ツール「RTL Compiler」に繋がるフローとその合成エンジンは、一定の顧客に受け入れられており、Forte,Calyptoに次ぐ第三の高位合成ツールとして存在感を示していた。高位合成の世界において最初に「ECO機能」を掲げたのは恐らく「C-to-Silicon Compiler」だ。

高位合成ツールの市場は、2000年初頭から大きな期待が集まり、数々のEDAベンダが立ち上がっては買収されるか消えていくというサバイバル市場で、日本が創成期の市場を牽引し、ここ数年でようやくワールド・ワイドで市場が立ち上がってきた状況。

EDA大手3社の状況を見ると、Synopsysは一度自社製品「Behavior Compiler」の失敗で高位合成市場から撤退した後、2010年に高位合成ツールベンダSynforaを買収し高位合成市場に再参入したが、以降、目立った成功は納めていない。Mentorは、育ててきた自社ツール「Catapult」の資産を2011年にCalypto Design Systemsに売却し、現在直接的には高位合成ツールを取り扱ってはいない。今回のCadenceによるForteの買収が完了すると、Cadenceは一気に高位合成ツールのトップ・ベンダとなり、システムレベルの合成ソリューションにおいて競合に大きく差をつけることになる。そして、その差は意外と大きいかもしれない。

2014.02.05

2014年2月4日、ARMは、2013会計年度第4四半期(2013年10-12月)の売上を報告した。

ARMの2013年Q4の売上は、前年比15%増、前期比約5.6%増の3億290万ドルで前Q3に続いて四半期売上記録を更新、税引き前の純利益は前年比約15%増の約1億5600万ドルだった。

売上の内訳を見るとライセンスの売上が前年比約27%増の1億2740万ドル、ロイヤリティの売上が前年比約7%増の1億4640万ドルだった。ライセンスの売上が堅調な伸びを示したのに対し、ロイヤリティの売上は勢いを失いつつあり、市場関係者はスマホ需要の鈍化によるものと指摘している。

ARMは2010年Q1より四半期売上の前年増を継続しており、今期で17四半期連続で売上前年増を達成。2013年会計年度の売上合計は、前年比24%増の11億1770万ドル、税引き前利益は前年比32%増の5億6900万ドルでいずれも過去最高となった。

ARMがこのQ4で獲得したプロセッサ・ライセンス契約は22社、26件でその半数以上が同社の新規顧客だった。プロセッサ・ライセンス契約の内訳は下記の表の通りで、ARMv8アーキテクチャのアーキテクチャ・ライセンス1件とCortex-A50シリーズのプロセッサ・ライセンスが2件含まれているとの事。

尚、ARMは各半導体ファウンドリのFinFET process向けにフィジカルIPを提供しているが、同フィジカルIPを用いたチップ設計がこのQ4で2件スタート。現在、ARMのFinFET process向けフィジカルIPを用いた設計が計4件進行中だという。

※画像はARM発表資料より抜粋

2013年Q4で出荷されたARM搭載チップの総数はQ3を上回る約29億個で2013年の出荷総数は100億個を超えた。その内訳は以下の表の通りで、モバイルデバイス向けが占める割合が減り、コントローラー、スマート・カード、ウェアラブル・デバイスなど組み込み向けの出荷が増え全体の32%を占めた。組み込み向けの出荷数は前年比35%増と成長しており、それと合わせてARM7コアの出荷数も増えている。

※画像はARM発表資料より抜粋

2014.02.04

2014年2月3日、米SIA(Semiconductor Industry Association)は、2013年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年12月の世界半導体売上は前年同月比7.7%増、前月比2.0%減の266億5000万ドルで、今年の2月以降10ヶ月連続で前年実績を上回った。

最終的に2013年(1-12月)の売上合計は、前年比4.8%増の3055億8000万ドルで過去最高を記録。日本を除く全ての市場で5%以上の成長を遂げ、中でも北米市場は前年比13.1%増と際立った成長を見せた。

2013年世界半導体市場の売上を製品カテゴリ別に見ると、ロジックの売上が前年比5.2%増の859億ドル、メモリの売上が前年比17.6%増の670億ドルと大きく成長、DRAMの売上は前年比33.3%増、NANDフラッシュの売上は前年比8.1%の伸びを示した。MOS micro-ICの売上は587億ドル、アナログの売上は401億ドル、オプトエレクトロニクスの売上は276億ドルだった。

尚、2012年12月時点の予測で2013年の半導体市場の成長率をほぼ当てたのはIDCで、Gartnerも精度の高い予測をしていた。※関連ニュース

2014年の世界半導体市場は概ね3-5%前後の成長と予測されている。

※SIA

2014.01.31

2014年1月29日、Cadenceは、2013会計年度第4四半期(2013年10-12月)の売上を報告した。

プレスリリース文

http://www.cadence.com/cadence/newsroom/press_releases/Pages/pr.aspx?xml=012914_financial&CMP=home

Cadenceの2013年Q4売上は、前年同時期比約8.9%増、前期Q2(13年4-6月)と比較して約2.7%増の3億7700万ドル。純利益は約3800万ドルで昨年よりも大幅に減った。

2013会計年度の売上合計は14億6000万ドルで前年比約10%増の伸び。純利益は1億6400万ドルで前年比約67%減だった。(※GAAP基準による会計結果)

CadenceのQ4売上実績は前Q3売上報告時の予測通りで、同社の売上はこれで16四半期連続で前年比増を記録。2010年から4年間連続で右肩上がりの成長を遂げたことになり、この4年間で売上は約1.7倍、株価は倍以上になった。

同社のCEO Lip-Bu Tan氏もコメントしているが、Cadenceは2013年中にこれからの主力製品となる複数の新製品をリリースしている他、Tensilicaをはじめとする複数のIPベンダの買収実施しIPポートフォリオを強化。今年以降も更に売上を伸ばしていく体制を整えている。

Cadenceは引き続き継続した成長を見込んでおり、次期2014年Q1の売上を3億7300-8300万ドル、2014年の年間売上を15億5000万-8500万ドルと予測している。

2014.01.31

2014年1月30日、ハードウェア設計の教育、コンサルティング、デザイン・サービスを手掛けるエッチ・ディー・ラボは、同社が国内初のXilinx認定トレーニング・プロバイダーとなった事を顧客にアナウンスした。

hdLabによると、Xilinxが公式に認定したトレーニング・プロバイダーは、hdLabが国内初。hdLabはこれを受けて2月からXilinxが開発した技術トレーニングの提供を開始する。

既に予定されているトレーニング・コースとしては、ARM搭載FPGA「Zynq」に関するコースが一つと、高位合成機能を備えるXilinxのFPGA開発ツール「Vivado」に関するコースが2つの計3種類で、今後順次開催コースを増やしていく予定だという。

2014.01.28

2014年1月23日、フォーマル検証技術をベースとしたEDAソリューションを手掛ける米Real Intentは、同社がSiliconIndia主催のアワード2部門を受賞した事を発表した。

SiliconIndiaは、エレクトロニクス分野を中心としたインド人向けのオンライン・コミュニティで、Webおよび雑誌媒体を中心に様々な情報を発信している。

今回Real Intentが受賞したのは、SiliconIndiaが選ぶ「si100 list」と「top 25 enterprise software companies」の2つのアワード。受賞したというよりは優れた企業として、リストに選出されたという方が分かりやすい。

SiliconIndiaの「si100 list」は、インド人によって米国で設立および経営されているテクノロジー企業トップ100を選出するもので、SiliconIndiaの編集部、インド人アナリスト、ベンチャーキャピタル、企業経営者などによって1500近くの候補から選ばれる。同リストにReal Intentが選出されたという事は、EDAという狭い世界だけでなくインド人を中心としたハイテク・コミュニティの中で同社が一定の評価を受けた結果と言える。

Real Intentはフォーマル検証ツール、Lintツール、CDC検証ツールが好調で、2013会計年度は売上前年比60%増を達成。昨年11月には、NECが通信システム用LSIの開発でReal Intentのフォーマル検証ツールを標準採用したとアナウンスしている。※関連ニュース

2014.01.27

2014年1月16日、グラフィックスIPコアを手掛ける国内のIPベンダDMP(ディジタルメディアプロフェッショナル)は、同社のグラフィックスIPコアがオリンパスのミラーレス一眼カメラ「OLYMPUS OM-D E-M1」に採用されたことを発表した。

発表によると今回オリンパスに採用されたDMPのグラフィックスIPコアは、「SMAPH-H」という3Dグラフィックス(OpenGL ES 1.1)と2Dベクターグラフィックス(OpenVG)の双方に対応するUIアプリケーション向けのハイブリッドIPコアで、DMPが業界初のモバイル・コンシューマ向け製品として売り出しているもの。

オリンパスは、DMPのグラフィックスIPコアの採用と合わせて、IPコアのサイズや消費電力の最適化、デバイス・ドライバの実装などでDMPのプロフェッショナル・サービスを活用したという。

同IPコアを搭載したミラーレス一眼カメラ「OLYMPUS OM-D E-M1」は昨年10月に発売されたオリンパスの最上位機種で、新たな画像処理エンジンを搭載し、コントラストAFと像面位相差AFを組み合わせた「DUAL FAST AF」機能などが実装されている。価格比較サイト「価格.com」のデジタル一眼カメラの売れ筋ランキングでは、今年に入り一時2位まで上昇した人気機種との事だ。

2014.01.27

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2014.01.27

2014年1月23日、Alteraは2013会計年度第4四半期(13年10-12月)の売上を報告した。

発表によるとAlteraの2013年Q4(13年10-12月)売上は、前年比約3%、前期Q3比約2%増の4億5440万ドル、営業利益は前年を下回る1億1715万ドルだった。

Alteraの2013会計年度の売上合計は、前年比約3%減の17億3257億ドル、営業利益は前年比約20%減の4億7575万ドルという結果に終わった。Alteraの2013会計年度は、Q1とQ4で売上前年増を記録したがQ2,Q3は前年割れだった。

Alteraは競合のXilinx同様、28nm FPGA製品が好調で2ケタ成長を遂げており、2014年Q1から量産出荷を開始する計画の20nm FPGAに大きな期待を寄せている。

AlteraのQ4売上を地域別で見ると、日本市場の売上が前Q3実績に対して13%成長、最大市場のアジアと北米もそれぞれ5%成長したが、2013会計年度でみるとアジアと北米が前年割れ、日本と欧州が前年比増を達成した形となった。

Q4売上を分野別で見ると、主力のテレコム/ワイヤレス分野が前年比6%減、2013会計年度の合計では同分野の売上が前年比9%減となっており、屋台骨の不調が同社の業績に現れた格好となっている。

製品別では、最新の28nm製品を含む新製品カテゴリの売上が前年比26%増と前期に続いて大きく成長。年間合計でみても前年比31%増と売上を伸ばし、売上に占める新製品カテゴリの割合は、昨年同時期で39%だったが今年は47%にまで上昇た。

Alteraは次期2014年Q1(1-3月)の売上を2013年Q4の2-6%減と予測している。

2014.01.24

2014年1月22日、CadenceとBerkeley Design Automationの両社は、両社の訴訟の和解を発表した。

今回和解に合意したのは、Cadenceが著作権の侵害を理由にBerkeley DAを訴えていた訴訟で、Berkeley DAがCadenceとの契約条項に反してCadenceのアナログ設計環境「Virtuoso Analog Design Environment(ADE)」にSPICEシミュレータ「Analog FastSPICE(AFS)」を接続するインタフェースを開発したというもの。

※関連ニュース:CadenceがBerkeley Design Automationを著作権の侵害で提訴

Berkeley DAはCadenceの訴えを事実無根としていたが、最終的に両社は両社ツール間のOASISインタフェースを通じたインターオペラビリティをサポートするという複数年契約に合意。Berkeley DAはそれに伴う(OASISライセンス料と思われる)費用をCadenceに支払うようだ。

結果的に手打ちとなった形だが、Webサイト「DeepChip」の記事によると、この訴訟は最終的に法廷でCadenceの訴えが却下されたようで、事実上Berkeley DAの勝利と見る向きもある。

※DeepChipの関連記事→http://www.deepchip.com/items/0535-07.html

2014.01.24

2014年1月16日、フォーマル検証ツールを手掛ける、米OneSpin Solutionsは、同社の2013年の業績を発表した。

発表によるとOneSpinの2013年の業績は非常に好調で、売上は前年比100%増すなわち2倍を記録し、受注額は前年比200%で3倍に達したとの事。

ここ最近OneSpinは、ASICに限らずFPGA設計も視野に入れてフォーマル検証の利用を進めており、昨年11月には、クラウド・ベースのFPGA設計プラットフォームを提供する米Plunify社のソリューション「EDAxtend」でOneSpin社のフォーマル・検証ツールが利用可能となった。

また同社自身、1時間25ドルから使用できる、Amazonのインフラを利用したクラウドベースのフォーマル検証ソリューションの提供を開始しているほか、Mentorに技術資産を売却したOasys Design Systemsに等価性検証ツールの技術をOEM供給するなど、ツールの開発、エンハンス以外にもサービス面で積極的に活動している印象が強い。

※OneSpin Solutions

2014.01.24

2014年1月22日、SystemCからの高位合成ツールを手掛ける、Forte Design Systemsは、同社の2013年の業績と市場シェアについて発表した。

Forteによると、同社の2013年の売上は前年比2ケタ増を達成し7年連続の売上増を記録。同社の最近の新規顧客としては、LG Electronics、日立情報通信エンジニアリング、京セラドキュメントソリューションズなどがあり、いずれも競合ツールからの乗り換えでForteの「Cynthesizer」を導入したという。

またForteによると、米国のEDA関連調査会社Gary Smith EDA社の調べでは、「ESL Synthesis」すなわち高位合成の分野でForteのシェアは31%で業界首位。Forteは同じくGary Smith EDA社の調べにおいて2011年にCalyptoを抜いて業界首位に立ったとされているが、2013年の好調な業績により、高位合成ツールのシェアで競合に更に差をつけたとしている。

2014.01.24

2014年1月21日、Xilinxは同社の20nm FPGA「Virtex UltraScale」のテープアウトを発表した。

「Virtex UltraScale」は、ASIC並みのクロック機能をうたう新たな「UltraScale アーキテクチャ」を採用する20nm FPGAファミリで同社最高峰の製品に位置するもの。既に「Kintex UltraScale」はサンプル出荷されているが、今回初めてテープアウトされた「Virtex UltraScale VU095」は、94万ロジックセル、150G Interlakenコア6個、100G Ethernetコア4個搭載、32.75Gb/sトランシーバーがチップ間、チップと光モジュール間、28Gb/sバックプレーンをサポート。4x100Gトランスポンダ、4x100G MAC-InterLakenブリッジなどのハイエンド通信インフラ・アプリをはじめ、宇宙航空/防衛、テスト/計測装置、ハイパフォーマンス・コンピューティングなどの高性能アプリを狙う。

TSMC 20nmプロセスで製造される「Virtex UltraScale VU095」は、今年Q2には出荷が開始される予定だという。

2014.01.24

2014年1月23日、Xilinxは2014会計年度第3四半期(2013年10-12月)決算を報告した。

Xilinxの2014会計年度Q3の売上は、前年同時期比15%増、前期Q2比2%減の5億8700万ドル。営業利益は前年比68%増、前期Q2比24%増の2億270万ドルで粗利益率は69.1%だった。(※GAAP基準による会計結果)

同社のCEOのコメントによると、Q2で売上8000万ドルを超えた28nm製品がQ3は1億ドルを突破。「Kintex-7」や「Zynq-7000」の売上が好調だったとの事。同社の売上は2013年4月以降、回復基調に変わっている。

XilinxのQ3売上を地域別でみると、アジア地域の売上が好調で全売上の40%を占めた。分野別の売上では、主力のコミュニケーションおよびデータ・センター、産業機器/航空宇宙防衛の2分野が堅調な伸びを示し、放送、民生機器/車載分野も好調だった。

製品別売上では、28nm製品を含む主力の新製品カテゴリ(Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6)の売上が引き続き伸びており売上で前年比78%増、売上全体に占める割合を38%まで高めた。

Xilinxは、次期2014年Q4(14年1-3月)の売上を今期実績の2%-6%増と予測をしている。

2014.01.22

2014年1月21日、Mentor Graphicsは、中国の公的研究機関である上海張江創新学院が同社のエミュレーター「Veloce2」を導入したことを発表した。

上海張江創新学院は、張江ハイテクパークに2006年に設立された公的機関で、エレクトロニクス、バイオ、ITなど複数分野の技術開発を進める傍ら各分野の人材育成(職業訓練)にも力を注いでいる。

今回、上海張江創新学院は、SoC設計の機能検証を対象とした研究開発にMentorの「Veloce2」を採用。「Veloce2」はエンジニアへの教育にも利用されるようで、担当者は「Veloce2を使って中国で毎年300?500名のエンジニアにSoC検証のベストプラクティスを学んでもらう予定」とコメントしている。

中国では転職率が高いため、上海張江創新学院は企業の人材育成を肩代わりする形で大卒以上の社会人を対象にレベルの高い職業訓練を実施しているようだ。

2014.01.15

2014年1月14日、米EDA Consortiumは、2013年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

EDACの発表によると、2013年Q3の世界のEDA売上総額は、前年比6.8%増、前Q2比4.6%増の17億2930万ドルで、Q3としての売上記録を更新すると同時に四半期ごとの世界EDA売上総額として15四半期連続で売上前年比増を達成した。

2013年Q3の売上を分野別に見ると、PCB/MCM分野以外の全ての分野が売上増となり、IC Physical Design & Verification分野はQ2に続いて11.1%の高成長。IP分野とサービス分野もそれぞれ12.7%、10.4%と大きく伸びた。

2013年Q3の売上を地域別に見ると、ここ最近のパターン通り日本を除く全ての地域で売上前年比増を達成。最も伸びたのはやはり前Q2同様アジアその他地域だった。しかしアジアその他地域の売上は、Q1で前年比20.5%、Q2で18%増だったが今期Q3は14.4%と若干ペースが落ちてきた感がある。その反面、為替レートの影響で一人負けの状態だった日本市場は、売上の下落ペースが緩やかになりつつある。

2013年Q3時点でのEDA業界の従業員数は29967人で、前年比3.8%増、前期Q2比2.3%増となっている。

2013年Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億4350万ドル 1.7%Up

■IC Physical Design & Verification分野 3億6290万ドル 11.1%Up

■IP分野 4億7690万ドル 12.7%Up

■サービス分野 9350万ドル 10.4%Up

■PCB/MCM分野 1億5250万ドル 0.3%Down

2013年Q3地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億7070万ドル 7.7%Up

■ヨーロッパ 2億8550万ドル 6.7%Up

■日本 2億2380万ドル 8.2%Down

■アジアその他地域 4億4930万ドル 14.4%Up

2014.01.14

2014年1月13日、Cadenceは同社の機能検証プラットフォーム「Insicive」のバージョンアップを発表した。

発表によると最新の「Incisive 13.2」では、IPブロック検証ならびにSoCインテグレーション検証に向けた包括的な機能強化を実施。主なエンハンス項目として以下の点を挙げている。

【IP機能検証向け】

・新たなフォーマル検証エンジンにより、フォーマル解析の性能を最大で20倍までに向上

・シミュレータに内蔵した新たな制約エンジンにより、UVMとSystem Verilogテストベンチ・シミュレーション、Palladiumプラットフォームのシミュレーション・アクセラレーションを10倍にまで加速

・Incisive Debug AnalyzerのSystem Verilogの新規サポート・シミュレータのデバッグ環境SimVisionのUVMデバッグ環境の機能強化、プロービング機能のエンハンスによるデータベース・サイズの縮小

・IEEE1647 eモジュールテスト支援機能によるテストベンチ・コードのデバッグ時間の短縮

【SoCインテグレーション機能】

・Incisive Enterprise SimulatorとIncisive Enterprise Verifierによる包括的なx伝播サポート

・ミックスシグナルのシミュレーションのスピードを100倍以上に高速化する、Incisive Digital Mixed SignalオプションでのSystem Verilog IEEE1800-2012準拠のリアル・ナンバー・モデルの新規サポート

Cadenceの「Incisive」のバージョンアップは昨年の5月以来。

今回新たにSystem Verilogをサポートした「Incisive Debug Analyzer」は、「SimVision」の機能をフル活用したデバッグ用の製品である。

※関連ニュース:

※日本ケイデンス・デザイン・システムズ社

2014.01.06

2014年1月3日、米SIA(Semiconductor Industry Association)は、2013年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年11月の世界半導体売上は前年同月比6.8%増、前月比0.6%増の272.4億ドルで、9月、10月に続いてまたもや単月売上記録を更新する好調な結果を残した。単月売上が前年実績を上回るのはこれで7ヶ月連続、前月実績を上回るのは9ヶ月連続となる。

これまで2013年の半導体売上は、Q4で大きく落ち込むが翌2014年Q1からはそのリバウンドで再び上昇という見立てが主流だったが、実際にはQ4に入り10月、11月と連続で単月売上記録を更新する好調ぶりで、2013年の売上累計額は現時点で約2780億ドルとなり、年間売上合計が3000億ドルの大台を超えることがほぼ確実となった。

2013年11月の売上を地域別でみると、北米市場が前月比4.2/前年比18.6%増と大きな成長を見せ、欧州市場もこれに続いた。日本市場も前月比では僅かにプラス、3ヶ月毎のアベレージとしては2.1%のプラス成長を示した。

2013.12.19

2013年12月18日、SystemCからの高位合成ツールを手掛けるForte Design Systemsは、京セラドキュメントソリューションズが同社の高位合成ツール「Cynthesizer」を導入したことを発表した。

発表によると京セラは、プリンタ複合機の画像処理回路の設計用にForteの高位合成ツール「Cynthesizer」を導入。ツール評価の結果、回路面積および速度の面で他のツールよりも優れた合成を実現したことから導入を決定した。まずは機能変更に伴う既存RTLコードの修正など、IPの再利用に「Cynthesizer」を適用していく予定だという。京セラでは、今回の「Cynthesizer」の導入に伴い、これまでのANSI-Cベースの手法からSystemCベースの手法に設計手法を変更したようだ。

2013.12.19

2013年12月17日、Mentor Graphicsは、噂されていた高速RTLフィジカル合成ツールを手掛ける米Oasys Design Systemsの買収を公式に発表した。

本件については下記の記事をご参照下さい。

2013.12.16

2013年12月10日、Synopsysは、スイスのファブレス半導体ベンダAbilis Systems社による、SynopsysのIPを中心としたセキュア・メディア・プロセッサ開発の成功事例を発表した。

発表によるとAbilis Systemsは、同社のIP再配信用の8チャンネル対応放送向けセキュア・メディア・プロセッサ TB100の開発において、Synopsysの下記のIP、ツール、ならびにサービスを導入してシリコン一発完動を達成。開発期間を3ヶ月削減することに成功した。

・DesignWare ARCプロセッサIP

・DesignWare インターフェイスIP

・DesignWare Embedded Memoryのメモリー・テスト&リペア機能

・チップ・インプリメンテーション環境 Lynx Design System

・Synopsys プロフェッショナル・サービス

尚、Abilis Systemsは、豊富な実チップ実績を重視しSynopsys製IPの採用を決定。わずか6週間という短期間で65nmプロセス向けの完全な設計フローの有効性を確認したという。

2013.12.16

2013年12月14日、当該企業による公式な発表はなされていないが、複数の業界メディアがMentor GraphicsによるOasys Design Systemsの買収を報じた。

各メディアの情報によると、MentorによるOasys Design Systemsの買収は事実のようで、比較的安い金額で株式交換を中心に買収が実施された様子。

Oasysは2004年設立のEDAベンチャーで、RTLからの高速なフィジカル合成を実現する「RealTime Designer」を2009年にリリースし、論理合成とレイアウト設計とのイタレーションを大幅に削減する高速かつ大規模デザイン対応のツールとして、Xilinx、TI、Qualcomm、Juniper Networks、NetLogic、STMicroelectronicsなど大手への納入実績を積み上げていた。

Mentorは古くから「Leonardo」、「Precision Synthesis」など論理合成ツールを保有していたが、現在の先端チップ設計向けに耐えうる技術は無く、自社の配置配線ツール「Olympus-SoC」を売る上でも論理合成の欠落は大きなネックとなっていた。そういった意味で、MentorがOasysを買収するメリットは大きく、今回の買収でOasysの技術を手に入れる事が出来れば、論理合成から配置配線に繋がるRTLからの一貫したインプリメント・フローを実現することが可能。更に高位合成ツール「Catapult」を委ねたCalypto Design Systemsと連携すれば、C/C++/SystemCからのインプリメント・フローも実現可能となる。

先端チップのインプリメント・ソリューションに関しては、業界トップのSynopsysに対してARMやTSMCの顧客を中心に巻き返しを図るCadence、新興勢力として存在感を増すATopTechという構図が出来上がりつつあったが、今回のMentorのOasys買収によりまた業界の構図が大きく変わる可能性が出てきた。

2013.12.13

2013年12月11日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、沖情報システムズが同社の検証ソリューションを採用した事を発表した。

発表によると沖情報システムズは、FPGAベンダ最大手のXilinxのプレミアデザインサービスのメンバー企業としてXilinx製FPGA向けのIP製品開発とデザインサービスを行っており、今回同用途向けにAldecの高機能論理シミュレータ「Riviera-PRO」、STARCガイドライン対応のHDLリントツール「ALINT」、FPGA設計向けの低価格論理シミュレータ「Active-HDL」を採用した。

沖情報システムズでは、主に「Riviera-PRO」と「ALINT」をXilinx認証IP製品の開発ツールとして使用し、同IPを使用するユーザー側への配慮として「Active-HDL」を用いたIPの検証環境を用意しているという事で、ユーザーは同環境があれば購入したIPのデザインへの取り込みをスムーズに行えるようになる。FPGAユーザーからの支持を集めているAldecにとっては、同社シミュレータの理想的な展開例と言えるだろう。

沖情報システムズのメディアソリューション統括部 IPプラットフォームBU BU長の山本康雄氏は、「Active-HDLのブロックダイアグラムエディタを使用することで、弊社IPユーザーが迅速にインプリメンテーションと検証を実行できた。」と今回の発表にコメントを寄せている。

2013.12.12

2013年12月9日、グラフィックスIPコアを手掛けるディジタルメディアプロフェッショナル(以下、DMP)は、カナダCogniVue Corporation社との代理店契約ならびに同社IP製品の販売開始について発表した。

発表によると、DMPはCogniVue社と同社製品の日本国内における独占販売代理店契約を締結し、「APEX Image Cognition Processing」という製品名のComputerVision向けIPの販売を開始した。

DMPの説明によると「APEX Image Cognition Processing」は、ComputerVision向けの画像処理に特化したプログラマブルIPコアで、車載カメラ処理、ジェスチャー認識、顔検出/顔認識などのComputerVision画像処理をCPUやDSPよりも100倍以上高速に行なうことが可能。既にFreescaleへのライセンス実績もあり自動車向けASSPとして製品化されているという。

DMPは自社の2D/3DグラフィックスIPコアと合わせて、CogniVue社の「APEX Image Cognition Processing」をComputerVision向けのソリューションとして提供していく予定で、それに伴い、各種IPコアをインテグレーションしてSoCシステム全体を検討・最適化する設計サービスや、ComputerVisionのアルゴリズム開発や最適化を行なうソフトウエアサービスなども提供していくという。

2013.12.06

2013年12月5日、Mentor Graphicsは、同社の組込みソフト開発環境「Sourcery CodeBench」のバージョンアップを発表した。

発表によると「Sourcery CodeBench」の最新バージョンは、コンパイラがGCC 4.8.1にアップデートされ、ランタイム性能が向上し高速コンパイルと高度なデバッグを実現。合わせてグラフィカル解析環境「Sourcery Analyzer」もバージョンアップされた。

「Sourcery Analyzer」は、Mentorが独自に開発しCodeSourcery社から買収した「Sourcery CodeBench」に追加したもので、マルチコア・システムを含めた組込みシステム全体の可視化に利用可能。また、「Sourcery CodeBench」は、MentorのESLツール「Vista」との連携も可能で、今回のバージョンアップにより「Vista」上のARM デュアルコアCortex-A9の仮想プロトタイピングと連携してソフトウェアのパフォーマンスや消費電力などを解析できるようになった。

更に「Sourcery Analyzer」の最新バージョンでは、車載インフォテイメント・システムのオープンソース開発プラットフォームを普及・促進する団体「GENIVI」の提供する、車載インフォテイメントECU向けの解析用標準フォーマット「DLT」のファイルをインポートが可能となり、ECUのトレースデータを解析できるようになったという。

尚、今回のバージョンアップにより、AlteraのCyclone V、Freescaleのi.MX6Q SABRE Lite、TIのOMAP5432 (ARM Cortex-A15)などのデバイスが新たに「Sourcery CodeBench」でサポートされた。

2013.12.06

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2013.12.06

2013年12月5日、Synopsysは、2013会計年度第4四半期(13年8-10月)の売上を報告した。

発表によると、Synopsysの2013会計年度Q4の売上は、前年同時期比約11%増、前期13年Q3比約4.5%増の5億490万ドル。純利益は前年同時期のほぼ倍の5690万ドルだった。(※GAAP基準による会計結果)

Synopsysは10月を会計上の決算月としており、2012年11月から2013年10月までの2013会計年度の売上合計は19億ドル6200万ドルで過去最高を記録。前年比11.7%増という結果だった。既に発表している売上予測によると、2014会計年度は20億ドルの大台を突破する見通しだという。

Synopsysは文字通り右肩上がりの成長を継続しており、売上の前年実績超えは13四半期連続で継続中。昨今は企業買収の件数も減り、北米およびアジア市場での成長とIP製品の拡大が同社の成長を維持しているようだ。

Synopsysは、次期2014会計年度Q1(13年11-12年1月)の売上を4億7500-8500万ドルと予測している。

2013.12.05

2013年12月4日、米SIA(Semiconductor Industry Association)は、2013年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2013年10月の世界半導体売上は前年同月比7.2%増、前月比0.8%増の270.6億ドルで先月に続いて単月売上記録を更新した。単月売上が前年実績を上回るのはこれで6ヶ月連続、前月実績を上回るのは8ヶ月連続となる。

アナリストなど、市場関係者の大半は今年の半導体需要はQ3がピークと見ているが、Q4最初の10月は傾向として年間売上の頂点に位置しており、今年も例年通りの高い実績を残した。つい先日、WSTSが今年の半導体売上額の予測を発表したが、今年は既に売上累計2530億ドルで、最終的には前年比4.4%の成長で史上初の売上3000億ドル超えを達成する見通しとなっている。

2013年9月の売上を地域別でみると、前月比/前年比ともに日本以外の全ての市場でプラス成長、前月比/前年比ともに最も伸びたのは北米市場だった。日本市場は為替レートの影響でドルベースで算出されている前年実績をが大きく下回る格好となっているが、売上の推移としては5-7月よりも8-10月の方が平均売上額が5.8%伸びている。

-thumb-600x409-2884.jpg)