NEWS

2014.08.20

Design Solution Forum 2014実行委員会および一般社団法人日本エレクトロニクスショー協会(JESA)は、2014年10月3日(金)、新横浜国際ホテル(横浜市港北区)において、国内エレクトロニクス技術者が相互に交流可能なコミュニティを形成することを目指し、設計者主体のセミナーイベントとして「創ろう、拡げよう、設計者ネットワーク」をスローガンに掲げ、第1回目の「Design Solution Forum 2014」を開催します。

開催に先立ち、8月20日(水)より、公式Websiteにて聴講予約の受付を開始します。

聴講予約のURLは以下のとおりです。

http://www.dsforum.jp/registration.html

基調講演は「IoT、次世代移動通信5Gの動向とエレクトロニクスの展望」と題し、株式会社NTTドコモ 移動機開発部 無線技術開発担当/担当部長の二方 敏之氏によりまして、ビッグデータ、5G、インフラ、IoTなどをキーワードに次世代のスマートライフの展望について講演していただきます。

セミナーを主体とした本イベントは、「Design」、「Verification」、「Soft&FPGA」、「Solution」のTrackを構成し、デザイン事例と技術トレンドの紹介を中心にセッションを実施いたします。

◆開催概要◆

■名 称: Design Solution

Forum 2014

■会 期: 2014年10月3日(金)

■開場時間 : 午前10時?午後5時20分

■会 場: 新横浜国際ホテル マナーハウス南館

■入 場: 無料(聴講予約制)

■主 催: Design Solution

Forum 2014実行委員会

一般社団法人

日本エレクトロニクスショー協会(JESA)

最新情報および詳細については、公式Websiteをご参照願います。

http://www.dsforum.jp

お問い合わせは、下記までお願いします。

一般社団法人日本エレクトロニクスショー協会

担当:石崎・森

TEL:(03)6212-5231 FAX:(03)6212-5225 E-mail:DSForum2014@jesa.or.jp

2014.08.19

2014年7月18日、みなとみらいのホテルでCadenceのプライベート・セミナー「CDN Live」が開催され、昨年を上回る参加者を集めた。

ここではCDN Liveで紹介された数々のユーザー事例の中から、オリンパスのRTL検証関連の事例講演を紹介する。

講演タイトル:

IESとSpecman、Palladiumを活用したCDV(カバレッジ・ドリブン・ベリフィケーション)高速検証環境のLSI検証適用の事例紹介

講演者:

オリンパス株式会社 光学・電子映像技術本部 SOC技術部 原浩隆

今回のCDNLiveに登壇したオリンパス原氏の所属部署SOC技術部では、社内の各事業部門と画像処理エンジンを共同開発しており、原氏はその中で検証専任として検証環境を見ている立場。

原氏によると同社では各設計ブロックの検証は設計者が担当し、各ブロックを結合したサブシステムの検証から検証専任者が検証に加わり設計品質を確保する開発プロセスを敷いていたが、近年システムの高機能化・大規模化が進みサブシステムが複雑化したことにより検証漏れが頻発。そこでランダム検証(Specman)とエミュレータ(Xtreme)を導入し品質確保と検証工数の削減を図った。

しかし、SpecmanとXtremeの導入により検証品質の向上と検証の高速化は実現できたが、Specmanを用いたCDV検証ではシミュレーション数が桁違いに増加し検証工数が増える形に。設計規模の増大に伴い検証工数が増加するという背景の中でCDV検証の工数が検証工数全体の6割まで占めるようになり、CDV検証の工数圧縮が大きな課題となった。そこでオリンパスではこの課題に取り組むべくエミュレータをCadenceの「Palladium XP」に乗り換え新たな検証環境の構築に着手した。

原氏によるとオリンパスが目指したのはエミュレータをベースとした高速CDV検証環境の構築で、シミュレーション・パターンの削減は考えずCDV検証を如何に高速化するかという視点でテストベンチをなるべくエミュレータに実装する事を考えた。そこで従来使用していた「e言語」はエミュレータに実装出来ないため、テストベンチの作成は「SystemVerilog」へ移行する事にした。また、シミュレーション環境とエミュレーション環境の共通化という点も環境構築の上で重要なポイントであったため、「SystemVerilog」による使用言語の統一を考えた。

しかし、実際に構築したSystemVerilogベースの環境と従来のe言語の環境とで比較したところ、SystemVerilogのランダム生成性能がe言語よりも著しく低い事が分かり、パラメータのランダム生成部分は「e言語」を使用する事にした。

続いてシミュレータとエミュレータの接続手法について検討を行い、まず「SCE-MI」インタフェースを用いた接続を試みたが複数インスタンスの実装で苦労し処理速度も低下する結果に。そこでSystemVerilogの「DPI-C」を用いたバーチャル・インタフェース(VIF)で環境を構築したところ「SCE-MI」よりも処理速度が優れていたため、VIFベースの環境構築を選択した。また、「DPI-C」では複数のデータ転送方法が用意されているため、各転送方法を評価し転送するデータサイズに応じて転送方法を切り替える環境を構築した。

シミュレータとエミュレータのCo-Sim環境においては、コンパイル時間が圧倒的に大きいため実行パターンを連結する事でコンパイル回数を減らし高速化を実現する形を取った。

最終的に構築したシミュレータとエミュレータのCo-Sim環境は、テストベンチをエミュレータに実装する事でシミュレータとエミュレータのやり取りを減らし、接続方法を工夫した事でシミュレータ単体よりも約50倍ほど高速なCDV検証(ブロックレベル)を実現した。

原氏は今回の取り組みにおいて苦労した点として、「Palladium XP」の立ち上げとCo-Sim環境のインタフェース部のモデル構築の2点を指摘していた。

2014.08.11

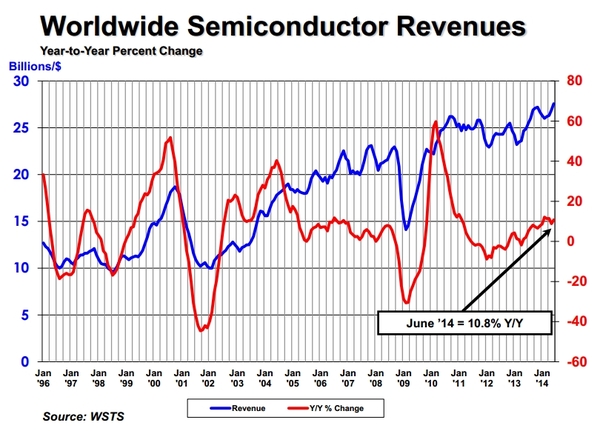

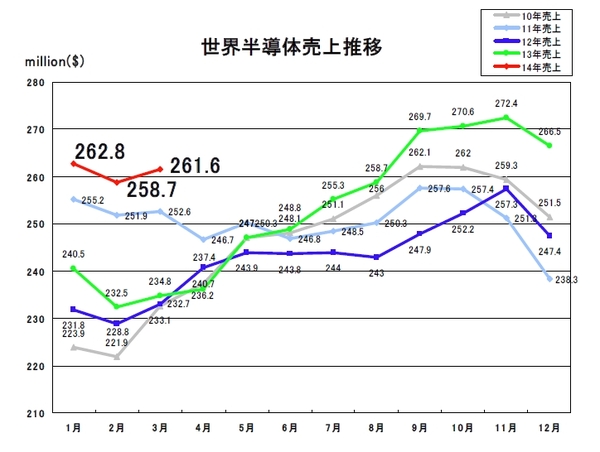

2014年8月4日、米SIA(Semiconductor Industry Association)は、2014年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年6月の世界半導体売上は前年同月比10.8%増、前月比2.6%増の275.7億ドルで6月の売上としては過去最高を記録した。

世界の半導体市場はスマホ/タブレット需要をはじめネットワーク関連、コンスーマ、自動車などあらゆる分野で好調を維持しており今年に入ってから全ての月で単月売上記録を更新中。この記録更新は昨年9月から10ヶ月継続しており、単月売上が前年実績を上回るのはこれで14ヶ月連続となる。

今年の上半期(1-6月)の世界半導体売上累計は前年比11.1%増の1590億ドルとなっており、6月に発表されたWSTS(World Semiconductor Trade Statistics)の2014年春季半導体市場予測(2014年は6.5%成長)を上回るハイペースで成長を続けている。

2014年6月の売上を地域別に見ると全ての地域で売上前年比増を達成。更に先月5月に続いて全ての地域で売上が前月実績を上回った。長らく不調だった日本市場もようやく世界水準に届く成長を見せはじめており、今後下半期への成長継続に期待がかかる。

2014.08.11

2014年8月4日、高位合成ツールをはじめフォーマル検証ツール、ローパワー設計ツールを手掛けるCalypto Design Systemsは、オリンパスが同社の高位合成ツール「Catapult」を採用した事を発表した。

発表によると今回Calyptoの高位合成ツール「Catapult」を採用したのはオリンパスのSOC技術部。同部署は社内各事業部で開発する製品のSoC開発に携わっている。

オリンパスのSOC技術部では、以前Bluespec社のSystemVerilogベースのESLツールを導入しその効果を事例発表していたりしたが(関連ニュース)、今回の発表によると幾つかの高位合成ツールを評価した結果「Catapult」の導入を決定。その理由として実績とC言語サポート、検証メソドロジを挙げている。

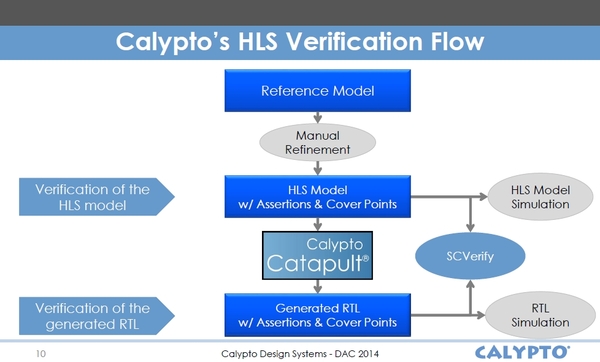

検証メソドロジに関してCalyptoは等価性検証ツール「SLEC」を提供しており、同ツールを用いることで高位合成前後の機能等価性を検証する事が可能。その他に「Catapulut」にはシミュレーション・ベースの検証環境「SCVerify」が備えられており、合成モデル(C++)とそのテストベンチから、自動的に合成されたRTLの検証環境を構築し、シミュレーションを実行することも可能となっている。

今回の「Catapult」採用に伴い、オリンパスがどのような検証環境を構築しているのかは定かでは無いが、来る8/29開催の「Calypto Users Forum 2014」にて、オリンパスが「Catapult」を画像処理IPの開発に適用した事例の講演が行われる予定となっており詳細が聞けるかもしれない。

2014.07.29

2014年7月24日、Alteraは2014会計年度第2四半期(14年4-6月)の売上を報告した。

発表によるとAlteraの2014年Q2(14年4-6月)売上は、前年比約17%、前期Q1比約7%増の4億9150万ドル、営業利益は前年比約8.9%増の1億4656万ドルだった。このQ2の売上実績は前四半期の売上報告時の予測を上回るもので、前年比2ケタ成長はQ1に続いて2四半期連続、売上が前四半期を上回るのは5四半期連続となる。製品別売上を見ると最新の20nm FPGA「Arria 10」を含む新製品カテゴリの売上が前Q1よりも15%も伸びており、売上全体を押し上げているのが分かる。ちなみに売上集計に20nm FPGA「Arria 10」の名が登場するのは今期が初めて。更に次世代のIntelプロセスを用いた14nm FPGAについては、既に先行顧客が現行製品比2倍のパフォーマンスを達成したと報じられている。

Alteraの2014年Q2の売上を地域別で見ると、北米と欧州の売上比率が上がり日本は落ちた。分野別ではテレコム/ワイヤレス分野がQ1比9%増、前年比28%増と大きく成長しており全売上に対する割合を46%まで伸ばしている。

Alteraは次期2014年Q3(7-9月)の売上を2014年Q2の-2%から+2%と幅のある予測をしている。

2014.07.24

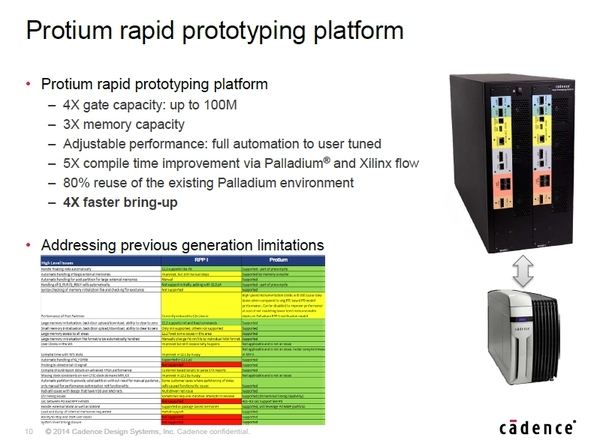

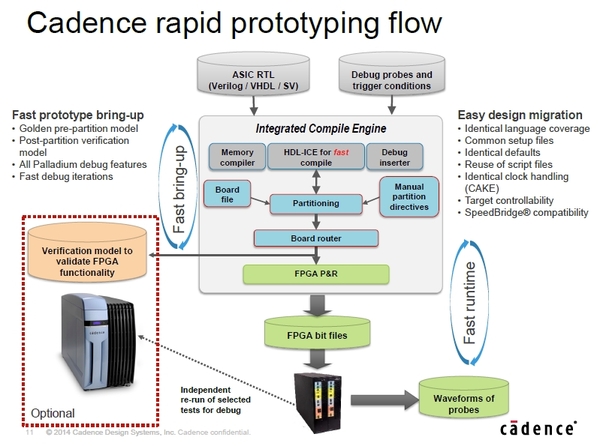

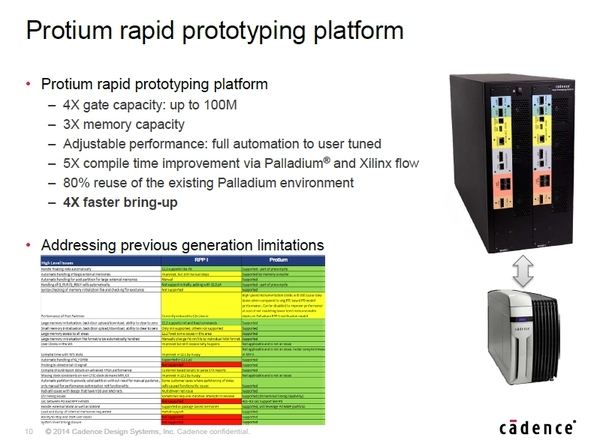

2014年7月18日、Cadenceは新型のラピッド・プロトタイピング・システム「Protium」を発表した。

発表当日みなとみらいで開催されたCadenceのプライベート・セミナー「CDNLive Japan 2014」にて、新製品「Protium」について話を聞いた。

CadenceがFPGAベースのプロトタイピング・システムを初めて発表したのは約2年前、「Cadence Rapid Prototyping Platform(RPP)」と命名されたその製品は某ボード・メーカーの製品を利用したもので、AlteraのFPGA「Stratix-4」をベースとしたものだった。

今回発表された「Protium」は、Xilinxの28nmFPGA「Virtex-7 2000T」をベースとしたもので、Cadenceのエミュレータ「Palladium」とのフロー互換など製品としてのコンセプトは前身の「RPP」と同じだが、その中身は全く異なる製品と言える。

まずFPGAが「Virtex-7 2000T」に置き換えられた事でそのデザイン容量は「RPP」の4倍に当たる最大1億ゲートへと拡張された。「Protium」のベース・ボードは、「Virtex-7 2000T」を2個搭載するものと4個搭載するものの2種類があり、最大8個のFPGAで1億ゲートに対応という計算だ。更にオン・ボード・メモリは「RPP」の3倍の最大64GBとなった。

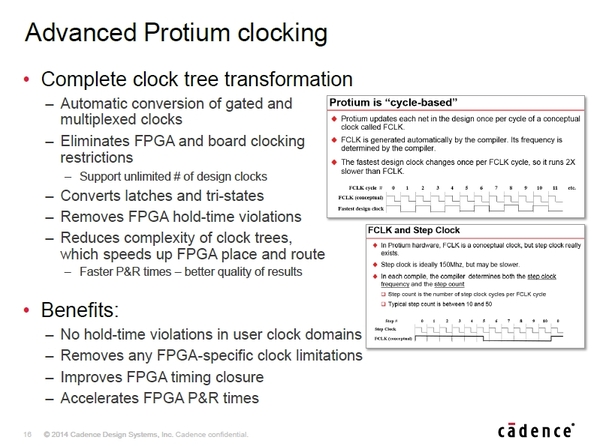

「Protium」の最大の特徴は、プロトタイピング・システムとしてのセット・アップ時間の短さで、デザインのコンパイル時間が改善され従来比5倍の速さでRTLを合成できるようになった。具体的には7000万ゲート規模のデザインを約1時間でコンパイル可能で、Cadenceは競合製品と比較してセット・アップ時間を70%短縮できるとしている。

コンパイルの高速化はエミュレータ「Palladium」の環境を再利用する事で実現されているという事だが、コンパイラ内部の各種処理でも様々な工夫が施されており、それらがセット・アップ時間の短縮に大きく貢献している。例えばFPGA実装向けにクロック・ツリーの自動再構成機能があり、非同期のユーザー・クロックのふるまいを継承しながらデザインを一つのクロック・サイクル・ベースにする事が可能。一本の高速クロックで全てのクロックを同期するこの手法により、ホールド・タイムの違反やクロック数の制限を無くす事ができ、タイミング収束や配置配線処理も加速可能となる。また、コンパイラにはスタティック・タイミング解析機能も備えられており、これもセット・アップ時間の短縮に貢献する。

更にFPGAの配置配線前にデザインを検証するためのソリューションとして、「Palladium」向けの検証モデルを生成する機能がオプションで用意されており、これによりデザインをFPGAに実装する前に数時間でデバッグできる。

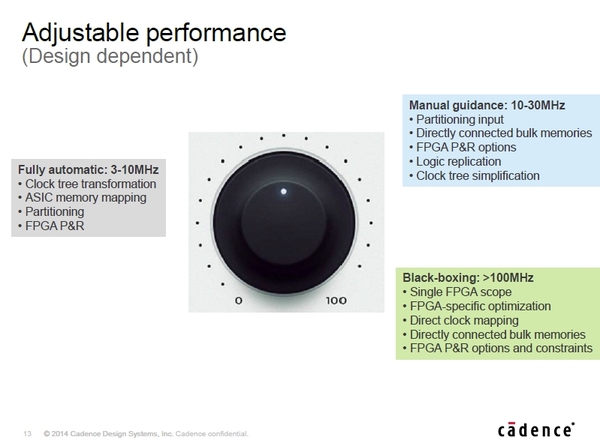

尚、プロトタイピング・システムのセット・アップをツールに任せて全自動で行うと最も短時間で数日から数週間で環境を構築できるが、その場合のパフォーマンスは3M-10MHz程度。デザインの分割など人手を駆使して様々な最適化を図れば10-30Mhzのパフォーマンスを実現可能との事。デザインの一部のブロックを単一のFPGAにカプセル化して実装する「Black-Boxing」という手法では100Mhz近い優れた性能を実現することも可能で、PCI-ExpressやUSBなどのアプリケーションが「Black-Boxing」に適しているとの話だった。

ソフトウェア開発のニーズとFPGAの進化により、FPGAベースのプロトタイピング・システムの市場には様々な製品が乱立しており激しいシェア争いを繰り広げているが、今回「Protium」によって「Virtex-7 2000T」ベースという意味でようやくCadenceは他社製品と同一の土俵に立った事になる。業界最新のプロトタイピング・システムとしての「Protium」のポテンシャルとFPGAベースのプロトタイピング・システムはエミュレータとの併用が多いという事を考えると、後発のCadenceにもまだまだチャンスはあると言えるだろう。

※ケイデンス・デザイン・システムズ社

2014.07.23

2014年7月16日、Cadenceは新型の寄生抽出ツール「Quantus QRC Extraction」を発表した。

発表間もない「Quantus QRC Extraction」について、7/18にみなとみらいで開催されたCadenceのプライベート・セミナー「CDNLive Japan 2014」で早速話を聞いた。

今回発表された新製品「Quantus QRC Extraction」は、既存製品の「QRC Extraction」をベースに改良された後継製品でCadence曰く業界随一の精度とパフォーマンス(速度)を誇る。

精度についてはTSMCが既に16nm FinFETプロセスにて「Quantus QRC Extraction」を認証しており、TSMCが顧客に公開しているレポートによると「Quantus QRC Extraction」を用いた寄生抽出結果が最も精度が高いという事だ。

パフォーマンス(速度)に関しては、市販の競合製品と比較してCPU単体での処理で平均5倍高速に。これは最新のアルゴリズムを実装した事によるもので、更に「Massively Parallel」と表現されるスケーラブルな複数CPUへの並列分散処理機能により、大規模デザインを高速に処理する事もできる。CPU数には制限がなく100個のCPUを用いた並列分散処理も可能だ。

また、同社のインプリメント環境「Encounter」やSTA「Tempus」と連動したインクリメンタルな寄生抽出も可能で、そのパフォーマンスは従来比およそ3倍の高速化を実現しているという。ちなみに同インクリメンタル抽出機能は既存製品から継承される機能で、フルチップ抽出の結果と差分の生じない精度の高さもうりの一つでECO時に重宝されているという。

またパフォーマンスに関しては、「Quantus QRC Extraction」に内蔵するフィールド・ソルバーも刷新されており、新たなランダム・ウォーク・フィールド・ソルバー「Quantus FS」は、従来比20倍の高速化を実現していると聞いた。言うまでも無いが同ソルバーは精度の高さにも大きく貢献している。

更に特筆すべきは寄生抽出結果を付加したネットリストのサイズで、「Quantus QRC Extraction」は従来比約半分のサイズにネットリストを小さくする事が可能。これは寄生抽出と情報付加の両面から実現している技術で、シミュレーション速度を2.5倍高速化する効果をもたらすという。

ツールの運用面では、「Quantus QRC Extraction」は既存製品の「QRC Extraction」の完全互換を実現しており、既存資産をそのまま「Quantus QRC Extraction」で利用可能。セットアップの手順なども基本的に同じとなる。

また、先に述べた通りデジタル・インプリメント環境「Encounter」やSTA「Tempus」と統合利用可能なほか、アナログ環境「Virtuoso」とも密接に連携可能で、例えば「Virtuoso」のGUI上の「Extracted view」を用いて回路パフォーマンスのデバッグなどもできる。精度と速度に合わせてアナログ/カスタム設計のデファクト環境「Virtuoso」との連携はCadenceならではの強みの一つと言える。

※画像は全てCadence提供のデータ

更に新しい「Quantus QRC Extraction」では、オートモーティブ・アプリケーション向けの新機能として、サブストレート・ノイズ解析やインダクタンス抽出、パワーMOS向け抽出などが用意されており、Cadence本社のプロダクト・マーケティング・マネージャーHitendra Divecha氏は、日本市場を意識してかパワーデバイスや自動車向けデザインにも利用できる事を強くアピールしていた。

ちなみに今回発表された「Quantus QRC Extraction」は、昨年リリースされたSTA「Tempus」、電力解析ツール「Voltus」と同じ事業部門の製品でCadenceのサインオフ・ソリューションの一角をなすもの。昨年から立て続けに刷新されたCadenceのサイオンオフ・ツールに共通するのは「高精度かつハイ・パフォーマンス」という点で、既存に強力な競合製品があるにも関わらず真っ向から市場に切り込んだ「Tempus」と「Voltus」は既に多くの大手顧客を獲得し一定の成功を収めている。「Quantus QRC Extraction」に関しては既にリコーが採用し、デザイン・クロージャーの寄生抽出時間を半分に短縮する事に成功したと報じられているが(Cadenceプレスリリース文)、Cadenceの放ったサインオフ・ツール第三の矢がどこまでシェアを広げるか、これからの事例発表が楽しみだ。

2014.07.23

2014年7月22日、Xilinxは2015会計年度第1四半期(2014年4-6月)決算を報告した。

Xilinxの2015会計年度Q1の売上は、前年同時期比6%増、前期Q4比1%減の6億1260万ドル。営業利益は前年比9%増の2億650万ドルだった。(※GAAP基準による会計結果)

前Q4売上報告時ではQ1の売上はQ4売上と同等もしくはそれ以上と予測していたが、予測に反して売上が落ちた。

同社のCEOのコメントによると、今四半期は防衛、無線関連の売上が予想を下回ったとの事。実際に製品分野別の売上では、航空・防衛分野の売上が全体の31%に留まっている。(昨年同時期は37%、前Q4は34%だった)

XilinxのQ1売上を地域別でみると、前Q4とほぼ同様でアジア地域の売上が全売上の43%を占めた。日本市場の売上は若干増えた。製品別売上では、28nm製品を含む主力の新製品カテゴリ(Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6)の売上が更に増え、売上全体に占める割合は45%にまで上昇した。

Xilinxは、次期2015年Q2(14年7-9月)の売上を今期実績の0%-4%減と予測をしている。

2014.07.23

2014年7月22日、ARMは、2014会計年度第2四半期(2014年4-6月)の売上を報告した。

ARMの2014年Q2の売上は、前年比約17%増、前期比約1.4%増の3億960万ドルで前Q1に続いて四半期売上記録を更新した。税引き前の純利益は前年比約9%増の約1億6100万ドルだった。

ARMの上半期の売上合計は前年比16%増の6億1480万ドル、純利益の合計は前年比9%増の2億6570万ドルとなっている。このままのペースで行くと2014年の売上合計は13億ドルに手が届きそうだ。

Q2売上の内訳を見ると、ライセンスの売上がQ1を上回る前年比約42%増と大きく伸び1億4610万ドル、ロイヤリティの売上は昨年と同レベルだった。ライセンスの売上の大半を占めるプロセッサ・ライセンスはこのQ2で41件の契約を獲得。うち7件は最新のARMv8-Aアーキテクチャ・ベースのプロセッサで、同v8アーキテクチャ製品の累計ライセンス数は50件、ARMの全ての製品の累計ライセンス数は1100件を超えた。ライセンス内訳は下記の表の通りでフィジカルIPの契約としては16/14nmプロセス向けのフィジカルIPも含まれているようだ。

※画像はARM発表資料より抜粋

2014年Q2で出荷されたARM搭載チップの総数は約27億個で前年比11%増。前Q1と比較すると若干減った。その内訳は以下の表の通りで1年前は前出荷数の52%を占めていたモバイル分野の出荷数が42%まで落ちた。これはARMコアの出荷数が伸びる中で徐々にモバイル以外の出荷が増えている事を表している。製品別出荷数としてCortex-Mシリーズの出荷が増えているのもモバイル以外の組込み分野の需要の影響と言えよう。

※画像はARM発表資料より抜粋

2014.07.22

2014年7月21日、Cadenceは、2014会計年度第2四半期(2014年4-6月)の売上を報告した。

Cadenceの2014年Q2(4-6月)売上は、前年同時期比約4.7%増、前期Q1(14年1-3月)とほぼ同額の3億7900万ドル。純利益は前年の倍以上の2300万ドルだった。(※GAAP基準による会計結果)

これまで右肩上がりで四半期売上を伸ばし続けてきたCadenceだが、成長カーブは徐々に緩やかになり遂にこのQ2で売上額が横這いとなった。売上額が四半期ベースで前期を上回らなかったのは2009年Q1以来5年ぶりの事なる。

とは言え同社の売上はこのQ2で18四半期連続で前年同時期比増を記録しており、来期Q3はQ2実績を上回る3億9000万?4億ドルの売上を予測している。

CadenceはこのQ2にフォーマル検証ツールのJasperの買収を完了したほか、7月に寄生抽出ツール、FPGAベースのプロトタイピング・システムと新製品2品種を投入しており、売上を伸ばす材料は十分にある。

2014.07.17

2014年7月17日、Mentor Graphicsは、ヘテロジニアス・マルチ・コアSoCに対応可能な業界初の組込みソフト開発ソリューションを発表した。

MentorはEDAベンダの中では最も広範囲に組込みソフト開発に対するソリューションを展開している企業と言えるが、今回発表したソリューションは既存の各ソリューションをベースにそれらを結びつけ相互運用するための独自の機能を追加したもので、ヘテロジニアス・アーキテクチャの次世代SoC向けのソフトウェア開発をターゲットにしている。

異なるアーキテクチャの複数のコアで構成されるヘテロジニアス・マルチ・コアSoCでは、Linux、RTOS、Hypervisorなど様々なOSやアプリケーションが稼働することがあり、それらをシステムとして統合しSoC化するには、個々のコアの実装だけでなく各コア上のOSの協調やコア間の通信なども考慮した複雑なシステム開発が必要となる。

今回Mentorが発表したソリューションは、同社の「Mentor® Embedded Linux」、「Nucleus® RTOS」、「Mentor® Embedded Hypervisor」の利用を前提としたヘテロジニアス・マルチ・コアSoC向けの開発ソリューションで、その開発環境は同社の組込みソフト開発環境「Sourcery™ CodeBench」がベースとなる。

ソリューションのキーとなるのは、Linux上のアプリから他のプロセッサやマイクロ・コントローラを制御する「リモートプロセッサフレームワーク(remoteproc)」機能や、サブシステム間やプロセッサ間通信を実現するための仮想インタフェース(VirtIO)、rpmsg、マルチコア通信API(MCAPI)、異なるOS間の情報のやり取りを視覚化するデバッグおよび性能解析機能などで、Mentorが開発したこれら機能によって様々な異種プロセッサ上に複数のOSとアプリケーションをコンフィギュレーションし搭載する事が可能に。複数のOSを効率的に同時に起動できるヘテロジニアス・マルチ・コア・システムが開発できるようになる。

尚、Mentorによると同ソリューションはTI社のOMAP5開発ボードを用いて実証済で、各種SoCベンダと様々な形で協業を進行中との事。顧客のニーズによってはMentor製OS以外の実装などにも対応可能という話だ。

今回のソリューションに対するMentorのメッセージのポイントは、単に新たな組込み開発ソリューションを用意したという事ではなく、既存の複数のシステムやチップをヘテロジニアス・マルチ・コアSoCとして機能集約する事でより高機能/高性能なシステムを実現できるため、そのために必要な開発環境を用意したというところにあり、例えば複数ECUの統合により低コスト化を狙う自動車業界などもそのメッセージの視野に入っているようだ。

更に付け加えると、同ソリューションを提供できるのは、組込みOS、RTOS、Hypervisor、そして組込み開発環境と多様な組込み開発ソリューションを包括的に用意しているMentorのみ。というところだ。

2014.07.17

2014年7月16日、米EDA Consortiumは、2014年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

EDACの発表によると、2014年Q1の世界のEDA売上総額は、前年比4.6%増、前Q4比7.6%減の17億4610万ドルで、Q1の売上記録として過去最高を達成。四半期の売上記録が前年同時期を上回るのはこれで17四半期連続となる。

2014年Q1の売上を製品分野別に見ると、ICPhysicalDesign&Verification分野とサービス分野以外は各分野で前年比増を達成。IP分野は前年比10.2%増と大きく伸び同分野としては初めて売上5億ドルの大台を超えた。

2014年Q1の売上を地域別に見ると、日本市場以外は全て前年比増を達成しており、アジアは二桁成長。半導体の売上が好調な欧州市場は北米を上回る成長を見せた。日本市場は前年比19.3%と大きく売上を落とし遂に売上全体に占める割合が12%まで下落。もはや為替レートの影響とはいえない状況にあり、半導体業界の衰退がEDAの売上にも色濃く現れている。

2014年Q1時点でのEDA業界の従業員数は前年比3.7%増、前期Q4比1.9%増の30440人で過去最高を記録。従業員数が3万人を超えるのは業界史上初となる。

2014Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億3860万ドル 6.6%Up

■IC Physical Design & Verification分野 3億3190万ドル 2.4%Down

■IP分野 5億1810万ドル 10.2%Up

■サービス分野 9770万ドル 4.1%Down

■PCB/MCM分野 1億5970万ドル 1.6%Up

2014年Q1地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億6070万ドル 7.1%Up

■ヨーロッパ 2億9680万ドル 7.4%Up

■日本 2億970万ドル 19.3%Down

■アジアその他地域 4億7890万ドル 13.5%Up

※EDAC(EDA Consortium)

2014.07.15

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

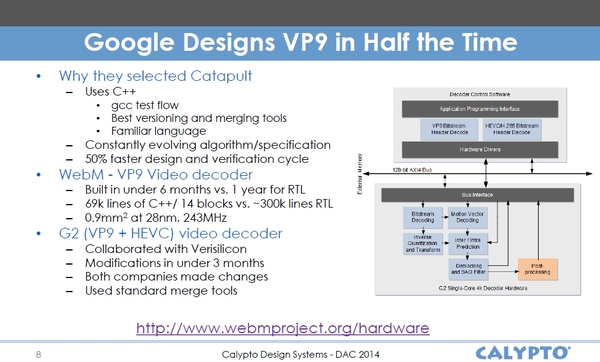

Calyptoのブースでは、同社製品の3本柱であるPower最適化ツール「PowerPro」、高位合成ツール「Catapult」、シーケンシャル等価性検証ツール「SLEC」を展示。「Catapult」に関してはブース内でGoogleとCienaによる事例のプレゼンが行われていた。

ここでは話題となっていたGoogleによる高位合成ツール「Catapult」の適用事例を中心にCalyptoの展示内容をを紹介する。

Googleと高位合成、一見結びつかない話と思いつつその詳細をCalyptoのマーケティングVP Mark Milligan氏に聞いたところ、Googleは誰もが無料で利用できるオープン・ソースでロイヤリティ・フリーなビデオ・フォーマット「WebM」を推進する「WebM」プロジェクトを主導しており、自ら開発したそのコーデック技術「VP9」のデコーダ開発においてCalyptoの高位合成ツール「Catapult」を採用した。

「Catapult」の採用理由としては、その合成品質やC++入力に対応している点などが挙げられるが、面白いのは「WebM」プロジェクトの一貫として「VP9」を普及させるために、そのデコーダ回路のRTLと合わせて「Catapult」向けの合成用のC++ソースコードと合成スクリプトを無償でパートナーに公開したという点。実際にGoogleのパートナー各社はこれを利用し10種以上のチップをテープアウトしているという話だ。

ちなみにその先陣を切ったのはVeriSilicon社で、同社はHEVC(H.265)とVP9双方に対応した「Hantro G2ビデオデコーダーIP」を約1年前に開発。同IPの開発はGoogleから無償提供されたCatapult向けのC++記述と合成スクリプト、そして自社のIPを元に進められ、わずか3か月で設計を済ませたという。

Googleが採用したツールという事で「Catapult」の評価は高まると思われるが、それ以上にGoogleのパートナー各社が「Catapult」を利用するとなるとCalyptoにとってビジネス的なメリットも大きいだろう。

ブース内で行われていたもう一つのCiena社の事例は詳細は聞けなかったが、同社のネットワーク向けのコヒーレント光プロセッサー「WaveLogic 3」のDSPブロックを「Catapult」で設計したという事例で、ビット・レート100Gbit/s以上という目標を達成。設計及び検証期間の短縮にも繋がったという。

尚、 「Catapult」のアップデートとしては、新たにアサーションやカバー・ポイントをデザインと共に合成されるRTLに挿入する機能が備えられた。これにより、合成モデル (C++、SystemC)をシミュレーションで検証する際に、アサーションによる検証や、カバレッジを取るだけではなく、それらをRTLでの検証にも活用できるようになり、特に他のブロックと結合した際の検証で検証効率を上げることが出来るようになった。

「Catapulut」にはシミュレーション・ベースの検証環境「SCVerify」が備えられており、合成モデル(C++)とそのテストベンチから、自動的に合成されたRTLの検証環境を構築し、シミュレーションを実行することが可能である。

もう一つの同社の主力製品「PowerPro」に関しては、新機能として「Physical-aware power analysis」という解析機能が追加された。これは文字通りフィジカル・ベースのPower解析を行うもので、RTLの合成結果をバック・アノテーションしてPower解析を実行。これによりパワー解析精度を向上できるという。ちなみにRTLでのパワー・リダクションに関して「PowerPro」はここ7-8年他社製品に負けたことがないと聞いたが、新機能「Physical-aware power analysis」を用いれば更に質の高いローパワー化が期待できるだろう。

※画像は全てCalypto提供のデータ

※カリプト・デザイン・システムズ株式会社

2014.07.15

2014年7月14日、Mentor Graphicsは、先端の高性能メモリ向けのエミュレーション・ソリューションを発表した。

発表されたソリューションはMentorのエミュレータ「Veloce」をベースとしたもので、ターゲットとなるのはハイブリッド・メモリ・キューブ(HMC)、LPDDR4、eMMC 5.0に準拠した高性能メモリ製品。今回Mentorはこれらメモリ製品を「Veloce 2」上で検証するためのデバイス・モデルを用意した。同モデルを利用すれば実シリコンが無い状態でSoC上のメモリ・デバイスを検証することが可能となる。

ちなみに、Mentorのエミュレータ「Veloce」シリーズでは、「iSolve」を用いたイン・サーキット・エミュレーション、「VirtuaLab」を用いたソフトウェア・モデルを用いたエミュレーション、トランザクション・ベースのアクセラレーションが可能だが、全てのアプローチにおいて今回開発された各種高性能モメリ・デバイス・モデルが利用できるとの事。また「Veloce」と連携するシミュレータ「Questa」においてもこれらモデルを利用可能だという。

エミュレータを利用した検証手法は、大規模かつ複雑な上に早期市場投入を迫られる先端チップの開発において無くてはならないものとなっており近年ニーズが急上昇。その売上平均成長率は2010年以降30%近くとなっている。Mentorはその波に乗り「Veloce」の実績を大きく伸ばし続けているが、Mentorのエミュレータが選ばれる理由の一つには豊富な周辺環境があり、各種標準インタフェースや今回のメモリ・デバイス・モデルなど、誰もが当たり前に必要とするものはエミュレーション環境として予め用意するというアプローチが顧客に受けているようだ。

2014.07.14

2014年7月11日、設計および検証サービスならびに自社開発のIPとEDAツールを手掛ける国内のベンチャーCMエンジニアリングは、最新の自社製品として機能検証向けのEDAツール「SpecInsight-ACE」の販売を発表した。

アサーションの生成はタイミング・チャートから生成する形となっており、「SpecInsight-ACE」にはGUI上で波形ベースでアサーションを描くことができる「タイミングチャートエディタ」が用意されている。同エディタはアサーション生成を容易化するために備えられるものだが、タイミング・チャートをGUIベース(波形ベース)で直感的に作成できるという意味で仕様書の整備や改善にも役立つという。

※画像はCMエンジニアリング提供のデータ

尚、CMエンジニアリングは今年の秋にもう一つの「SpecInsight」ファミリ製品として、デザインの仕様書情報からテストベンチを自動生成する新製品のリリースを予定しているとの事。既存の「SpecInsight」と合わせてRTL設計およびRTL検証に利用できるポイント・ツールを更に拡充していく計画だ。

「SpecInsight-ACE」は既に出荷中で価格は39.8万円から、出力するアサーション・コードはCadence,Mentor,Synopsysの各シミュレータで利用可能。

※CMエンジニアリング株式会社

2014.07.11

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

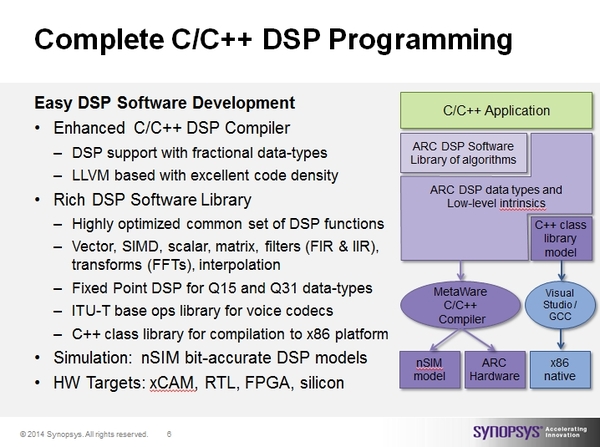

Synopsysは例年通り今回のDACに合わせ幾つかの新ソリューションを発表していた。ここではSynopsysがDAC直前に発表した新型の超ローパワーDSP「DesignWare ARC EM DSP Family」について取り上げる。

「ARC EM DSP Family」は、超低消費電力が求められる常時動作を前提とした組込みDSPアプリケーション向けに開発されたDSPコアで、IoT機器の音声起動システムなどが一つのターゲットとされている。製品としては「ARC EM5D」と「ARC EM7D」の2種類の製品が用意されており、その最大の特徴はSmall&LowPowerだ。「ARC EM5D」は主要な40nm LPプロセスで実装した場合の最小面積は0.03mm角と非常に小さく、動作時の消費電力は僅か7μW/MHz。TSMC 28nm HPMプロセスで実装した場合、消費電力は4μW/MHzまで抑えられるとのことでまさに超ローパワーを実現する。

一方、性能面でも優れたパフォーマンスを発揮し、「ARC EM7D」は動作周波数は最大530MHz、演算能力は最大938DMIPSを実現。「ARC EM5D/EM7D」を利用すれば既存のDSPアプリケーションのパフォーマンスを維持しながら小型化、ローパワー化が可能で両コアでイタレーションすることで組込みDSPアプリ実装の最適解を見つけることが出来るという。

「ARC EM5D/EM7D」は、ARCプロセッサ・ファミリ共通のARCv2 Instruction Set Architecture(ISA)に信号処理アルゴリズムを高速化するためのDSP命令セットを100以上追加しており、ユーザー独自の命令定義も可能。DSP処理に特化したコンフィギュアビリティの高いアーキテクチャで性能と消費電力の両面で最適化されており、オプションで浮動小数点ユニットやメモリ保護ユニットも用意されている。

「ARC EM5D/EM7D」向けのソフトウェアは専用のツール・キット「MetaWare」を用いてC言語で開発することができ、豊富なソフトウェア・ライブラリによりビギナーでも容易にプログラミングできると同時に上級者による高度な性能の追求も可能。x86プラットフォーム向けのC++クラス・ライブラリも用意されている。また、高速シミュレーション用の命令精度のシミュレーション・モデル「nSIM」を出力できるほか、ハードとしての性能解析にはISS「xCAM」をコンフィギュレーションに応じて出力できる。

ARCプロセッサ製品のプロダクト・マーケティング・マネージャーPaul Garden氏によると、「ARC EM5D/EM7D」はIoTの中心となる各種センサーや、オーディオ/音声処理を行う常時動作機器に最適なDSPソリューションで競合する製品は無く、市場における最も小さく最も低消費電力なDSPコアであるとの事。既に各種組込みシステムの市場でARCコアは年間約15億ユニットの出荷実績を誇っているが、今後その市場は更に拡大する見通しで、「ARC EM5D/EM7D」はIoTの世界で無くてはならない製品になるだろうという事だった。

※日本シノプシス合同会社

2014.07.09

2014年7月9日、Mentor Graphicsは、車載エレクトロニクス・システムの各種リファレンス・プラットフォームを提供する独XS Embeddedを買収したことを発表した。

XS Embeddedは、車載エレクトロニクス・システム向けにソフトおよびハードから成る各種リファレンス・プラットフォームを提供している会社で、自動車向けのビデオ/オーディオ、各種グラフィック・システムのリファレンス・プラットフォームの他に、Linuxベースシステムのプロファイラや、独自の組込みOS、ボード開発サービス等を提供している。

Mentorは同社を買収することで既にある自動車向けのソリューションを拡充。既存ソリューションとXS Embeddedのソリューションの組み合わせにより、車載システムの量産開始までの時間を短縮できるとしている。

2014.07.08

2014年7月7日、米SIA(Semiconductor Industry Association)は、2014年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年5月の世界半導体売上は前年同月比8.8%増、前月比2.0%増の268.6億ドルで5月の売上としては過去最高を記録した。

5月の売上は前年比ではひと桁増に落ち着いたが、依然半導体市場の好況は継続しており、単月の売上記録の更新は昨年9月以来9ヶ月連続、単月売上が前年実績を上回るのはこれで13ヶ月連続となる。

2014年5月の売上を地域別に見ると、先月同様に日本市場を含めた全ての地域で売上前年比増を達成。更に全ての地域で売上が前月実績を上回っており、全ての地域で前年比/前月比共に売上増を記録するのは2010年8月以来初めてのことになる。地域別では北米、アジアが安定的に好調を維持しているが、ここのところ欧州の売上も回復してきている。

2014.07.02

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

e,SystemVerilog対応の多言語IDE「DVT」を手掛けるルーマニアのEDAベンダAMIQは、新製品となるドキュメント生成ツール「Specador」を展示していた。

「Specador」は、ソースコード上に埋め込まれたコメントからHTMLドキュメントを自動生成するツールで、同ツールを利用することでソースコードからクラス継承ツリー、デザイン階層構造、モジュール・ダイアグラムなどを容易に入手できる。生成されたドキュメントはソースコードと同期可能で変更を反映しコードのリビジョン管理も可能。

「Specador」はデザイナーおよび検証エンジニアをターゲットとしたものだが、使い方としてはIPのパッケージに用いてIPの情報をIP利用者に提供するという形もあるという。

AMIQ製品は株式会社シンコムが日本代理店として提供している。

2014.07.02

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

インドのIPベンダSmartDV社は今回が初のDAC出展。同社のブースでは主力の検証IPを中心に展示していた。

SmartDVはASIC設計者が立ち上げたIPベンダで非常に広範囲な検証IPの品揃えがウリ。聞くところによると検証IPは70種以上のプロトコルをサポートしており、品揃えは自称業界トップとの事。他社の検証IPよりも2-4倍高速でその価格は概ね他社製品よりも3割は安いという。

既にワールドワイドで60社を超える顧客を抱えているが日本には販売ルートが無く未だ顧客はいない。検証IPと合わせて各種メモリ・モデルやデザインIPも提供しており、主力の検証IPはUVM,VMM,OVM,Vera,SystemVerilog,Verilog,e,SystemCをサポートしていると聞いた。

2014.07.02

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

RocketickのブースではDAC前にアナウンスした新製品「RocketSim-CPU」を展示していた。

「RocketSim-CPU」は、同社のGPUベースのVerilogシミュレーション高速化ツール「RocketSim」と同様にVerilogシミュレーションを高速化するツールで、Cadence,Mentor,Synopsysの提供する市販シミュレーターをサポート。一般的なマルチコアCPUサーバーを併用してシミュレーションを5-10倍高速化する。

「RocketSim」の場合はNVIDIAのGPUベースのソリューションのため、ユーザーがGPUを搭載したボードを用意する必要があるが、「RocketSim-CPU」は一般的なマルチコアCPUサーバーがあればシミュレーションを高速化できるので環境を構築する上での敷居が低いという。

ちなみに「RocketSim」と「RocketSim-CPU」は同じ定価。日本国内に代理店は無くRocketickが直接製品を供給する形をとっている。

2014.06.30

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

Real IntentのブースではDAC開催前にアナウンスしたバージョンアップしたてのRTLリントツール「Ascent Lint」をはじめ、CDC検証ツール「Meridian」、RTL早期バグ発見用のフォーマル検証ツール「Ascent IIV」、「Ascent XV」と一連のフォーマル検証ソリューションを展示していた。

RTLリントツール「Ascent Lint」は元々その速さが特徴の一つだが、最新バージョンではランタイム、キャパシティとも大きく改善され、最大500Mゲートのデザインを1時間以内で解析可能との事。またツールに予め備えられるルールが追加され、SystemVerilogのサポートも強化された。面白い機能としては今回新たにMathWorksのRTL生成ツール「HDL Coder」との連携が可能に。「HDL Coder」でMatlabコードから生成したRTLを「Ascent Lint」でLintチェックできるという。

また、X伝搬検証ツール「Ascent XV」も今年4月にバージョンアップされ、ランタイムが約10倍高速となったほか、SystemVerilogのサポートを強化。SynopsysのVerdiとインテグレーションも実現した。

聞くところによると、同社は非常に業績好調で2013会計年度は売上前年比60%増を達成。新規顧客との契約数が増えており、各ツール複数ライセンスをまとめて導入する顧客も多いという。

DAC開催後の6月23日には、日本国内におい日立金属がCDC検証ツール「Meridian CDC」を採用したという発表もあった。同社はネットワーク・コミュニケーション製品(イーサネット・スイッチ)のFPGA設計で「Meridian CDC」を使用しているという。(プレスリリース文)

2014.06.27

2014年6月20日に開催されたセミナーSystemC Japan 2014の講演資料の一部を公開致しました。

下記SystemC Japan公式サイトより無償でダウンロード可能です。

http://www.systemcjapan.com/library.html

※ダウンロードにはメンバー登録が必要となります。

※新規のメンバー登録には多少時間がかかる場合がございます。

SystemC Japan 運営事務局

2014.06.27

2014年6月20日、新横浜のホテルで今年で第9回目の開催となるシステム記述言語SystemCにフォーカスしたセミナー「SystemC Japan 2014」が開催された。今年は昨年を上回る延べ250人の参加者が集まり、高位合成の話題を中心に様々な発表が行われた。

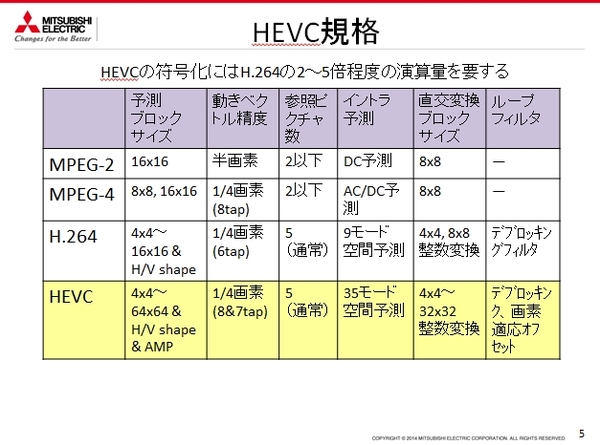

ここでは三菱電機の山本亮氏による講演、「HEVC方式によるSHVリアルタイムエンコーダ開発への高位合成適用事例」について紹介する。

SHVはNHK技研が開発した8Kにあたる次世代のスーパーハイビジョン国際規格で、2013年にNHKと三菱電機が世界初となるHEVC符号化方式を開発している。今回の山本氏の講演は同HEVC方式のSHVエンコーダをRTLを書いたことのないアルゴリズム開発者が中心となって高位合成で開発したというのが大きなポイントとなる。

山本氏によると高位合成を使ったモチベーションは、出来るだけ少人数かつ短期間でチップを開発したいという開発の効率化にあり、その背景には映像規格もののチップとして出来るだけ早く市場に投入したい(シェアを獲得したい)という要求や映像系専門のLSI設計者の減少、海外との競争で高まる開発コストの削減要求などがある。

また実際の開発現場では、アルゴリズム開発者とRTL設計者の両者によるキャッチボールで開発を進めていたが、どちらかが開発全体をカバー出来れば開発を効率化できると考え、アルゴリズム開発者が高位合成を使ってRTLを設計するという開発体制に辿り着いた。アルゴリズムの習得とRTL設計の習得を考えた場合、アルゴリズム開発者によるSystemCの習得(高位合成の習得)が最も早く開発がスムーズという判断だ。実際にアルゴリズム開発者は半日程度の学習でSystemCをほぼ習得できたという。

しかし、はたしてアルゴリズム開発者だけで回路設計が可能か?

回路品質などの課題を考えた結果、対策として回路全体のアーキテクチャを仕切れるハード設計者を置く事に決定。設計上大事なところはハード設計者が仕切る形とし、高位合成の利用については山本氏がサポートする形を取った。

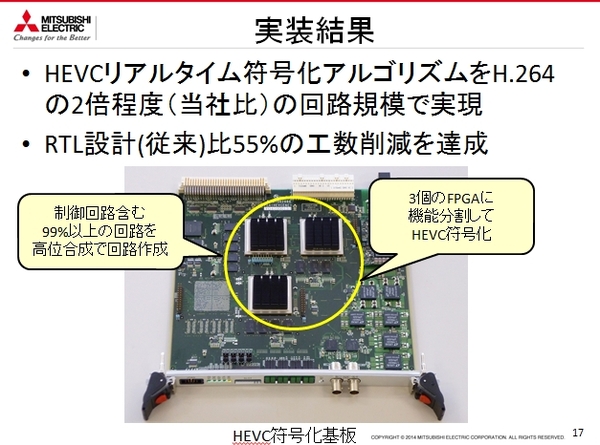

実際のエンコーダの設計では、制御回路も含めて全ての設計をSystemCで実施。これは部分的にHDLを使うなどしてアルゴリズム開発者に負担をかけないためで、既存のRTL資産や外部から調達したIPを除いて回路全体の99%以上をNECの高位合成ツール「CyberWorkBench」を使ってSystemCで設計。見積上のRTL設計による工数と比較して55%の工数削減を達成し、HEVC符号化アルゴリズムをH.264の2倍程度の回路規模で実現する事に成功した。

山本氏によると、この成功の裏には上述した開発体制の他に幾つかのポイントがあった。

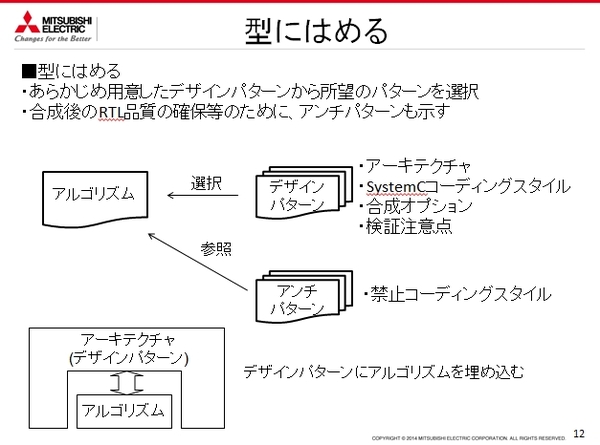

まず、設計にあたっては山本氏が幾つかのデザイン・パターンを用意した。デザイン・パターンにはターゲットとする回路アーキテクチャに応じたSystemCのコーディング・スタイル、使用する合成オプション、検証上の注意すべき点などがまとめられており、アルゴリズム開発者は手掛ける回路に適したデザイン・パターンを選択して設計を進めた。山本氏はこの手法を「型にはめる」設計と表現したが、デザイン・パターンにアルゴリズムを埋め込むという形がこの手法の目指すところで、上手く型にはめるためにツールの特性を考慮したアンチ・パターン(禁止するコーディング・スタイル)も合わせて用意した。

また、回路設計の知識が無いアルゴリズム開発者に対して、演算器の大きさや回路規模が小さくなるコーディング方法など回路規模に関する基本を指南。設計はブロック単位で論理合成結果を確認しながら進め、統合時の性能未達などを事前に回避した。

更にSystemCの実装テクニックとして高位合成用のテンプレートを用意し、パラメータによって複数の回路を合成する方針を取ることで似て非なる回路の設計効率を改善。このテンプレートによるパラメータ化手法は今後の製品展開を見据えた資産流用という意識もあっての対策だったという。

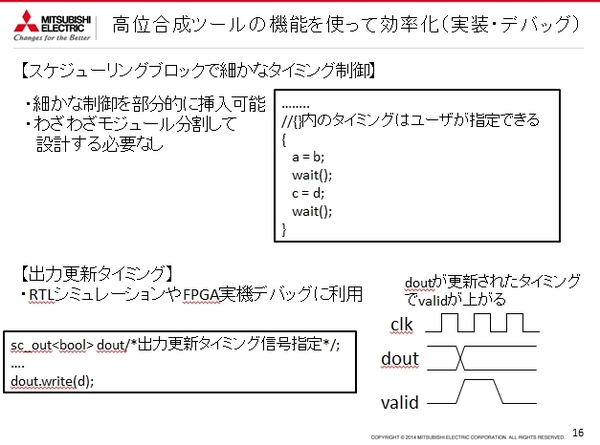

「CyberWorkBench」の機能としては、細かなタイミング制御機能によって一つのソースに制御回路と演算回路を混在できるため、わざわざモジュール分割せずに設計できる点、出力の更新のタイミングを知らせるオプションで回路の性能確認やデバッグが容易に可能となる点などを嬉しいところとして挙げた。

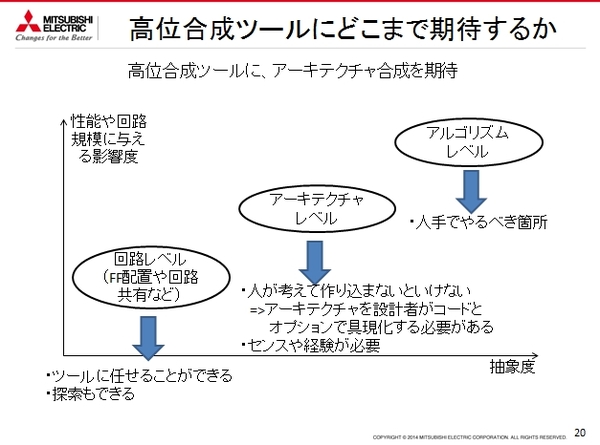

山本氏は講演の終わりに高位合成ツールへの要望として、配線の考慮や合成時間の短縮、ライブラリ・マニュアルの強化などを挙げ、今後は現状の更に上に行くアーキテクチャ・レベルでの合成の実現に期待するとした上で、「高位合成は、HW設計者のためだけのツールではなく、SW設計者やアルゴリズム開発者にとって、なくてはならないモノになる!」とコメント。合わせて発した「これからはアルゴリズムの性能だけを追求していてはダメ。アルゴリズム開発者も高位合成を上手く使って自分のアルゴリズムが安いコストで実現できる事を示していかなければならない」という言葉が印象的だった。

尚、今回の山本氏の講演はSystemC Japanとして公募した講演の一つで、セミナー会場で実施した聴講者によるアンケート結果から最優秀公募講演として表彰され、主催のAccellera Systems Initiativeより賞品としてMac Book Airが進呈された。

※画像は全て山本氏の講演データ

2014.06.26

2014年6月20日、新横浜のホテルで今年で第9回目の開催となるシステム記述言語SystemCにフォーカスしたセミナー「SystemC Japan 2014」が開催された。今年は昨年を上回る延べ250人の参加者が集まり、高位合成の話題を中心に様々な発表が行われた。

ここでは富士通マイクロソリューションズの鈴木晃一氏による講演、「気軽に試せるSystemC開発-ソフトウェアツールを活用しよう-」について紹介する。

鈴木氏はハード設計関連の各種セミナー、イベントで様々な講演経験のあるハードウェア設計者で、SystemCを用いた設計に関して豊富な実績を持つ人物。今回の講演ではそんな鈴木氏が自ら体験したフリー(無償)のソフトウェアツールによるSystemC設計の効率化手法を紹介してくれた。

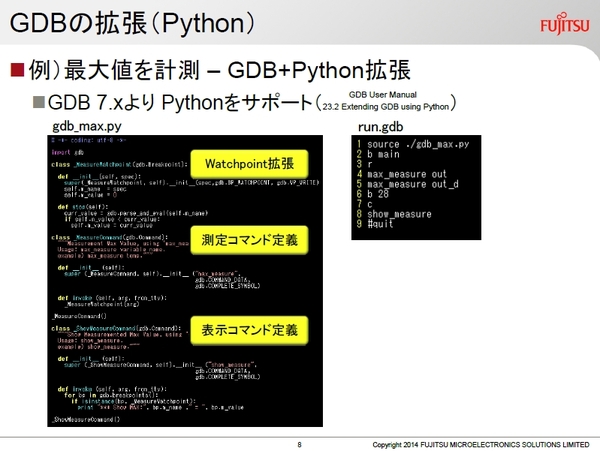

鈴木氏が最初に紹介した手法は、設計フェーズにおいてGNUのデバッガ「GDB」を活用するというもので、アルゴリズムをハード化する際に必要となる量子化作業(ビット幅の確定)の効率化を狙うもの。GDBのコマンドや測定用のソースを使うことで、例えば整数の最大値の計測など、prinf文やstd::coutで値を計測したりテキストにダンブするよりも効率的に計測できると鈴木氏。ただ、普通にGDBを使うだけではデータ型毎に関数を用意しなければならないなど応用が効かないため、鈴木氏はスクリプト言語「Python」を使ってGDBの拡張を試みた。

鈴木氏が行ったGDBの拡張は、ウォッチポイントの拡張、GDB測定用コマンドの追加、表示コマンドの追加などで、GDBにPythonのコードを読み込ませる事でこれらを実現した。Pythonを利用すれば様々な拡張が可能で非常に便利だという。

次に紹介してくれたのは設計フェーズにおいてSystemCコードの複雑度を測定するという手法。この手法ではCおよびC++言語のフリー(無償)のコード解析ツール「CCCC」を利用した。

鈴木氏によると同ツールを利用するとコード中の基本パス数を表す「MVG値」を測定することが可能で、その値が大きければ大きいほど複雑なコードと判断できるとの事。鈴木氏はこの「CCCC」をSystemCコードにも利用できないかと考え、一般的なソフトウェア開発でのMVG値の基準値に対して、実際の開発で記述した高位合成向けのSystemCコードの測定結果がどうなるか関数ごとに計測した。

その結果、MVG値が非常に高く「コードを理解不能」と判断される計測結果が多数あった。鈴木氏が着目したのはその計測結果と高位合成結果の相関性で、MVG値の高いブロックは高位合成が不可能であったのに対し、MVG値の低いブロックは合成品質はともかく高位合成可能だった。そのことから鈴木氏はSystemC開発においても「CCCC」を適用する事でそのコードの複雑度が数値から判断できるだけでなく、高位合成に入力できるかどうかの判断も可能かもしれないと語った。

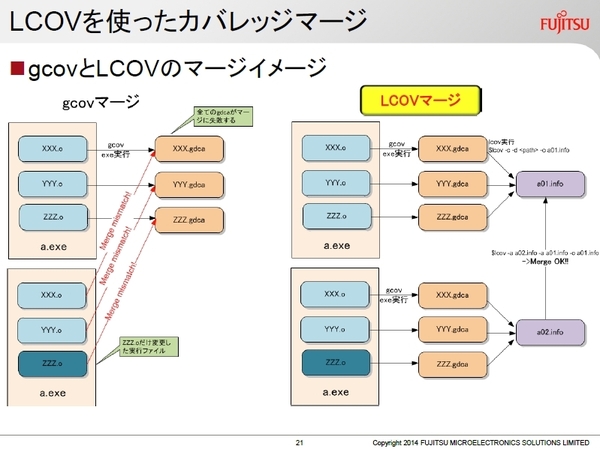

続いて紹介したのは検証フェーズのコード・カバレッジ計測に対して「LCOV」を使うという手法。「LCOV」はGNUのコンパイラgccに付属するコード・カバレッジ計測ツール「gcov」のグラフィカル・フロント・エンド環境で計測結果をHTMLで出力するなど非常に結果が見やすいと鈴木氏。更に「LCOV」の「tracefile」を使えば「gcov」ではうまく出来ないコード・カバレッジ結果のマージにも対処できるとの事だった。

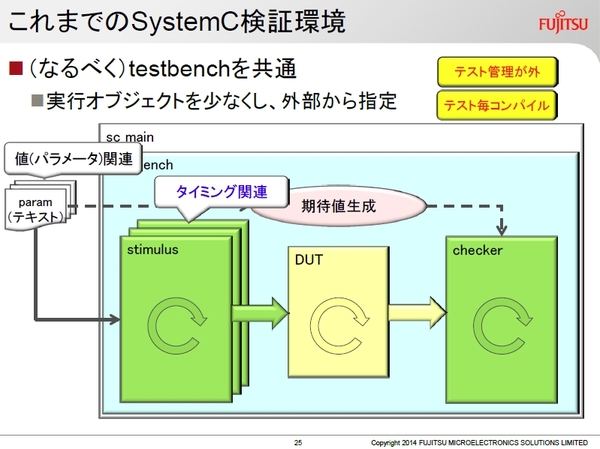

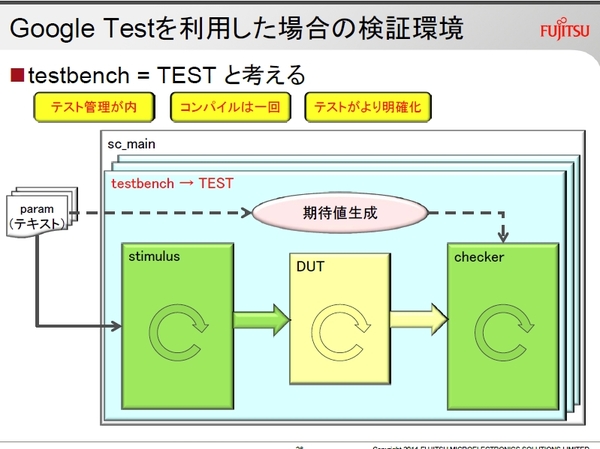

鈴木氏が最後に紹介したのは検証フェーズでのSystemC検証環境構築に関するもので、C++向けのテストフレームワークを活用するというもの。世の中に幾つか存在している無償のフレームワークの中から「Google Test」を用いた手法を紹介してくれた。

鈴木氏によると「Google Test」を用いたテストフレームワークでは、検証メソドロジUVMにおけるUVM testのようにTestbench=TESTという考えで一つの実行オブジェクトで複数のテストを行うことが可能。テスト毎にコンパイルする必要が無く複数のテストを単一のオブジェクトの中で管理することができ、検証項目に合わせてTestbenchやcheckerを作成できるためテストの明確化にも繋がるとの事だ。

但しSystemCの環境では連続してテスト実行できないため、鈴木氏は連続実行するためにグローバル関数「sc_get_curr_simcontext」のメンバー関数「reset」を利用して連続テストを実現。但し「sc_get_curr_simcontext」はSystemCのLRMに載っていないので使用はご注意下さいとの話だった。

※画像は全て鈴木氏の講演データ

以上、鈴木氏が紹介してくれた各手法は、講演のタイトル通り「SystemC環境で気軽に試せる」という点に主眼が置かれており、無償のツールがベースとなっているためSystemCビギナーのHDL設計者にとっては有益な情報と思える内容だった。また、ソフトウェア開発のようにある程度無償のツール環境だけで様々な試行が可能な点もSystemCの良さの一つと実感する講演であった。

ちなみに鈴木氏の所属する富士通マイクロソリューションズでは、90年代後半からSystemCの取り組みを開始。その豊富な経験をもとに各種SystemC開発関連のサービスを提供しているという事だ。

2014.06.19

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

OneSpin Solutionsのブースでは同社のフォーマル検証ツール群を展示していた。

今回のDACでのOneSpin Solutionsの新たな打ち出しとして目を引いたのは、ここ数年自動車業界でのホットな話題となっている自動車の電気/電子に関する機能安全規格「ISO 26262」に対するソリューション。

「ISO 26262」に対するソリューションとは、OneSpinのフォーマル検証技術を用いて設計した回路が「ISO 26262」に準拠しているかどうかチェックを行うもので、Infineon Technologiesやルネサスエレクトロニクスといった車載マイコンメーカーとのコラボレーションで開発したもの。具体的には等価性検証技術を用いたフェイル・セーフ設計構造の検証やフォルト・インジェクションによって「ISO 26262」の準拠を確認する。

マーケティングVPのDave Kelf氏に聞いたところ、OneSpinのツール自体が「ISO 26262」のツール認証を取得している訳ではないが、フォーマル検証ツールを提供するEDAベンダとして「ISO 26262」に対するソリューションを打ち出したのはOneSpin業界初。プロパティ・チェックとカバレッジ解析の技術を有しているからこそ実現できたとの事。

またDave氏によると、プロパティ・チェックがスタンダードになりつつあり、それに合わせて会社の業績は上々という話で、EDA市場としては厳しい状況とされる日本国内においても顧客が増えているという事だった。クラウド・ベースのFPGA設計プラットフォームを提供する米Plunifyと組んでFPGA向けのソリューションを拡大するなど、フォーマル検証技術をコアに様々な展開を進めているOneSpinだが、今後の計画としては高位合成ツール向けのカバレッジ解析やCDCチェック、Power関連のソリューションも打ち出していく予定と聞いた。

※OneSpin Solutions

2014.06.19

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

Ansysのブースでは傘下のApache Designの各種ツールを展示。連日ブース内スイートで自社顧客のユーザー事例を紹介していた。

主力のダイナミック・パワー解析ツール「RedHawk」は、DACに合わせてバージョンアップされ「RedHawk 2014」がリリースされたばかり。同バージョンでは複数コンピュータによる分散処理がサポートされ、メモリ使用量を平均3分の1に抑えられるようになり、シミュレーションのキャパシティが1億インスタンス以上に拡大された。

また同最新バージョンでは先端のFinFETベースのデザインにも対応しており、DAC会期中にIntelの14nm Tri-Gateプロセスのリファレンス・フローに「RedHawk」をはじめ「Totem」、「PathFinder」が認証された事がアナウンスされていた。Intelの先端フローでEM,ESD,NOISEと3種類のツールが全て認証されているのはApacheだけだという。ちなみにApacheの「RedHawk」はIntelの他にTSMC,Samsung,Global Foundries,TowerJazzなど大手ファウンドリの先端プロセスにて一通り認証されている。

新製品としては今回のDACで「RedHawk CPA」という製品を新たに披露。CPAとはChip-Package Analysisの略で、同製品は文字通りチップ内に限らずパッケージも含めた形で電圧降下をチェックする事が可能だという。

尚、今年Ansysブースで発表された事例は、Ciena、Samsung、Synapse、Applied Micro、NXP、STMicroelectronics、LSIなど有名どころがずらり。STMicroelectronicsの事例は「RedHawk」を利用してダイサイズを縮小に成功したというものだった。

2014.06.19

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

S2Cのブースでは同社のプロトタイピング・ボード「Virtex-7 TAI Logic」ファミリの各種ボードを展示していた。

今年2月にリリースした最新の「QuadE V7 TAI Logic Module」は、XilinxのFPGA Virtex-7 2000Tを4個搭載しており最大8000万ゲートのデザインに対応。計32GBのDDR3メモリを搭載している。また、イーサネット経由でリモート利用する機能がサポートされ、複数拠点、複数チームによる同時共有利用も可能に。ボード上のデザインの書き換えはボード上のSDカードを使って行う。

展示ブースでは、同社のプロトタイピング・ボード「Virtex-7 TAI Logic」の使い方として4種類のフローを紹介。スタンドアロンでの使い方に加えて、Mentor GraphicsのESLツールと連携して利用するフローも紹介していた。この使い方は昨年開催されたセミナーSystemC Japan 2013で日本サーキットが講演した手法に良く似ており、ひょっとするとそれがベースになっているのかもしれない。

・Design Exploration flow

Mentor GraphicsのESLツール「Vista」と連携したアルゴリズム開発/SoCアーキテクチャの探求

・IP Validation flow

S2C TAI Logic Moduleベースのプロトタイピング済みIP「Prototype-Ready IP」を用いたIP評価および選定

・System Integration flow

70種以上あるインタフェース・ドータ・カードを用いたプロトタイプの作成

・Software Development flow

Mentor Graphicsの「Embedded CodeBench Virtual Edition」と連携したバーチャル・プロトタイプ・ベースのソフトウェア先行開発

尚、ブース内スイートでは展示していない新製品を密かに顧客に紹介していた様子。次々と新製品の開発を進めている同社だけに、どのような新製品が出てくるのか楽しみだ。

2014.06.18

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

Intelのブースでは同社のESLツール「Cofluent Studio」をツールを展示していた。

「Cofluent Studio」は、Intelが2011年に仏CoFluent社を買収して以降、Intel自身が社内のSoC開発部隊で活用しており、社外ユーザーだけでなく社内に多数のユーザーを抱えている。

聞いたところによると、IntelではSoC開発において「Cofluent Studio」と合わせてCadenceの高位合成ツール「C-to-Silicon Compiler」を利用する事を決定しており、「Cofluent Studio」と「C-to-Silicon Compiler」の連携フローを構築しているとの事。具体的にはシステムレベルのSoC仕様を「Cofluent Studio」で検討・確定し、ハード化部分は「Cofluent Studio」から出力されるSystemCモデルをベースに「C-to-Silicon Compiler」で高位合成するというフローになる。

また、ソフトウェア部はIntel傘下のWindRiverが提供するシミュレータ「Simics」環境を用いて開発を行う形で、「Simics」のシミュレーションで利用する仮想ハードウェアのモデルを「Cofluent Studio」で作成するというツール連携も実現していると聞いた。

ちなみにIntelの「Cofluent Studio」の日本国内の販売に関しては、今年3月にネットワーク・シミュレーター「OPNET」を取り扱う情報工房が代理店になったとアナウンスされている。

2014.06.18

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

RTL静的解析ツールを手掛けるBlue Pearl Softwareのブースは年々大きくなる印象。同社のブースではRTLサインオフの実現を目指す一連のRTL静的解析ツールを展示していた。

※Blue Pearlのブースはサムスンの向かいに位置

※画像はBlue Pearlのニュースレター掲載のもの

※画像はBlue Pearlのニュースレター掲載のものBlue Pearl SoftwareはRTL静的解析ツールとしてLintツール、CDCチェック、SDC生成と大きく3種類の製品を提供しており、ここ最近はFPGA設計向けのRTLサインオフ・ソリューションとして打ち出している。話によるとFPGA向けというのはそのツールの価格の安さからくるもので、製品の定価は明らかにされていないがBlue Pearl Softwareのツールは競合製品よりも大幅に安い価格で購入できるようだ。

また、安さだけではなくツールの機能面においても幾つか優れた特徴があり、例えばLint機能を中心としたRTL解析ツール「Analyze RTL」はFPGAベンダ向けのチェック機能を備えているほか、フォーマル検証技術によるステートマシン解析機能なども用意されておりRTLからステートマシンを抽出しデッドロックや到達不能ステートの検出を自動処理できる。

※画像はFSM解析機能のGUI画面(Blue Pearl社Webサイト掲載)

更にセットアップのし易さと充実したビジュアル環境も同社ツールの特徴の一つで、今回のDACでは新しくなった「Analyze RTL」のセットアップ・ウィザードや新たなCDC解析向けのクロック解析ダイアグラムなどを披露していた。

ちなみにBlue Pearl Softwareは日本国内にもオフィスを構えており、日本人エンジニアによる技術サポートも可能。FPGAユーザーに限らずASICユーザーにも手軽な高機能RTL解析ツールとしてBlue Pearl Softwareの製品を利用して欲しいとの事だった。

※Blue Pearl Software

2014.06.16

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

検証サービスを手掛ける日本のベンチャーVtechは今回がDAC初出展。自社製品の検証IP「VARON」を展示していた。

検証IP「VARON」は、回路に実装してオンチップ解析を行うタイプのIPでターゲット・デバイスの中身を「何でも見れる」のが最大の特徴。その用途は様々だが最も好評な機能の一つがバスのパフォーマンス・チェックで、ASICのプロトタイピングとしてデザインと共に「VARON」をFPGAに実装すれば、バスのトラフィックや割り込みの状況などをリアルタイムに観測可能。シミュレーションやICEでは確認できない実デバイスの挙動を最高の形で確認できる。

また、SVA(System Verilog Assertion)を回路に実装する解析機能を備えており、様々な形でトリガを調整しながら回路をデバッグする事も可能。ユーザーによってはSoC型FPGAのソフトウェアのチューニング用にパフォーマンス解析を試みるケースや、アナログのサンプリングに「VARON」利用するケースもあるようで、ハードウェアの検証だけでなくハードウェアやソフトウェアの性能向上を目的に導入を検討するユーザーもいるという。

製品は検証IPと外部からのコントローラ、解析環境とコンパイラからなるソフトウェアがパッケージ化されておりライセンス形式で提供されるが、製品としてチップに実装する場合はロイヤリティ契約となる。

既に日本国内に限らず米国にもユーザーが存在しているようで、大規模な先端FPGAユーザーからの引き合いが多いと聞いた。

2014.06.13

2014年6月1日-5日、カリフォルニア州サンフランシスコで開催された第51回Design Automation Conferenceの展示会レポート。

Mentor Graphicsは今年も自社の展示ブースとは別に「Verification Academy」のブースを設置。同ブースでは日替わりで数々の機能検証関連のプレゼンが行われ多くの聴講者を集めていた。

「Verification Academy」は、Mentor Graphicsが運営する機能検証技術のスキルアップを目的としたエンジニア向けのナレッジサイトで、検証メソドロジUVMを中心に様々な機能検証技術に関するコンテンツを無償で提供している。

※UVM:Universal Verification Methodology

今回聴講した「A New Era in Functional Verification」というプレゼンは、Mentor GraphicsのChief Verification ScientistであるHarry Foster氏によるもので、ここ最近の検証のトレンドを解説。同氏によると検証作業の増加とともにSystemVerilogを用いたテストベンチ作成がメイン・ストリームとなってきており、それに合わせて検証メソドロジUVMの採用も拡大。「Verification Academy」の登録メンバー数も右肩上がりで伸びており、この1年間で約1.5倍の23000人超になったとの事。近年の傾向としては先端デバイスを中心にSoCに実装される組込みソフトの量が増え、必要とされるソフトウェアエンジニアの人数も急上昇。最先端の16/14nmチップでは90nmチップの約17倍ものソフトウェアエンジニアが必要になるという。

そんな中、ソフトウェア開発の効率化に一役買っているのがエミュレータであり、エミュレータの市場は2010年以降、平均成長率30%近くと急速に拡大。Mentorではニーズの高まりに応じて、エミュレーション・ソリューションの強化を進めており、今年4月にエミュレーション環境「Veloce」と機能検証環境「Questa」を統合した新たな検証ソリューション「Mentor Enterprise Verification Platform(EVP)」を発表している。

Harry Foster氏は、既に検証メソドロジにフォーカスしていた「Verification 2.0」の時代は終わり、これからはシステム視点でハードとソフトの検証にフォーカスする「Verification 3.0」の時代になるとし、そのためには機能検証に要求される様々な要素を包含するエンタープライズ・レベルの検証ソリューションが必要だと語っていた。

2014.06.11

2014年6月4日、米SIA(Semiconductor Industry Association)は、2014年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年4月の世界半導体売上は前年同月比11.5%増、前月比0.6%増の263.4億ドルで4月の売上としては過去最高を記録した。

前年比11.5%増という成長率は過去3年で最も高いもので、単月の売上記録の更新は昨年9月以来8ヶ月連続、単月売上が前年実績を上回るのはこれで12ヶ月連続で世界の半導体業界は右肩上がりの成長を続けている。

先頃SEMIから発表された2014年Q1の世界半導体製造装置の売上にも業界の活況が現れており、2014年Q1売上は前年比39%増の101.5億ドル。米国市場以外は全ての地域で売上前年比増を記録しており、韓国市場は前年比135%増、中国市場は前年比209%増と大幅な伸びを示した。半導体製造装置への投資は今後の更なる需要増を見越したもので、半導体好景気は長期的に継続すると予測される。

※2014年Q1世界半導体製造装置売上統計(SEMI)単位:10億ドル

また、世界半導体市場の統計をまとめているWSTS(World Semiconductor Trade Statistics)が6月3日に2014年春季半導体市場予測を発表したが、それによると今年の世界半導体市場の売上は前年比6.5%増の3250億ドルに到達。その後も、2015年+3.3%、2016年+4.3%と成長を継続し2016年には3505億ドルに到達すると予測している。

2014年の市場別の成長率は、アジア市場が9.3%、欧州市場が7.9%と大きな成長が見込まれており、2013年に二桁成長を果たした北米市場は2.1%、日本市場のみ-1.3%のマイナス成長と予測されている。日本市場の成長率はドルベースで算出されたもので、円ベースで算出すると4.0%の成長となる。

2014年4月の売上を地域別に見ると、日本市場を含めた全ての地域で売上前年比増を達成。最も高い成長率を示したのは北米市場で前年比14.7%だった。

2014.05.30

2014年5月30日、ARMはアイルランドの新興EDAベンダDuolog Technologiesの買収を発表した。

ARMの発表によると、ARMの狙いはDuolog Technologiesの提供するEDAツール「Socrates」を自社のARM開発用ツールに取り込む事で、それによりユーザーの複雑なSoCインテグレーションを助けると同時に、自社の「CoreLink」、「CoreSight」といったのシステムIPの利用が増えると考えているようだ。

「Socrates」はSoCサブシステムのシステムレベルのインテグレーション、機能検証、接続確認を可能とするツール環境で、「Socrates」シリーズの製品として、I/O仕様の策定とファブリック生成を行う「Spinner」、レジスタやメモリマップの管理を行う「Bitwise」、トップレベルのチップ・アセンブリ(結線)を行う「Weaver」の3つの製品を提供している。ARMによるとDuolog Technologiesの「Socrates」は、過去10年でテープアウト100件以上の実績があるとの事。

ARMは自社の成長と合わせて数々の企業買収を行っているが、EDAベンダとしては2011年にプロセッサ検証向けテストベンチ生成の米Obsidianとフィジカル最適化ツールの米Prolificを買収している。最近では2013年にフィンランドのIoT向けソフトウェアのベンダSensinode Oyを買収しているほか、同じく2013年にゲーム向けのグラフィック技術を手掛ける英Geomerics社を買収している。

尚、ARMによるDuolog Technologiesの買収は2014年Q3で完了予定。ARMは買収後「Socrates」のライセンスを持つ顧客のサポートを継続するとしている。

2014.05.23

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2014.05.23

2014年5月22日、Mentor Graphicsは、2015会計年度第1四半期(14年2-4月)の売上を報告した。

発表によると、Mentorの2015会計年度Q1の売上は、前年比約11%増の2億5220万ドル、営業利益は164万ドルで前年比72%減だった。(※GAAP基準による会計結果)

Mentorの今期Q1の売上を製品別で見ると、大黒柱のCalibreをはじめとする物理設計ツールよりも、エミュレータを中心とした検証ツールの方が売上全体に占める割合が大きかった。

Mentorはこの4月に高速高精度SPICEのBerkeley Design Automationの買収を発表し業界を驚かせたほか、シミュレータ「Questa」とエミュレータ「Veloce」を統合した検証環境ソリューションも発表しており、大きな意味での「検証ソリューション」の拡充を図っている。

Mentorは次期2015会計年度Q2(14年5-7月)の売上を今四半期同等の2億5000万ドル程度と予測している。

2014.05.23

2014年5月21日、Synopsysは、2014会計年度第2四半期(14年2月-4月)の四半期決算を報告した。

発表によると、Synopsysの2014会計年度Q2の売上は、前年同時期比約3.7%増、前期Q1比約8%増の5億1770万ドルで同社の四半期売上記録としては過去最高。前Q1決算報告時の予測を上回る好結果となった。純利益は前年同時期比約8%減の6330万ドルだった。(※GAAP基準による会計結果)

Synopsysはこの2月から4月の間に、「Verification Compiler」、「IC Compiler II」と大型の新製品を相次いで発表。更にソフトウェア静的解析ツールのCoverityを買収しソフト開発分野への本格参入を果たした。これらのビジネス効果は次の四半期には売上に反映される見通しでSynopsysは次のQ3の売上を今期Q2を上回る5億1500-2500万ドルと予測している。

2014.05.23

2014年5月21日、Mentor Graphicsは、機能検証ソリューション「Questa」シリーズの新製品「Questa PropGen」を発表した。

Mentorによると新製品「Questa PropGen」は、Questaフォーマル検証ソリューションの一端を担うツールでその名の通りプロパティを自動生成する事が可能。アサーションベース検証における大きな課題であるアサーション記述の手間を省きアサーションベース検証の自動化を促進できる。同種のソリューションとしてはAtrentaが「BugScope」という製品をJasperが「ActiveProp」という製品を提供しているがEDA大手3社の中ではMentorの「Questa PropGen」が唯一の存在となる。※JasperはCadenceによる買収が決定している

また発表によるとMentorはフォーマル検証ツール「Questa Formal」のエンジンを強化したようで、同エンジンを利用するCDC検証ツール「Questa CDC」は検証速度が6倍に向上したという。

2014.05.23

2014年5月21日、Mentor Graphicsは、3次元電磁解析シミュレーターの米Nimbic社の買収を発表した。

MentorによるNimbicの買収は既に完了しており、Nimbicの提供していたソリューションはMentorのPCB/ICパッケージ向けソリューションの一部として提供される。

Nimbicは以前「Physware」という社名でEDAツールを販売していたが、2011年にNimbicとしての営業を開始。PCBボードおよびICパッケージ向けの3次元電磁解析ツール「nWave」、3次元寄生抽出ツール「nAPEX」、3次元パワー・インティグリティ解析ツール「nVolt」の3つの製品とこれらツールをクラウド環境上で利用できる「nCloud」というソリューションを提供していた。

日本国内ではステイシフト社がNimbic製品の代理店として製品を提供しており、ルネサス、東芝、パナソニックなどが顧客に名を連ねていた。

2014.05.13

システム記述言語「SystemC」にフォーカスした技術セミナー「SystemC Japan」

9回目の開催となる今年のSystemC Japan 2014は、Accellera Systems Inisiative主催の下、国内外14社のスポンサー企業が協力し開催。公募による3件の講演を含めた計11件のセッションとパネル・ディスカッションを実施致します。

セミナー終了後のレセプション・パーティーでは、スポンサー企業14社のソリューションを展示し、恒例のプレゼント抽選会も行います。

世界最大のSystemCユーザー・セミナー「SystemC Japan 2014」に是非足をお運び下さい。→申し込みはこちら

SysmteC Japan 2014運営事務局

2014.05.07

2014年5月5日、米SIA(Semiconductor Industry Association)は、2014年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年3月の世界半導体売上は前年同月比11.4%増、前月比0.4%増の261.6億ドルで3月の売上としては過去最高を記録した。

前年比11.4%増という成長率は先月発表された2014年2月の売上同様過去3年で最も高いもので、単月の売上記録の更新は昨年9月以来7ヶ月連続、単月売上が前年実績を上回るのはこれで11ヶ月連続となる。

今年の世界半導体市場は、2013年の過去最高を上回る3200億ドル前後と予測されているが、既に2014年Q1の売上は四半期売上として過去最高の784.7億ドルを記録している。

売上を地域別に見ると、北米市場とアジアその他地域が成長を維持してともに前年比2ケタ増。日本市場は昨年11月以来の前年比増をかろうじて達成した。

2014.05.07

2014年4月24日、Alteraは2014会計年度第1四半期(14年1-3月)の売上を報告した。

発表によるとAlteraの2014年Q1(14年1-3月)売上は、前年比約12%、前期Q4比約1%増の4億6110万ドル、営業利益は前年比約14%増の1億3459万ドルだった。

Alteraは前四半期の売上報告時に2014年Q1の売上を前年割れと予測していたが、中国におけるLTE需要の拡大が同社のテレコム/ワイヤレス分野の売上を押し上げ、終わってみれば予想を上回る四半期決算となった。

それを示すように地域別ではアジア地域が、分野別ではテレコム/ワイヤレス分野がそれぞれ全売上に対する割合を伸ばしている。製品別では、最新の28nm製品を含む新製品カテゴリの売上が大きく成長している。

Alteraは2014年1-3月の間に同社の戦略に関わる様々な発表を連発。主なところでは、Intelの14nmトライゲート・プロセスで作ったFPGAをデモ、浮動小数点DSPのハードコアを20nm FPGA向けに用意、TSMCの最新のパッケージ技術を20nm FPGAに採用などがあった。

Alteraは次期2014年Q2(4-6月)の売上を2014年Q1の2-6%増と継続的な成長を予測している。

2014.04.25

2014年4月23日、Xilinxは2014会計年度第4四半期(2014年1-3月)決算を報告した。

Xilinxの2014会計年度Q4の売上は、前年同時期比16%増、前期Q3比5%増の6億1780万ドル。営業利益は前年比29%増の1億8950万ドルだった。(※GAAP基準による会計結果)

2014会計年度の売上合計は、前年比10%増の23億8000万ドルで純利益は前年比29%増の6億3000万ドルを計上した。

同社のCEOのコメントによると、28nm製品の成功が2014会計年度の増収増益に大きく貢献したとの事で、Xilinxの28nm FPGAは28nm FPGA市場の70%のシェアを獲得しているという。

XilinxのQ4売上を地域別でみると、アジア地域の売上が全売上の43%とQ3実績を上回る伸びを見せた。分野別の売上では、主力のコミュニケーションおよびデータ・センター向けが全売上の49%と大きく伸びた。製品別売上では、28nm製品を含む主力の新製品カテゴリ(Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6)の売上が強力で前年比85%増、売上全体に占める割合は42%まで上昇した。

Xilinxは、次期2015年Q1(14年4-6月)の売上を今期実績の0%-4%増と予測をしている。

2014.04.24

2014年4月23日、ARMは、2014会計年度第1四半期(2014年1-3月)の売上を報告した。

ARMの2014年Q1の売上は、前年比16%増、前期比約0.7%増の3億520万ドルで前Q4に続いて四半期売上記録を更新、税引き前の純利益は前年比約9%増の約1億470万ドルだった。

売上の内訳を見るとライセンスの売上が前年比約37%増と大きく伸び1億2990万ドル、ロイヤリティの売上が前年比約3%増の1億4450万ドルだった。ライセンスの売上の約86%はプロセッサ・ライセンスの売上だが、ARMはこのQ1で前期Q4と同じ26件のプロセッサ・ライセンスの契約を獲得。うち5件は最新のARMv8-Aアーキテクチャ・ベースのプロセッサで、同v8アーキテクチャ製品の累計ライセンス数は43件となった。内訳は下記の表の通り。

※画像はARM発表資料より抜粋

2014年Q1で出荷されたARM搭載チップの総数は約29億個で2013年Q4と同等。その内訳は以下の表の通りでこちらも前Q4とほぼ同じ内容。製品別出荷数としてはCortex-Mシリーズの出荷が若干増えた。

※画像はARM発表資料より抜粋

2014.04.23

2014年4月23日、SystemVerilogベースのESLツール「Bluespec」の日本代理店サイバネットシステムは、「Bluespec」の廉価版「Bluespec Lite」のリリースを発表した。

サイバネットによると「Bluespec Lite」は、保守(電話とメールによる技術サポート)を含めた1年間ライセンスで100万円(税抜き)と同種のESLツールとしては破格の設定。通常製品と同様に「Bluespec Lite」にはBluespecコンパイラとBluespecシミュレータがバンドルされているが、廉価版として合成対象のソースコード中のオブジェクト数が1800までという制限と、使用者は1ライセンスにつき特定の1名のみという制限が設けられている。

※オブジェクトとは、変数、インスタンスしているモジュール(レジスタやワイヤ等も含む)、式など。

「Bluespec Lite」は、ユーザーの製品評価・製品導入の障壁を引き下げることを目的としてサイバネットシステムが発案した日本国内限定のプログラムという事で、まずはブロック単位の設計で試しに「Bluespec」を使ってみたいというニーズにマッチしている。

尚、今回の「Bluespec Lite」のリリースに合わせて、サイバネットではビギナー向けにBluespec SystemVerilogの自習用の教材を刷新したとの事。

「Bluespec」は、SystemVerilogベースの専用言語「Bluespec SystemVerilog」で記述されたRTLよりも抽象度の高い回路記述をRTLに合成するESLツール。ユーザーによっては、SystemC TLMよりも生産性が高くSystemCの約半分のコーディングで済むといった話もあり、専用言語さえ習得すればかなり自由度の高いシステムレベルの設計からRTLを実装できる。また「Bluespec」は、サイクルベースの記述から合成することも可能でSystemCもサポートしている。

※画像はサイバネットシステムのブローシャより抜粋

2014.04.22

2014年4月21日、Cadenceは、2014会計年度第1四半期(2014年1-3月)の売上を報告した。

Cadenceの2014年Q1売上は、前年同時期比約7%増、前期Q4(13年10-12月)と比較して約0.5%増の3億7900万ドル。純利益は前年比約60%減の3300万ドルだった。(※GAAP基準による会計結果)

同社の売上はこれで17四半期連続で前年比増を記録している。

Cadenceは次期2014年Q2の売上を3億7000-8000万ドルと予測している。

2014.04.22

2014年4月21日、Cadenceはフォーマル検証ツールを手掛けるJasper Design Automationの買収を発表した。

発表によるとCadenceはJasperを現金約1億7000万ドルで買収する事でJasperと正式契約。買収は今年Q2の間に完了する見通し。

Cadenceは自前のフォーマル検証ツールとして「Incisive Formal Verifier」を保有しているが、単体のフォーマル検証ツールの市場シェアとしては恐らく業界首位と思われるJasperのソリューションを取り込むことで、自社の検証ソリューションの更なる拡充を計る。

Jasperはフォーマル検証ツールのEDAベンダとしては老舗で設立は2000年。日本国内では早くからサイバーテック社が代理店として販売を開始し複数の大手顧客を獲得していた。大手IPベンダの大規模採用なども後押しして同社の業績は順調に伸びていたが、2010年から打ち出した個別の検証要求にフォーカスした自動化アプリ「Jasper Apps」の戦略があたり急成長。昨年時点で半導体上位15社のうち10社が顧客だとしていた。

チップの複雑化、大規模化に伴い、あらゆる検証手法を駆使する先端チップの開発ベンダを中心にフォーマル検証の市場はここ数年拡大傾向にあり、2010年以降の市場成長率はシミュレータを上回る10%を超えるとされている。その市場の中でJasperは中心的な存在だっただけに今回の買収に関するインパクトは大きい。

2014.04.16

2014年3月19日、IP-XACTベースのESLソリューションを手掛ける仏Magillemは、同社のESL技術の提供でSTMicroelectronicsとOEM契約した事を発表した。※訂正あり

発表によるとMagillemは、STMicroelectronicsの開発したTLMモデリング環境及びメソドロジを同社のEclipseベースのデザイン環境上に統合。STMicroelectronicsの技術とMagillemの環境をインテグレーションすることにより、バーチャル・プラットフォームの作成と解析を行うためのSystemC TLMインフラの構築を実現した。

このインテグレーション環境には、SystemC準拠のシミュレーターでコンパイルおよびシミュレーション可能なHWおよびSWモデルの自動コード生成機能が含まれているとの事で、それらがMagillemの技術を活かしたSystemC TLMインフラの中核機能の一つ。開発した環境はMagillemのESLソリューションとして、MagillemによってSTMicroelectronicsの顧客やパートナーに販売されるという。

Magillemのツール環境はIP相互運用のための標準規格IEEE1685 IP-XACTをはじめ、SystemC TLM2.0, SystemC AMS, SystemRDLなど複数の業界標準をサポートしており、独自のコード生成技術を活かしてIPベースのシステムの構築を中心にESLからRTLまでの設計フローに対応。ユーザーの工夫一つで仕様となるIP-XACTデータを起点に様々なSystemC TLMベースの環境を自動生成できるほか、メモリマップ等の定義、デバイス・ドライバの生成、設計データのバージョン管理やドキュメント生成など周辺機能も充実している。

※画像はMagillem提供のデータ

Magillemによると発表したSTMicroelectronicsとのOEM契約は、両社の長年のコラボレーションの成果であるとの事。Magillemは欧州大手を中心に北米、日本にも複数の大手顧客を抱えているが、導入各社の事例を見ていると今回のSTMicroelectronicsのようにMagillemの環境を設計フロー上のインフラとして活用しているケースが多いようだ。

2014.04.16

2014年3月24日、各種FPGAベースのプロトタイピング・システムを取り扱うプロトタイピング・ジャパンは、新たに独PRO DESIGN社のプロトタイピング・ボードの販売を開始した事を発表した。

PRO DESIGNは、2012年にXilinx Virtex-7ベースのプロトタイピング・システム「proFPGA」を発表し、現在Xilinx Virtex-7 XCV2000Tを搭載する製品を3種類(FPGA1個/2個/4個)リリースしているほか、増設用の各種FPGAモジュールやドータ・ボードなど包括的にプロトタイピング・システムを提供している。

※画像はPRO DESIGNのWeb上の画像「proFPGA quad V7」

同社は以前「CHIPit」と呼ぶFPGAベースのプロトタイピング・システムを手掛けていたが、2008年に同事業をSynopsysに売却し、新たなアーキテクチャーを用いたプロトタイピング・システム「proFPGA」を製品化した。

「proFPGA」のうりは豊富な拡張モジュール、ドータ・ボードによる拡張性の高さと速さで、独自の高速コネクタ仕様によりボード間のデータ転送速度は1.2Gb/秒、FPGA上のトランシーバーのデータ転送速度は12.5Gb/秒を実現する。

プロトタイピング・ジャパンは、社名の通りプロトタイピング・ソリューションにフォーカスした技術商社としてプロトタイピング・システムの提供では多数の実績を誇り、現在も複数のソリューションを提供中。かつては現在Synopsysが提供している「HAPS」も同社が提供していた。

2014.04.16

2014年3月7日、ネットワーク・シミュレーター「OPNET」を取り扱う情報工房は、ESLツール「CoFluent Studio」の販売でIntelと代理店契約した事を発表した。

発表によると情報工房はESLツール「Intel CoFluent Studio」の販売に加え、保守サポートやカスタマイズにも対応するほか、同社の扱うネットワーク・シミュレーター「Riverbed OPNET」と「Intel CoFluent Studio」協調シミュレーション・ソリューションを提供していくという。

「Intel CoFluent Studio」は、Intelが2011年に買収によって獲得したISSを使用しないシステム・レベルのシミュレーション環境で、Intel社内で自社製品の開発に活用している他、携帯電話や複写機、車載システムの開発などの用途で社外にも複数のユーザーを抱えている。

設計の初期段階における仕様情報から動くシミュレーション環境を作成できるのが「Intel CoFluent Studio」の大きな特徴の一つで、UML,SysMLまたは独自グラフィカル言語やMatlab,ANCI-Cなど、多彩な言語からパフォマーンス・シミュレーション用のSystemCモデルを自動生成する事が可能。実装用の組込みCコードの出力機能なども備えている。

※画像はIntelのWeb上の画像