NEWS

2014.12.12

2014年12月11日、Cadenceはソフトウェア・ドリブンSoC検証向けの新製品「Perspec™ System Verifier」を発表した。

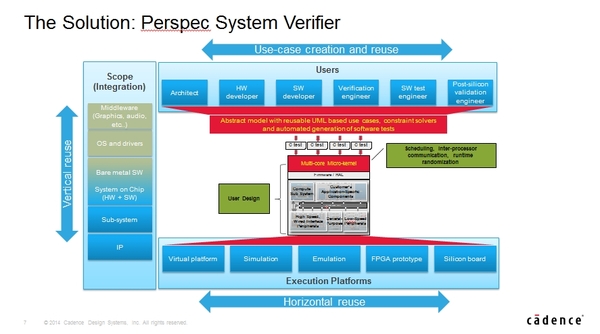

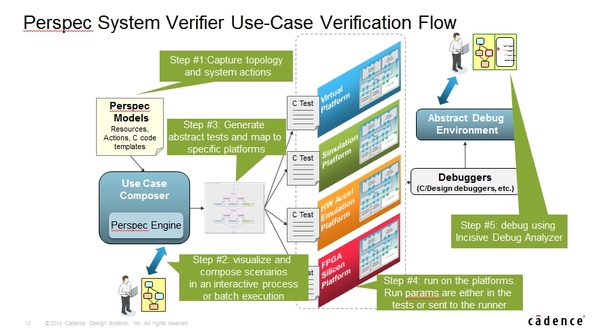

「Perspec™ System Verifier」はソフトウェアを用いたSoC検証のためのツールで、簡単に表現すると、SoCの仕様情報とユーザーが定義したシナリオからCのテストコードを自動生成してくれるツールである。同種の製品としては、Breker Verification Systemsが「TreKSoC」という製品を出しているが、Cadenceの「Perspec™ System Verifier」はそのコンセプトからして大きく違う。

「Perspec™ System Verifier」の目指すのは、同社がこれまで培ってきた制約付きランダム的な考え方やカバレッジ手法をソフトウェア・ベースのダイレクト・テストに取り込む事で、ユーザー、検証環境、検証の抽象度を問わないソフトウェア・ドリブンSoC検証の実現がコンセプトとなっている。

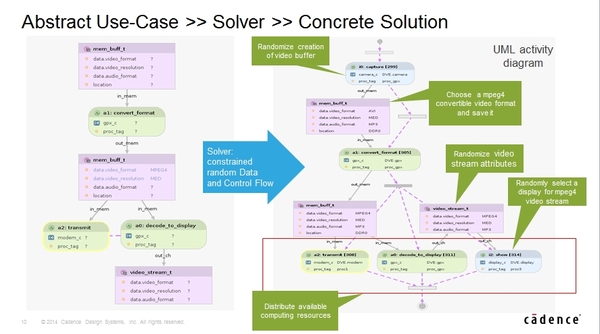

「Perspec™ System Verifier」の具体的な使用法としては、まずCのテストコードを生成するためにSoCを構成するリソースの情報、それら各リソースの機能/動き、接続、Cのテンプレートを用意する。

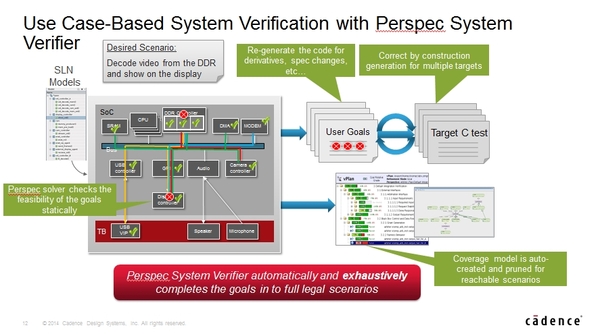

次にシナリオとしてSoCにして欲しい動作、どのように動いて欲しいかをUMLのアクティビティ・チャートで定義する。そうすると「Perspec™ System Verifier」は、前提となるリソース情報から与えられたシナリオに矛盾しないあらゆる処理パターンを自動的に洗い出しそれをCのテストコードとして出力。同テストコードを使えば、シナリオ通りにハードがアクティベートされたかどうか、どのようにハードがチェックされたかを確認出来る。

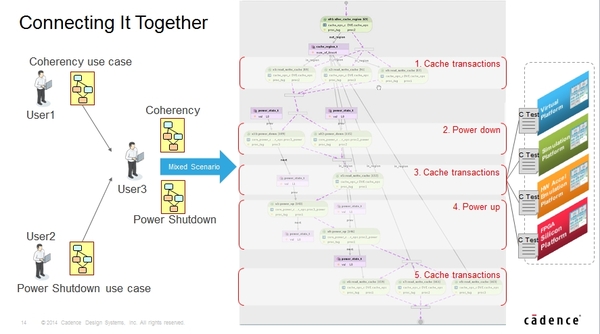

シナリオの記述においてデータ量のパラメータや使用するリソースの条件、処理の順序などを変更すれば、「Perspec™ System Verifier」はその制約条件に応じたテストコードを自動的に出力してくれるほか、複数のシナリオを組み合わせてテストコードを自動生成する事も可能。例えば、キャッシュ・コヒーレンシを確認するシナリオとパワー・シャット・オフを確認するシナリオを組み合わせて、パワー・シャット・オフしてもキャッシュ・コヒーレンシは大丈夫か?といった事を確認するテストコードを生成することも出来る。

「Perspec™ System Verifier」の生成したテストコードは、同社のシミュレータ、エミュレータ、バーチャル・プラットフォーム、FPGAプロトタイピング環境、いずれの環境でも利用する事が可能。テスト結果のカバレッジは、連携する同社の検証プロジェクト管理ツール「vManager」を用いて確認できる。

「Perspec™ System Verifier」の利用にあたってはUMLの記述が一つの壁となるが、CadenceはUMLのサンプルを含んだチュートリアルを用意しているという。

2014.12.12

2014年12月11日、Cadenceはソフトウェア・ドリブンSoC検証向けの新製品「Perspec™ System Verifier」を発表した。

「Perspec™ System Verifier」はソフトウェアを用いたSoC検証のためのツールで、簡単に表現すると、SoCの仕様情報とユーザーが定義したシナリオからCのテストコードを自動生成してくれるツールである。同種の製品としては、Breker Verification Systemsが「TreKSoC」という製品を出しているが、Cadenceの「Perspec™ System Verifier」はそのコンセプトからして大きく違う。

「Perspec™ System Verifier」の目指すのは、同社がこれまで培ってきた制約付きランダム的な考え方やカバレッジ手法をソフトウェア・ベースのダイレクト・テストに取り込む事で、ユーザー、検証環境、検証の抽象度を問わないソフトウェア・ドリブンSoC検証の実現がコンセプトとなっている。

「Perspec™ System Verifier」の具体的な使用法としては、まずCのテストコードを生成するためにSoCを構成するリソースの情報、それら各リソースの機能/動き、接続、Cのテンプレートを用意する。

次にシナリオとしてSoCにして欲しい動作、どのように動いて欲しいかをUMLのアクティビティ・チャートで定義する。そうすると「Perspec™ System Verifier」は、前提となるリソース情報から与えられたシナリオに矛盾しないあらゆる処理パターンを自動的に洗い出しそれをCのテストコードとして出力。同テストコードを使えば、シナリオ通りにハードがアクティベートされたかどうか、どのようにハードがチェックされたかを確認出来る。

シナリオの記述においてデータ量のパラメータや使用するリソースの条件、処理の順序などを変更すれば、「Perspec™ System Verifier」はその制約条件に応じたテストコードを自動的に出力してくれるほか、複数のシナリオを組み合わせてテストコードを自動生成する事も可能。例えば、キャッシュ・コヒーレンシを確認するシナリオとパワー・シャット・オフを確認するシナリオを組み合わせて、パワー・シャット・オフしてもキャッシュ・コヒーレンシは大丈夫か?といった事を確認するテストコードを生成することも出来る。

「Perspec™ System Verifier」の生成したテストコードは、同社のシミュレータ、エミュレータ、バーチャル・プラットフォーム、FPGAプロトタイピング環境、いずれの環境でも利用する事が可能。テスト結果のカバレッジは、連携する同社の検証プロジェクト管理ツール「vManager」を用いて確認できる。

「Perspec™ System Verifier」の利用にあたってはUMLの記述が一つの壁となるが、CadenceはUMLのサンプルを含んだチュートリアルを用意しているという。

2014.12.12

2014年12月9日、Synopsysは新型の配置配線ツール「IC Compiler II」の一般リリースを発表した。

「IC Compiler II」は今年3月に発表された新型の配置配線ツールで、既存製品よりも総合的なインプリメントの処理で10倍もの能力を発揮するとされている。

Synopsysによると「IC Compiler II」は既に今年6月から主要顧客への提供が開始されており、実チップの設計で幅広く利用が進んでいる。今回リリースされた最新バージョン 2014.12は、マルチ・オブジェクティブ・クロック/データ同時最適化、最先端ローパワー最適化など幾つかの新機能が追加された他、10nmプロセスを新たにサポート。同バージョンから一般顧客への提供も開始された。

発表に寄せられたルネサスシステムデザインの加賀谷氏のコメントによると、同社において「IC Compiler II」は既に製品差別化において無くてはならないソリューションとなっており、ルネサスでは40nmから28nmおよびそれ以降の全ての進行中のチップ開発に「IC Compiler II」の適用を拡大しているという。

※画像はSynopsys提供のデータ

2014.12.12

2014年11月6日、Synopsysは京セラドキュメントソリューションズが同社のカスタム・プロセッサ開発ツール「Processor Designer」を採用した事を発表した。

発表によると京セラドキュメントソリューションズは、次世代多機能プリンター向け高性能DSPの開発で「Processor Designer」を採用。これによりソフトウェア開発キットとRTLの生成にかかる工数を目標としていた開発期間よりも9ヶ月も早くDSPの開発を完了した。

工数を大幅に短縮出来たのは「Processor Designer」を利用すれば、LISA言語で記述したDSPの仕様記述から、合成可能なRTLと命令セットシミュレータ/アセンブラ/リンカ/デバッガ/Cコンパイラなどのソフトウェア開発キットを自動生成できるため。

※画像はSynopsys社Web上で公開のデータ

京セラドキュメントソリューションズのモチベーションは、画像処理用の専用ハードを高性能DSPに置き換える事でプリンター・ファミリー製品の機種間の差異に柔軟に対応する事にあった。「Processor Designer」を用いることで画像処理機能に合わせてDSPアーキテクチャの最適化に専念でき、結果として汎用DSPよりも高性能なDSPを短期間で実現した。

2014年12月5日、SynopsysはFaraday Technologyが同社の仮想プロトタイピング・ソリューション「Virtualizer」を採用した事を発表した。

発表によるとFaradayは、マルチメディア/ネットワーキング/ディスプレイ機器向けの様々なSoCデザイン向けのソフトウェア開発キットを開発するために「Virtualizer」を採用した。Faradayの開発するソフトウェア開発キットは、同社の顧客に提供するためのもので、これを利用する事でFaradayの顧客はFaradayに依頼したSoCの設計が完了する前(最大12ヶ月前)にソフトウェアの開発に着手できるようになる。

Faradayが「Virtualizer」を使用して開発するソフトウェア開発キットは、同社が持つ様々なIPのTLMモデルを組み合わせたもので、それらTLMモデルは「TLM Creator」という「Virtualizer」の付属ツールを用いて短期間で開発できるという。

Synopsysはソフトウェア先行開発用に使用するバーチャル・プラットフォーム・ベースのソフトウェア開発キットを「VDK」と呼び、自ら各種「VDK」を開発して顧客に提供しているが、最近はSoCベンダが自ら「VDK」を開発し顧客に提供するというケースが出てきているようだ。

※画像はSystemC Japan 2014での日本シノプシス講演データ

2014.12.12

2014年12月2日、CadenceはHuaweiの子会社Hisiliconによる同社製品の採用を発表した。

発表によるとHisiliconは、16nmのFinFET設計向けにCadenceのデジタル、カスタム/アナログ各種ツールとIPの採用を大幅に拡大した。

Hisiliconは今年9月に業界初となるTSMC 16nm FinFETプロセスを用いたARMベースのネットワーク・プロセッサの設計に成功しており、それを受けてCadence製品の採用拡大を決定した。Cortex-A57ベースの32コア、最大2.6GHz動作の同ネットワーク・プロセッサは、3D-IC設計ツール、エミュレーターを含むCadenceの各種デジタル/アナログ設計ツールとDDR4のIPを用いて設計されたようだ。

尚、今回の16nmのFinFET設計向けのツール採用拡大と合わせて、Hisiliconは10nmおよび7nmプロセス向けの設計フローの構築に向けて、Cadenceと協力強化の契約を締結したという事だ。

今回Hisiliconに採用されたツールは以下の通り。

・デジタル設計ツール

Encounter® Digital Implementation System

Tempus™ Timing Signoff Solution

Voltus™ IC Power Integrity Solution

Quantus™ QRC Extraction Solution

Incisive® Enterprise Simulator

・カスタム/アナログ設計ツール

Virtuoso®カスタムデザイン・プラットフォーム

Spectre®シミュレーション・プラットフォーム

Physical Verification System

Litho Physical Analyzer

CMP Predictor

・3D-IC設計ツール

Encounter Digital Implementation System

Allegro®

Voltus

Sigrity™ソリューション

2014.12.12

2014年11月12日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、同社の論理シミュレータ「Riviera-PRO」の機能強化を発表した。

発表によると、「Riviera-PRO」の最新バージョン2014.10では、ユーザーの定義した要求ベースのテストプランとカバレッジ・メトリクスをリンクさせることが可能となった。

具体的には、ユーザーがExcelなどのスプレッドシートで記述したテストプランをXMLに変換してカバレッジ・データベース・ファイルとして「Riviera-PRO」インポートし、シミュレーション実行結果から集めたカバレッジ・データベースにテストプランのセクションをリンクできる。これによりテストプランとカバレッジの相関を見ながら効率的に検証の進捗を確認する事が可能。「Riviera-PRO」にはテストプランとカバレッジの相関に関するレポート出力機能も備えられている。

具体的には、ユーザーがExcelなどのスプレッドシートで記述したテストプランをXMLに変換してカバレッジ・データベース・ファイルとして「Riviera-PRO」インポートし、シミュレーション実行結果から集めたカバレッジ・データベースにテストプランのセクションをリンクできる。これによりテストプランとカバレッジの相関を見ながら効率的に検証の進捗を確認する事が可能。「Riviera-PRO」にはテストプランとカバレッジの相関に関するレポート出力機能も備えられている。

Aldecは、カバレッジ結果のチェックに頼るだけでなく、要求ベースのテストプランとカバレッジ・メトリクスを相関させることで、より高速で効率的なカバレッジ・クロージャ手法ができるようになるとしている。

2014.12.11

2014年12月10日、日本EDAベンチャー連絡会(略称:JEVeC)は、「JEVeC会員紹介冊子-201412」(第3版)の発行をアナウンスした。

JEVeCはその名の通り国内EDAベンチャーの連絡会で設立から8年が経つ。正会員は17社で学術会員として大学教授5名が名を連ねている。

ハードウェアの設計現場で利用されるEDAツールの大半が海外EDAベンダ製となった現在、国内EDAベンチャーのビジネス環境は決して良い状況とは言えないが、例えばミニマル・ファブなど日本独自の動きと同調した活躍に期待したい。

2014.12.09

2014年12月5日、(株)半導体理工学研究センター(STARC)は、「STARCシンポジウム2015」の開催をアナウンスし同セミナーの申し込み受付を開始した。

STARCの発表によると「STARCシンポジウム2015」では、半導体関連産業界が取り組むべき方向として、「IoT」そして「設計メソドロジの深耕」という2つのテーマを掲げ、それらテーマに則したプログラムを用意。

具体的にはIoT関連の講演として、米GE(General Electric)のグローバル・リサーチセンター 日本代表 浅倉 眞司氏が同社の提唱する「Industrial Internet(産業機器とITの融合)」について講演。

設計メソドロジ関連としては、名古屋大学 准教授 本田 晋也 氏がシステムレベル設計にフォーカスした講演を行うほか、九州大学 教授 村上 和彰 氏をモデレータに迎えたパネル・ディスカッション『「クラウド、IoT、ビッグデータ」時代のシステム設計のあり方とは?』(仮題)が企画されている。

また、STARC共同研究に関連する全国の学生によるショート・プレゼンテーション、ポスター・セッションも例年通り実施される予定で、セミナー終了後は関係者/参加者によるレセプションが行われる予定となっている。

「STARCシンポジウム2015」の参加は無料。申し込みは下記STARCホームページより。

http://www.starc.jp/cd_event/sympo2015/

2014.12.08

2014年12月2日、高位合成ツールをはじめフォーマル検証ツール、ローパワー設計ツールを手掛けるCalypto Design Systemsは、同社高位合成ツールの新バージョン「Catapult 8」を発表した。

発表によるとCalyptoは今回発表した「Catapult 8」を第三世代の高位合成ツールと称しており、初期の市場を形成した第一世代の高位合成、入力がSystemCとC/C++ベースとなり、人手と同等の自動化を実現した第二世代の高位合成よりも、設計・検証の両面で大幅に生産性を向上できるとしている。

具体的には、Calyptoが「Catapult 8」の特徴としている下記5つが設計および検証の生産性を向上するための大きな柱となっており、Calyptoは「Catapult 8」によって高位合成の導入障壁多くを解消できると主張する。

・複雑な設計を収束させるために必要なユーザーからの制御性と予測性

・10倍のキャパシティを持つ、包括的な設計管理とデザインの組み立て機構

・標準的な機能検証メソドロジとの統合

・パワーと検証に最適化されたレジスタ・トランスファ・レベル(RTL)コード

・SystemCとC++の2つの言語をネイティブにサポート

今回発表された「Catapult 8」は、一つ前のバージョンである「Catapult 7.2」から導入された新しい高位合成アーキテクチャーで構成されており、SystemCとC++をネイティブにサポート。合成品質やキャパシティなど高位合成のコアも含めた機能改善が図られているほか、検証手法やローパワー手法など高位合成をより効果的に運用するための技術をサポートしており、それを競合製品との差別化ポイントとしている。

またCalyptoは新製品「Catapult 8」のリリースと合わせて高位合成用のライブラリ「CatapultCatware」の提供を開始。「CatapultCatware」はパラメータ化され簡単に設定変更が可能なSystemC/C++のソースコード・ライブラリで、フィルタやFFTなど各種広範なライブラリが用意されているという。

※画像は全てCalypto Design Systems提供のデータ

2014.12.05

2014年12月2日、米SIA(Semiconductor Industry Association)は、2014年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年10月の世界半導体売上は前年同月比9.6%増、前月比1.5%増の296.9億ドルで6月から5ヶ月連続で単月の売上記録を更新した。

2014年10月の売上を地域別に見ると為替の圧力の強い日本市場以外は全て前年比増を達成。アジアと北米市場は共に12%を超える伸びを示した。前月の実績に対しては北米市場が5.8%増と伸び率が最も大きかった。

先出の

WSTSの2014年秋季半導体市場予測によると、2014年の日本市場はドルベースでは前年比1.3%増と僅かな成長に留まっているが、円ベースでは7.1%増の成長で市場規模約3兆6400億円になると見られている。

2014.12.05

2014年12月4日、Synopsysは、2014会計年度第4四半期(14年8月-10月)の四半期決算を報告した。

発表によると、Synopsysの2014会計年度Q4の売上は、前年同時期比約6.7%増、前期Q3比約3.3%増の5億3900万ドルでまたもや同社の四半期売上記録を更新した。純利益は前年同時期比約9.7%増の6245万ドルだった。

Synopsysの2014会計年度の売上合計は前年比約4.8%増の20億5747万ドルで過去最高。純利益は前年比約4.5%の計2億5912万ドルとなっている。(※GAAP基準による会計結果)

Synopsysはこの8月-10月の間に、「DesignWare Sensor and Control IP Subsystem」、「USB 3.1 IP」、「DesignWare ARC HS38プロセッサ」、といった新たなIPソリューションや、新たな検証ソリューション

「Verification Continuum platform」を発表している。

Synopsysは次の2015会計年度Q1(14年11月-15年1月)の売上を5億3500-4500万ドルと予測。年間売上に関しては2014会計年度を上回る21億8500-22億2500万ドルと予測している。

2014.12.05

2014年11月20日、Mentor Graphicsは、2015会計年度第3四半期(14年8-10月)の売上を報告した。

発表によると、Mentorの2015会計年度Q3の売上は、前年比約6.2%増、前Q2比約12.4%増の2億9268万ドル、営業利益は前年を下回る2100万ドルだった。この実績はQ2実績報告時の予測を上回るもので同社のQ3実績としては過去最高を記録した。(※GAAP基準による会計結果)

Mentorの今期Q3の売上の内訳を見ると、バックエンド設計分野、北米市場が伸びている様子。

MentorはこのQ3(8-10月)の間にPCB設計ツールの新製品「Xpedition Systems Designer」を発表。ニュースとしては組み込みシステム開発向けのソリューションに関するものが多かった。

Mentorは次期2015会計年度Q4(14年11-15月1月)の売上を4億2500万ドル程度と予測しており、この数字は同社のQ4売上記録を上回るものとなる。

2014.11.26

2014年11月19日、名古屋大学、富士ソフト、ASTC、TOPPERSプロジェクトが連名でTOPPERS/ATK2のルネサスRH850対応とその一般公開を発表した。

発表によると名古屋大学らTOPPERSプロジェクトの関連チームは、これまでルネサスのマイコン「RH850」に対応していなかったAUTOSARベースのRTOS「TOPPERS/ATK2」を同マイコンに対応すべく活動。ソースコードの開発は名古屋大学 大学院情報科学研究科 附属組込みシステム研究センター(NCES)が行い、それを富士ソフトが検証。開発はASTCの提供する「RH850」のバーチャル・プラットフォームを用いて行われた。

今回開発された「TOPPERS/ATK2」のルネサスRH850対応版は、「RH850/F1L」および「RH850/F1H」に対応しており、他の品種にも移植が容易な構造となっているとの事。TOPPERSの開発する車載向けRTOSとしては既にOSEK/VDX仕様に準拠した「TOPPERS/ATK1」があり、日産は同RTOSを市販車シーマ、フーガ、スカイラインのハイブリッド制御モジュールに使用している。「TOPPERS/ATK2」は「TOPPERS/ATK1」に続く第二世代の車載向けRTOSとして開発されたもので、現在も機能安全規格対応や時間パーティショニング機能の追加などエンハンスが進められている。

「TOPPERS/ATK2」の開発に使用されたASTCのバーチャル・プラットフォームは「VLAB」という製品名で、業界では後発といえる環境ながら車載分野をはじめ各種組み込みソフトの先行開発で実績を上げている。

ASTCはRH850のユーザー向けに「VLAB RH850 バーチャルプラットフォームツールボックス」を用意しており、これを用いる事でセーフティ、シャーシ、ハイブリッドモーター、エンジンコントロール、ボディ向けの各種「RH850 ファミリ」をターゲットとしたソフトウェア開発が可能。同ツールボックスには、RH850 IPブロックの各モデル、MCUの各シリーズのネットリスト、ターゲットソフトウェアのサンプルコード、起動スクリプトそしてドキュメントが同梱されており、今回の「TOPPERS/ATK2」RH850対応版の開発にもこれらが用いられたようだ。尚、ASTCの「VLAB」環境は、MathWorksのMATLAB/Simulink、 Green HillsのMULTI IDE、VectorのCANoe等ECU開発で使用される各種主要ツールとのインタフェースも備えている。

ルネサスRH850対応の「TOPPERS/ATK2」は、TOPPERSのWebサイト上で一般公開されている。

2014.11.05

2014年11月3日、米SIA(Semiconductor Industry Association)は、2014年9月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年9月の世界半導体売上は前年同月比8%増、前月比1.6%増の290億ドルでまたもや単月の売上記録を更新。今年6月から4ヶ月連続の記録更新となる。

売上を四半期単位で見ると、2014年Q3(7-9月)の売上は前年比8%増の計870億ドル。好調だったQ2(4-6月)売上823億ドルを更に上回った。

2014年9月の売上を地域別に見ると最大市場のアジアと北米市場が共に伸び、欧州および日本市場は若干売上を落とした。しかし3ヶ月単位の平均売上額は全ての地域でQ3実績がQ2実績を上回った。

2014.10.29

2014年10月28日、Mentor Graphicsは、複数ボード・システム開発向けの新製品「Xpedition Systems Designer」を発表した。

発表によると新製品「Xpedition Systems Designer」は、複数のボードで構成されるシステムのシステム設計において、論理システムの定義も含めて個々のボードのハードウェア記述を取り込み、マルチレベルのシステム設計の同期プロセスを自動化することが可能。

複数のボード設計に対応する環境は市場にも存在しているが、ボード上の論理システムの定義を完全に細部まで取り込み複数のレベルとドメインを通じて設計変更を自動的に同期する「Xpedition Systems Designer」のようなソリューションはこれまで存在していなかった。

「Xpedition Systems Designer」のシステム設計テクノロジを利用することで、チームによるコンカレント設計での設計の完全性と一貫性を実現でき、接続エラーを排除した生産性の高いシステム開発を実現できる。

※メンター・グラフィックス・ジャパン株式会社

http://www.mentorg.co.jp

2014.10.29

2014年10月21日、インターコネクトIPのSonicsは、仏Magillem社とのコラボレーションを発表した。

発表によるとSonicsは、MagillemのIP-XACTチェッカーを顧客に提供する開発環境に取り込み、自社NoC IPのバリデーション・プロセスで利用。SoC設計フローへのIPインテグレーションに役立てる。

MagillemのIP-XACTチェッカーは、言わばIEEE-1685 IP-XACT規格の純正コンプライアンス・チェッカーであるため、IP-XACT対応の環境でモデル・チェックに利用できる。

尚、聞いた話では元々Sonicsの環境に組み込まれているNoC生成にもMagillemツールが使われているとの事。IP-XACTベースのMagillemの環境はトップのRTL Netlistの他に仮想プラットフォームやテストベンチ、Cドライバ、UVM、UPF/CPF、アナログ・モデル、各種ドキュメント・データなど様々なコード自動生成機能を持っている。

2014.10.29

2014年10月29日、Synopsysは業界初となるUSB 3.1対応のIPソリューションを発表した。

発表によると今回Synopsysが開発したのは、USB 3.1デバイス・コントローラIP、検証IP、USB 3.1の仮想プラットフォーム・キット(VDK)の3つ。今年7月に策定されたUSB 3.1仕様に対応するIPソリューションは業界初となる。

SynopsysによるとUSB 3.1対応機器は、ハブやドッキング・ステーションなどホスト側デバイス、SSDなどが2015年から登場する見通しで、今回はまずデバイス・コントローラの設計IPとSystemVerilogベースの検証IPを用意した。USBのIPに関してはSynopsysが市場シェアの半分以上を握っており実績も多数。USB 3.0のコントローラIPを使ったSoCの出荷数は1億個以上、検証IPは100以上のSoC開発で利用された実績がある。

今回発表したUSB 3.1 デバイス・コントローラIPの構造は以下の図の通りで、実績のある既存のUSB 3.0のIPをベースに作られている。一つのIPでUSB 3.1/3.0.2.0に対応可能で当然ながらUSB 3.1の10Gbpsのデータ転送速度に対応する事が可能。既存のSynopsysのUSB 3.0 IPのユーザーはUSB 3.0のドライバをそのまま利用できる。

また今回はデバイス・コントローラIP、検証IPに加えてUSB 3.1のバーチャル・モデルも用意。Synopsysはこのバーチャル・モデルを「ARM Cortex-A57 Versatile Express Board」のバーチャル・プラットフォームと合わせてパッケージした「USB 3.1 IP VDK」として提供する予定。同VDKはSynopsysのバーチャル・プロトタイピング環境「Virtualizer」で動くソフトウェア開発向けの環境で、Linaro Linuxで実行可能。USB 3.1のサンプル・ドライバも付属される。

Synopsysは既に開発したUSB 3.1 デバイス・コントローラIPを自社のFPGAプロトタイピング環境「HAPS」に実装しデモを披露した事もあり、同IPを利用するユーザーは同じようにHAPS環境を用いて開発を進める事ができる。ちなみにSynopsysでは全てのIPのバリデーションをHAPSで実施しているという。

発表されたUSB 3.1 デバイス・コントローラIPと検証IPは既に出荷中で、VDKの提供は2015年Q1から。USB 3.1 PHY IPは現在開発中で来年以降に提供される計画である。

※画像は全てSynopsys提供のデータ

2014.10.28

2014年10月、Cadenceはこの1ヶ月の間に4種の設計/検証IP新製品を立て続けに発表した。

10月14日に発表した「MIPI SoundWire Controller IP」は、MIPI Allianceの策定したデジタル・オーディオの新しいインターフェイス仕様「MIPI SoundWire」を実装した設計IPで同規格準拠の設計IPは業界初。Cadenceは既に同規格の検証IPをリリースしている。

一般顧客には年内に提供が開始される予定。

10月17日に発表した「DDR4/LPDDR4マルチプロトコルIP」は、文字通りDDR4とLPDDR4に対応するコントローラ及びPHY IPで単一のIPで両規格をサポートする設計IPは業界初。

同IPは最大転送速度3200Mbpsまで対応しているため、より高性能なDDR4およびLPDDR4 DRAMが利用可能になった時にもそのまま利用可能。また、チップの再設計をせずに容易にDDR4からLPDDR4に移行できる。

一般顧客には年内に提供が開始される予定。

10月27日に発表した「3Dメモリー向け検証IP」は、Wide I/O 2、Hybrid Memory Cube(HMC)、High Bandwidth Memory(HBM)、DDR4 3D Stacking(DDR4-3DS)等、各種メジャーな3Dメモリー規格全てに対応するもので、今後の普及が見込まれる各種3Dメモリーとの正確なインターフェイスを検証することができる。

同製品は既に製品出荷中。

10月28日に発表した「25G Ethernet 検証IP」は、25G Ethernet Consortiumによって策定された25ギガビットEthernet規格に対応した検証IPで業界初。MACとPHYの両方の検証に対応しているほか、25G Ethernet規格に含まれる、40Gと比較してポートを半減し25%増の帯域幅を実現する50Gの定義にも対応している。

同製品の出荷状況は不明。

尚、各種IP製品の拡張に力を注ぐCadenceは、ユーザーの評判やポートフォリオ、技術サポート力などから、同じく今年10月にTSMCのアワード「TSMC Partner of the Year」のSoft IP部門を受賞している。

2014.10.27

2014年10月23日、Cadenceは自動車向けの新ソリューションとして、機能安全規格ISO 26262向けの検証ソリューションを発表した。

Cadenceの発表によると新たな機能安全ソリューションは、同社の機能検証プラットフォーム「Incisive」をベースとしたもので、機能安全規格ISO 26262への準拠手順の自動化をサポートするもの。

Cadeceはこれまでインタープリター式のシミュレーション・エンジンを用いた機能安全シミュレーションを提供していたが、今回「Incisive Enterprise Simulator」のコンパイル式のシミュレーション・エンジンで動作する新型の「Incisive Functional Safety Simulator」を開発。これにより故障注入シミュレーションのシミュレーション性能を最大10倍に向上させた。

更に「Incisive」向けの検証マネジメント環境「Incisive vManager」に新たに「Functional Safety Analysis機能」を用意し、機能安全リグレッション解析の効率化を実現した。同機能を用いることでシミュレーターで作成した故障事象から安全性検証リグレッション・テストを自動生成し、シミュレーション結果からの安全性のメトリクス追跡を自動化出来るようになるという。

同機能安全ソリューションは現在一部限定カスタマー向けに提供中で、一般向けには2015年前半に提供開始となる予定。

ここ数年、自動車業界を意識したISO 26262に向けた取り組みはEDA業界でも一つのトレンドとなっており、以下のような数々の機能安全向けソリューションが既に存在している。

・Aldecのリントツール「ALINT」

・Synopsysの「VDK(Virtualizer Development Kits)」

・Synopsysno「ARC EM SEP」※IPコア

・Mentor Graphicsの「Tessent TestKompress」

・OneSpin Solutionsのフォーマル検証ソリューション

2014.10.27

2014年10月21日、CadenceはGlobal Unichipによる成功事例を発表した。

Cadenceの発表によるとTSMCの設計子会社であるGlobal Unichipは、同社初となるTSMC 16nm FinFET Plusプロセスを用いた製品デザインをCadenceのインプリメント・ツール(Encounter Digital Implementation System)でテープアウトした。

Global Unichipが設計したのは計算用途向けのASICで、以前のデザインと比較してシステム性能を2倍、周波数を18%向上させ、消費電力は28%削減できたとしている。以前のデザインの詳細は不明だが今回のデザインは1億8000万ゲートで、Global UnichipはCadenceの協力を得て設計からテープアウトまで3ヶ月で完了できたという。

ちなみにGlobal Unichipは、TSMC 20nmプロセスの最初のテスト・デザインにおいてもCadenceの「Encounter Digital Implementation System」を使用していた。(※関連ニュース)

2014.10.22

2014年10月21日、Xilinxは自社の設計環境「Vivado Design Suite」のバージョンアップを発表した。

Xilinxは今回、「Vivado Design Suite」と合わせてSDKもアップデートし、「UltraFast™ エンベデッド設計手法ガイド」と呼ぶARM搭載FPGA「Zynq」向けのドキュメントの提供を開始した。

最新の「Vivado Design Suite 2014.3」では、内蔵する高位合成ツール「Vivado HLS」とIP統合ツール「Vivado IP Integrator」の機能強化が図られており、SDKには性能のモニタリング機能と可視化機能が新たに追加された。

Xilinxはこれら最新の開発環境と「UltraFast エンベデッド設計手法ガイド」を組み合わせて使用すると生産性が10倍以上向上できることを実証済としている。

2014.10.22

2014年10月20日、FPGAベースのプロトタイピング・システムを手掛ける独ProDesignは、新製品「proFPGA Zynq 7000 FPGA Module」のリリースを発表した。

発表によると「proFPGA Zynq 7000 FPGA Module」は、同社のプロトタイピング・システム「proFPGA」ファミリ製品向けのオプション・モジュールで、「proFPGA Virtex 7 2000T FPGA module」等の他のオプション・モジュールと併用してのプロトタイピング・システム「proFPGA」の環境に接続できる。

製品としてはXilinxの「Zynq XC7Z100」または「Zynq XC7Z045」のいずれかを搭載する形で2種類あり、各モジュールのインタフェース等の詳細は下記Webページ参照。

尚、同社CEOのコメントによると、ProDesignは2012年に市場デビューしてから既に世界10カ国、30社以上の半導体ベンダを顧客に持っているという。

2014.10.22

2014年10月20日、業界標準ツール「SpyGlass」をはじめとしたRTL解析ソリューションを手掛けるAtrentaは、Kodak Alaris社が同社のCDC検証ツール「SpyGlass CDC」を採用した事を発表した。

発表によるとKodak Alarisは、社内のFPGA設計フローの強化に伴いAtrentaのCDC検証ツール「SpyGlass CDC」を採用。

Kodak Alarisは、Atrentaから提供された「スマート・モデル」と呼ばれるFPGAベンダ製IPの抽象モデルを利用することで、CDC検証の効率化を果たしたとしている。

2014.10.22

2014年10月14日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは増資を発表した。

発表によるとS2Cは三回目となる資金調達でベンチャー・キャピタルらから計460万ドルを調達。S2Cはこの資金を元にプロトタイピング・システムの研究開発を推進。既に販売とサポート・チャンネルの拡大を実施している。

詳細は明らかにされていないが、S2Cは自社のプロトタイピング・システムをクラウド・ベースのソリューションへと進化させる計画があるようだ。

2014.10.21

2014年10月20日、Cadenceは、2014会計年度第3四半期(2014年7-9月)の売上を報告した。

Cadenceの2014年Q3(7-9月)売上は、前年同時期比約9%増、前期Q2比約5.5%増の4億ドル。純利益は前年より微減の3800万ドルだった。(※GAAP基準による会計結果)

前Q2は5年振りの売上横這いだったがQ3は再び売上増に転じる結果となった。

Cadenceの社長兼CEO Lip-Bu Tan氏のコメントによると、先端プロセス向けのビジネス、Incisiveシリーズの検証ソリューション、そしてIP分野の売上が好調との事。

Cadenceは、来期Q4の売上額を4億1700-2700万ドルと予測している。

2014.10.21

2014年10月20日、Xilinxは2015会計年度第2四半期(2014年7-9月)決算を報告した。

Xilinxの2015会計年度Q2の売上は、前年同時期比1%増、前期Q1比1%減の6億400万ドル。営業利益は前年比22%増の2億ドルだった。(※GAAP基準による会計結果)

売上額はQ1に続いてQ2も前四半期を下回る格好となったが、Q2の利益率は33%と高く昨年を上回る数字となった。売上減の要因は28nm製品を中心とした新製品カテゴリの販売実績によるものと想像できるが、XilinxのCEOはQ3に28nm製品の売上が大幅に回復すると予測している。

XilinxのQ2売上を地域別でみると、アジア地域の売上比率が落ちた分、北米の売上比率が増加した。製品分野別の売上では、前Q1で不調だった航空・防衛分野の売上が回復した。製品別売上では、これまで右肩上がりで伸びてきた主力の新製品カテゴリ(Virtex-7, Kintex-7, Zynq-7000, Virtex-6, Spartan-6)の売上比率が前Q1の45%から43%へと初めて下がった。

Xilinxは、次期2015年Q3(14年10-12月)の売上を今期実績の0%-4%増と予測をしている。

2014.10.08

2014年10月6日、ESLソリューションを手掛ける米Carbon Design SystemsとSoCのテストケース自動生成ツールを手掛けるBreker Verification Systemsは、両社製品のインテグレーションを発表した。

発表によると両社はCarbonの提供する仮想プロトタイピング・キット「CPAK(Carbon Performance Analysis Kits)」とBrekerの提供するSoCのテストケース自動生成ツール「TrekSoC」とのダイレクト・リンクを用意。これによりバーチャル・プラットフォームのユーザーが「TrekSoC」の生成するSoCセルフ・チェック用のCのテストケースを利用してSoCの機能やアーキテクチャを確認できるようになる。

既に製品として「TrekSoC」とのリンクを備えるARM Cortex-A15ベースの「CPAK」が用意されており、「TrekSoC」本体と合わせてCarbonのWebサイト「IP Exchange」を通じて提供が開始されている。Carbonは「TrekSoC」と繋がる「CPAK」を順次追加していく予定だという。

2014.10.07

2014年10月3日、Synopsysは富士通セミコンダクターによる同社インプリ・フローの成功事例を発表した。

発表によると富士通セミコンダクターはSynopsysのインプリ・フローを用いてARM big.LITTLE技術を採用した「ARM Mali-T624」GPU搭載のマルチコアの高性能画像処理プロセッサ「MB86S70」を開発。性能を犠牲にすることなく30%以上ものリーク電流を削減する事に成功した。

富士通セミコンダクターが使用したSynopsysのインプリ・フローは、論理合成ツール「Design Compiler Graphical」、配置配線ツール「IC Compiler」、スタティック・タイミング・サインオフ・ツール「PrimeTime」によって構成されるもので、富士通セミコンダクターはこれらツールで実現されるUPFベースの階層ローパワー設計フローを用いて6000万ゲートのデザインを28nmプロセスで実装した。

富士通セミコンダクターの「MB86S70」は、「ARM Mali-T624」GPUを4個、「ARM Cortex A15」と「Cortex-A7」を2個づつ搭載する大規模画像処理プロセッサで、設定した非常に高い消費電力/性能目標をクリアするために、多電源や機能ブロック単位の電圧調整といった最先端のローパワー・マネージメント・テクニックを駆使することで目標を上回る消費電力と性能を実現したという。

「PrimeTime」などSynopsysの単品ツールを用いた富士通セミコンダクターの事例は珍しくないが、先端SoC開発でSynopsysのインプリ・フローを使用したという事例発表は比較的珍しいと言える。ちなみに同成功事例は先日サンタクララで開催されたARMのイベント「ARM TechCon 2014」にて富士通セミコンダクターによって発表されたようだ。

2014.10.07

2014年10月3日、CadenceはARMによるエミュレータ/アクセラレータ「Palladium XP」の成功事例を発表した。

発表によるとARMは同社のGPU「Mali-T760」の開発にCadenceのエミュレータ/アクセラレータ「Palladium XP」を利用。自社の高速シミュレーション用プロセッサ・モデル「ARM Fast Models」と「Palladium Hybrid技術」を併用する事でハードウェアとソフトウェアの協調検証環境を構築し、OSの立ち上げ時間を50倍高速化する事に成功した。

「Palladium Hybrid技術」は、Cadenceのエミュレーション/アクセラレーション環境「Palladium」とCadenceのバーチャル・プロトタイピング環境「Virtual System Platform」をインテグレーションする技術で、ARMは同技術を用いて「Virtual System Platform」上に「ARM Fast Models」を用いたプロセッサ・サブシステムを構築。エミュレータ「Palladium XP」上の「Mali GPU」と接続してシステム全体の検証環境を実現したと見られる。

CadenceによるとARMは「Palladium Hybrid技術」を用いた協調検証環境により、既存のエミュレーション単体環境よりもハードウェアとソフトウェアの組み合わせテスト全体が10倍高速化できたとしている。

バーチャル・プラットフォームを構築する上で通常ネックとなるGPU部をエミュレータで処理する手法は今年の51DACにおいてもハイブリッド手法としてCadenceは強くアピールしていた。このようなハイブリッド・ソリューションを提供できるのは大手3社だけだが、今回ARMがCadenceの同ソリューションを用いたというのはインパクトのある話と言える。

※画像はWebサイトSemiWiki上で公開されていたNVIDIAの昨年のARM TechConでの発表資料。NVIDIAもARMと同じようにCadenceのハイブリッド手法を活用しているようだ。

2014.10.07

2014年10月6日、米EDA Consortiumは、2014年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

EDACの発表によると、2014年Q2の世界のEDA売上総額は、前年比6.3%増、前Q1比0.7%増の17億5790万ドルで、Q2の売上記録として過去最高を達成。四半期の売上記録が前年同時期を上回るのはこれで18四半期連続となる。

2014年Q2の売上を製品分野別に見ると、主力のCAE分野とIC PhysicalDesign&Verification分野が前年割れしたのに対し、IP分野とPCB分野がともに前年比20%以上の売上増と大きな成長を見せた。

2014年Q2の売上を地域別に見ると、日本市場以外は全て前年比増を達成しており、北米とアジアは二桁成長。日本市場は前年比16.6%減で遂に売上2億ドル台を割ってしまった。為替レートの影響を加味しても日本市場における売上はかなり落ち込んでいる状況にある。

2014年Q2時点でのEDA業界の従業員数は前年比6.7%増、前期Q1比2.7%増の31259人でQ1に続いて過去最高記録を更新した。

2014Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 5億9970万ドル 1.9%Down

■IC Physical Design & Verification分野 3億5790万ドル 4.8%Down

■IP分野 5億3200万ドル 23.2%Up

■サービス分野 8990万ドル 4.3%Up

■PCB/MCM分野 1億7840万ドル 20.3%Up

2014年Q2地域別の売上と昨年同時期との比較は以下の通り。

■北米 7億9440万ドル 11.2%Up

■ヨーロッパ 2億9040万ドル 3.5%Up

■日本 1億8920万ドル 16.6%Down

■アジアその他地域 4億8400万ドル 12.1%Up

2014.10.07

2014年10月3日、米SIA(Semiconductor Industry Association)は、2014年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年8月の世界半導体売上は前年同月比9.4%増、前月比1.3%増の284.4億ドル。単月の売上としては過去最高の金額となった。今年の半導体市場は過去最高のペースで売上が推移しており大幅な成長が予想されている。WSTS(WORLD SEMICONDUCTOR TRADE STATISTICS)が今年6月に発表した予測では2014年は前年比6.5%の成長としていたが、2014年8月までの累計売上金額は前年比10.1%となっている。単月売上で見ると15ヶ月連続で前年実績を上回る売上を叩きだしている。

2014年7月の売上を地域別に見ると日本市場以外の全ての地域で売上前年比増を達成。欧州、アジアともに前年比10%増以上の成長を示した。日本市場は為替の関係でドルベースでマイナス成長となっているが、売り上げ的には7月と同額の売上となっており、円ベースで見ると他の市場同様に前年比10%増近い成長となる。

2014.10.06

2014年10月3日、新横浜のホテルで今回が初開催となるセミナー「Design Solution Forum 2014」が催され、500名以上の参加者を集めた。

Design Solution Forum 2014 公式ページ

セミナーでは4つの会場に分かれて計42のセッションが実施され、セミナー終了後には展示会場にて交流会が行われた。

ここではフォト・レポートとして、Design Solution Forum 2014の様子をお届けします。

セミナー実行委員長の京セラドキュメントソリューションズ 岡田充弘氏の挨拶でセミナー開始。

基調講演はNTTドコモの二方敏之氏でIoTや5Gに関するお話。

NTTドコモ二方氏の基調講演は全ての会場に配信された。

セミナー参加者の投票で最優秀エンジニア講演賞を受賞した京セラドキュメントソリューションズ可児守氏の講演風景。投票は接戦で2位との差は僅か一票だった。同氏には賞品としてクロスバイクが贈られた。

セミナー参加者の投票でNECの若林一敏氏と同率首位で最優秀スポンサー講演賞を受賞したCMエンジニアリングの二見誠一氏。両氏には賞品としてカニ缶セットが贈られた。

各セミナー会場での講演風景。多数のセッションが満席となり、中には立ち見のセッションも。日立製作所 瀬能俊太郎氏の講演風景(下)

三菱電機マイコン機器ソフトウェア 石野禎将氏の講演風景(下)

わさらば合同会社 三好健文氏の講演風景(下)

富士通セミコンダクター 宮川 達氏の講演風景(下)

リコー 守田 直也氏の講演風景(下)

その他、エンジニア・セッション講演者の皆様。

富士通関西中部ネットテック 中野雅夫氏(左上)、モルフォ 平本一博氏(右上)、ニコン 高見亮氏、松本矩尚氏(左中)、富士通九州ネットワークテクノロジーズ 斎藤睦巳氏(右中)、リコー 小澤賢一氏(左下)、ルネサスシステムデザイン 植西俊哉氏(右下)

昼食はスポンサーの展示を見ながらのビュッフェ・スタイル。

高位合成ツールについて語ったHLSトークの風景。モデレータはセミナー実行委員のコニカミノルタ 河邊恭氏。

日本を明るくする検証ビジネスについて語ったVerificationトークの様子。モデレータはセミナー実行委員の富士通セミコンダクター 古手川博久氏。

ハード目線、ソフト目線、双方から組込みソフトのテストについて語った、Software-Testトークの風景。モデレーターはセミナー実行委員の京都マイクロコンピュータ 辻邦彦氏。

ユーザーにとって使い易いIPとは?について語ったIPトークの様子。モデレーターはセミナー実行委員のリコー 木村貞弘氏。

セミナー終了後の大交流会。開始直前の様子。300名近くの人が参加。

セミナーDesign Solution Forumは来年も更に規模を拡大して開催される予定。

※セミナーで行われたセッションの詳細については後日レポート記事を掲載する予定です。

2014.10.02

2014年10月1日からサンタクララで開催されているARMのプライベート・イベント「ARM TechCon 2014」にて今年もARMから幾つかの新たな発表が行われた。

ここでは現時点でARMが公式発表している最新の3つのプレスリリースについて取り上げる。

1.Cortex-Aシリーズプロセッサ向けにOpenCLをサポート

ARMは「OpenCL™ for ARM NEON™ technology」を発表した。プレスリリース文

ARMの「NEON」はCortex-Aシリーズプロセッサ向けに用意されたマルチメディア・フォーマット処理のための拡張SIMDエンジンで、「OpenCL™ for ARM NEON™ technology」によりCortex-AシリーズプロセッサでOpenCLフレームワークが利用可能となる。

「OpenCL™ for ARM NEON™ technology」でOpenCLがサポートされるプロセッサは以下の通り。

?Cortex-A7, Cortex-A9, Cortex-A15, Cortex-A17 (ARMv7)

?Cortex-A53, Cortex-A57 (ARMv8-A, 32-bit execution state)

2.IoT向けの「ARM mbed™ IoT Device Platform」を発表

ARMはIoT製品開発向けの環境として「ARM mbed™ IoT Device Platform」を発表した。プレスリリース文

「ARM mbed™ IoT Device Platform」にはARM Cortex-MベースのMCU向けの無償の「mbed OS」が含まれているほか、有償ライセンスとして「mbed Device Server」が用意される。

「mbed Device Server」は、IoTデバイスとIoT Cloudサービスを繋ぐソフトウェア製品で、IoTデバイスのプロトコルとウェブ・デベロッパーによって使用されるAPIの間のブリッジを提供する。

※mbed OSのアーキテクチャ

※画像はmbedのWebサイト掲載のデータ

3.TSMC 16nm FinFETデザイン向けのフィジカル・インプリメンテーション・ソリューションを発表

ARMはTSMC 16nm FinFETプロセス向けの新たなインプリメント・ソリューション「ARM Artisan® Power Grid Architect」と「ARM Artisan Signoff Architect」を発表した。プレスリリース文

「ARM Artisan® Power Grid Architect」と「ARM Artisan Signoff Architect」はいずれもTSMC 16nm FinFETプロセスをターゲットしたもので、「ARM Artisan® Power Grid Architect」はARMのTSMC 16nm FinFETプロセス向けフィジカルIPをインプリメントする際にFinFETデザイン・ルールに則した最適なパワー・ネットワークを作成可能。PPA改善のためのフロアプランニングを自動化する。「ARM Artisan Signoff Architect」は、既存のIPモデル・フォーマットには無いより正確なSBOCV(stage-based on-chip variation)サインオフ・メソドロジを提供する。

「ARM Artisan Signoff Architect」は今年10月、「ARM Artisan Signoff Architect」は今年Q4にそれぞれβ版がリリースされる予定となっている。

2014.10.02

2014年9月12日、新横浜のホテルでAtrentaのプライベート・セミナー「Atrenta Technology Forum 2014」が開催された。

同セミナーではAtrenta製品のユーザーとして、京セラドキュメントソリューションズ、富士通九州ネットワークテクノロジ、パナソニックデバイスシステムテクノ、スパンション・イノベイツの4社が事例講演を行った。

ここでは各社の事例と共に発表されたAtrenta製品の最新アップデートについてレポートする。

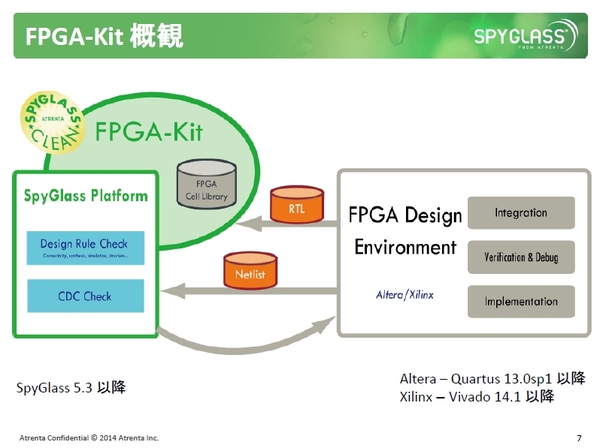

Atrenta製品として今回のセミナーでまず最初に紹介されたのは、新製品「SpyGlass FPGA-Kit」である。同製品は高度化するFPGA設計のニーズに応えるRTLの品質チェックのためのツールで、その実体はSpyGlassプラットフォームでFPGAデザインを検証するためのスクリプトウェアとAlteraおよびXilinxのセル・ライブラリとなる。

「SpyGlass FPGA-Kit」はFPGAデザイン(RTL)のルールチェックとCDCチェックに利用できるが、特徴的なのはAtrentaの強みの一つであるCDCチェック機能で、同梱されるFPGAライブラリにより簡単な設定でFPGAデザインのCDC検証環境をセットアップする事が可能。FPGAライブラリを含むサブブロック毎に同期化回路構造をチェックできる。また、CDCチェック機能としては、デザインの深い階層のリコンバージェンス・チェック、非同期リセットなどリセット構造のチェックも可能だ。

RTLシミュレーションだけでは実機動作が不安な複雑なFPGAデザインに対して、「SpyGlass FPGA-Kit」は一つの有効なソリューションと言えよう。

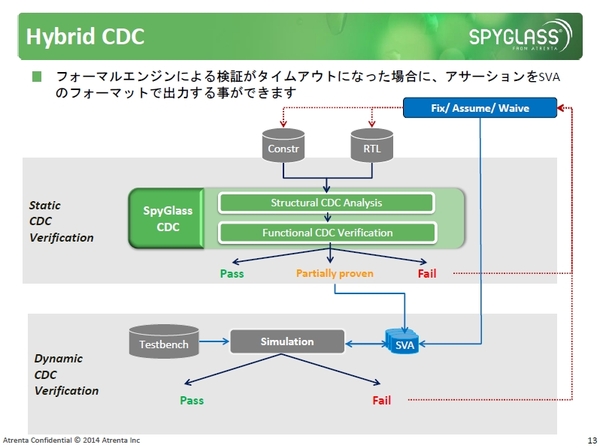

続いて「SpyGlass Platform」について。「SpyGlass Platform」のベース機能であるLintについては新たにSystemVerilog用のルールが追加されたほか、既存のSTARC準拠ルールの幾つかがSystemVerilogに対応した。また、デザイン中の同期FIFOを認識し、オーバーフロー/アンダーフローをチェックできる新たなルールも追加された。更にフォーマル検証のタイムアウト対策としてSVAを出力する機能も用意された。

CDC機能に関しては、同一ソースレジスタからの信号の同期化後の合流を検出する新ルールやLint同様にフォーマル検証のタイムアウト時にSVAを出力する機能が追加されたほか、擬似エラーのフィルタリング機能が改善された。

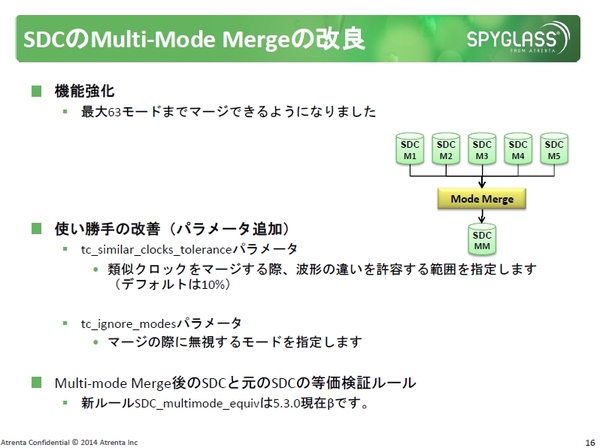

SDC機能に関しては、幾つかの新ルールに加え複数SDCモードのマージ機能が強化された。これまでは2モードしかマージ出来なかったが、新バージョンβ版では最大63モードまでマージ可能となった。

またマルチサイクルパスやフォルスパスをチェックする「SpyGlass TXV」のパフォーマンスが強化され、同一時間内により多くの制約を検証できるようになった。「SpyGlass TXV」は非常に好評でこの1年間だけで既に多数の国内企業が導入しているという。

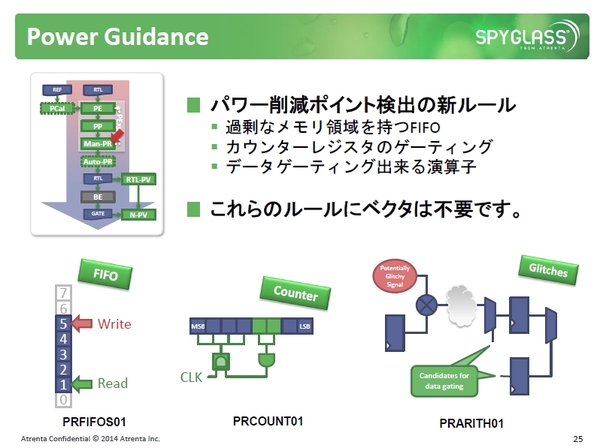

パワー解析を行う「SpyGlass Power」に関しては、パワー・リダクションのための新ルールが追加され、パワー削減のポイントを検出できるようになった。

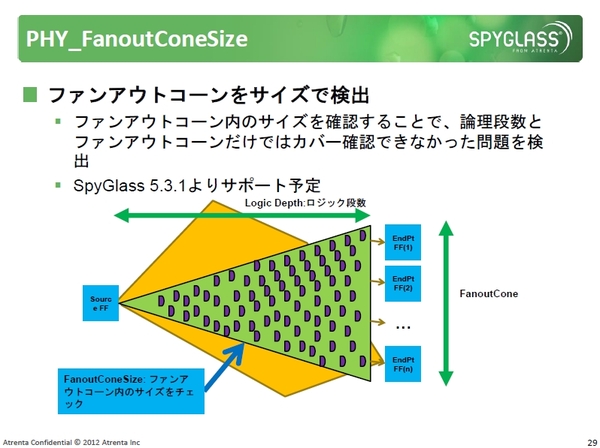

RTLでフィジカル解析を行う「SpyGlass Physical Base」に関しては、配線の混雑性を解析する機能が強化されたほか、ファウンアウト・コーンをサイズで検出する新機能が追加された。(次期バージョンからサポート予定)

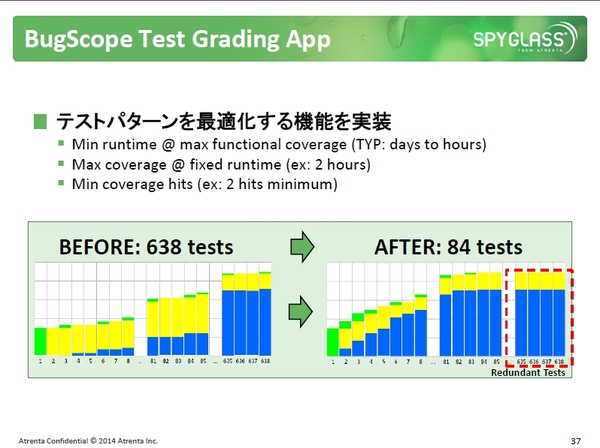

その他、プロパティ自動生成ツール「BugScope」では、テストパターンを最適化する機能が実装され、より機能検証の効率化が図れるようになった。

他にも各ツールの細部に渡り様々なアップデートが報告されていたが、大きなトピックスとしては上記の通り。

2014.09.30

2014年9月29日、FPGAベースのプロトタイピング・ソリューションを手掛ける米S2Cは、新製品となる「AXI-4 Prototype Ready Quick Start Kit」のリリースを発表した。

発表によるとS2Cの「AXI-4 Prototype Ready Quick Start Kit」は、同社のプロトタイピング・プラットフォーム「S2C TAI Logic Module」とXilinxの「Zynq」搭載ボードを簡単に接続するためのキットで、キットの一部として「Zynq」搭載ボードと「S2C TAI Logic Module」とを接続するインタフェース・モジュールとAXI-4 Bridge IPが提供される。また、その他に外部インタフェース用の「HDMI TX Module」、「GPIO Extension Module」もキットに含まれる。

このキットを利用すれば、ARMのCortex-A9 プロセッサをベースとした大規模SoCデザインを容易にプロトタイピング可能となる。

S2Cは同製品を10/1-3、サンタクララで開催予定のARMのプライベート・イベント「ARM® TechCon 2014」で初披露する予定だという。

※画像はS2C提供のデータ

2014.09.30

2014年9月29日、TSMCはIoTとウェアラブル・デバイス・アプリケーションをターゲットとした新しい低消費電力プロセス技術「Ultra-Low Power Technology Platform」を発表した。

発表によるとTSMCは新たな「Ultra-Low Power Technology Platform」として、既存の0.18μm、90nm、16nmプロセスに加え新たに55/40/28nmプロセスを追加ラインナップ。新たな55/40/28nmプロセスでは最大1.2GHzのプロセッシング・スピードはをサポートする。

-0.18-micron extremely low leakage (0.18eLL)

-90-nanometer ultra low leakage (90uLL)

-16-nanometer FinFET

-55/40/28-nanometer ultra-low power (55ULP/40ULP/28ULP)

TSMCによると新たな低消費電力プラットフォームは既存のプロセスよりも動作電圧が20-30%低く、アクティブ・パワーとスタンバイ・パワーの両方を削減可能。結果としてIoTやウェアラブル・デバイスのバッテリー寿命を2-10倍に伸ばすことが出来るとする。

55ULP、40ULP、28ULPについては既に先行顧客によるデザインが開始されており、リスク生産は2015年に開始される計画。日本では既に富士通セミコンダクターが28ULPにアクセスしているようだ。

尚、TSMCの「Ultra-Low Power Technology Platform」の発表に合わせ、ARMとCadenceが同プロセス技術をターゲットとしたコラボレーションを発表。両社はIoTおよびウェアラブル・デバイス・アプリケーション向けのARMベース・デザイン・ソリューションを提供する。

またCadenceはいち早く自社EDAツール及びIP製品のTSMC ULPプロセスのサポートを表明している。プレスリリース文

2014.09.26

2014年9月23日、Synopsysは新たな検証ソリューション「Verification Continuumプラットフォーム」を発表した。

新製品「Verification Continuumプラットフォーム」については別途詳細をレポートする予定だが、発表によると同製品の概要は以下の通り。

・適用範囲

プレ・シリコンの検証、ポスト・シリコンのバリデーション、ソフトウェア早期開発までをカバー

・機能

?Synopsysの保有する各種検証エンジンをベースに開発された単一の統合検証環境

?単一の環境として以下の全ての機能を提供

仮想プロトタイピング

スタティック・フォーマル検証

シミュレーション

エミュレーション

FPGAベース・ハードウェア・プロトタイピング

デバッグ

検証プランニング

カバレッジ解析

?Synopsysのシミュレータ「VCS」と同じコンパイル・エンジンを搭載

?「Verdi」と共通のデバッグ環境

・提供時期

2014年12月に早期適用企業向けに提供開始。2015年中に一般提供開始。

2014.09.26

2014年9月30日にサンノゼでTSMCのプライベート・イベント「TSMC 2014 Open Innovation Platform® Ecosystem Forum」が開催される。

同イベントではここ数年TSMCの最新プロセスのリファレンス・フローが発表されるのが恒例となっているが、今年は16nm FinFET+プロセスのリファレンス・フローが発表される予定で、それに先行してEDA大手各社が自社ツールの認証について一斉にアナウンスを開始した。

Cadenceは具体的なツール名を挙げていないが、これまでの経緯からするとインプリメンテーション環境「Encounter」の他にタイミング検証ツール「Tempus」、カスタム設計環境「Virtuoso」などが16nm FinFET+プロセスのリファレンス・フローに認証されている見通し。同イベントでは16nm FinFET+プロセスをターゲットとした「DDR4 Subsystem」のインプリ事例の講演なども行うようだ。

Mentorは今年3月に買収したBerkeley Design Automationの「Analog FastSPICE (AFS™) Platform」、「AFS Mega」、そして「Eldo」の3種類のSPICE製品が16nm FinFET+プロセスのリファレンス・フローに認証されたことを発表。配置配線ツール「Olympus-SoC™」と物理検証ツール「Calibre」も既に16nm FinFET+プロセスの認証に向けて拡張済としている。

Synopsysは具体的な製品名を挙げていないが、「Galaxy™ Design Platform」が16nm FinFET+で利用可能になったとしており、同プラットフォームに含まれる各種デジタル/カスタム設計ツールがリファレンス・フローに認証されている事を暗に示している。

尚、CadenceとSynopsysの両社は次世代のTSMC 10nm FinFETプロセスに向けた設計ソリューションについても言及しており、特にSynopsysは10nm FinFETプロセスに関するTSMCとのコラボレーションを強調。既に「Galaxy™ Design Platform」が10nm FinFETプロセスで利用可能としている。

実際のチップ開発事例としては、中国Huaweiの半導体部門子会社であるHiSiliconがTSMC 16nm FinFETプロセスを用いた業界初となるARMベースのネットワーク・プロセッサを設計したことを発表。

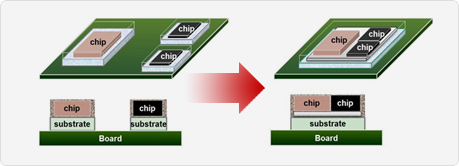

Hisiliconが作ったネットワーク・プロセッサは、ARM Cortex-A57を32個搭載するもので、TSMCのヘテロジニアスCoWoS 3D ICパッケージ・プロセスを用いて16nm ロジック・チップと28nm I/Oチップを統合する形で実現されているとの事。同ネットワーク・プロセッサは、28nm HPM製品と比較して同じパワーで40%の速度向上、同じ速度で60%パワー削減を実現しているという。

2014.09.25

2014年9月24日、ARMは32ビット・プロセッサ・コアの新製品「ARM Cortex-M7」を発表した。

発表によると新製品「ARM Cortex-M7」はハーバード・アーキテクチャーである「ARMv7-M」アーキテクチャの32ビット・プロセッサで同社の「Cortex-M」シリーズ製品としては最高のパフォーマンスを誇る。既存の「Cortex-M4」と比較するとDSP性能は2倍、6段パイプライン構成でベンチマーク・スコア 5 CoreMarks/MHzを達成する。

また「ARM Cortex-M7」は既存の「Cortex-M」シリーズ同様、高いエネルギー効率を実現しており、モーター制御、FA、オーディオ、イメージ・プロセッシング、自動車、IoTなど様々なスマート・コントロール・システムでの利用が想定されている。

ARMによると既にAtmel、Freescale、ST Microelectronicsらが早期顧客としてライセンスを獲得しているという。

2014.09.25

2014年9月23日、ESLソリューションを手掛ける米Carbon Design Systemsは、バーチャル・プラットフォーム・キット「CPAK」を提供する新たなWebポータルの開設を発表した。

Carbonは同社のバーチャル・プラットフォーム作成環境「SoC Desginer Plus」で利用可能な各種IPモデルを提供するWebポータル「IP Exchange」を2010年に立ち上げ、現在も運用を続けているが、今回立ち上げたのはバーチャル・プラットフォーム・キット「CPAK(Carbon Performance Analysis Kits)」を提供するための専用ポータルとなる。

バーチャル・プラットフォームを一から構築しようとするとモデルの調達から始まり多大な工数を要するため、予め必要最低限なバーチャル・プラットフォームを用意するというCarbonが仕掛けたアプローチ「CPAK」はユーザーに好評で同社の売上増の原動力になっている。

※カーボン・デザイン・システムズ・ジャパン株式会社

2014.09.25

FPGA大手のAlteraとXilinxはFPGAに関する無償のeBookの配布を開始した。

Alteraが配布するのは「FPGAs For Dummies」というタイトルのeBookで、FPGAの基礎や設計フロー、FPGAの歴史、ヘテロジニアス・コンピューティングやOpenCLを含むシステム・デザインにおけるFPGAの未来など、FPGA全般に渡る解説書という位置づけ。

一方のXilinxが配布するのは「The Zynq Book」というタイトルでその名の通りXilinxのARM搭載FPGA「Zynq」にフォーカスしたもので「Zynq」を用いた組み込みシステムの開発プロセスについて解説する。同書についてはペーパーブックも用意されており、既にAmazonでベスト・セラー・リストのTOP10にランキングされているとの事。

Altera、Xilinxいずれの書籍もWeb上で無償でダウンロードできる。

2014.09.24

2014年9月18日、Synopsysは、AMDとのIPに関する契約内容を発表した。

発表によるとSynopsysとAMDは、IPの提供で複数年の契約を締結。これによりAMDはSynopsysの提供する16/14nmおよび10nm FinFET向けのインタフェースIP、ロジックライブラリ、アナログIPそしてメモリ・コンパイラを利用可能に。また、この契約に伴いSynopsysは、AMDの保有するインタフェースIPならびにファウンデーションIPを買収し、合わせてAMDのIP R&D部隊150名のエンジニアを雇い入れる事になった。

SynopsysのIP利用と本業外のIP開発の切り離しを求めるAMDと、IPポートフォリオを拡張したいSynopsysの利害が一致し、両社は今回の合意に至ったと推測できる。

Synopsysはこれまで様々なIPベンダを買収し、資産と人材の獲得を進めてきているが、単独のIPベンダではない半導体ベンダのIP資産の買収を発表するのは恐らく今回が初である。

IPの部品化と流通が進む今日のSoC開発を考えると、今後今回のような半導体ベンダによるIP資産の売却やIP外部調達の流れは更に加速すると思われる。

2014.09.12

2014年10月3日(金)、新横浜国際ホテル南館にて、第一回目の開催となる新セミナー「Design Solution Forum 2014」が開催されます。

新セミナー「Design Solution Forum 2014」は、エレクトロニクス業界の第一線で活躍する各分野のエキスパートが中心となって企画した設計者による設計者のための技術フォーラムです。

計42セッションで構成される同フォーラムでは、ハードウェア設計および組み込みソフトウェア開発に関する様々な技術情報を発信すると共に、「創ろう、拡げよう、設計者ネットワーク」をスローガンに設計者の皆様の交流の場を提供致します。

是非この機会に「Design Solution Forum 2014」に参加頂き、国内のエレクトロニクス業界を活気づける設計者ネットワークを創り出しましょう。

■■セミナーの見どころ

●基調講演:株式会社 NTTドコモ 移動機開発部 無線技術開発担当/担当部長

二方 敏之 氏

●エンジニア・セッション:設計者による事例講演全16セッション!

?Designトラック

?Verificationトラック

?Soft&FPGAトラック

?Solutionトラック

- Javaによる手軽なFPGA開発の世界を目指して -

●トーク・セッション:各トラックにて様々なテーマでエンジニアが激論!

?今後の検証ビジネスの方向性を検証の匠に聞く?

●スポンサー・セッション:最新の設計ソリューション紹介全20セッション!

?参加スポンサー(アルファベット順)

■■開催概要

名 称:Design Solution Forum 2014

会 期:2014年10月3日(金)

開場時間:午前10時?午後5時20分

入 場:無料(聴講予約制)

主 催:Design Solution Forum 2014実行委員会

一般社団法人 日本エレクトロニクスショー協会(JESA)

2014.09.11

2014年8月29日、高位合成ツールをはじめフォーマル検証ツール、ローパワー設計ツールを手掛けるCalypto Design Systemsは、新横浜のホテルでプライベート・セミナー「Calypto Users Forum 2014」を開催。セミナー会場には推定100名近くの来場者が集まり、例年以上も盛り上がりを見せていた。

ここでは同セミナーで発表された、富士ゼロックスの設計事例について紹介する。

講演タイトル:

「画像処理アルゴリズムのハードウェア化設計へのCatapultoの適用事例」

講演者:

富士ゼロックス株式会社 コントローラ開発本部 コントローラプラットフォーム第五開発部 三角 晃

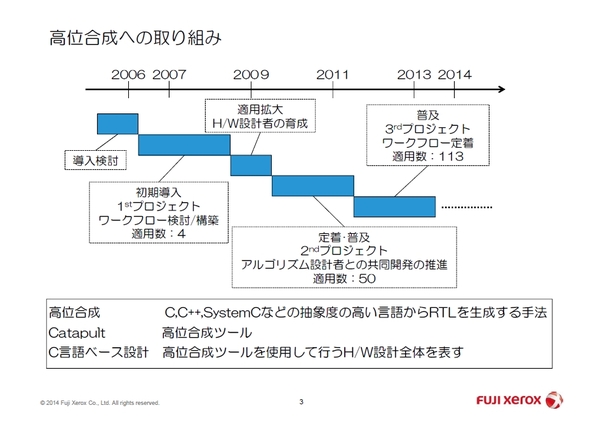

講演者の三角氏によると、富士ゼロックスでは2007年からCalyptoの高位合成ツール「Catapult」(※当時はMentor Graphics社が販売)を導入し複写機向けのコントローラ開発に適用。時間をかけて社内への普及を進め、過去約7年間で150以上の回路モジュールに適用(その大半は過去3年以内)。最近は画像処理部は全て「Catapult」で設計するプロジェクトもあるという話。

※画像は富士ゼロックス提供のデータ

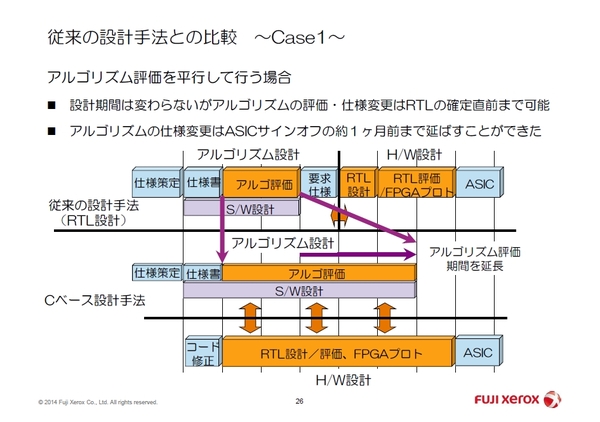

同社における高位合成へのモチベーションは明確で、開発の効率化とアルゴリズム設計側からの要求の2つ。後者は何かと言うと、アルゴリズムの評価期間を出来るだけ長く取りたいという要求だ。実際の導入にあたっては「Catapult」の使用による回路要求仕様の最適化や設計資産のCモデル化(プロジェクト間でRTLではなくCモデルを再利用)などにも期待した。

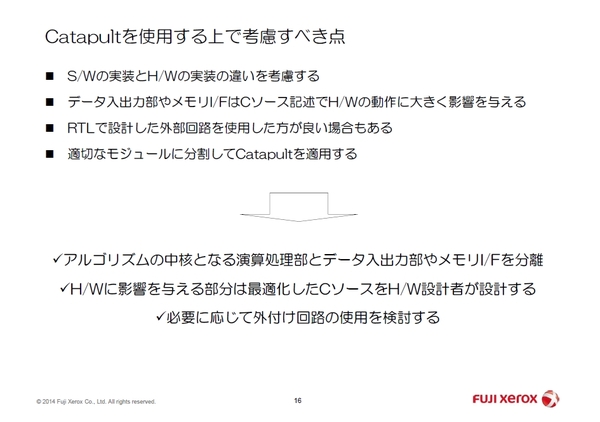

既に「Catapult」を導入しコントローラ開発で定着させている同社だが、三角氏によると「Catapult」の普及に向けてはそれなりに苦労したという事で、その経験に基づいた「Catapult」利用上の注意点(考慮すべき点)として、インタフェース部などハードに影響する部分はハード設計者がCソースをしっかり最適化する。もしくはRTL回路の外付けを検討すること。そして合成は関数単位など適切なモジュールに分割して実施すること。などを挙げた。

※画像は富士ゼロックス提供のデータ

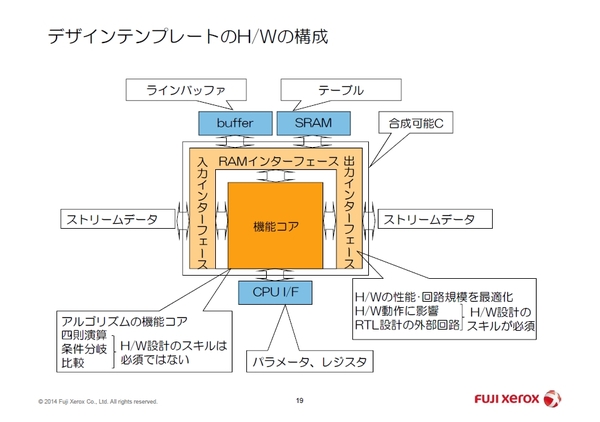

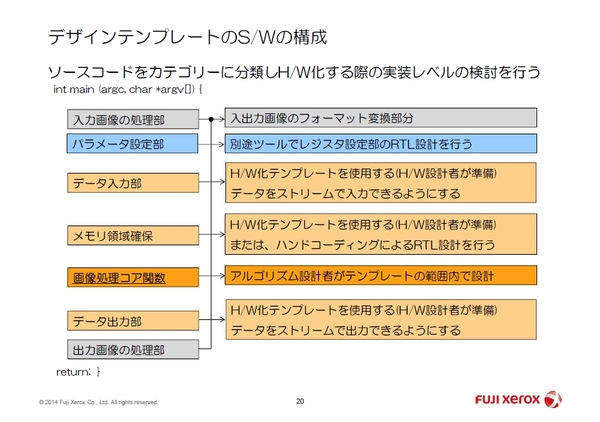

更に三角氏は「Catapult」の運用ノウハウとして「デザインテンプレートの作成」について紹介。三角氏によると同社では高位合成の対象とする画像処理部を機能別に4つのタイプに分類し、各タイプ毎にデザインテンプレートを用意。それを用いることで設計の効率化と同時にアルゴリズム設計者とハードウェア設計者の作業分担/ワークフローを明確化しており、合わせてCアルゴリズムの修正を行う際のルールを設定する事でハード化への影響を抑えているという話だった。

テンプレートを用いた作業分担としては、アルゴリズム設計者はアルゴリズムの機能コアの設計にフォーカスし、それ以外はハード設計者が担当。メモリ・インタフェース部に関してはCコードで実装せずにハード設計者がRTLをコーディングというのがポイントのようだった。

※画像は富士ゼロックス提供のデータ

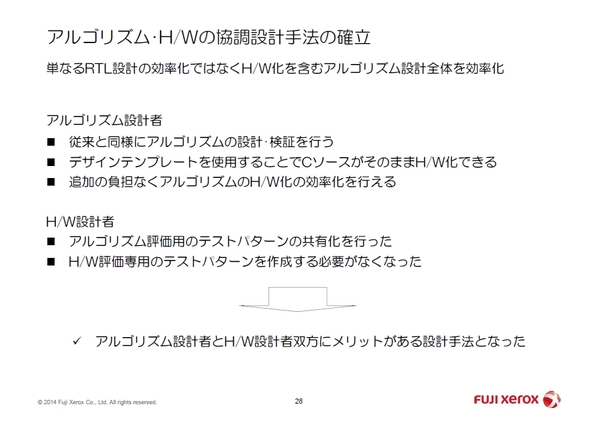

このようにして実際に「Catapult」を適用した結果、従来シーケンシャルに進めていたアルゴリズム設計とRTL設計が同時並行的に進める事が可能となり、あるケースではASICサインオフの約1ヶ月前までアルゴリズムの仕様変更が可能に。またアルゴリズムが確定しているケースでもRTL設計期間の短縮によりASIC設計を前倒しでき、全体的な設計期間の短縮を実現できたという事。三角氏はこれら成果と合わせ幾つかの具体的なメリットを示した上で、「Catapult」によりアルゴリズム設計者とハードウェア設計者双方にメリットがある協調設計手法を確立出来たと語った。

※画像は富士ゼロックス提供のデータ

尚、三角氏によると「Catapult」は既にアルゴリズム設計者にとっても無くてはならないツールとなっており、「Catapult」を利用する事によってハード化による回路規模やコストを意識するなど、アルゴリズム設計者の意識が良い意味で変化しているという。

2014.09.04

2014年9月2日、米SIA(Semiconductor Industry Association)は、2014年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年7月の世界半導体売上は前年同月比9.9%増、前月比2.4%増の280.7億ドルで先月6月に続いて単月売上記録を更新した。上半期を終えても市場の活況が続く世界の半導体市場は、これで14ヶ月連続で前年実績を上回る売上を叩きだしている。

2014年6月の売上を地域別に見ると日本市場を含む全ての地域で売上前年比増を達成。前年比では欧州が14.9%増と大きな成長を示した。

2014.09.01

2014年8月27日、国内のファブレス半導体ベンダ、ザインエレクトロニクスは、同社の画像処理プロセッサを中国のスマートフォン・メーカーkoobeeが新規採用したことを発表した。

発表によると今回koobeeが採用したのはザインのカメラ用ISP(Image Signal Processor)製品「THP7212」で、SONYのCMOSイメージセンサ「IMX214」、1300万画素カメラを搭載するkoobeeのスマートフォンの新製品「MAX3」に搭載されるとの事。

ザインの「THP7212」は1300万画素のカメラ解像度に対応した画像処理プロセッサで、ザイン独自の技術によりフレームメモリを使わずに自動補正(オートフォーカス、オートホワイトバランス、自動露出補正等)、顔検出、暗部補正、動画手振れ補正等を処理することが可能。メモリを内蔵しないことで消費電力の削減と製品コストの削減を実現している。また、チップのパッケージにWLCSP (Wafer Level Chip Size Package)を採用し、3.8mm×3.8mmと超小型チップサイズを実現している。

ザインは「THP7212」と同じISP製品ファミリとして1600万画素に対応する「THP7312」も提供しており、自動車向けのADASなどに採用されている。

2014.09.01

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2014.08.27

2014年8月25日、NECはテルモが同社の提供する高位合成ツール「CyberWorkBench」を採用した事を発表した。

発表によるとテルモは、輸液管理用医療機器に用いる制御FPGAの設計に「CyberWorkBench 」を採用。「CyberWorkBench 」を導入した事により、従来の人手設計と比較して工数を約6割短縮出来たという。

テルモでは医療機器向けの制御FPGAを元となるC言語記述から人手で設計しており、その効率化が課題となっていた。具体的には、人手設計によるバグの混入防止や仕様変更の度に発生する回路修正作業の大幅削減が課題だった。

「CyberWorkBench」は数ある高位合成ツールの中でもFPGAターゲットの合成に最も注力しているツールで、デバイスの特性に応じた細かな最適化を行うのも特徴の一つ。今回のテルモの事例においても「CyberWorkBench」の各種FPGA向けの最適化機能が駆使されているはずで、それによって回路の設計品質が保たれていると思われる。

また、「CyberWorkBench」は古くから「制御回路設計にも使える高位合成ツール」として打ち出しており、その実績やノウハウも多数備えているため、今回のテルモのケースのようなFPGAターゲットの制御回路設計は「CyberWorkBench」が最も得意とするところであったと言えるだろう。

2014.08.22

2014年8月21日、Mentor Graphicsは、2015会計年度第2四半期(14年5-7月)の売上を報告した。

発表によると、Mentorの2015会計年度Q2の売上は、前年比約2.7%増、前Q1比約2%増の2億6023万ドル、営業利益は1691万ドルで前年比37%減だった。この実績はQ1実績報告時の予測を上回るものとなる。(※GAAP基準による会計結果)

Mentorの今期Q2の売上を地域別で見ると、北米、欧州の売上比率が減った分、アジア・パシフィック地域の売上が増え売上全体に占める割合が25%となった。

MentorはこのQ2(5-7月)の間にに3Dフルウェーブ電磁界シミュレーションの米Nimbic社と車載エレクトロニクス設計ソリューションの独XS Embedded社を買収。(関連ニュース1、関連ニュース2)

新製品としては以下の通り多方面に渡る製品を新たにリリースした。

・フォーマル検証用のプロパティ自動生成ツール「Questa PropGen」

・PCB設計ツール「Xpedition Path Finder」、「Xpedition Data Management」

・メモリ製品の検証向けエミュレーション・ソリューション

・ヘテロジニアス・マルチ・コアSoCに対応する組込みソフト開発ソリューション、

Mentorは次期2015会計年度Q3(14年8-10月)の売上を今四半期売上を上回る2億7500万ドル程度と予測している。

2014.08.22

2014年8月20日、Synopsysは、2014会計年度第3四半期(14年5月-7月)の四半期決算を報告した。

発表によると、Synopsysの2014会計年度Q3の売上は、前年同時期比約8%増、前期Q2比約2%増の5億2180万ドルでQ2に続いて同社の四半期売上記録を更新した。純利益は前年同時期比約25%増の6565万ドルだった。(※GAAP基準による会計結果)

SynopsysはDACを挟んだこの5月-7月の間に、「PCI Express 4.0 IP」、「IP Development Kit」、ARCファミリのローパワーDSP「ARC EM5D/EM7D」、「DDR4/3、LPDDR4/3/2の検証用IP」など立て続けに新たなIPソリューションを発表。IP分野ビジネスの強化を着々と図っている。(※

関連ニュース1、

関連ニュース2)

Synopsysは次のQ4(8-10月)の売上を今期Q3を更に上回る5億3700-4700万ドルと予測しており、予測通りの売上が達成されると2014会計年度の売上合計は同社初の20億ドル超えとなる。