NEWS

2015.02.20

2015年2月16日、Synopsysは新製品「DesignWare DDR Explorer」の発売を発表した。

Synopsysによると「DDR Explorer」は、同社のDDRメモリ・コントローラIPを用いたDDRメモリー・サブシステムのパフォーマンス解析を行うツールで、同メモリ・コントローラIPの最適なコンフィギュレーションを短期間で決定できる。

「DDR Explorer」によるパフォーマンス解析は、DDRメモリ・コントローラIPのトランザクション・レベルのアーキテクチャ・モデルを利用してグラフィカルな環境で実行され、同じ時間内でRTLよりも10倍以上のシミュレーション/解析が可能。「DDR Explorer」を用いてメモリ・コントローラIPのコンフィギュレーションを最適化することで、メモリー処理効率は最大20%向上可能で、消費電力やコストの低減に繋がるだけでなく、IPのインプリと検証にかかる期間を短縮することもできる。

「DDR Explorer」は既に出荷中。LPDDR2、LPDDR3、DDR2、DDR3、DDR4など業界標準DRAMインターフェイス全てをサポートしている。

Synopsys売上報告、14年11-15年1月は前年比13.2%増の5億4200万ドルで過去最高更新

2015.02.19

2015年2月18日、Synopsysは、2015会計年度第1四半期(14年11月-15年1月)の四半期決算を報告した。

発表によると、Synopsysの2015会計年度Q1の売上は、前年同時期比約13.2%増、前期Q4比約0.5%増の5億4200万ドルで四半期売上記録を更新。純利益は前年同時期比約3.7%減の6520万ドルだった。(※GAAP基準による会計結果)

Synopsysはこの11月-1月の間に、配置配線ツール「IC CompilerII」の最新バージョンをリリースしたほか、LPDDR4、UFS、UniPro、eMMCの検証IP、組込型不揮発メモリIPの新ファミリ「Medium Density NVM IP」などを新製品として市場投入している。

Synopsysは次の2015会計年度Q2(15年2月-4月)の売上をQ1を上回る5億4300-5300万ドルと予測している。

ARMがCortex-M4ベースの「ARM Microcontroller Design Contest」を開催

2015.02.19

2015年2月18日、ARMは同社のプロセッサ・コア「Cortex-M4」を用いた「ARM Microcontroller Design Contest 2015」の開催を発表した。

コンテストの開催は、ARMのCortex-MベースのMCU開発環境「ARM Keil® MDK Microcontroller Development Kit」や同じくCortex-M向けに用意されているソフトウェア・コンポーネント(インタフェース・ソフト「CMSIS」、各種ミドルウェア)のプロモーションの一環で、コンテスト参加者には「ARM Keil MDK」のプロフェッショナル版のライセンス(6ヶ月間)や開発用のボード(Freescale,NXP,Infineon,STMicroの4種のうちどれか)が提供される。コンテストのお題はホーム・オートメーション、IoT、各種システム・コントロールなど自由で、コンテスト参加者は用意されているテンプレート・アプリケーションも利用できる。

コンテスト参加希望者はまず3末までにプロジェクトの登録を行い、選考を通過すると次のステップとして開発環境が提供される。コンテストに参加できるプロジェクトは100前後の予定。コンテストの期間は6末までとなっており結果発表は10月。上位5つのプロジェクトに上から5000ドル、3000ドル、1500ドル、500ドルと賞金が用意されている。

AlteraがMentorとのコラボでSoC FPGAのバーチャル・プラットフォームを無償提供

2015.02.18

2015年2月17日、Alteraは同社のSoC FPGAのバーチャル・プラットフォームの提供を発表した。

発表によるとAlteraはMentor Graphicsとのコラボレーションにより、Mentorの提供するバーチャル・プロトタイピング環境「Vista」の技術をベースとしたSoC FPGAのバーチャル・プラットフォームを開発。Intelの14nm Tri-Gateプロセスで製造される64ビット・クアッドコア ARM Cortex-A53搭載の「Stratix 10」を含む各種SoC FPGAのバーチャル・プラットフォームの無償提供を開始する。

無償提供されるバーチャル・プラットフォームには、ARMのプロセッサ・コアとそのペリフェラルで構成されるARMプロセッサ・サブシステムの完全な機能シミュレーションモデルがプリ・ビルドされており、同環境を利用すれば各種AlteraのSoC FPGA上で走るソフトウェアの先行開発が可能となる。このAlteraのSoC FPGAのバーチャル・プラットフォームは、無償のバイナリとしてMentorのWebサイト上で提供される予定で実行にあたり「Vista」のライセンスを必要としない。しかし、SoC FPGAのカスタム・ロジック部も含めたバーチャル・プラットフォームを構築しハード/ソフトの相互動作をシミュレーションするとなると、Mentorの提供する「Vista」のライセンスを別途購入する必要がある。

尚、Alteraは以前、SynopsysとSoC FPGAのバーチャル・プラットフォーム「Virtual Target」を共同開発しており、業界初のSoC FPGA向けソフトウェア開発環境として発表していた。同時の「Virtual Target」の中身は旧Virtio社の「Innovator」がベースとなっており価格は数百万円だった。今回発表されたMentorの提供するSoC FPGAのバーチャル・プラットフォームは無償提供されるという事で、ユーザーにとってはバーチャル・プラットフォームを利用する敷居が大きく下がる。

ちなみにAlteraの競合Xilinxは、ARM搭載FPGA「Zynq」のバーチャル・プラットフォームでCadenceとコラボレーションしている。

CMエンジニアリングがタイミングチャートからテストベンチを生成する新製品を発表

2015.02.17

2015年2月16日、検証/設計サービスと機能検証用のEDAツールを手掛けるCMエンジニアリングは、新製品となる機能検証ツール「SpecInsight-TEX」のリリースを発表した。

「SpecInsight-TEX」は、インタフェース仕様として作成したタイミングチャートからテストベンチの入力情報、検証シナリオ、シミュレーション実行スクリプトを自動生成するツールで、生成するテストベンチ記述はVerilog/VHDLをサポートしており、RTLとテストベンチは入力端子表から自動的に接続可能。検証シナリオは複数のタイミングチャートを組み合わせて生成できる。

タイミングチャートから簡単にテストベンチを生成できるため、設計初期の段階で素早くシミュレーションを実行出来る点、エンジニアの検証スキルを問わない点などが「SpecInsight-TEX」の特徴である。

同社は機能仕様書からRTLや検証用コードを生成するツールを「SpecInsightファミリー」として展開しているが、新製品「SpecInsight-TEX」では、アサーション自動生成ツール「SpecInsight-ACE」で生成したアサーションを取り込む事もできる。

ちなみにアサーション自動生成ツール「SpecInsight-ACE」には、タイミングチャートを簡単に作成する専用エディタが備えられているので、「SpecInsight-ACE」と「SpecInsight-TEX」を組み合わせて利用するとより検証を効率化出来そうだ。

尚、新製品「SpecInsight-TEX」の価格は公表されていないが、恐らく「SpecInsight-ACE」の価格と同レベルで数十万円程度で購入できると思われる。

Mentorが産業オートメーション向け組込みシステムソリューションを発表

2015.02.16

2015年2月10日、Mentor Graphicsは、産業オートメーション向けの組込みシステムソリューションを発表した。

今回のMentorの発表は産業オートメーション業界向けのイベント「ARC Industry Forum」の開催に合わせたもので、同社の組込みソリューションを産業オートメーション向けにも利用できるようにしたという内容。

Mentorは組込みシステム向けソリューションとして、組込みOS(Nucleus® RTOS/Mentor Embedded Linux)とソフトウェア開発環境(Sourcery™ CodeBench)の二本柱のソリューションを持っているが、これらソリューションをベースに産業オートメーション向けの機能を実装し、パートナー企業のソリューションと連携する事で産業オートメーション向けの組込みシステムソリューションを実現している。

ポイントとしては、組込みOS「Nucleus® RTOS」によるIEC 61508(一般産業の機能安全を対象とした国際機能安全規格)やWurldtech Achilles(制御機器の世界的なセキュリティ認証)のサポート、Mentor Embedded Linuxによる産業プロトコルやSELinux(Security-Enhanced Linux)の強制アクセス制御のサポートなどが挙げられる。

また、パートナーとしては、Softing AG、Icon Labs、Wurldtechといった企業と連携している。

SynopsysがルネサスRH850のVDKにEthernet AVBとCAN-FDモデルを追加

2015.02.16

2015年2月12日、Synopsysは、同社の提供するバーチャル・プロトタイピング環境向けの新モデルを発表した。

今回Synopsysが発表したのは、ルネサス製RH850マイコンのバーチャル・プロトタイピング開発に利用できるEthernet AVBとCAN-FDの両モデル。これらモデルはSynopsysが提供しているRH850ファミリ向けの「Virtualizer Development Kit」の一部として顧客に提供される。

発表では詳細が明らかにされていないが、今回発表されたEthernet AVBとCAN-FDの両モデルはSystemC言語で記述されており、用途に応じて精度と実行速度をトレードオフして利用できるはずだ。

「Virtualizer Development Kit(VDK)」は、特定プロセッサ向けのバーチャル・プロトタイピングを効率的に開発するためのキットで、SynopsysはARM,Freescale,Renesasなど主要なベンダと協業して各種VDKをリリースしている。自動車向けとして世界一のシェアを誇るルネサスRH850ファミリ向けのVDKは、車載ECUのソフトウェア開発をターゲットに2013年から提供されている。(関連ニュース)

AldecがVirtex-7 2000T 6個搭載のプロトタイピング・システム「HES-7」を発表

2015.02.13

2015年2月9日、AldecはFPGAベースのプロトタイピング・システム「HES-7」の最新製品「HES7XV12000BP」のリリースを発表した。

最新のHES-7「HES7XV12000BP」は、Xilinxの28nm FPGA Virtex-7 2000T FPGAを6個搭載するプロトタイピング・ボードで、ボード1枚当たり最大7200万ASICゲートに対応。同ボードをバックプレーン(HES7-BPx4)に4枚接続することでそのデザイン容量は最大2億8800万ASICゲートに拡張できる。

Synopsysの「HAPS」、Cadenceの「Protium」、S2Cの「V7 TAI Logic」など、EDAベンダ各社からリリースされているFPGAベースのプロトタイピング・ボードの上位製品には概ねXilinxの28nm FPGA Virtex-7 2000Tが4個搭載されているが、今回Aldecがリリースした「HES7XV12000BP」はVirtex-7 2000Tを6個搭載という事で、単純にボード1枚当りのデザイン容量としては業界最大のものとなる。

Aldecの「HES-7」は他社製品よりもコスト・パフォーマンスの高いプロトタイピング・ボードとして知られている。

メガチップスがセンサーHUB LSI「frizz」のコアにCadenceのXtensaプロセッサを採用

2015.02.12

2015年2月10日、Cadenceはファブレス半導体ベンダのメガチップスがセンサーHUB LSIの開発でCadenceのXtensaプロセッサを採用した事を発表した。

メガチップスが開発したセンサーHUB LSI「frizz」は今年のCESでも展示された同社の新製品で、一般的な既存のセンサーHUBチップとは違い、制御処理と合わせて低消費電力で高速なアルゴリズム演算を実行することが可能。そのコアに利用されているのがCadenceのXtensaプロセッサである。

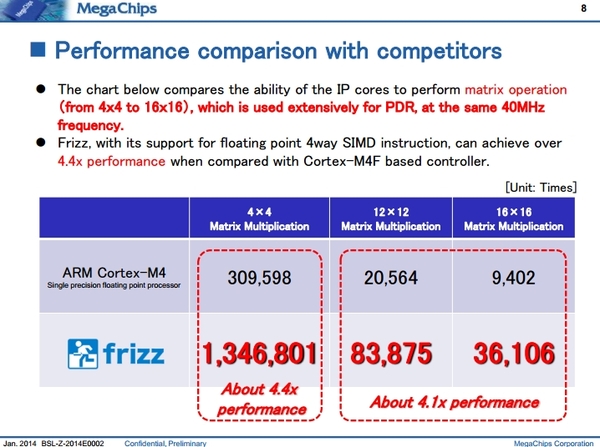

メガチップスは、Xtensaプロセッサをベースに3ウェイVLIW命令、浮動小数点4ウェイSIMD命令を追加して独自のモーション・エンジン「ParaForce」を開発。これ組み込む事で高速演算を超低消費電力で実行できるセンサーHUB LSI「frizz」を実現している。

メガチップスが公開している情報によると、実際に歩行者推定航法(PDR)アプリケーションを使ってセンサーHUB LSI「frizz」をベンチマークした結果、「frizz」はARM Coretx-M4Fベースのコントローラよりも4倍以上高速なパフォーマンス(演算処理速度)を実現。また同じくPDRアプリケーションの実行において「frizz」の消費電力はARM Cortex-M4Fの10分の1以下に抑える事ができたという。

メガチップスによるセンサーHUB LSI「frizz」の実現は、CadenceのXtensaコアの優れたアーキテクチャもさることながら、Tensilicaの公認デザイン・センターとしての同社のこれまでのノウハウも大きかったようだ。

メガチップスの「frizz」は、スマートフォンやIoT、ウェアラブルデバイスをターゲットとした常時接続センサーHUB LSIとして今年1000万個の販売目標を掲げており、各種センサ処理用のソフトウェア・ライブラリや加速度、ジャイロ、地磁気、気圧の計10軸のセンサを搭載した評価用ボードも用意しているという。

ARM売上報告、2014年売上は前年比16%増の12億2900万ドルで過去最高

2015.02.12

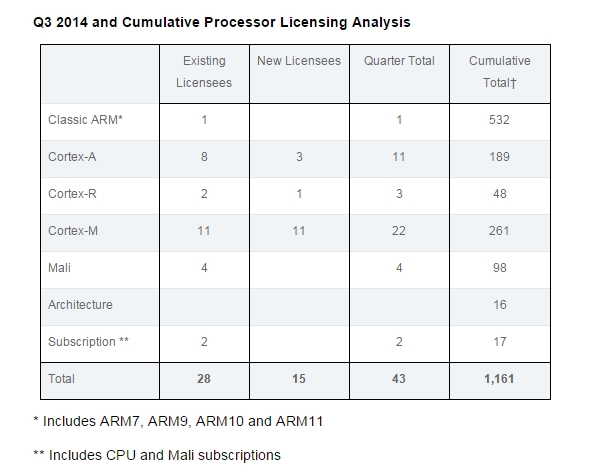

2015年2月11日、ARMは、2014会計年度第4四半期(2014年10-12月)の売上を報告した。

ARMの2014年Q4の売上は、前年比約18%増、前期比約11.7%増の3億5760万ドルで前Q3に続いて四半期売上記録を更新した。税引き前の純利益は前年比約25%増の約1億8820万ドルだった。

ARMの2014会計年度の売上合計は前年比16%増の12億2900万ドルで過去最高。税引き前の純利益の合計は前年比13%増の6億5100万ドルとなっている。

ARMのQ4売上の内訳を見ると、プロセッサ・ライセンスの売上が前年比約30%増の1億3950万ドルと大きく伸びた。プロセッサ・ロイヤリティの売上も好調で前年比16%増の1億5070万ドルだった。

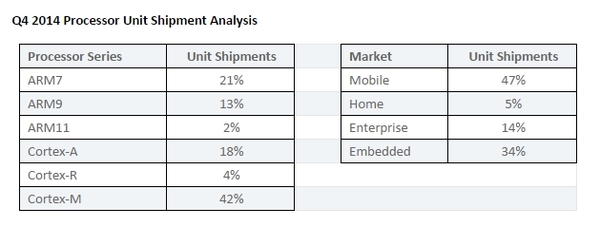

プロセッサ・ライセンスの契約数はこのQ4で計53件。最も多かったのはCortex-Mプロセッサのライセンスで23件、9件は最新のARMv8-Aアーキテクチャ・ベースのプロセッサ、GPU Maliのライセンス契約も10件と好調だった。

ライセンス内訳は下記の表の通り。

※画像はARM発表資料より抜粋

2014年Q4で出荷されたARM搭載チップの総数は約35億個で前年よりも約20%増えた。

※画像はARM発表資料より抜粋

DMPの世界最小サイズのGPU IPコア「ant200」が車載機器向け製品に採用される

2015.02.09

2015年2月7日、グラフィックスIPを手掛ける日本のIPベンダ、ディジタルメディアプロフェッショナル(DMP)は、同社のUltra tiny GPUコア「ant200」が車載機器向け製品に採用されたことを発表した。

DMPは導入先の詳細は明らかにしていないが、GPUコア「ant200」のベースとなる「SMAPH-F」はカーナビのほかデジカメなどでも豊富な採用実績がある。

DMPは「ant200」を「SMAPH-F」から更にサイズをコンパクトにしたベクターグラフィックス対応のGPUコアと説明しており、GPU IPコア製品としては世界最小サイズとしている。

小型サイズを特徴とする「ant200」の利点としては、これまでサイズの問題で難しかったFPGAでの利用が考えられるという。

MentorのECUシステム設計ツール「Volcano VSA」が車載Ethernetに対応

2015.02.06

2015年2月6日、Mentor Graphicsは、同社のECUシステム設計ツール「Volcano VSA」が車載Ethernetに対応したことを発表した。

「Volcano Vehicle Systems Architect(VSA)」は、AUTOSARをサポートする車載ECUのシステム設計ツールでこれまでCAN、LIN、FlexRayに対応していたが、新たにEthernetにも対応した。

Mentor担当者のコメントによると、広帯域幅を持ち製造コストの優位性もあるEthernetネットワークが最新車両のECUネットワークとして選ばれることが増えてきているという事で、「Volcano VSA」を利用すれば、Ethernet、CAN、LIN、FlexRayといった複数ネットワークを混在させた設計の効率化に役立つという。

MentorはECU設計向けのソリューションとして「Volcano」製品ファミリを展開しており、「Volcano VSA」を含む4種類の製品を提供している。

Synopsysが25G/50G Ethernetの検証IPをリリース

2015.02.06

2015年2月3日、Synopsysは25G/50G Ethernetの検証IPをリリースした事を発表した。

今回発表された検証IPは、25 Gigabit Ethernet Consortiumが策定した25G/50G Ethernet仕様に準拠するもので、同社の他の検証IPと同様にSystemVerilog Universal Verification Methodologyアーキテクチャをベースに開発されている。

SynopsysはEnterprise 25G/50G デジタルコントローラIPも既にリリースしているという。

FPGAベース・プロトタイピングのS2Cがインタフェース・ライブラリを拡張

2015.02.06

2015年2月3日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、同社のプロトタイピング・システム向けのインターフェース・ライブラリの拡張を発表した。

S2CはユーザーのSoCプロトタイプ開発を容易化するために各種ハードおよびソフトのインタフェース・ライブラリを提供しており、今回新たに12種のライブラリを追加した。同社の提供する主なライブラリは下記表の通りで計80種以上のラインナップだという。

CadenceとSynopsysがARM Cortex-A72のサポートを表明

2015.02.05

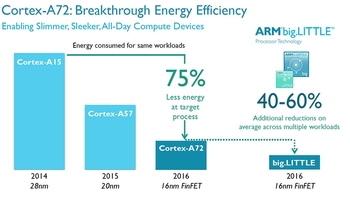

2015年2月3日、CadenceとSynopsysの両社はCortex-A72を含むARMの新IP「Premium mobile IP suite」の発表を受けて、自社のEDA環境が同IPをサポートする事を発表した。

ARMの新ハイエンド・コアCortex-A72を搭載した製品が市場投入されるのは2016年の予定。既にHiSilicon, MediaTek, Rockchipなど先端モバイルAPを手掛ける各社がCortex-A72 processorをライセンス済みで、年内にはCortex-A72ベースSoCのテープアウト事例が発表されるだろう。

Cadence売上報告、14年10-12月は前年比約12.2%増の4億2300万ドル-また売上記録更新

2015.02.05

2015年2月4日、Cadenceは、2014会計年度第4四半期(2014年10-12月)の売上を報告した。

Cadenceの2014年Q4(10-12月)売上は、前年同時期比約12.2%増、前期Q3比約5.7%増の4億2300万ドル。純利益は前年比約74%増の6500万ドルだった。(※GAAP基準による会計結果)

Cadenceは前Q3で四半期売上記録を更新していたがこのQ4で再び記録を更新。2014会計年度の売上合計は前年比約8.3%増の15億8100万ドル、純利益は約3%減の1億5900万ドルだった。

Cadenceの社長兼CEO Lip-Bu Tan氏のコメントによると、2014会計年度はIP事業がブレイクし売上が40%近く増えたとの事。

Cadenceは、来期2015年Q1の売上額を4億500-15000万ドル、2015会計年度の売上合計は2014年を上回る16億8000万-17億2000万ドルに到達するとみている。

Synopsysから組込型不揮発メモリIPの新ファミリ「Medium Density NVM IP」が登場

2015.02.05

2015年1月30日、Synopsysは組込型不揮発メモリIPの新ファミリ「DesignWare Medium Density NVM IP」のリリースを発表した。

Synopsysによると「Medium Density NVM IP」は、フラッシュ・メモリーと同等の機能を提供する組込型不揮発メモリIPで最大64Kバイトをサポート。フラッシュ・メモリーと違い追加のマスク生成などが不要なためダイコストを最大25%削減可能で、コスト増加を避けつつキロバイト級の不揮発メモリー機能を実装できる。

「Medium Density NVM IP」がターゲットとするのはスマート・センサー、電力管理、タッチスクリーン・コントローラなどのアナログICで、マイクロコントローラの組み込みにおける拡張EEPROM、フラッシュ・メモリーの置き換えを狙う。

「Medium Density NVM IP」はTSMC 180nm 5V CMOSおよびBCDプロセスをサポートしており、エラー検出訂正(ECC)機能も搭載。既に早期適用顧客に提供が開始されている。

Vtechがフィリピンに現地法人設立、世界初のLSI内蔵型検証IP「VARON」の展開を加速

2015.02.03

2015年2月3日、日刊工業新聞が検証/設計サービスを手掛けるベリフィケーションテクノロジー株式会社(以下、Vtech)のフィリピン法人設立を報じた。

記事によるとVtechはフィリピンのマニラに同社の現地法人「ベリフィケーションテクノロジー・フィリピン」を新設。現地採用の10人と日本人1人の11名で技術サポートを中心に生産・販売拠点として活動する。

Vtechは自社製品のLSI内蔵型検証IP「VARON」が好調のようで、米国の大手のデジタル半導体メーカーの受注契約を目前に控えているとの事。フィリピンではユーザーの利用を想定した「VARON」の組込みテストなどを担当するようだ。

「VARON」の価格は検証用途にライセンスを購入する場合は1000万円、製品としてチップに実装する場合はロイヤリティ契約(単価の約2%)になるとの事。

関連記事:

2014年の世界半導体市場は過去最高の3358億ドルで前年比9.9%の成長

2015.02.03

2015年2月2日、米SIA(Semiconductor Industry Association)は、2014年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年12月の世界半導体売上は前年同月比9.3%増、前月比2.2%減の291.3億ドルで12月の売上としては過去最高を記録した。

2014年の半導体市場は1月から12月まで全ての月で過去最高の売上を計上、2014年の売上合計額は前年比9.9%増の3358億ドルで、当然ながら過去最高となった。

2014年世界半導体市場の売上を主要製品カテゴリ別に見ると以下の通り。

・ロジック売上916億ドル(前年比6.6%増)

・メモリ売上792億ドル(前年比18.2%増)

・マイクロプロセッサ売上587億ドル(前年比5.8%増)

・アナログ売上444億ドル(前年比10.6%増)

・ディスクリート売上202億ドル(前年比10.8%増)

メモリ売上の中でもDRAMの成長は凄まじく前年比34.7%増を記録。また、パワー・トランジスタも前年比16.1%増の119億ドルと大きな成長を見せた。

2014年世界半導体市場の売上を地域別に見ると以下の通り。

・アジア・パシフィック市場売上1943億ドル(前年比11.4%増)

・北米市場売上693億ドル(前年比12.7%増)

・ヨーロッパ市場375億ドル(前年比7.4%増)

・日本市場348億ドル(前年比0.1%増)

日本は2010年以降、ドルベースで初の売上前年比増を達成。円ベースで見ると前年比約8.5%の成長となる。(年間平均レートで算出)

WSTS(世界半導体市場統計)が2014年11月に発表した予測によると、2015年の世界半導体市場の成長率は3.4%となっている。(WSTSは2013年11月に2014年の成長率を4.1%と予測していた。)

※SIA

AldecがCDC検証ツール「ALINT-PRO-CDC」をリリース

2015.02.02

2015年1月29日、各種検証ソリューションを手掛けるAldecは、新製品となるCDC検証ツール「ALINT-PRO-CDC」のリリースを発表した。

Aldecによると新製品「ALINT-PRO-CDC」は下記3つの機能で構成されている。

・スタティック構造検証:

?クロックとリセット、非同期クロックドメインとその乗り換えポイントを自動検出

?切り換えをチェックして同期を確認し、ベストプラクティスと比較検証

・デザイン制約設定:

?クロック・ネットワーク解析の結果をベースに初期SDCファイルを作成

?デザイン制約のカスタム拡張機能と正確なリント・チェック

→合成できないモジュールやカスタム同期機能を記述可能

・ダイナミック機能検証 (Riviera-PROTMとの連携)

?自動でSystemVerilogテストベンチを生成

?メタステーブルを通常のシミュレーション・ベースの検証フローで処理

?アサーション文、カバレッジ文による同期やクロックドメイン乗り換えのチェック

「ALINT-PRO-CDC」は既にリリース中で無料の評価版も用意されている。

AtrentaのCEO Dr. Ajoy Bose氏がEDA Consortiumのボードメンバーに

2015.02.02

2015年1月29日、米国のEDA業界団体EDA Consortiumは、Atrentaのチェアマンであり社長兼CEOのDr. Ajoy Bose氏が同団体のボードメンバーに就任した事を発表した。

EDA ConsortiumはCadenceとPDF Solutionsの両CEOが共同チェアマンを務め、役員としてはSynopsys, IC Manage, Sonics, Mentor Graphics, ARMの各CEOが名を連ねているが、ここにAtrentaのCEOも加わる形となる。

これらボードメンバーの任期は2016年春まで。昨年春に発表された新役員にはNimbic社のCEOも含まれていたが、その後Mentorに買収された為Nimbic社のCEOはボードメンバーから外れた。

MentorがAlteraらと「HyperLynx Alliance」を立ち上げ-クラウドで高速PCB設計を評価

2015.01.29

2015年1月28日、Mentor Graphicsは、パートナー企業数社と共に「HyperLynx Alliance」を立ち上げた事を発表した。

Mentorによると「HyperLynx Alliance」は、PCB伝送路シミュレータ「HyperLynx」をベースとした高速PCB設計向けのソリューションをグラウド環境上で提供する。Altera、PMC-Sierra、Samtec、eASICが立ち上げメンバーとして名を連ねている。

「HyperLynx Alliance」が提供するのは「仮想ラボ」と呼ぶ無償の評価環境で、Mentorの「HyperLynx」、パートナー企業のIBIS-AMIモデル、Sパラメータモデル、リファレンスデザイン、テストケース、利用ガイドなどで構成されている。

「仮想ラボ」は、高速プリント基板のSerDes設計およびDDR設計の課題解決をターゲットとしており、設計者は「仮想ラボ」を利用する事で推奨検証メソドロジとチャネル設計見本を使ってデバイスパラメータの評価とトレードオフを実行する事が可能。仮想ラボでの成果物は、実設計と実装段階において再利用できるという。

現在Altera向けの「仮想ラボ」が無償提供されており、続いてPMC-Sierra、Samtec、eASIC向けの仮想ラボがリリースされる予定。

Cadenceの11世代目の「Tensilica Xtensa」はローパワー&省メモリを実現

2015.01.27

2015年1月13日、Cadenceは同社のコンフィギュラブル・プロセッサ「Xtensa」の最新版を発表した。

Cadenceが発表した新しい「Xtensa」はTensilicaプロセッサとして11世代目に当たる製品で、Xtensa LX6とXtensa 11の2系統のラインナップ。既に製品としての出荷が開始されている。

新世代製品として大きく変わったのは、「Xtensa LX6」において4から16バイトまでの任意の命令長のVLIW命令が使用可能となった点。これによりコード・サイズを最大25%削減することが可能となりローカル・メモリやキャッシュのサイズを削減できるようになった。

またその他にも以下の通り、複数のローパワー化が実現されている。

・キャッシュ・メモリを動作中にパワー・ダウンするオプションを用意

ローカル・メモリの消費電力を最大75%削減可能

・プロセッサコアのダイナミック・スイッチング・パワーを最大25%削減可能

・関数の高速化によりデータ・キャッシュの読み出し回数を削減

システムの消費電力を削減可能

Synopsysのセキュリティ機能搭載HDMI 2.0 IPがHDMIの認証を取得

2015.01.26

2015年1月22日、Synopsysは、同社HDMI 2.0 IPの認証取得について発表した。

Synopsysの発表によると、同社のDesignWare HDMI 2.0 Transmitter/Receiverデジタル・コントローラIPならびにPHY IPが、HDMIの認証を取得。同設計IPはElliptic Technologies社の組込みセキュリティ機能を搭載しており、組込みセキュリティ仕様HDCP 2.2の認証も取得しているという。

SynopsysのDesignWare HDMI 2.0IPはファウンダリ各社の28nmプロセスならびに16nm FinFETプロセスに対応しており、シリコン実証済の形で提供される。

またSynopsysは、「DesignWare IP Prototyping Kit for HDMI 2.0」も提供しており、HDMI 2.0IPのプロトタイピングと統合に必要となるハードウェアとソフトウェアを提供している。

Synopsysがモバイル・インタフェース向けにUFS、UniPro、eMMCの検証IPをリリース

2015.01.26

2015年1月21日、Synopsysは、新たな検証IPのリリースを発表した。

今回Synopsysがリリースした検証IPは、JEDECのメモリ規格「UFS(Universal Flash Storage」、「eMMC(embedded MultiMediaCard)」ならびにMIPIのインタフェース規格「UniPro(Unified Protocol)」向けの検証IPで、これらプロトコルを採用するSoCの検証を加速する。

新しいUFS、UniPro、eMMCの検証IPは、単品製品、SynopsysVIPライブラリ、Verification Compilerの一部として提供中。Synopsysは既にUFS、MIPI UniPro、eMMCの設計IP(コントローラIP)も提供している。

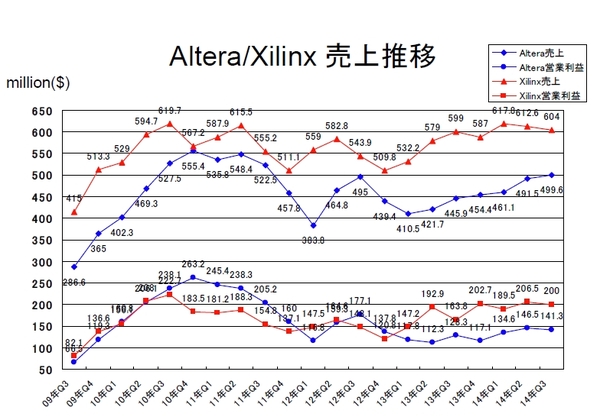

Altera売上報告、14年10-12月は前年比6%増の4億7990万ドル、14年合計は前年比12%増

2015.01.26

2015年1月22日、Alteraは2014会計年度第4四半期(14年10-12月)の売上を報告した。

発表によるとAlteraの2014年Q4売上は、前年比約6%増、前期Q3比約4%減の4億7990万ドル、営業利益は前年比約3%増の1億2087万ドルだった。このQ4の売上実績は前四半期の売上報告時の予測通り。Alteraは2013年Q2より6四半期連続で売上を伸ばし続けていたが、1年半振りに四半期売上が前四半期売上を下回った。

Alteraの2014会計年度の売上合計は19億3200万ドルで前年比12%増、営業利益は5億4336万ドルで14.2%増だった。

Alteraの2014年Q4の売上の内訳を見ると最新の20nm FPGA「Arria 10」を含む新製品カテゴリの売上が前Q3よりも3%伸びており、売上全体に占める割合が59%と拡大。地域別では日本と欧州の売上が伸びた。

Alteraは次期2015年Q1(1-3月)の売上を2014年Q4の±0%から-4%と予測している。

バージョンアップでOVM/UVMユーザーへの利用メリットが向上したAldecの「HES-DVM」

2015.01.23

2015年1月15日、Aldecはハードウェアエミュレーション・ソリューションのソフトウェア「HES-DVM™」の最新バージョン 2014.12 をリリースした。

「HES-DVM™」は、Aldecの提供するプロトタイピング・プラットフォーム「HES-7™」だけでなく、市販のFPGAボードや社内開発のFPGAプロトタイピング・ボードにも利用できるデザイン・ベリフィケーション・マネージャ (DVM)で、ハードウェアを用いたシミュレーション・アクセラレーションやエミュレーションをサポートする。

Aldecは今回のバージョンアップでOVM/UVMシミュレーション・フローにSCE-MIベースのハードウェア・エミュレーションを導入し易くなるよう「HES-DVM」の機能およびサポート範囲を拡張した。

またエミュレーション向けの機能拡張と合わせて、OVM/UVMシミュレーション・アクセラレーション・インタフェースも大幅に高速化した。この高速化にはDPI-C関数の定数引数を最適化する「SCE-MI Clocks Turbo Mode」と呼ばれる自動クロック・リスケール技術が利用されている。

Aldecは今回の「HES-DVM」のバージョンアップによって、SCE-MIトランザクタをFPGAにインプリメントする際に使うチップリソースも小さくなり、エミュレーション実行全体の所要時間も大幅に短縮できるとしている。

尚、アルデックはFPGAベースのプロトタイピング・ボード「HES-7™」を提供しているが、同社のWebサイトには最新のボード「HES7VX12000BP」が紹介されている。 「HES7VX12000BP」はXilinxの28nmFPGA Virtex-7 2000Tを6個搭載するボードで最大7200万ASICゲートに対応可能。同ボードは4枚接続可能で最大2億8800万ASICゲートのデザインを扱うことができるようだ。

「HES7VX12000BP」はXilinxの28nmFPGA Virtex-7 2000Tを6個搭載するボードで最大7200万ASICゲートに対応可能。同ボードは4枚接続可能で最大2億8800万ASICゲートのデザインを扱うことができるようだ。

Xilinx売上報告、14年10-12月は前年比1%増の5億9400万ドル

2015.01.23

2015年1月21日、Xilinxは2015会計年度第3四半期(2015年10-12月)決算を報告した。

Xilinxの2015会計年度Q3の売上は、前年同時期比1%増、前期Q1比2%減の5億9400万ドル。営業利益は前年比5%減の1億9000万ドルだった。売上額は昨年10月時点の同社の目標値を下回り、3四半期連続で売上が減少する形となった。(※GAAP基準による会計結果)

XilinxのCEOはQ3に28nm製品の売上が大幅に回復すると予測していたが、実際にQ3売上における28nm製品の売上はQ2比20%増の1億5000万ドルに達した。しかし新製品カテゴリ(Virtex® UltraScale™, Kintex® UltraScale, Virtex-7, Kintex7, Artix®-7, Zynq®-7000, Virtex6, Spartan®6 products)という括りで見ると売上全体に占める割合は43%でQ2と大きな違いはない。

Xilinxは、次期2015年Q4(15年1-3月)の売上を今期実績の2%-6%減と予測をしている。

メガチップスがExcelliconのSDC生成、検証、マネジメントツールを採用

2015.01.22

2015年1月20日、タイミング制約に関する包括的なEDAソリューションを提供する米Excelliconは、メガチップスが同社のSDCソリューションを採用した事を発表した。

発表においてはメガチップスが採用した個別の製品名は挙げられていないが、ExcelliconはSDC生成ツール「ConMan」、SDC解析ツール「ConCert」、タイミング制約サインオフ・ツール「ConSTAr」を提供中。同社のSDCソリューションは、大規模SoCデザインをターゲットにしており、SDCの解析、デバッグ、生成において既存の市販ソリューションを上回るパフォーマンスを発揮するとされている。そのベースとなるのはフォーマル解析技術を用いた特許取得済みの同社独自のアルゴリズムだ。

Excelliconはここ数年売上を順調に伸ばし続けており、半導体上位10社は既に同社の顧客もしくは同社の製品を評価中という状況である。

富士通が3次元構造の次世代プロセッサ開発でANSYSのパワー解析ツールを採用

2015.01.22

2015年1月13日、パワー解析・最適化ソリューションを手掛けるApache Designを傘下に持つANSYSは、富士通による同社EDAツールの採用事例を発表した。

発表によると富士通はTSV(through-silicon-via)を用いた3次元構造の次世代プロセッサ開発でANSYSのパワー解析ツール「RedHawk」と「Sentinel」を採用。富士通の担当者は両ツールの利用により、パワー、性能、チップのコストに合ったデザインの最適化が可能となるとコメントしている。

UMCとCadenceが28nm設計リファレンス・フローで協業

2015.01.22

2015年1月21日、CadenceはUMCとの協業成果について発表した。

今回発表されたのは、UMC 28nmプロセスの設計リファレンス・フローの実現に関する協業で、UMCはCadenceのEDAツールをベースに既存のソリューションよりも短TATで高性能なチップを実現する設計フローを構築した。

同フローを用いて製造した28nm ARM® Cortex®-A7 MPCoreベースSoCは、1.7GHzの目標性能を達成し、これまで使用していたソリューションよりもダイナミック・パワーを20%削減、テープアウトまでの時間は33%削減出来た。

UMCは既にARM® Cortex®-A7 MPCoreベースSoC向けのリファレンス・デザインを顧客に提供している。

今回の28nmリファレンス・フローでUMCが採用したCadenceのEDAツールは以下の通り。

・Encounter Digital Implementation System

・Tempus Timing Signoff Solution

・Voltus IC Power Integrity Solution

・Quantus QRC Extraction Solution

・Physical Verification System

・Litho Physical Analyzer

・CMP Predictor

Mentorがバーチャル・プロトタイプ・キットの提供を開始、まずはCortex-A9ベース

2015.01.21

2015年1月21日、Mentor Graphicsは、新たなソリューションとして「Mentor® Embedded Virtual Prototype Kits(VPK)」の提供を開始した事を発表した。

Mentorの提供する「VPK」は、ソフトウェア開発のために利用するコンピュータ上で動く仮想ハードウェアで、同社のESLツール「Vista」および組込みソフト統合開発環境「Sourcery™ CodeBench Virtual Edition」で利用できる。

仮想ハードウェアは、CPUモデル、バスモデル、周辺回路モデルを組み上げて作るが、手間がかかるためキットで提供されると開発者は嬉しい。

同じようなバーチャル・プロトタイプ・キットは、SynopsysやCarbon Design Systemsが提供しているが、CPUをはじめとした各種モデルの構造とバリエーションに各社の違いがある。

Mentorはまずは下記各デバイス向けの「VPK」を提供開始。いずれもARM Cortex-A9がベースとなっている。

「VPK」はMentorのSupportNet(https://supportnet.mentor.com)内の製品ダウンロードページからダウンロードできる。

●VPKのラインナップ:

-Altera Arria-V

-ARM Versatile Express for Cortex A-9

-Freescale i.MX 6プロセッサ

-Xilinx Zynq

※メンター・グラフィックス・ジャパン株式会社

グラフィックスIPコアのDMPがCadenceのアクセラレータ/エミュレータPalladium XP採用

2015.01.21

2015年1月20日、Cadenceは、グラフィックスIPコアを手掛けるDMPがアクセラレータ/エミュレータ「Palladium XP」を採用した事を発表した。

DMPはCadenceの「Palladium XP」を使ってシリコンが届く前にIP製品向けのソフトウェアスタックの開発を完了。これまで利用していたソリューションよりも最大500倍高速なシミュレーション性能を実現した。

システム・エミュレーションでは、DDR3 DFI(DDR PHY Interface)、SD(Secure Digital)インターフェイスをはじめとする周辺回路向けのモデルを使用した。

発表にコメントを寄せているDMPの大渕氏は、「Palladium XPプラットフォームのモデリング機能」が設計工数減に繋がったと評価している。

2014年Q3世界EDA売上は前年比5.7%増の約18億2810万ドル-日本は3%減

2015.01.21

2015年1月16日、米EDA Consortiumは、2014年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

EDACの発表によると、2015年Q3の世界のEDA売上総額は、前年比5.7%増、前Q2比4.0%増の18億2810万ドルで、Q3の売上記録として過去最高を達成。四半期の売上記録が前年同時期を上回るのはこれで19四半期連続となる。

2014年Q3の売上を製品分野別に見るとIP分野がQ2に続いて前年比20%増以上の成長。サービス分野も大きく伸び初の1億ドル台に乗せた。IPとサービスの伸びは確実に業界の実態を反映した結果と言える。

2014年Q3の売上を地域別に見ると、強い米国が更に強くなり、それを二番手のアジアが追随する構図。アジア市場は売上5億ドルが目前となった。日本市場は前年比15.3%減の約1.9億ドルで円ベースでみても前年比約3%減となっている。

2014年Q3時点でのEDA業界の従業員数は前年比5.6%増、前期Q2比1.2%増の31648人で過去最高を記録した。

2014Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億450万ドル 6.1%Down

■IC Physical Design & Verification分野 3億5780万ドル 1.4%Down

■IP分野 5億8610万ドル 22.9%Up

■サービス分野 1億1240万ドル 20.2%Up

■PCB/MCM分野 1億6740万ドル 9.7%Up

2014年Q3地域別の売上と昨年同時期との比較は以下の通り。

■北米 8億4020万ドル 9.2%Up

■ヨーロッパ 2億9680万ドル 4.0%Up

■日本 1億8950万ドル 15.3%Down

■アジアその他地域 4億9990万ドル 11.3%Up

東芝がアプリケーション・プロセッサ「TZ2100」開発でSONICSのNoCを採用

2015.01.14

2015年1月13日、インターコネクトIPの業界大手SONICSは、東芝がアプリケーション・プロセッサ「TZ2100」グループの開発でSONICSのインターコネクトIPを採用した事を発表した。

東芝のアプリケーション・プロセッサ「TZ2100」グループは、ARM Cortex-A9 MPCoreをベースとした「TZ2000」シリーズの上位品となる組込み向けプロセッサで、「TZ200x」よりも高速かつ省電力で通信セキュリティが強化されている。製品としてはTZ2100XBG/TZ2101XBG/TZ2102XBGの3種類が用意され、最大動作周波数600MHzまで対応している。

東芝は約12年に渡りSONICSのインターコネクトIPのユーザーとして数々のSoCにSONICS製品を採用しており、既にSONICSのIPを搭載したSoCの出荷は2億を超えているとの事。今回の「TZ2100」での採用はこれまでの実績から必然の流れと言える。

尚「TZ2100」グループは昨年発表されたばかりの新製品で2015年6月より量産出荷の予定。

MentorがFPGAプロトタイピング向けコンパイラの仏Flexras Technologiesを買収

2015.01.14

2015年1月13日、Mentor GraphicsはFPGAプロトタイピング向けのデザイン・パーテショニング・ツールを手掛ける仏Flexras Technologiesを買収した事を発表した。

Flexras Technologiesは、ピエール・エ・マリー・キュリー パリ VI大学とパリのコンピュータ・サイエンス研究機関「LIP6」での研究成果をベースに2009年に設立されたEDAベンチャーで、FPGAベース・プロトタイピング向けのデザイン自動分割マッピング・ツール「Wasga Compiler」を提供している。

「Wasga Compiler」は、独自のタイミング・ドリブンなパーティショニング手法により、大規模ASICデザインを複数FPGAに最適かつ短時間で分割実装する事が可能で、クロック周波数を10倍向上出来るとしている。

Mentor Graphicsは、FPGAベースのプロトタイピング環境を製品として提供していないが、今回買収したFlexras Technologiesの技術を元にFPGAベースのプロトタイピング・ソリューションを出してくるのかもしれない。

ちなみにFlexras Technologiesと同じフランスのREFLEX CES社は、提供するプロトタイピング・ボードのソフトウェア環境として「Wasga Compiler」を利用している。

2014年11月の世界半導体市場は前年比9.1%増の297億ドル、単月売上記録の更新途切れる

2015.01.06

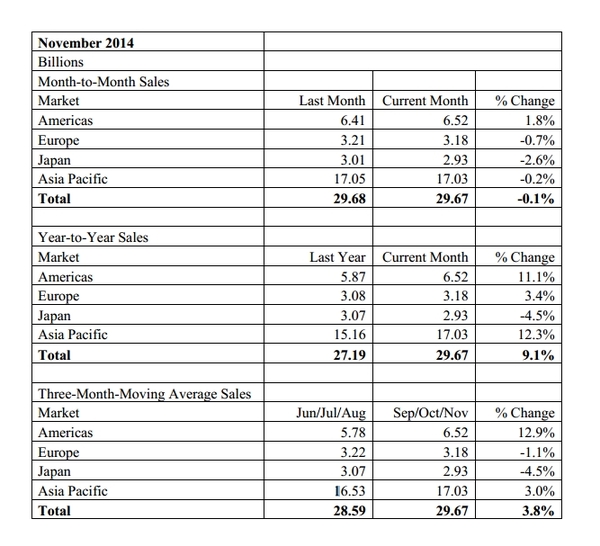

2015年1月5日、米SIA(Semiconductor Industry Association)は、2014年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2014年11月の世界半導体売上は前年同月比9.1%増、前月比0.1%減の296.7億ドル。売上が前月実績を下回るのは9ヶ月ぶりで、今年6月から5ヶ月連続で単月の売上記録を更新していたが遂に記録更新が途絶えた。とは言え、売上額は高水準を維持しており、既に11月時点の14年売上累計が13年売上合計に到達。14年の世界半導体市場は前年比10%増近くの成長となる事がほぼ確実となった。

2014年11月の売上を地域別に見ると、北米市場以外は全て前月実績を割り込んだ。前年比で見ると日本市場以外は全てプラス成長。日本市場はドルベースでは昨年実績を割り込んでいるが、円ベースでは前年比10.7%近くの売上増となっている。

※SIA

Synopsysのデバッグ環境「Verdi」で使えるカスタム・アプリが100種以上に

2014.12.26

2014年12月16日、Synopsysは、同社のデバッグ環境「Verdi」で使用できるデバッグ/解析アプリケーション・ソフトウェアが100種を超えたことを発表した。

「Verdi」用のデバッグ/解析アプリは、2011年に旧SpringSoft社が「Verdi」のデータベースとGUIのインタフェースを公開した事によって生まれたカスタム・アプリで、VerdiのユーザーやサードパーティーEDAベンダによって開発されている。これらアプリはSynopsysによるSpringSoft買収後も継続して公開・提供されており、現在ではWebサイト「VC Apps Exchange」とソフトウェア・パッケージ「Verdi VC Apps ToolBox」を通じて入手できる。

※画像は「VC Apps Exchange」のスクリーンショット

Verdi用のカスタム・アプリ「VC Apps」は、ユーザーの細かな検証ニーズを補完するために開発されたものと、「Verdi」とサードパーティーEDAツールのインテグレーションを実現するために開発されたものと大きく2種類あり、公開・提供されているものは「Verdi」ユーザーであれば自由に利用できる。

発表に寄せられたコメントによると、ルネサスシステムデザインでは、階層間の結線チェックの効率化、故障シミュレーションの解析、ドキュメンテーションの自動化などに「VC Apps」を利用しているという。

GLOBALFOUNDRIESとCadenceが28nm-SLPプロセスでARM Cortex-A17ベース・チップを製造

2014.12.25

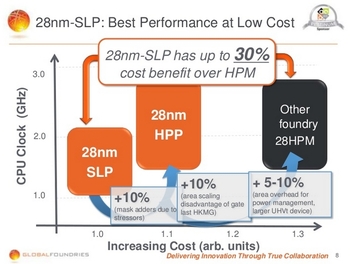

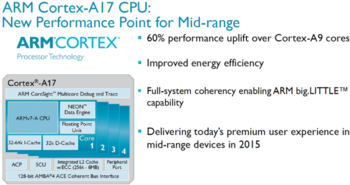

2014年12月18日、GlobalfoundriesとCadenceは、両社の協業によるARM Cortex-A17ベース・テスト・チップの成功事例を発表した。

発表によると両社は今回GlobalfoundriesのHigh-k Metal Gate 28nm Super Low Powerプロセスを使用してARM Cortex-A17ベースのクアッド・コア・テスト・チップを製造。同チップはCadenceのEDAツールのみでテープアウトされ、CadenceのSTA「Tempus」の予測通りとなる標準動作条件で2.0GHzの性能を達成した。

両社はこの成功を受けて最新のARM Cortex-A17 processor RTL、ARM POP IPを用いて2つ目のテスト・チップを製造。その結果、最大周波数2.0GHzのサインオフ目標を達成しつつ最初のテストチップよりもシングル・コアのチップ面積を23%縮小することに成功した。

※画像はGLOBALFOUNDRIESの公開データ

テスト・チップの設計に使用されたのは、下記Cadenceツールで2個目のテスト・チップ設計では、これらツールに加えパワー・インテグリティ解析ツール「Voltus」とローパワー設計考慮の等価性検証ツール「Encounter Conformal Low Power」も使用されたという。

-Encounter® Digital Implementation System

-Encounter RTL Compiler

-Quantus™ QRC Extraction Solution

-Tempus Timing Signoff Solution

-Encounter Conformal® Equivalence Checker

-Physical Verification System

-Litho Physical Analyzer

ARMの「Cortex-A17」は今年発表されたばかりのミッドレンジ向けCPUで「Cortex-A9」の置き換えソリューションとされている。未だ市場には「Cortex-A17」を搭載した製品は登場しておらず、公にアナウンスされたテスト・チップの実装例は恐らく今回が業界初。Cadenceはここ数年、ARMのリリースする新CPUコアをいち早く各半導体ファンドリの先端プロセスで実現する事に注力しており、TSMC 20/16nm、Samsung14nm、IBM14nmなど様々なプロセスにおいて先行する形でテスト・チップのテープアウト実績を残している。

※画像はARMの公開データ

Aldecの設計要求管理/追跡ツール「Spec-TRACER」がIBMの「Rational DOORS」と連携

2014.12.24

2014年12月10日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、同社の設計要求管理/追跡ツール「Spec-TRACER」のバージョン・アップを発表した。

Aldecによると「Spec-TRACER」の最新バージョン 2014.12では、IBMの要求管理アプリケーション「IBM® Rational® DOORS®」との双方向連携がサポートされ、「DOORS」で定義された要求と属性の「Spec-TRACER」データベースへのインポート、および「Spec-TRACER」で管理・作成されるFPGAデザイン関連項目の「DOORS」データベースへのエクスポートが可能となった。

「Spec-TRACER」で管理・作成されるFPGAデザイン関連項目としては、FPGAデザインの要求、HDLデザイン・テストベンチのタグ、トレーサビリティ・データ、テストケース、ログファイル、波形、コードカバレッジ結果などがあるという。

その他、「Spec-TRACER 2014.12」では、CSV形式のトレーサビリティ・ファイルのインポートが可能となったほか、トレーサビリティ機能の改善、「Spec-TRACER」データベースと機能カバレッジの連携などが実現された。

※画像はAldec社Web上のデータ

Alteraの20nm FPGA「Arria 10」が業界最高のDDR4データ・レート2666Mbpsを達成

2014.12.24

2014年12月22日、Alteraは、同社の20nm FPGA「Arria 10」のDDR4 SRAMメモリ・インタフェースが業界最高のデータ・レート2666Mbpsで動作する事を実証したと発表した。

Alteraの20nm FPGA「Arria 10」は、カタログ・スペックとして業界最高性能の2666Mbps DDR4 SRAMメモリ・インタフェースのサポートをうたっているが、今回それを実シリコンによるデモで実証したとの事。この性能は同社の前世代のミッドレンジFPGAと比較して43%、競合他社の20nm FPGAより10%優れているという。

この「Arria 10」のDDR4 SRAMメモリ・インタフェースは、FPGA内でメモリ・コントローラと共にハードウェア化されており、ソフトウェア実装よりも高性能、広帯域幅、低消費電力を実現。DDR4メモリを搭載するシステムの開発が格段に容易となる。

またこの他にも「Arria 10」にはハード化されたフローティング・ポイントDSPブロックが備えられており、ユーザーは業界最高水準の1.5TFLOPSのDSP性能を利用することができる。

同社の専用設計環境「Quartus II」の最新バージョンv14.1は、これらパフォーマンスを備えた「Arria 10 FPGAおよびSoC」を既にサポートしている。

※画像はAltera社Webサイト上のデータ

SynopsysがLPDDR4向け検証IPをリリース

2014.12.18

2014年12月9日、SynopsysはJEDECの策定するモバイル・デバイス向けのDRAM規格LPDDR4向けの検証IPのリリースを発表した。

SynopsysのLPDDR4 検証IPは、SystemVerilogでコーディングされたモデルで、検証プランニング機能、ビルトイン・カバレッジ解析機能、Verdi Protocol Analyzerのプロトコル考慮メモリー・デバッグ機能、トランザクタ/モニター機能などを備えている。

LPDDR4の検証IPはCadenceがSynopsysに先行して提供中。またMentor Graphicsは、LPDDR4を同社のエミュレータ「Veloce」上で検証するためのデバイス・モデルを用意している。

AldecのFPGA向け論理シミュレータ「Active-HDL」が64ビット対応

2014.12.18

2014年12月8日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldec社は、同社のFPGA設計向け論理シミュレータ「Active-HDL」が64ビット・シミュレーションに対応した事を発表した。

「Active-HDL」はFPGA設計にフォーカスしたコスト・パフォーマンスの高い論理シミュレータで、アジア地域において大きな支持を得ている。

昨今、FPGAデバイスの大規模化・複雑化が進みユーザーのニーズが高まったため、Aldecは「Active-HDL」の64ビット対応を行った。

「Active-HDL」には複数の製品グレードが存在するが、64ビット版は上位グレード製品向けの設定。既に上位グレードの「Active-HDL」を利用しているユーザーは、無償で64ビット版にアップデートできる。

「Active-HDL」はFPGA設計にフォーカスしたコスト・パフォーマンスの高い論理シミュレータで、アジア地域において大きな支持を得ている。

昨今、FPGAデバイスの大規模化・複雑化が進みユーザーのニーズが高まったため、Aldecは「Active-HDL」の64ビット対応を行った。

「Active-HDL」には複数の製品グレードが存在するが、64ビット版は上位グレード製品向けの設定。既に上位グレードの「Active-HDL」を利用しているユーザーは、無償で64ビット版にアップデートできる。

ARM売上報告、14年7-9月は前年比約12%増の3億2020万ドルで売上記録更新

2014.12.16

2014年10月21日、ARMは、2014会計年度第3四半期(2014年7-9月)の売上を報告した。

※売上報告記事の掲載が遅くなりました。

ARMの2014年Q3の売上は、前年比約12%増、前期比約3.4%増の3億960万ドルで前Q2に続いて四半期売上記録を更新した。税引き前の純利益は前年比約9%増の約1億6570万ドルだった。

ARMの2014会計年度の売上合計は前年比15%増の9億3500万ドル、純利益の合計は前年比9%増の4億8030万ドルとなっている。

ARMのQ3売上の内訳を見ると、ライセンスの売上が前年比約16%増の1億4250万ドル、ロイヤリティの売上は前年比9%増の1億5020万ドルだった。ライセンスの売上としては前年と比較してプロセッサ・ライセンスよりもフィジカルIPの成長率の方が高かった。

プロセッサ・ライセンスはこのQ3で43件の契約を獲得。うち半数の22件はCortex-Mプロセッサのライセンスで、7件は最新のARMv8-Aアーキテクチャ・ベースのプロセッサとなる。43件という契約数は過去最高の実績である。ライセンス内訳は下記の表の通り。

※画像はARM発表資料より抜粋

2014年Q3で出荷されたARM搭載チップの総数は約30億個で、マイクロ・コントローラとネットワーキング向けに大きく伸びた。30億個のうち11億個はマイクロ・コントローラとスマート・カードだという事でCortex-Mシリーズの出荷が増えている。

※画像はARM発表資料より抜粋

Altera売上報告、14年7-9月は前年比12%増の4億9960万ドル-6四半期連続売上増

2014.12.16

2014年10月23日、Alteraは2014会計年度第3四半期(14年7-9月)の売上を報告した。

※売上報告記事の掲載が遅くなりました。

発表によるとAlteraの2014年Q3(14年7-9月)売上は、前年比約12%、前期Q2比約2%増の4億9960万ドル、営業利益は前年比約66%減の1億4132万ドルだった。このQ3の売上実績は前四半期の売上報告時の予測通りで、前年比2ケタ成長はQ2に続いて3四半期連続、売上が前四半期を上回るのは6四半期連続となる。

Alteraの2014年Q3の売上を製品別売上を見ると最新の20nm FPGA「Arria 10」を含む新製品カテゴリの売上が前Q2よりも9%伸びており、売上全体に占める割合が56%と拡大した。

Alteraの2014年Q3の売上を地域別で見ると、前Q2と同様に北米と欧州の売上比率が上がり日本は落ちた。分野別ではネットワーキング、コンピュータおよびストレージ分野の売上が前Q2よりも14%伸びている。

Alteraは次期2014年Q4(10-12月)の売上を2014年Q3の-2%から-6%と今期実績を割り込む予測をしている。

年明け1/19より幕張メッセでASP-DAC 2015開催-参加登録受付中

2014.12.16

2015年1月19日から22日まで幕張メッセにてASP-DAC 2015が開催される。

2年おきに日本で開催されているASP-DACはASP-DACは、VLSIとシステムの設計技術に関するアジア・南太平洋地区最大の国際会議で今回は20回目の開催。

基調講演は下記の3者が登壇の予定で、計6のチュートリアル、計108の論文発表が行われる計画。

1.Dr. Udo Wolz(ボッシュ(株)取締役副社長),

"The required technologies for Automotive towards 2020"

2.高原 厚 博士(NTT未来ねっと研究所 所長),

"Programmable Network"

3.新井 紀子 博士(国立情報学研究所 教授),

"When and how will an AI be smart enough to design?"

また、次世代カーエレクトロニクス、4K/8K TV技術、データセントリック・コンピューティング・プラットフォーム、IPベースSoCデザインとIPデザインのイノベーションをトピックとしたデザイナーズ・フォーラムと合わせて下記5つの特別セッションが実施される予定。

・"Internet of things"

・"The Future of Emerging ReRAM Technology"

・"Machine Learning in EDA: Promises and Challenges in Selected Applications"

・"New Challenges and Solutions in Nanometer Physical Design"

・"System-Level Designs and Tools for Multicore Systems"

更に、大学での最先端LSIの設計事例を完成度の高さで競い合うデザインコンテストでは、実デバイスで実証済の論文が20件以上発表される予定となっている。

ASP-DAC 2015のプログラム詳細および参加登録はこちら

Mentorが新しいデザイン考慮の検証IP「EZ-VIP PCI Express」をリリース

2014.12.15

2014年12月10日、Mentor Graphicsは新たな検証IP「Mentor® EZ-VIP PCI Express」のリリースを発表した。

Mentorによると新しい検証IP「EZ-VIP PCI Express」は、従来の検証IPとは異なりデザインを考慮できるため、設計プロジェクト毎に行うテストベンチの構成、実装セットアップなどテストベンチ組立てに必要ないくつもの作業を省くことが可能。Mentorはこれによりテストベンチの構築時間を最大で10倍加速できるとしており、発表には「EZ-VIP PCI Express」を支持するARM、PLDA、Northwest Logicのコメントが寄せられている。

「EZ-VIP PCI Express」は、PCIe 1.0、PCIe 2.0、PCIe 3.0、PCIe 4.0、mPCIeをサポート。PHY、ルートコンプレックス、エンドポイントの検証にも対応している。

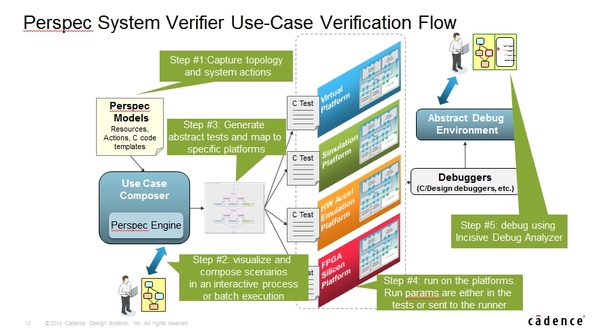

Cadenceがソフトウェア・ドリブンSoC検証の新製品「Perspec™ System Verifier」を発表

2014.12.12

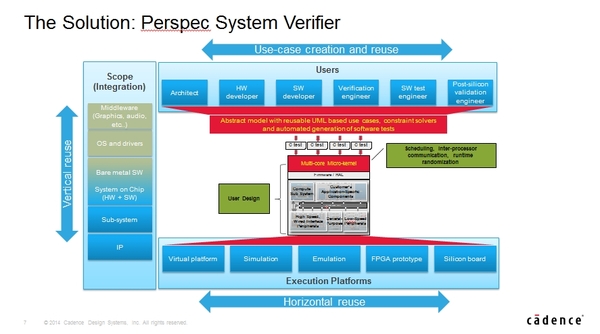

2014年12月11日、Cadenceはソフトウェア・ドリブンSoC検証向けの新製品「Perspec™ System Verifier」を発表した。

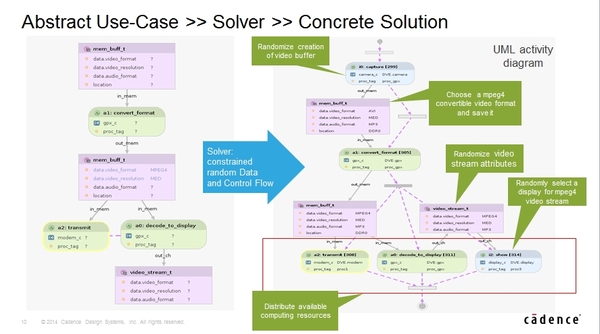

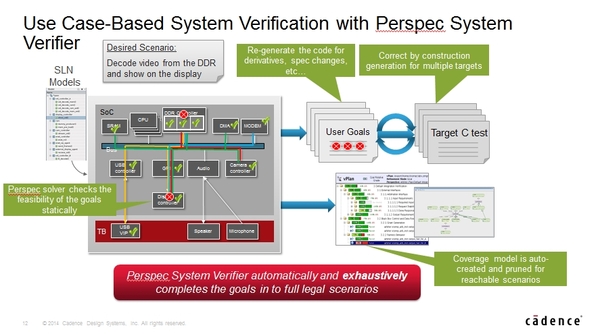

「Perspec™ System Verifier」はソフトウェアを用いたSoC検証のためのツールで、簡単に表現すると、SoCの仕様情報とユーザーが定義したシナリオからCのテストコードを自動生成してくれるツールである。同種の製品としては、Breker Verification Systemsが「TreKSoC」という製品を出しているが、Cadenceの「Perspec™ System Verifier」はそのコンセプトからして大きく違う。

「Perspec™ System Verifier」の目指すのは、同社がこれまで培ってきた制約付きランダム的な考え方やカバレッジ手法をソフトウェア・ベースのダイレクト・テストに取り込む事で、ユーザー、検証環境、検証の抽象度を問わないソフトウェア・ドリブンSoC検証の実現がコンセプトとなっている。

「Perspec™ System Verifier」の具体的な使用法としては、まずCのテストコードを生成するためにSoCを構成するリソースの情報、それら各リソースの機能/動き、接続、Cのテンプレートを用意する。

次にシナリオとしてSoCにして欲しい動作、どのように動いて欲しいかをUMLのアクティビティ・チャートで定義する。そうすると「Perspec™ System Verifier」は、前提となるリソース情報から与えられたシナリオに矛盾しないあらゆる処理パターンを自動的に洗い出しそれをCのテストコードとして出力。同テストコードを使えば、シナリオ通りにハードがアクティベートされたかどうか、どのようにハードがチェックされたかを確認出来る。

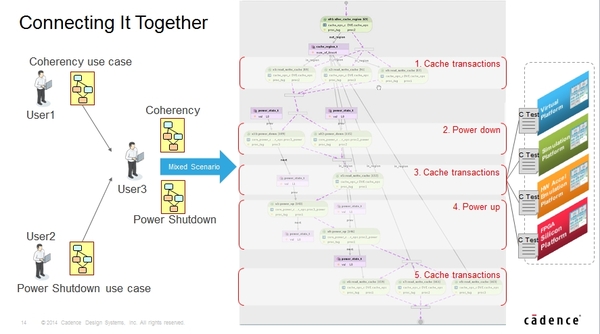

シナリオの記述においてデータ量のパラメータや使用するリソースの条件、処理の順序などを変更すれば、「Perspec™ System Verifier」はその制約条件に応じたテストコードを自動的に出力してくれるほか、複数のシナリオを組み合わせてテストコードを自動生成する事も可能。例えば、キャッシュ・コヒーレンシを確認するシナリオとパワー・シャット・オフを確認するシナリオを組み合わせて、パワー・シャット・オフしてもキャッシュ・コヒーレンシは大丈夫か?といった事を確認するテストコードを生成することも出来る。

「Perspec™ System Verifier」の生成したテストコードは、同社のシミュレータ、エミュレータ、バーチャル・プラットフォーム、FPGAプロトタイピング環境、いずれの環境でも利用する事が可能。テスト結果のカバレッジは、連携する同社の検証プロジェクト管理ツール「vManager」を用いて確認できる。

「Perspec™ System Verifier」の利用にあたってはUMLの記述が一つの壁となるが、CadenceはUMLのサンプルを含んだチュートリアルを用意しているという。