NEWS

2015.07.28

2015年7月28日、Synopsysは、業界初となるUSB Type-CをサポートするIPソリューションを発表した。

今回Synopsysが市場に投入した新製品は、「DesignWare USB-C 3.1 PHY」と「DesignWare USB-C 3.0 PHY」の2つの設計IPで、いずれも製品名にある通りUSB Type-Cコネクタ仕様をサポートしている。

Synopsysは昨年10月に業界に先駆けてUSB 3.1コントローラIPと検証IPを同時にリリースしており、今回の新製品の投入でPHY、コントローラ、検証IPとUSB 3.1/3.0の包括的なIPソリューションが整った格好だ。

SynopsysはIPビジネスの大きな柱の一つとしてUSB IPに力を注いでおり、ここのところ14年連続でUSB IP市場のトップシェアを維持。その強さの理由は、競合の追随を許さないスピード感だけでなく、豊富な実績から生まれる品質にもあるようだ。Synopsysによると同社のUSB IPのデザイン成功例は3000以上(USB2.0だけで約2800件)、出荷ユニット数は10億を超えているという。

今回発表した「DesignWare USB-C 3.1 PHY」と「DesignWare USB-C 3.0 PHY」は、それぞれ下記画像資料の通りUSB 3.1&3.0, USB 3.0&2.0をサポートしており、「DesignWare USB-C 3.1 PHY」は10Gbpsもしくは5Gbpsのデータ転送レートを提供。「DesignWare USB-C 3.0 PHY」はUSB 3.0/2.0の全ての転送モードをサポートする。また両製品共に最先端の14/16nm FinFETプロセスをターゲットに捉えている。

その他、「DesignWare USB-C 3.1 PHY/3.0 PHY」の共通の特徴としては、ピンの並びをコネクタに合わせ配線性が向上している点、シングルPHYソリューションとしてピン数を最大40%削減可能な点などが挙げられる。

またSynopsysは今回の「DesignWare USB-C 3.1 PHY/3.0 PHY」のリリースに合わせて、それらを用いたシステムの開発環境として「IP Prototyping Kit」と「Software Development kit」を用意。

「IP Prototyping Kit」は、FPGAベースのHAPSボードをベースとした実機のプロトタイピング・ソリューションで、PHYを搭載したドータ・カードをはじめUSB 3.1/3.0を動かす環境一式がパッケージで提供される。これを利用すれば通常組み上げに3ヶ月は要していたプロトタイピング環境を数日で立ち上げる事ができてしまう。

もう一つの「Software Development kit」は、バーチャル・プロトタイピング・ツール「Virtualizer」をベースとしたソフトウェア開発環境で、USB 3.1/3.0のSystemCモデルをはじめとするソフト開発向けの環境一式がパッケージで提供される。

新製品「DesignWare USB-C 3.1 PHY」と「DesignWare USB-C 3.0 PHY」は、先行リリースされているコントローラIP、検証IPと合わせて既に出荷が開始されている。

※画像は全てSynopsys提供のデータ

※画像は全てSynopsys提供のデータ

2015.07.28

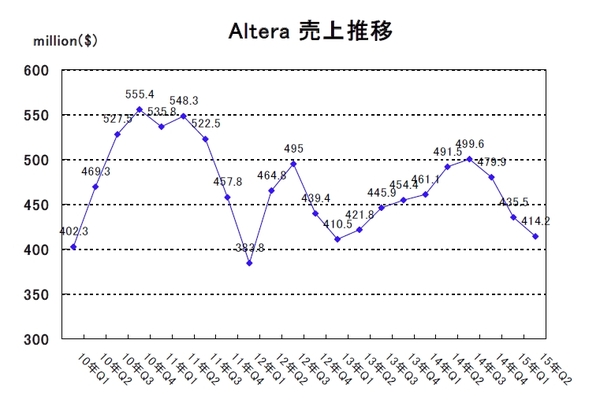

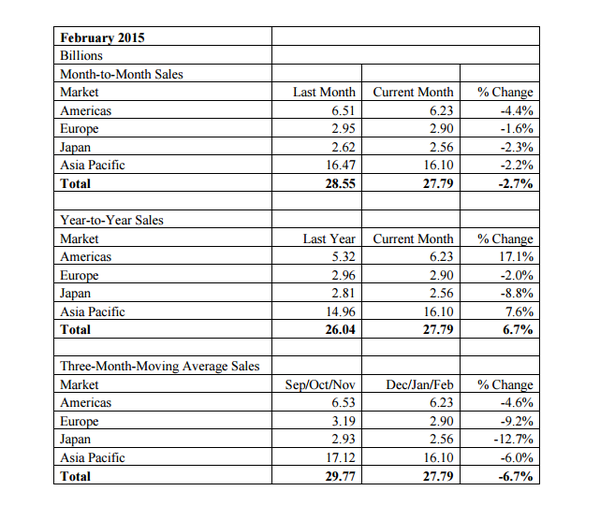

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2015.07.28

2015年7月23日、Alteraは2015会計年度第2四半期(15年4-6月)の売上を報告した。

発表によるとAlteraの2015年Q2売上は、前年比約16%減、前期Q1比約5%減の4億1420万ドル、営業利益は前年比約41%減の8633万ドルだった。このQ2の売上実績は前四半期の売上報告時の予測値通りで、Alteraは3四半期連続で前四半期売上実績を下回った。

Alteraの2015年Q2の売上の内訳を見ると、製品カテゴリ別ではArria 10, Stratix Vをはじめとする主力の新製品カテゴリの売上が前年比14%減と大きく落ちた。市場分野別ではテレコム&ワイヤレス向けの売上が前年比44%減と足を引っ張った。地域別では北米市場だけがかろうじて売上前年増を達成したが、その他全ての地域において売上を落とした

なお、Alteraは今Q2の6月1日にIntelに買収される事が正式に発表されている。買収額は167億ドルで6-9カ月以内にIntelによる買収手続きが完了する予定となっている。

2015.07.24

2015年7月22日、Xilinxは2016会計年度第1四半期(2015年4-6月)決算を報告した。 ※訂正あり

Xilinxの2016会計年度Q1(2015年4-6月)の売上は、前年同時期比約10%減、前期Q4比約3%減の5億4900万ドル。営業利益は前年比14%減の1億7800万ドルだった。(※GAAP基準による会計結果)

四半期ごとの売上額で見るとXilinxは2四半期連続で売上前年割れとなっている。

なお、XilinxによるとQ1の粗利率は71%、20nm製品の売上が1000万ドルに到達したとの事。

Q1売上を地域別に見ると、北米市場の売上が前年比18%と大きく成長した反面、他の地域は軒並み前年割れで最大市場のアジア市場は前年比24%減と大きく落ち込んだ。

アプリケーション別に見ると、主力の通信およびデータセンター向けの売上が前年比36%減と大幅減、その一方で産業、航空、軍事向け売上は前年比27%増と大きく成長した。

製品別では新製品カテゴリ(Virtex® UltraScale™, Kintex® UltraScale, Virtex-7, Kintex7, Artix®-7, Zynq®-7000, Spartan®6)の売上が前年比10%増と伸びた。XilinxによるとZynqのADAS向けの売上が好調だという。

Xilinxは、次期2016年Q2(15年7-9月)の売上は更に減少すると予測をしている。

2015.07.24

2015年7月22日、ARMは、2015会計年度第2四半期(2015年4-6月)の売上を報告した。

ARMの2015年Q2の売上は、前年比約15%増、前期比約2.5%増の3億5710万ドル、税引き前の純利益は約1億9360万ドルで英ポンド・ベースでは前年比約32%増だった。

ARMのQ2売上の内訳を見ると、プロセッサ・ロイヤリティの売上がドルベースで前年比約31%増と大きく伸びた。それに対しプロセッサ・ライセンスの売上は前年比3%増だった。

プロセッサ・ライセンスの契約数は過去最高となる54件で、うち12件は新規のライセンス契約者だった。この中には最新のARMv8-Aアーキテクチャ・ベースのプロセッサのライセンス契約が7件、GPU Maliのライセンス契約が9件含まれている。ライセンス内訳は下記の表の通り。

※画像はARM発表資料より抜粋

2015年Q2で出荷されたARM搭載チップの総数は約34億個で前年よりも約26%増えた。

ARMの2015年度の上半期の売上合計額は7億520万ドルで、前年比15%増の伸びを示している。

2015.07.08

2015年6月29日、SynopsysはセキュリティIPコアおよびソフトウェアを手掛けるElliptic Technologies社の買収を発表した。

Synopsysは買収条件などの詳細は発表していないが、既にElliptic Technologies社の買収を完了。同社の手掛けるセキュリティIPコアおよびソフトウェアを自社のIPポートフォリオに追加し、セキュリティ分野の専門家であるR&DチームがSynopsysに加わるとしている。

Elliptic Technologies社のソリューションは、コネクテッド・デバイスにおけるデータ盗難、改ざん、サイドチャネル攻撃、マルウェア攻撃などに対処するもので、製品としては暗号化コア、セキュリティ・プロトコル・アクセラレータおよびプロセッサなどの他にセキュリティ向けのミドルウェアなどソフトウェア・スタックも提供している。これら製品は既にデジタル著作権管理向けに利用されているようだ。

2015.07.08

2015年7月3日、米Gary Smith EDA社の創業者であるアナリストGary Smith氏が肺炎によりアリゾナ州フラッグスタッフの自宅で他界した。享年74歳だった。

Gary Smith氏はカリフォルニア州生まれで、メリーランド州にある米国海軍士官学校で工学の理学士号を取得。ベトナム戦争を経験した後にエレクトロニクス業界に入り、LSI Logic社ではRTL設計手法のエヴァンジェリストとして活躍した。

その後1994年に調査会社Dataquest社に入社しEDA業界のアナリストとして手腕を振るい、2006年に自らEDA業界・技術に特化した調査会社Gary Smith EDA社を興した。

Gary Smith氏はEDA業界のご意見番としてあまりにも有名で業界No1アナリストとして知られる人物。DAC(Design Automation Conference)で毎年行う講演は、業界の一つの指標としてEDAベンチャーの業績にも影響を与えていた。ここ数年はシステムレベルの設計手法の重要性を説き続け、米国におけるESL手法普及の一端を担っていた。

Gary Smith氏の追悼セレモニーは7月12日にサンノゼのダブルツリーホテルで開催される予定。

※Gary Smith氏 2014年サンフランシスコDAC会場で撮影

Gary Smith氏の訃報に接し、謹んで哀悼の意を表します。

2015.07.08

2015年7月7日、米EDA Consortiumは、2015年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

EDACの発表によると2015年Q1(1-3月)の世界のEDA売上総額は、前年比7.5%増、前Q4比10.8%減の18億7700万ドルで、Q1の売上として過去最高を記録した。四半期の売上記録が前年同時期を上回るのはこれで20四半期連続となる。

2015年Q1の売上を製品分野別に見ると最大のCAE分野以外は全て前年比増を達成。中でもIP分野は前年比19.3%増と大きな伸びを示した。IP分野の売上はCAE分野に迫る勢いとなっている。

2015年Q1の売上を地域別に見ると、最大市場の北米が前年比12.2%増と大きく成長、アジア市場も前年比12%とこれに続いた。日本市場はドルベースでは前年比0.2%減となっているが、円ベースでみると前年比約13.5%増という結果となっている。

2015年Q1時点でのEDA業界の従業員数は前年比5.5%増の32127人で過去最高を記録した。

2015Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億3370万ドル 0.8%Down

■IC Physical Design & Verification分野 3億3930万ドル 8.3%Up

■IP分野 6億1810万ドル 19.3%Up

■サービス分野 1億440万ドル 6.8%Up

■PCB/MCM分野 1億6150万ドル 1.1%Up

2015年Q1地域別の売上と昨年同時期との比較は以下の通り。

■北米 8億5320万ドル 12.2%Up

■ヨーロッパ 2億7830万ドル 6.2%Down

■日本 2億930万ドル 0.2%Down

■アジアその他地域 5億3620万ドル 12.0%Up

※EDAC(EDA Consortium)

2015.07.08

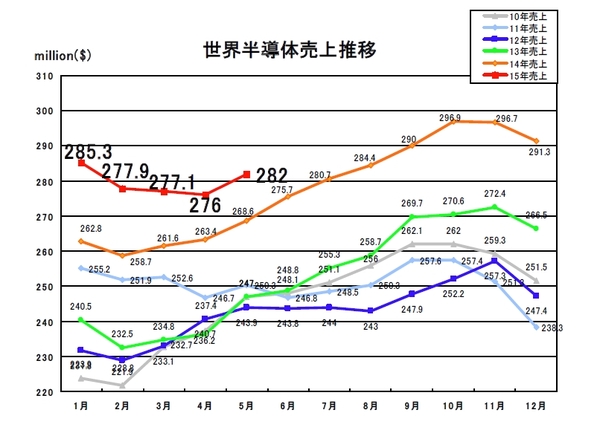

2015年7月6日、米SIA(Semiconductor Industry Association)は、2015年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年5月の世界半導体売上は前年同月比5.1%増、前月比2.1%増の282億ドルで5月の売上としては過去最高を記録。売上が前年実績を上回るのはこれで25ヶ月連続となる。

2015年5月の世界半導体売上を地域別に見ると、北米が前年比11.4%と好調、中国も前年比9.5%増、前月比4%増と強さを見せた。日本市場はドルベースで前年比11.8%減となっているが円ベースで換算すると前年比約4.5%の成長となる。

なお、WSTS世界半導体市場統計は2015年の世界半導体市場は前年比3.4%の成長と予測しているが、今のところ1月から5月は平均6%以上の成長を維持している。

※SIA

2015.06.12

2015年6月15日、Cadenceは第52回DACの開催に合わせて新製品のフォーマル検証ツール「JasperGold」の発表を行った。

「JasperGold」という名前は、Cadenceが昨年4月に買収したJasper Design Automationの旗艦製品として市場では有名だが、今回Cadenceはその名前を引き継ぎ新たな製品としてリリースした。

新しい「JasperGold」は、旧製品とCadenceの提供していた「Incisive Formal Verifier」を統合したフォーマル検証ツールで、基本的には旧「JasperGold」をベースとしながらも両製品の良さを残しつつ中身は大きな変化を遂げている。

ライセンスの供給形式は、フォーマル検証ユーザーに対してやりたい事に合わせてアプリケーション毎に「App」としてソリューションを提供してきた旧「JasperGold」のスタイルがそのまま継承されており、新「JasperGold」においては以下の通り計12の「App」が用意されている。この「App」は今後もラインナップを増やす計画のようだ。

・Formal Property Verification APP

・X-Propagation Verification APP

・Connectivity Verification APP

・CSR Verification APP

・Low Power Verification APP

・ARCH APP

・Structural Property Synthesis APP

・Behavioral Property Synthesis APP

・Security Path Verification APP

・Sequential Equivalency Checking APP

・Coverage APP Option

・Deadlock Detection APP

ツールのインタフェースについては、旧「JasperGold」のユーザーにとっては今まで同様、「Incisive Formal Verifier」のユーザーにとっても内部のパーサーがリンクする構造となっており基本的に大きなインパクト無くツールを利用できる。

内部のフォーマル・エンジンに関しては、「JasperGold」と「Incisive Formal Verifier」の両ツールの持っていた複数のエンジンに加え新たなコンストレイント・ソルバーが用意され、これらエンジンを協調的に働かせるような仕組みになっており、ユーザーの目的に応じて都合の良いエンジンをツールが自動的に選んでくれる。つまりユーザーは使用するエンジンを意識すること無く、目的に応じた最適なアウトプットを手に入れる事ができる。これによりツールの処理性能は最大15倍程度引き上げる事が可能ということだ。

また、「JasperGold」はCadenceの設計/検証プラットフォーム「System Development Suite」の一部に位置付けられており、デバッグ環境「Indago」や検証マネジメント環境「vManager」と高度な連携が可能な一つの検証エンジンとなっている。そのため「vManager」を用いてフォーマル検証結果を可視化する事や、デバッグ環境「Indago」のバックグラウンドで「JasperGold」を走らせたりという事が可能。既にこういったツール連携はサポートされている。

ちなみに、今年の4月にリリースされたばかりのデバッグ環境「Indago Debug Platform」では、新たに「Adovanced Debug Analyzer App」という機能が用意されたが、その中身は「JasperGold」のフォーマル技術が利用されており、What-if解析やアサーションにフォーカスしたコード解析などシミュレーション結果のデバッグをより効率化できるようになっている。

その他、新たな「JasperGold」では、Lintツールとしても使えるRTLの構造チェック機能や、ローパワー検証向けの機能(CPFサポート済)など様々な機能追加/機能向上が図られているほか、「JasperGold」ユーザー向けにフォーマル検証で利用できる合成可能なアサーション・ベースのVIPも用意されている。

※日本ケイデンス・デザイン・システムズ社

2015.06.11

FPGAベースのプロトタイピング・ボードを手掛けるAldecとPro Designの両社は、52DACの開催に合わせて新製品の発表を行った。

両社が発表した新製品はいずれもXilinx製の20nm FPGA「Virtex UltraScale VU440」を搭載するもので、Aldecの「HES-7」は一つのボード上に「Virtex UltraScale VU440」を6個搭載しており、この搭載数は今のところ業界最大。ボードに実装可能なデザイン容量やボードの最大接続数などの詳細は不明だが、Aldecはボードを接続すればデザイン容量はゆうに10億ゲートの域に達するとしている。

一方、Pro Designは今年2月末に業界に先駆けて「Virtex UltraScale VU440」を4個搭載した「proFPGA quad VUS 440 System」の市場投入をアナウンスしていたが、今回は「Virtex UltraScale VU440」を1個搭載する「proFPGA UNO」、2個搭載する「proFPGA DUO」のリリースを発表している。

※画像はPro Designの「proFPGA quad VUS 440 System」

なお、FPGAベースのプロトタイピング・ボード市場ではSynopsysが提供する「HAPS」が大きなシェアを握っているが、遅かれ早かれSynopsysも「Virtex UltraScale VU440」搭載の「HAPS」を市場投入してくるに違いない。搭載するFPGAが同じとなると、次なる差別化ポイントは価格、立ち上げ易さ、運用性、オプション数などになり、各社ともに独自性の強化に力を注いでいるように見えるが、独自性という意味ではAltera推しのベンダが出てくると市場は更に面白くなるだろう。

2015.06.09

2015年6月7日、カリフォルニア州サンフランシスコにて第52回Design Automation Conferenceが開幕した。

今年のDACは昨年に続いてサンフランシスコでの開催。

開催期間は6月7日から11日、学会と平行して6月8日から10日の3日間、展示会場でEDA関連各社の展示が行われる。

今年の52回DACで発表される研究論文数は計162本、昨年の174本より若干減った。ベスト・ペーパー候補となっているのは下記6本の論文。今年は昨年に続いて組み込みシステム関連の論文が多く、「Embedded System Architecture and Design」、「Embedded Software」に分類される論文は計48本、全体の約30%となる。

【ベスト・ペーパー候補の論文タイトル】

研究論文以外では計74のセッションが用意され、約150件の発表が予定されている。その内訳は以下の通りで今年も様々なテーマの企画がある。

・ 4 amazing Keynote Sessions and 1 Visionary Moore's Law Talk

・ 8 interesting SKY (short keynote) Talks

・ 9 Tutorials, 9 Workshops, and 6 Colocated Conferences

・ 2 Management Day Sessions

・ 24 Special Sessions and Panels

・ 21 Designer and IP Track Sessions, and a special poster networking session

・ 6 training sessions on Thursday by Doulos

今年のキーノートは、Google、DELPHIからの登壇者が予定されており、それぞれスマート・レンズと車載システムの開発について講演する。またキーノート・パネルでは、コネクテッド・カーのセキュリティや安全性などについて議論される予定で、昨年に続き今年のDACにおいても「オートモーティブ」は一つのキーワードとなっている。

http://www.dac.com//content/conference-highlights

もう一つ今年のDACの大きなキーワードとなっているのは「IoT」で、各セッションを通じて様々なIoT関連の発表が予定されている。

http://www.dac.com/content/conference-highlights#iot-program

展示会の方は昨年より微減の170社が出展予定。(重複除く。EDA-EX調べ)うち初出展の企業は23社で昨年よりも倍増した。日本からの出展は、毎年出展しているTOOL、ジーダット、ベリフィケーション・テクノロジーの3社に加えてハギワラソリューションズが初出展している。

DACの来場者数は昨年前年比13%増の6700人と少し回復した。今年も昨年同様サンフランシスコ開催であり、世界的には半導体業界に追い風が吹いているため来場者が減ることは無さそうに見える。

尚、毎年恒例となっているGary Smith EDA社の「DAC要チェックリスト2015年版」は以下の通り。また、EDA業界の情報屋であるJohn Cooley氏のWebサイトでも、「My Cheesy Must See List for DAC 2015」と称した要チェックリストが公開されている。http://www.deepchip.com/gadfly/gad060515.html

※画像はGary Smith EDA社の公開データ 同リストはGary Smith EDA社のWebサイトから無償でダウンロード可能

2015.06.09

2015年6月7日、Synopsysは、RTL解析ツール「SpyGlass」をはじめとしたEDAソリューションを手掛ける米Atrenta社を買収することを発表した。

今回の買収について、その取引条件等の詳細は明らかにされていないが、一部のEDA関連情報サイトでは買収額は$150M程度と推測する記事が掲載されていた。

AtrentaはRTL解析ツール「SpyGlass」で成功した米国のEDAベンダで設立は2001年。日本法人の設立は2005年8月で以前は図研が国内代理店としてAtrentaのツールを販売している時期もあった。

Atrentaは「SpyGlass」シリーズ製品としてCDC検証、SDC解析、パワー解析、DFTなど様々な製品を展開するほか、チップ・アッセンブリのためのソリューションとして「GenSys」シリーズも提供。2012年にはアサーション合成ツール「BugScope」を手掛けるNextOp社を買収しソリューションを拡張していた。

経営面では、2006年に資金調達第4ラウンドで1600万ドルを調達したのを最後にこの9年間はオフィシャルな増資の発表は無かった。

2009年以降、大手EDA3社による同業買収が加速し、Atrentaは残り少ない中堅EDAベンダの一角を担っていたが遂に買収が決定。EDA業界はデパート的な大手3社と多数の小規模専門店が混在する市場になった。

2015.06.05

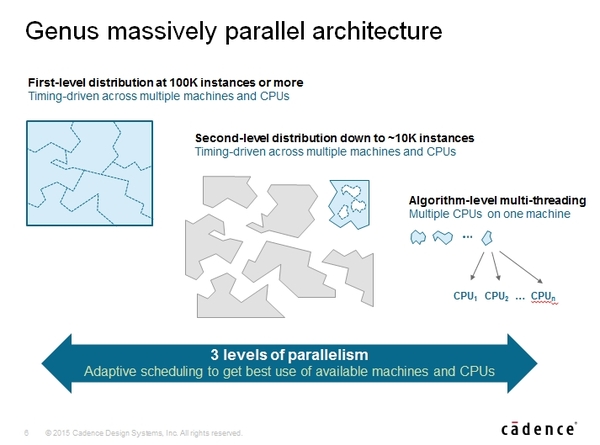

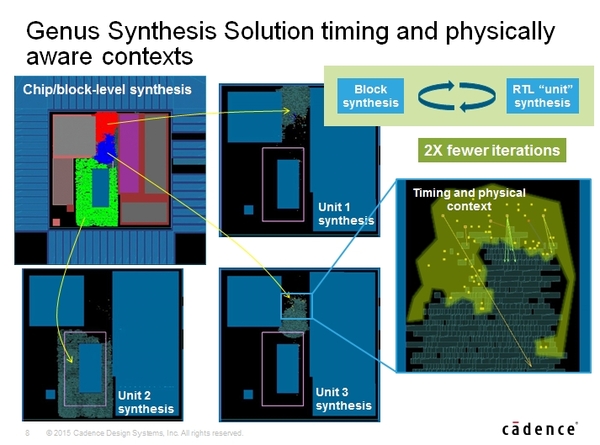

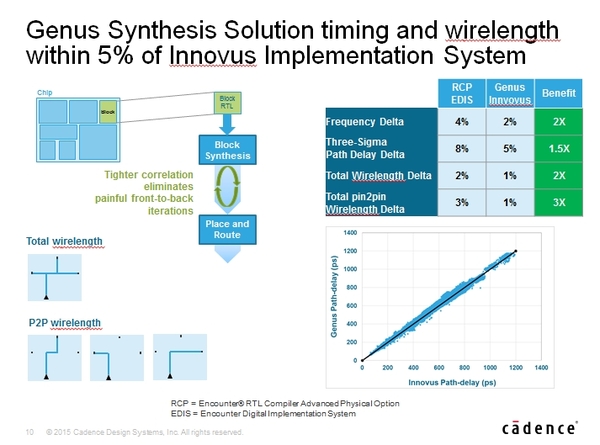

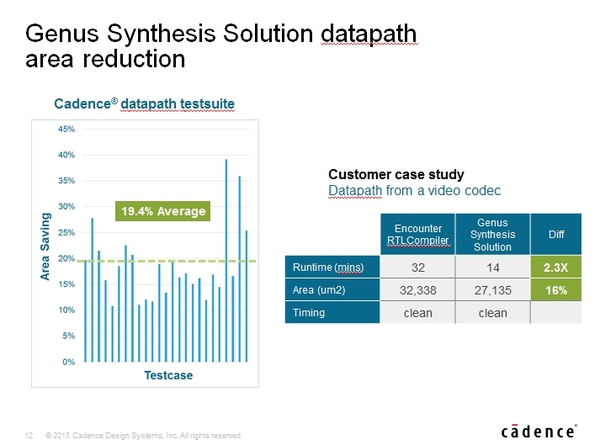

2015年6月3日、Cadenceは新製品の論理合成ツール「Genus」のリリースを発表した。

「Genus」は、Cadenceの既存製品「RTL Compiler」の後継となる論理合成ツールで、28nm以降の先端大規模チップの設計を主たるターゲットとしている。Cacdenceは「Genus」を利用する事で「RTL Compiler」と比較して設計生産性を最大10倍に向上できるとする。

「RTL Compiler」に対して「Genus」がどう進化したかと言うと、まず合成の処理時間が最大5倍高速になった。これは新しい大規模分散型並列処理アーキテクチャーの採用によるもので、分散効率が高められただけでなく、デザインをより細かく広範囲に分散処理する事が可能となった。聞くところによると論理回路レベルで分散処理を行うことも可能なようだ。

また処理速度に加えて、「Genus」では階層設計における上位レベル(チップレベル)の合成と下位レベル(ユニットレベル)の合成との間のイタレーションを半分以下にできるようになった。言い換えればイタレーションの生産性は2倍向上という事で、5倍の速度向上と合わせて最大10倍の生産性向上という計算だ。

イタレーション削減の秘訣はフィジカル情報を考慮したコンテキスト生成機能で、上位レベルの合成を行う際にコマンド一つで下位レベルの配線およびタイミングに関する情報を読み取る事が可能となった。この機能によって上位レベルにおける合わせ込みが非常に楽になるという。

更に「Genus」は下流の新型配置配線ツール「Innovus」との高い相関性が確保されており、合成と配置配線のイタレーション工数も大きく削減出来るようになった。元々「RTL Compiler」は配置配線ツール「Encounter」との相関性の高さがウリの一つであったが、「Genus」と「Innovus」はそれを上回るタイミングおよび配線長の高い相関性を実現しており、その誤差は5%以内に収まるという事だ。理由は寄生抽出、遅延計算、配線経路の見積エンジンを「Genus」と「Innovus」は全て共有しているため。この精度の高さはインプリメント工数の多くを占めるイタレーション工数の削減に大きく効くと同時に配置の改善にも役立つものだ。

もう一つ、今回の新製品「Genus」の特筆すべき能力はPPA最適化機能だ。新たなアルゴリズムをベースとした最適化エンジンでは、各々データパスの局所的な最適化だけではなくデザイン全体を見たベストなトレードオフ(最適化)を行うことが可能で、ワードレベルの演算子まで踏み込んだ形でRTLを最適化できる。その結果、データパス・エリアを平均20%も削減する事が可能という事で、このエリア削減効果はパワー削減の面でも大きい。

なお、「Genus」のGUIは配置配線ツール「Innovus」、タイミング解析ツール「Tempus」と共通化されており、これら3ツールはコマンド体系やレポート・スタイル等も統一されている。どれか一つのツールを覚えれば自然と他のツールも扱い易く、ツールのよる処理結果の比較などもし易い。

「Genus」は既に出荷が開始されており、プレスリリースにはTexas Instruments社がユーザーとしてコメントを寄せているほか、別のプレスリリースにてImagination Technologies社の「Genus」を利用した成功事例が発表されている。両社共に「Genus」を使うことでTATを5分の1以下に短縮できたとしている。

2015.06.04

2015年6月2日、米SIA(Semiconductor Industry Association)は、2015年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年4月の世界半導体売上は前年同月比4.8%増、前月比0.4%減の276億ドルで4月の売上としては過去最高を記録。売上が前年実績を上回るのはこれで丸二年、24ヶ月連続となる。

2015年4月の世界半導体売上を地域別に見ると、3月と比較して各地域が売上を落とす中、中国を除くアジアその他地域のみ2.3%増を記録。前年比では北米および中国が強さを見せた。日本市場はドルベースで前年比10.7%減となっているが円ベースで換算すると前年比約4.3%の成長となる。

尚、時同じくしてWSTSが発表した2015年春季世界半導体市場予測によると、2015年の世界半導体市場は前年比3.4%増の成長、その後も安定成長を続け、2016年3.4%増、2017年3.0%増と向こう3年間は緩やかな成長が継続すると予測されている。

WSTSは今年3月時点で2015年の世界半導体市場の成長率を4.9%と予測していたが、今回予測を下方修正した形となる。ちなみに各市場調査会社の予測は概ね5%の成長となっており、現時点での2015年売上累計額は前年比5%以上増加している。

日本市場に関しては、2015年2%増、2016年2%増、2017年1.5%増と世界水準は下回るものの、平均1.8%増の成長が見込まれている。

※SIA

2015.06.01

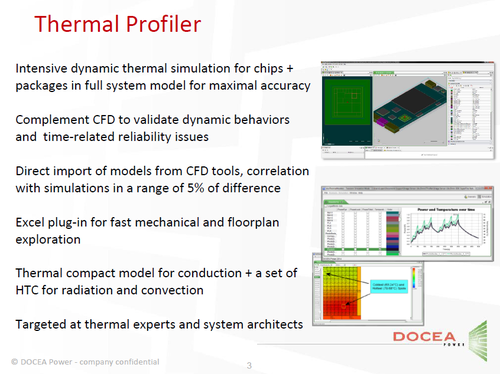

昨今、モバイルデバイスに限らず、あらゆる機器開発で無視できない「熱」の問題。チップ上の熱は消費電力にも影響を及ぼすため、設計の早期段階にシステム・レベルで熱/消費電力を見積る事が理想的だが、これまでCFDツールに代わる熱シミュレーションのためのソリューションは無かった。

しかし、仏Docea Power社のEDAツール「Thermal Profiler」は、コンパクトな熱モデルを用いてダイナミックかつ高速/高精度に設計早期段階での熱シミュレーションが可能と聞き、その詳細についてDocea社のマーケティング・ディレクター Ridha HAMZA氏に話を聞いた。

Ridha HAMZA氏によると、「Thermal Profiler」は動的なシミュレーションによってシステム・レベルで熱のプロファイリングを行うツールで、一般的なCFDツール(熱流体解析ツール)よりも1,000倍高速な熱シミュレーションが可能。従来数日要していた熱シミュレーションを数分で完了する事ができ、その精度誤差は5%程度に収めることができる。

「Thermal Profiler」の熱シミュレーションが高速なのは、Docea独自のシステム・レベルのコンパクトな熱モデルを使用しているからで、その熱モデルはCFDツールからモデルを直接インポートする事で自動生成する事が可能。余計なモデリング工数を必要としない。

また、「Thermal Profiler」が優れているのは熱シミュレーションの速度だけではない。CFDツールは一般的にワースト・ケースを想定した固定値で静的に熱を解析するのに対し、「Thermal Profiler」はシナリオに基づいた動的なシミュレーションが可能で、同社のシステムレベル・パワー・モデリング及びシミュレーション・ツール「Aceplorer」と併用することにより熱と合わせてリーク電流を解析する事も可能。解析結果を元に熱要因のデバッグを行う機能も併せ持っている。

Ridha HAMZA氏によると、「Thermal Profiler」のユースケースとして多いのが、解析対象となるチップの動作シナリオに基づいてチップ内の各所の熱を解析し、その結果を元に熱の影響を考慮しながらチップのフロアプランを検討するという手法。この手法を設計の初期段階で用いることで、熱に対する過剰なマージンを抑えるだけでなくローパワー化も実現できるため、「Thermal Profiler」は大手のモバイル・チップや4K画処理チップの開発チームなどで重宝されているとの事。

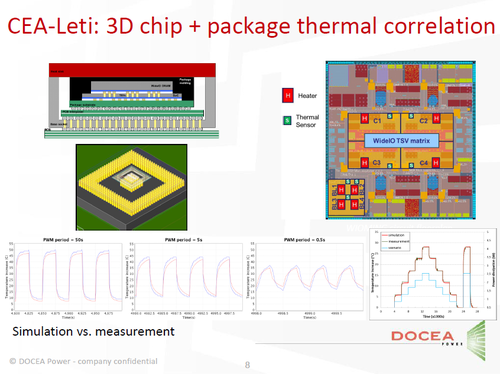

尚、「Thermal Profiler」は、チップ単体のみならず、パッケージ・レベル、ボード・レベルでの熱シミュレーションも可能で、Docea社の母国フランスの研究機関CEA-Letiでは、「Thermal Profiler」を用いて積層チップのパッケージをシミュレーションした結果、実測値にかなり近いシミュレーション結果を得る事ができたという。

ちなみに「Thermal Profiler」の想定ユーザーについてRidha HAMZA氏に聞いたところ、主なターゲット・ユーザーはシステム・アーキテクトという回答だったが、CFDツールを使う熱解析チームとシステム・アーキテクトがコラボレーションする事で「Thermal Profiler」の機能を最大限に活用できるという話で、「Thermal Profiler」は必ずしもCFDツールを置き換えるものではなく、CFDツールと補完し合うソリューションとの事だった。

※Docea Power社製品に関するお問い合わせ先:kawahara@nextream.bz

2015.06.01

2015年5月26日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、新製品「Prodigy Cloud Cube」のリリースを発表した。

発表によると「Prodigy Cloud Cube(以下、Cloud Cube)」は、複数ロケーションの複数ユーザーによる利用を想定した、言わばプロトタイピング環境の統合管理プラットフォームで、最大32個のFPGAを搭載可能な筐体にはパワー、冷却、リモート制御機能が備えられている。

「Cloud Cube」のユーザーはネットワーク経由で遠隔地から「Cloud Cube」にアクセスする事が可能で、目の前にFPGAボードがある感覚でローカルでの作業を「Cloud Cube」に転送し「Cloud Cube」上のFPGAリソースでプロトタイピングを実行できる。このアプローチはFPGAベースのプロトタイピング・システムとしては業界初で、S2CのCEOである中間俊雄氏は、「大幅なコスト削減と市場投入期間の短縮を実現する」と主張。「Cloud Cube」にはS2C社の提供する各種FPGAボードを搭載でき、デザイン容量は最大で14億ゲート、最大16ユーザーで利用する事ができるという。

なお、「Cloud Cube」には制御、モニタリング用のランタイム・ソフトウェア、ハードウェアの問題点を検出するセルフテスト機能などが付属しているが、運用に当たっては自動パーティショニング・ツール「Prodigy Player Pro」、システムレベル・シミュレーションとの協調検証用インタフェース「Prodigy ProtoBridge」、80種以上のドーターカードおよびライブラリ群「Prodigy Complete Prototyping Platform」といった既存のソリューションを利用する事が可能。今月20日に発表したVirtex UltraScale 440を搭載した新製品「シングルVU440 Prodigy Logic Module」も「Cloud Cube」に搭載できる。

※S2Cジャパン株式会社

2015.05.27

2015年5月8日、Matlab/Simulinkを手掛けるMathWorksは、ハードウェア設計向けの新製品「Vision HDL Toolbox」を発表した。

MathWorksの発表によると「Vision HDL Toolbox」は、Matlab/Simulinkの最新バージョン「Release 2015a」にて使用可能なビジョン・システム設計向けのパッケージで、FPGA/ASICをターゲットとするハードウェア設計向けにピクセル・ストリーミング・アルゴリズムや設計フレームワークを提供する。

「Vision HDL Toolbox」を利用すれば、FPGA/ASIC設計用に用意された各種画像処理およびコンピューター・ビジョンのアルゴリズム・ライブラリを元にサイズ変換、ピクセル←→フレーム変換などの機能を用いて所望のアルゴリズムを実現し、それをスムーズにハード化(HDL化)する事が可能。ハード化は同社のHDL自動生成ツール「HDL Coder」を用いて行うためHDLコードの記述に伴う工数を削減できる。

「Vision HDL Toolbox」の主な機能は以下の通り。(MathWorks Webサイトより)

・イメージ強調、フィルター処理、モルフォロジー、統計などの、ピクセル ストリーミング アーキテクチャを使用した画像処理、ビデオ、コンピューター ビジョンのアルゴリズム

・MATLAB /Simulink のフレームベース処理機能と統合するためのフレームからピクセルへの変換、およびピクセルからフレームへの変換

・理想的でないタイミングと様々な解像度に対応するためのビデオ同期信号

・高精細ビデオ(1080p / 60FPS) を含む、フレーム レートとフレーム サイズを設定可能・HDL コード生成とリアルタイム検証のサポート

2015.05.27

2015年4月23日、アナログ/カスタムIC向けのレイアウト自動化ソリューションを手掛ける英Pulsic社は、リコーが同社の自動配置配線ツール「Animate」を採用した事を発表した。

「Animate」は、Pulsicが2014年5月にリリースしたトランジスタ・レベルの自動配置配線ツールで、回路図を解析し制約を自動抽出し、「PolyMorphic Layout Technology」という特許出願技術をベースに配置と配線を同時に処理し複数のレイアウト結果を生成する。

リコーはレイアウト工数の削減に取り組む中で、電源ICレイアウトの工数の50-80%を占める「セルの作成」を効率化すべく「Animate」を採用。これにより実データを用いたセル作成レイアウト設計評価において40%の工数削減を実現したという。

2015.05.27

2015年5月7日および5月11日、Mentor Graphicsは、同社製RTOS「Nucleus」の新製品2品種を連続して発表した。

今回Mentorがウェアラブル端末向けに用意したのは、ヘテロジニアスなマルチコア・プラットフォーム上での稼働を想定した「Nucleus RTOS」で使用状況に応じてアプリケーションの演算性能を最大化したり、バッテリ寿命を最大化する機構を備えている。

もう一つIoT向けに用意したのは、プロセスモデルを拡張したARM Cortex-Mファミリ向けの「Nucleus RTOS」でIoTデバイスのアプリケーションを稼働中であっても動的にロード/アンロードできる機構を備えている。この最新の「Nucleus RTOS」は、搭載するデバイスとして新たにTIのモバイル・チップ「WiLink 8.0シリーズ」をサポートしている。

2015.05.25

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2015.05.25

2015年5月22日、Mentor Graphicsは、2016会計年度第1四半期(15年2月-4月)の売上を報告した。

発表によると、Mentorの2016会計年度Q1の売上は、前年比約7.9%増の2億7210万ドル、営業損益を766万ドル計上した。この実績は前Q4実績報告時の予測を上回るものだった。(※GAAP基準による会計結果)

MentorはこのQ1(2-4月)にアナログ/ミックスドシグナルIC設計ツールを手掛けるTanner EDAの事業資産を買収。(※

関連ニュース)

新製品としては車載システム開発、組み込みシステム開発、PCB設計と各分野向けの新製品を複数発表している。

Mentorは次期2016会計年度Q2(15年5-7月)の売上を2億5000万ドル程度と予測している。

2015.05.21

2015年5月21日、Synopsysは、2015会計年度第2四半期(15年2月-4月)の四半期決算を報告した。

発表によると、Synopsysの2015会計年度Q2の売上は、前年同時期比約7.6%増、前期Q4比約2.8%増の5億5720万ドルでまた四半期売上記録を更新した。売上記録の更新はこれで5四半期連続。Q2の純利益は5560万ドルで前年実績を下回った。(※GAAP基準による会計結果)

Synopsysはこの2月-4月の間に、25G/50G Ethernet 検証用IP、エンベデッド・ビジョン・プロセッサIP、TSMC 16nm FinFET Plusプロセス向け設計IPなどIP新製品を投入。ツールとしてはカスタム・プロセッサ開発向けの新製品「ASIP Designer」をリリースした。

またバーチャル・プロトタイピング・ツール「Virtualizer」をバージョンアップしたほか、同ツールで利用するキット「VDK」のラインナップを車載システム開発向けに拡充した。

更にこの4月にはソフトウェア・セキュリティを手掛けるフィンランドのCodenomicon社を買収し、新たなソフトウェア向けソリューションを手中に収めている。

Synopsysは次の2015会計年度Q3(15年5月-7月)の売上を5億5000-6000万ドルと予測している。

2015.05.20

2015年5月12日、Alteraは同社のFPGA専用設計ツール「Quartus II」の新エンジンを発表した。

発表によるとAlteraは、「Quartus II」用に「Spectra-Q(スペクトラ・キュー)」と呼ぶ新たなエンジンを開発。このエンジンを用いることでデザインのコンパイル時間を大幅に短縮させたほか、デザインの部分的な変更に対応するインクリメンタルなコンパイル機能をサポート。更にはCまたはC++からの高位合成機能もサポートした。

また、同エンジンをベースにアーキテクチャ探索やインタフェースの割り当てに利用するツールとして「BluePrint」呼ぶ新ツールも開発し、開発環境を大きく充実させた。

これらAlteraの新たな設計環境に関しては、別途取材の上、詳細をレポートします。

※日本アルテラ株式会社

2015.05.20

2015年5月12日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、新製品「シングルVU440 Prodigy Logic Module」のリリースを発表した。

「シングルVU440 Prodigy Logic Module」は、ロジック・セル数440万個のXilinxの20nm FPGA「Virtex UltraScale XCVU440」を搭載するスタンドアロンのプロトタイピング・ボードで、「Virtex-7 2000T」を搭載する既存の「V7 Prodigy Logic Module」の倍にあたる最大4400万ゲートのデザインを実装することができる。

また、詳細は不明だが、「シングルVU440 Prodigy Logic Module」は「Cloud Cubeシステム」と呼ばれる大規模ユニットに最大16台格納可能で、クラウド経由でプロトタイピング・システムをリモート管理できるようだ。この「Cloud Cubeシステム」は、これまで業界に無かったタイプのプロトタイピング・システムで、複数ユーザーで「Cloud Cubeシステム」内のプロトタイピング・ボードを遠隔利用する事が可能。新製品の「シングルVU440 Prodigy Logic Module」に限らずXilinxのVirtex-7、Kintex-7、AlteraのStratix-4を搭載する他の「Prodigy Logic Module」も格納して利用できるという。

※S2Cはこれまで「TAI Logic Module」と呼んでいたボード製品をいつからか「Prodigy Logic Module」と呼び名を変えている。

Virtex UltraScale搭載のプロトタイピング・ボードとしては、既にドイツのProDesign社が製品を市場投入しているが、この6月にサンフランシスコで開催されるDAC(Design Automation Conference)では、S2C以外にもVirtex UltraScale搭載のプロトタイピング・ボードの発表があるかもしれない。

※画像はS2C社Webサイト上のデータ

※S2Cジャパン株式会社

2015.05.15

2015年4月30日、Cadenceは、デバッグ・ツールの新製品「Indago Debug Platform」を発表した。

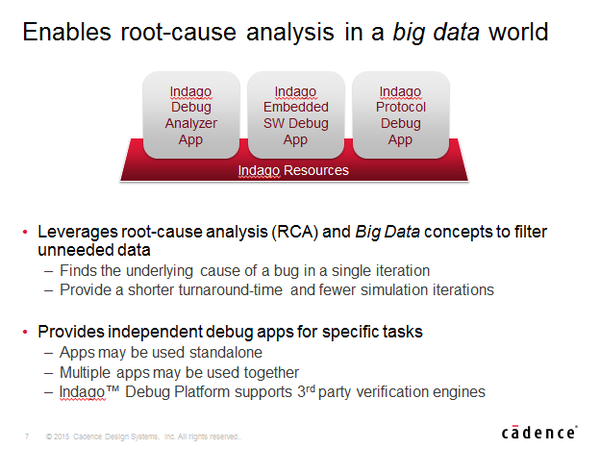

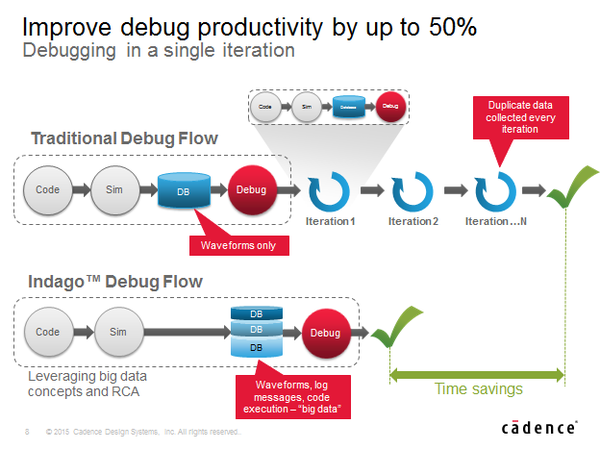

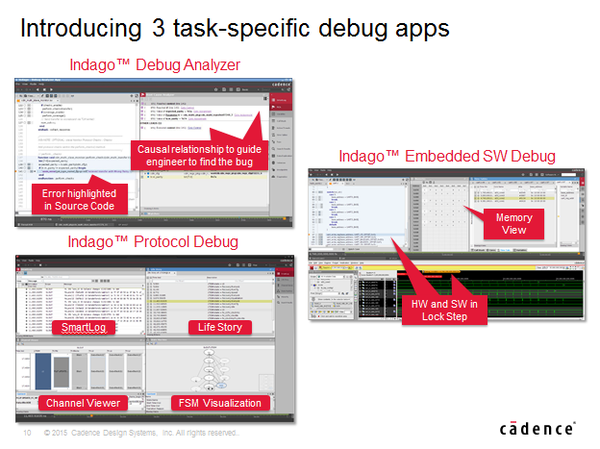

「Indago Debug Platform」は、Cadenceのフロントエンド設計ツール群「System Development Suite」の一部として提供されるデバッグ用のツール環境で、下記3種類の個別のツールによって構成されている。

・Indago Debug Analyzer

・Indago Embedded SW Debug

・Indago Protocol Debug

「Indago Debug Analyzer」は、デザイン本体のみならずテストベンチも含めた形でのデバッグを実現するもので、SystemC Verilog、e、SystemCなど各種言語で記述されたテストベンチをデバッグできるほか、UVMライブラリの変数を解析する仕組みなどUVMデバッグ用の仕組みも用意されている。テストベンチもデバッグ対象としてデザインとテストベンチを同期させてインタラクティブにデバッグ出来るというのがこのツールの特長と言える。

「Indago Embedded SW Debug」は、SWも含めたデバッグSoCレベルのデバッグを実現するもので、SoC上で動くHWとSWをリンクさせて同期させながらステップ・バイ・ステップでデバッグする事ができる。同ツールでSW本体のデバッグも可能だが、HWのデバッグにおいてSWも考慮するというのが想定されている利用法である。

「Indago Protocol Debug」は、AMBAなどオンチップ・バスに主眼を置いたプラットフォーム・ベース検証のためのデバッグ・ツールで、デザイン内の各機能ブロック間やデザインとテストベンチ間、検証IP間などでオンチップバスを介して行われるデータのやり取りを可視化する事ができる。

これら3つのツールは、それぞれ個別に購入でき他社の検証ツールでも利用する事が可能となっているが、検証エンジン、検証IPへの対応において当然ながらCadence製品向けに最適化されている。

Cadenceはこれらツールをまとめた総称として「Indago Debug Platform」と呼んでいるが、「Indago Debug Platform」の狙いは言うまでもなくデバッグ工数の削減で、今日のSoC開発では限界となりつつある旧来手法の力任せのRTLデバッグの刷新を目指している。そのためにCadenceは「Indago Debug Platform」に「RCA:Root cause analysis」の技術を導入しバグの原因解析手法を提供しているが、その代表的なアプローチとして「ビッグデータの活用」というコンセプトがある。

Cadenceの言うビッグデータとは、デバッグに役立てる各種データの総称で波形データに限らずシミュレーターやフォーマル検証ツールなど各種検証ツールやSWデバッガの吐き出すログなどの情報を集めビッグデータとして活用するために整理、分類する仕組み「SmartLog」を用意している。またシミュレーションを再実行せずに時間を戻すリバース・デバッグ機能も用意しており、これら機能を活用することで無駄なイタレーションを減らしデバッグ効率を高める事が可能になるという。

※画像は全てCadence提供のデータ

Cadenceによると「Indago Debug Platform」を用いる事でデバッグ工数を最大50%削減できるという事だが、IPや機能ブロックなどデザイン内のデバッグだけではなく、UVMなど先進的なテストベンチのデバッグ、HWとSWを組み合わせた境界領域のデバッグなど、SoC開発で行われる各種デバッグを単一のツール・プラットフォームで一気通貫に実現できる点が「Indago Debug Platform」の最大の魅力と言えるだろう。

「Indago Debug Platform」は今年6月から正式リリースの予定で、現在先行ユーザーに限定的に提供されている。ツールの一部機能は既に日本国内のユーザーにも利用されているという話で、7月17日に予定されているCadenceのプライベート・イベント「CDNLive Japan」ではユーザーの事例を聞くことができるかもしれない。

※日本ケイデンス・デザイン・システムズ社

2015.05.15

2015年2月4日、Cadenceは、2015会計年度第1四半期(2015年1-3月)の売上を報告した。

Cadenceの2015年Q1売上は、前年同時期比約8.4%増、前期Q4比約2.8%減の4億1100万ドル。純利益は前年比約9%増の3600万ドルだった。(※GAAP基準による会計結果)

Cadenceは2009年Q1から四半期売上を伸ばし続けていたが、6年ぶりに四半期売上が前四半期売上を下回った。しかし、Cadenceは自社の業績が2015会計年度も順調に推移するとみており、年間売上は前年比増を達成すると予測。今後2年間で4.5億ドルの自社株買い戻しを計画している。

CadenceはこのQ1において新型の配置配線ツール「Innovus」や「Cynthesizer」と「CtoS」を統合した新型高位合成ツール「Stratus」を発表している。

Cadenceは、来期2015年Q2の売上額を4億1000-2000万ドルと予測している。

2015.05.12

2015年6月19日、今年で開催10周年となるSystemC」にフォーカスした技術セミナー「SystemC Japan 2015」が開催されます。

「SystemC Japan 2015」は、ハードウェア設計関連の標準化団体である米Accellera Systems Inisiative主催の下、国内外13社のスポンサー企業が協力して開催致します。

セミナーでは公募による2件の講演を含めた計12件のセッションとパネル・ディスカッションを実施する予定です。世界最大規模を誇るSystemCユーザー・セミナー「SystemC Japan 2015」に是非足をお運び下さい。

<講演タイトル一覧>

・Accellera Systems Initiative Update

・ソフトウェア技術者によるSystemC開発-ハードウェアも出来るソフトウェア技術者を目指して-

・仮想プロトタイピングへの挑戦

・モデリングによるターゲットシステムの最適仕様の探求

・Intel® CoFluent™ Studioで作成したマイクロアーキテクチャモデルによるシステム仕様検証とWindRiver Simic* 仮想プラットフォームやプリシリコン開発環境でモデルを再利用した事例の紹介

・車載ソフトウェアプラットホーム開発への仮想環境の適用

・低消費電力ビットコインマイニングIPの開発

・SystemCを用いた画像処理アルゴリズム開発手法

・ケイデンスの新システムレベル設計プラットフォームStratus High-Level Synthesis

・4K/60p HEVCリアルタイムビデオエンコーダLSIへの高位合成適用事例-インターフェイスライブラリによる設計効率化-

・徹底討論:SystemC IPは本当に必要なのか?(パネル・ディスカッション)

※セミナー内容の詳細はこちら

http://www.systemcjapan.com/SCJ2015/aboutseminar.html

■セミナー開催概要

会期:2015年6月19日(金)

9:30-17:40(セミナー)、18:00-19:30(パーティー)

会場:新横浜国際ホテル 南館 〒 222-0033 横浜市港北区新横浜 3-18-1

セミナー会場:2F チャーチル、レセプション会場:3F クリスティ

※会場へのアクセス→http://www.khgrp.co.jp/shinyoko/access/index.php

参加:無料(昼食付、事前登録制) 定員300名

※セミナーのお申し込みにあたり、「お申し込みにともなう個人情報の取り扱い」に同意いただく必要がございます

※当セミナーは設計現場のエンジニアの方の参加を優先しております。

お申込者の所属や職種によりセミナーへの参加をご遠慮頂く場合がございますので、予めご了承下さい。

主催: Accellera Systems Initiative

メインスポンサー:

日本ケイデンス・デザイン・システムズ社

インテルコーポレーション

Magillem社

OneSpin Solutions社

協賛:

アダプトIP株式会社

アルデック・ジャパン株式会社

ASTC株式会社

株式会社インターバディー

カリプト・デザイン・システムズ株式会社

東芝情報システム株式会社

株式会社エッチ・ディー・ラボ

日本電気株式会社

株式会社プライムゲート

※セミナー公式Webページはこちら

http://www.systemcjapan.com/SCJ2015/

※セミナー参加企業の紹介はこちら

http://www.systemcjapan.com/SCJ2015/aboutshuttensha.html

2015.05.11

2015年5月4日、米SIA(Semiconductor Industry Association)は、2015年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年3月の世界半導体売上は前年同月比6%増、前月比0.1%減の277億1000万ドルで3月の売上としては過去最高を記録。売上が前年実績を上回るのはこれで23ヶ月連続となる。

なお、四半期ごとの売上で見ると2015年Q1(1-3月)の売上合計は831億ドルで前年同時期よりも6%の増加。各団体や調査機関の予測通り、今年の世界半導体市場は順調に成長を続けている。

SIAはこれまで世界の半導体市場を北米、欧州、日本、アジアその他地域と4つの地域に分けて統計を発表していたが、今回から中国市場の売上をアジアその他地域から分離して独立計上する形に変更した。その結果、地域別売上の統計上ではアジアその他地域に次いで中国が世界第二位の市場規模となっている。

2015年3月の世界半導体売上を地域別に見ると、前年比では北米および中国が2ケタ成長を果たしているが、前月比では北米市場が6.9%減と落ち込んでいる。日本はドルベースで前年比9.6%減となっているが円ベースで換算すると前年比約6.4%の成長となる。

※SIA

2015.05.07

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2015.05.07

2015年4月23日、Alteraは2015会計年度第1四半期(15年1-3月)の売上を報告した。

発表によるとAlteraの2015年Q1売上は、前年比約6%減、前期Q4比約9%減の4億3550万ドル、営業利益は前年比約23%減の1億302万ドルだった。このQ1の売上実績は前四半期の売上報告時の予測値よりも悪く、2四半期連続で前四半期売上実績を下回った。

Alteraの2015年Q1の売上の内訳を見ると、製品カテゴリ別の売上比率と市場分野別の売上比率は前Q4とほぼ同じだが、地域別の売上比率は北米、アジアの売上比率が増え、欧州、日本の比率が下がった。

つい先日、AlteraがIntelに買収されるかもしれないという話が世間を賑わせたが、両社の買収交渉は物別れに終わり、現在Alteraの株主が買収再検討をAlteraに提案しているという話だ。ちなみにAlteraの株価はIntelの買収交渉の話が明らかになった事で25%近く上昇。現在も上昇後の株価を維持している。

Alteraは次期2015年Q2(4-6月)の売上を2015年Q1実績の-4%から-8%と予測している。

2015.04.24

2015年4月23日、Xilinxは2015会計年度第4四半期(2015年1-3月)決算を報告した。

Xilinxの2015会計年度Q4の売上は、前年同時期比約8%減、前期Q3比約4%減の5億6700万ドル。営業利益は前年比17%減の1億5900万ドルだった。四半期ごとの売上額で見ると4四半期連続で売上減となった。(※GAAP基準による会計結果)

2015会計年度(14年4月-15年3月)の売上合計は23億8000万ドルで前年とほぼ同等。純利益は前年比3%増の6億4800万ドルだった。なお、2015会計年度の粗利率は過去最高の70%を記録した。

Q4売上を市場別に見ると、通信およびデータセンター向けの売上比率が昨年同時期よりも10%下がった。製品別では新製品カテゴリ(Virtex® UltraScale™, Kintex® UltraScale, Virtex-7, Kintex7, Artix®-7, Zynq®-7000, Virtex6, Spartan®6)の売上比率が更に伸び49%となった。Xilinxによると28nm製品の年間売上額は5億8000万ドルに達した。

Xilinxは、次期2016年Q1(15年4-6月)の売上は更に減少すると予測をしている。

2015.04.22

2015年4月21日、ARMは、2015会計年度第1四半期(2015年1-3月)の売上を報告した。

ARMの2015年Q1の売上は、前年比約14%増、前期比約2.7%減の3億4820万ドル、税引き前の純利益は前年比約24%増の約1億8440万ドルだった。

ARMのQ1売上の内訳を見ると、フィジカルIPライセンスとプロセッサ・ロイヤリティの売上がともに前年比約31%増と大きく伸びた。プロセッサ・ライセンスの売上は前年比2%減だった。フィジカルIPのロイヤリティの売上には初めてFinFETプロセス向けの売上が計上された。

このQ1で獲得したプロセッサ・ライセンスの契約数は30件、この中には最新のARMv8-Aアーキテクチャ・ベースのプロセッサ、GPU Maliのライセンス契約がそれぞれ4件含まれている。ライセンス内訳は下記の表の通り。

※画像はARM発表資料より抜粋

2015年Q1で出荷されたARM搭載チップの総数は約38億個で前年よりも約31%増えた。

※画像はARM発表資料より抜粋

2015.04.15

インターコネクトIPを手掛けるArterisは、今年2月以降、幾つかのプレスリリースを連続して発表した。Arterisと言えば約1年半前にQualcommによる技術買収の一件で世間を賑わせたが(※関連ニュース)、当時公言していた通りその後も同社の主力製品である「FlexNoC」の販売、サポートは継続されており、つい先日最新製品「FlexNoC Version 3」が発表された。

「FlexNoC Version 3」は、ユーザーの設計生産性向上にフォーカスしてアッセンブリ機能が強化されたバージョンで、開発環境としてSoCのトポロジ・エディターやユーザー・インタフェース、NoCのインテグレーション機能がエンハンスされた。

最近発表された事例としては、AppliedMicroによるサーバー向けチップへの採用、Rockchipによる通信用プロセッサへの採用、TIによるローパワー・ワイヤレスMCUへの採用などがあり、いずれも同社の既存顧客によるもの。その他に企業名は公表されていないが、大手SSDベンダ2社がSSDで「FlexNoC」を採用したという発表もある。

また、今年2月には自動車の機能安全規格ISO 26262に対応するSoC開発に向けて、イタリアのYOGITECH社との提供を発表している。YOGITECH社は元々検証IPなどを手掛けるEDA寄りの企業であったが、近年は機能安全ソリューションに特化して活動しており、Arterisと組んで「FlexNoC」ベースの車載向けSoCのISO 26262対応を効率化するという。

2015.04.14

2015年4月13日、米EDA Consortiumは、2014年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

EDACの発表によると2015年Q4の世界のEDA売上総額は、前年比11.9%増、前Q3比15.0%増の21億400万ドルで、四半期の売上記録として過去最高を達成した。四半期の売上記録が前年同時期を上回るのはこれで19四半期連続となる。

2014年Q4の売上を製品分野別に見るとIC Physical Design & Verification分野とIP分野が大きく売上を伸ばしているのが分かる。IC Physical Design & Verification分野の伸びは毎年Q4に大きな売上を計上するMentor Graphicsの影響が大きいと思われる。IP分野はQ2,Q3,Q4と3四半期連続で20%以上の成長を続けている。

2014年Q4の売上を地域別に見ると、最大市場の北米が堅調な伸びを示し、中国を中心としたアジアが33.9%と大きな成長を見せた。アジア市場の四半期売上が6億ドルを超えるのはこれが初めてとなる。日本市場は前年比19.5%減と大きく後退。円ベースでみても前年比約7.6%減という結果となっている。

2014年Q4時点でのEDA業界の従業員数は前年比6.2%増、前期Q3とほぼ同じ31735人で過去最高を記録した。

2014Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億9950万ドル 3.1%Down

■IC Physical Design & Verification分野 4億8370万ドル 25.9%Up

■IP分野 6億4280万ドル 32.0%Up

■サービス分野 1億160万ドル 4.9%Up

■PCB/MCM分野 1億7620万ドル 7.6%Down

2014年Q4地域別の売上と昨年同時期との比較は以下の通り。

■北米 9億3540万ドル 13.8%Up

■ヨーロッパ 3億2890万ドル Flat

■日本 2億680万ドル 19.5%Down

■アジアその他地域 6億3290万ドル 33.9%Up

※EDAC(EDA Consortium)

2015.04.08

2015年4月8日、サンノゼで開催されたTSMC Technology Symposiumを受け、EDA各社がTSMC 10nm FinFETプロセスでのツール認証を相次いで表明した。

プレスリリースを行ったのは、Ansys, ATopTech, Cadence, Mentor, Synopsysの5社で各社の発表は以下の通り。

Ansysが認証を受けたのは、旧Apache時代からTSMC御用達のスタティック/ダイナミック電圧降下解析ツール「RedHawk」とエレクトロマイグレーション解析ツール「Totem」の2製品。同ツールはIntelやSamsungの先端プロセスでも認証されている。

AtopTechが認証を受けたのは配置配線ツール「Aprisa」とフロアプランニング・ツール「Apogee」の2製品。同社の「Aprisa」は、Samsungの14nm FinFETプロセスでも実績があるようだ。

Mentor製品では物理検証ツール「Calibre」と回路シミュレータ「Analog FastSPICE」、が認証された。さらに配置配線ツール「Olympus-SoC」は現在認証作業が進められているとの事。高い市場シェアを誇る「Calibre」と「Analog FastSPICE」はさておき、「Olympus-SoC」は競合製品ひしめく中、TSMCの先端プロセスで毎回認証を獲得しており健闘していると言える。

CadenceとSynopsysの両社は、配置配線ツールを中心に複数のデジタル、アナログ/カスタム/ツール群が認証を受けた。Synopsysは16nm FinFET+プロセスに関する認証も含めて発表しているため、どこまでが10nm FinFETプロセスで認証されたツールか定かではないが、少なくとも配置配線ツール「IC Compiler」は10nm FinFETプロセスで認証されており、新型の配置配線ツール「IC Compiler II」は現在認証作業が進められているとの事。またSynopsysは他社に先駆けてTSMC 16nm FinFET+プロセス向けのUSB,PCIe,HDMI,MIPI,DDR4,LPDDR4などのシリコン実証済みIPの提供開始を別途アナウンスしている。(プレスリリース文)

Cadenceも既存の配置配線ツール「Encounter Digital Implementation System」は10nm FinFETプロセスで認証されたが、新型の配置配線ツール「Innovus」は現在認証作業が進行中。その他に以下のツール群が10nm FinFETプロセスで認証されている。なお、CadenceによるとTSMCの10nmライブラリーはCadenceのキャラクタライゼーション・ツール「Liberate」と回路シミュレータ「Spectre」を使用して作成されているという。

Tempus™ Timing Signoff Solution

Voltus™ IC Power Integrity Solution

Voltus-Fi Custom Power Integrity Solution

Quantus™ QRC Extraction Solution

Virtuoso® advanced node platform

Spectre® simulation platform

Physical Verification System and Litho Electrical Analyzer

ちなみにTSMCの最先端10nm FinFETプロセス製品の量産は、今のところ2017年に予定されている。最初に出荷されるチップがどこの製品になるのか今から楽しみである。

2015.04.07

2015年4月6日、米SIA(Semiconductor Industry Association)は、2015年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年2月の世界半導体売上は前年同月比6.7%増、前月比2.7%減の277億9000万ドルで2月の売上としては過去最高を記録。売上が前年実績を上回るのはこれで22ヶ月連続となる。

2015年2月の世界半導体市場の売上を地域別に見ると、1月と同様に北米とアジアの成長が強く全体を押し上げている構図。日本はドルベースで前年比8.8%減となっているが円ベースだと前年比約5.7%増の換算となり実質的には成長している。

※SIA

2015.03.31

2015年3月30日、Synopsysはエンベデッド・ビジョン(Embedded Vision)向けの新たなプロセッサIPコア「EV Processor Family」を発表した。

Synopsysによると新製品「EV Processor」はコンピュータ・ビジョン技術の組み込みに特化したプロセッサで、ビジョン・プロセッシング向けに最適化されたマルチコア・アーキテクチャにより、ハイパフォーマンスかつローパワーな処理を実現。監視カメラ、ADAS、ゲームやバーチャル・リアリティといった様々な分野での利用を想定している。

「EV Processor」は32ビットのRISC CPUと「Object Detection Engine」と呼ぶプログラマブル・ユニットで構成されている。32ビットのRISC CPUは今回Synopsysが独自開発したコアで2コアまたは4コアを選択できる。特徴的なのは「Object Detection Engine」で、エンジンとしては最大8つのPE(processing element)を利用可することができ、機械学習のアルゴリズムであるコンボリューショナル・ニューラル・ネットワークを用いた物体認識が可能。このエンジンを利用する事で高性能なプロセッシングをミリワット・レベルの低消費電力で実現できる。Synopsysによると「EV Processor」は、既存のビジョン・プロセッサと比べて消費電力性能が5倍高い1000 GOPS/ワットの性能を発揮するという。

「Object Detection Engine」に実装されるコンボリューショナル・ニューラル・ネットワーク技術は、予め実施した機械学習のトレーニング/ティーチング結果をインプリする形で実現されており自律学習するものではない。また実装作業はSynopsysに依頼する必要があるが、将来的にはユーザーが独自に「Object Detection Engine」に実装できる開発環境が提供される計画。Synopsysは顔認識や道路の速度標識認識のリファレンス・デザインを用意している。

「EV Processor」の開発環境は、同社のARCプロセッサの開発環境「MetaWare Development Toolkit」を利用できるほか、OpenCVならびにOpenVXライブラリを利用可能。「EV Processor」上での実行に最適化された43のコンピュータ・ビジョン標準カーネルを持つOpenVXフレームワークも提供される。

「EV Processor」はSoCへの統合が容易でホスト・プロセッサへのアクセスやホスト・プロセッサとの同期が可能。またインターコネクト経由でSoC外のデータにアクセスする事もできる。Synopsysは既にプロトタイピング・システム「HAPS」上に「EV Processor」を実装したデモ環境を用意しているが、バーチャル・プラットフォーム向けの「EV Processor」のSystemCモデルも用意しており、これを利用する事で「EV Processor」を用いたSoCのソフト先行開発も可能となっている。

ビジョン・プロセッシングはGPGPUやカスタム・プロセッサを用いて高速処理を実現しているケースがあるが、組み込み用途には消費電力やコストの面で不向きであった。そこを狙ったのが今回Synopsysが発表した「EV Processor」で、小型でありながら、高性能かつ高精度、さらに低消費電力と、既存のソリューションを凌駕する最適なエンベデッド・ビジョン向けソリューションと言える。

Synopsysは5月29日に毎年開催しているASIP関連のセミナーを品川で開催する予定で、同セミナーにて「EV Processor」に関する詳細が紹介される予定。また、同セミナーでは先頃発表されたASIP開発向けの新ツール「ASIP Designer」についても紹介される見通し。

2015.03.23

2015年3月17日、Synopsysは同社の仮想プロトタイピング・ツール「Virtualizer」のバージョン・アップを発表した。

発表によると今回のバージョン・アップにより「Virtualizer」にMultiSim 機能、SimSight 機能、FirstBuild 機能の3つの新機能が搭載され、これによって仮想プロトタイピング・キット「VDK」を用いたシミュレーションのパフォーマンスが最大5倍に向上可能となった。

各新機能の概要は以下の通り。

MultiSim機能:VDKの並列実行機能、ホストマシンのマルチコア活用効率を最適化

SimSight機能:シミュレーションの視覚化機能、シミュレーションのプロファイリングを向上

FirstBuild機能:シミュレーション環境の構築、VDKのアップデートを加速

新機能を搭載した「Virtualizer」の最新バージョンは既に出荷が開始されている。

Synopsysはここ最近、特定プロセッサ向けの仮想プロトタイピングがプリ・ビルドされている開発キット「VDK」のラインナップ強化に力を入れており、先日もFreescale社がADAS開発向けに提供しているMCU「S32V200」ファミリーのVDKをリリースしている。(※プレスリリース文)

2015.03.23

2015年3月19日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けのEDAツールを手掛ける米Silvacoは、ICサインオフ解析ツールを手掛ける米Invarianの買収を発表した。

SilvacoによるInvarianの買収は既に完了済。その取引条件については明らかにされていない。

Invarianは最先端の大規模チップをターゲットに、電力、電圧、熱のサインオフ解析をコンカレントに実行できる「InVar」製品ファミリを提供していた。「InVar」製品ファミリは下記3製品を中心に構成されており、静的/動的IRドロップ解析ならびにエレクトロ・マイグレーション解析のサイン・オフ・ツールとしてTSMCの先端プロセス(20nm/16nm FinFET+ v0.9)で認証されていた。

・パワー解析ツール「InVar Pioneer Power」

・エレクトロ・マイグレーション/IRドロップ解析ツール「InVar Pioneer EM/IR」

・サーマル解析ツール「InVar Pioneer Thermal」

InvarianのCEOは「InVar」プラットフォームはSilvacoの回路シミュレータ「SmartSpice」やAMSシミュレータ「Harmony」の理想的な拡張になるとコメントしている。

※株式会社シルバコ・ジャパン

2015.03.20

2015年3月10日、Synopsysは、量産向けFinFETデザインにおける同社「Galaxyデザイン・プラットフォーム」の実績について発表した。

Synopsysの発表によると、量産向けFinFETデザインの90%でSynopsysのインプリメント・ツール群「Galaxyデザイン・プラットフォーム」が活用されているという事で、SynopsysはそのユーザーとしてGLOBALFOUNDRIES、Intel、Samsungのファウンドリ3社の名を挙げた。

90%という数字は、Intel、SamsungおよびSamsung&GlobalFoundries連合がFinFETチップの量産で先行しているためで、これにファウンドリ最大手のTSMCが加わると状況は大きく変わると思われるが、現時点ではSynopsysの「Galaxyデザイン・プラットフォーム」が量産向けFinFETデザインのメイン・ストリームとなっているようだ。

各ファウンドリの顧客として名が挙がっているのは、Achronix、Global Unichip、HiSilicon Technologies、Marvell、Netronome、NVIDIA、Samsungの7社。

Synopsysの「Galaxyデザイン・プラットフォーム」は以下のツールで構成されている。

・論理合成ソリューション Design Compiler

・テストパターン生成ソリューション TetraMAX ATPG

・配置配線ソリューション IC Compiler、IC Compiler II

・スタティックタイミング・サインオフ・ソリューション PrimeTime

・寄生抽出ソリューション StarRC

・回路シミュレータ HSPICE

・FastSPICEシミュレータ CustomSim、FineSim

・カスタム・デザイン向けスケマティック・ソリューション Galaxy Custom Designer

・カスタム・デザイン・レイアウト・ソリューション Laker

・フィジカル検証ソリューション IC Validator

2015.03.20

2015年3月9日、Synopsysは、東芝による同社の配置配線ツール「IC Compiler II」の採用事例を発表した。

発表によると東芝はSynopsysの「IC Compiler II」を用いて40nm SoCのテープアウトに成功。「IC Compiler II」を用いることでインプリメンテーションの実行速度を6倍に向上しメモリー使用量は1/3に削減。また、クロックツリー・シンセシス工程でのバッファ・エリアを60%に削減し、面積と消費電力の結果品質を大幅に改善した。

「IC Compiler II」によるインプリメント結果は当初の品質目標を上回るもので、東芝はこの成功を受け「IC Compiler IIデザイン・キット」をリリースし、「IC Compiler II」の社内標準ツールとしての展開を加速させたという。

「IC Compiler II」は昨年3月に発表され、その一般リリースは昨年12月に開始されたばかり。昨年3月の時点ではパナソニックやルネサスなどが先行ユーザーとして名を連ねていたが東芝の名は無かった。

2015.03.12

2015年3月10日、Cadenceは「Encounter Digital Implementation(EDI) System」の後継となる新しい配置配線ツール「Innovus(イノバス)」を発表した。

Cadenceによると、新製品「Innovus」は先端の16/14/10nm FinFETプロセスに対応する配置配線ツールで、既存の配置配線ツール「EDI」と比較して平均10-20%、PPA(Performance,Power,Area)を改善し、TATを最大10分の1に削減する事が可能。Cadenceは「Innovus」をあらゆるプロセスノードに対応可能としているが、先端チップの主流である28nmプロセス以降のチップ設計を主なターゲットに見据えている。

新製品「Innovus」では新技術の導入や既存機能の改善など様々な改良が施されているが、大きなポイントは2つ。一つは、大規模デザインを効率的にハンドリング可能となった点。そしてもう一つは最適化機能が広範囲に強化された点である。

まず、分散処理の機能が改善され、従来よりも広範囲な分散処理が可能となった。Cadenceによると分散効率は既存の「EDI」と比較して最大10倍という事で、分散効率だけでなくシングルCPUでの処理効率も改善されているという話。

また、デザイン・キャパシティも拡張され、インスタンス数5-10Mのより大規模なデザイン・ブロックを取り扱う事が可能となった。これによりデザインの合計ブロック数が減り、結果として設計工数を週単位、月単位で削減できるようになる。

最適化機能については、「全体最適化」というのが一つのキーワードとなっており、様々な新技術が導入されている。まず今回「Innovus」では新たな配置エンジン「GigaPlace」が導入された。「GigaPlace」は配線長やパスに注目したポイント的な最適化ではなく、全体のスラックのマッピングを行った上で全体的な配置最適化を可能とする。これにより配置の質を改善すると同時にデザイン全体の合計スラック数を1/5-1/10に圧縮できるという事で、配置以外の最適化にも大きな効果がある。

タイミングの最適化に関しては、分散処理効率の向上と合わせて「GigaOpt」と呼ばれる最適化エンジンがエンハンスされ、タイミング、パワー、エリアの各最適化をワンショットで一気に最適化できるようになった。更にクロック・ツリー・合成に関しては、「CCOpt」と呼ばれるエンジンに「FlexH」と呼ぶ新たなクロック合成機能が搭載され、従来人手で作成していたHツリーライクなクロッキングをフロアプランを考慮して自動的に作成できるようになった。

これら複数の新たな最適化手法によって「Innovus」はPPA(Performance,Power,Area)の改善を実現している。

その他、設計生産性の向上という面では、同社の新型サイン・オフ・ツール「Voltus」、「Tempus」、「Quantus」のエンジンが「Innovus」に取り込まれ、設計の初期段階からインプリメントとサインオフの誤差を無くした設計が可能に。これらの効果により、「Innovus」を利用すればデザインの目標性能により早く到達可能で、同じ時間を費やせば「EDI」よりも質の高いデザインを実現できるという。

尚、今回の「Innovus」の発表には既に先行ユーザーとして同ツールを利用しているARM、Juniper Networks、Renesas、FreeScale、MaxLiner、Spreadtrumがコメントを寄せている。ARMはCadenceと共同で「Innovus」を用いて最新のCortex-A72コアを実装し、面積目標をクリアしながら2.6GHz超の動作周波数を達成したとしている。(関連プレスリリース1、

関連プレスリリース2)

2015.03.10

2015年2月26日、Synopsysは、同社のARCプロセッサをベースとしたシステムのソフトウェア開発をターゲットとしたオープン・ソース・プラットフォーム「embARC Open Software Platform」の立ち上げを発表した。

今回発表された「embARC Open Software Platform」は、WebサイトembARC.org、同サイト上に用意されるオープンソースのソフトウェア群、開発ツール、ドキュメント、ユーザー・フォーラムの総称で、ARCベース・システム向けのソフトウェア開発の効率化を目的としてSynopsysが用意した環境となる。

WebサイトembARC.orgは無料で登録可能。登録すればオープンソースのソフトウェア群を無料で一括ダウンロードできる。

提供されるソフトウェアは以下の図の通りで、リアルタイムOSやドライバの他に組込みソフトウェア・スタック、ファイルシステム、プロトコル・スタックなどミドルウェアも提供される。

開発ツールとしては、GNUベースの無償ソフトウェア開発環境「GNU command line tools for ARC Processors」をGitHubからダウンロード可能。embARC.orgからダウンロード先がリンクされている。

また開発環境としては、Xilinx Spartan-6を搭載し、ARC EM4, EM6, EM5D, EM7Dの各コアのFPGAイメージがプリ・インストールされた開発ボード「ARC® EM Starter Kit」も用意されており、同ボードを用いてARC向けソフトウェアを開発する事もできる。同ボードは有償で価格は99ドル。Synopsysが直接オンラインで販売している。

※画像はARC® EM Starter Kitのブロック図

SynopsysはIoTと呼ばれるトレンドをARCプロセッサ拡販の商機と捉え、無償または低コストでユーザーがアクセスできる「embARC Open Software Platform」を用意することで、顧客の新規開拓と囲い込みを狙っている。

2015.03.05

2015年3月4日、Mentor Graphicsは、アナログ/ミックスドシグナルIC設計ツールを手掛けるTanner EDAの事業資産を買収したことを発表した。

今回の買収に関する取引条件などの詳細は明らかにされていないが、既に買収の契約は完了しており、今後Tanner EDAの提供するEDAツールはMentor Graphicsを通じて提供されることになる。当然ながらMentor GraphicsはTanner EDAの既存の顧客のサポートを継続する。

Tanner EDAは1988年創業のEDAベンダでフロント・エンドからバック・エンドまでアナログ/ミックスドシグナルIC設計に包括的に対応するツール群を提供。Tabber EDAのツールはWindosをベースとしており、リーズナブルな価格設定である事から教育機関等でも幅広く利用されており、同社によるとユーザー数は67ヶ国5000以上、33000以上のライセンス発行実績があった。また、アナログ/ミックスドシグナルIC設計ツールと合わせてMEMS設計向けのツールにも力を注いでいた。

近年はサードパーティー各社とのツール連携に積極的に動いており、STAツールのIncentia、論理シミュレータのAldec、SPICEシミュレータのBerkeley Design Automationなどとコラボレーションしていた。ちなみにBerkeley DAも昨年Mentor Graphicsに買収されている。(※関連ニュース)

※メンター・グラフィックス・ジャパン株式会社

2015.03.04

2015年3月3日、米SIA(Semiconductor Industry Association)は、2015年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年1月の世界半導体売上は前年同月比8.7%増、前月比2%減の285億3000万ドルで1月の売上としては過去最高を記録した。売上が前年実績を上回るのはこれで21ヶ月連続。世界半導体市場は2014年に過去最高を記録したがWSTSの予想通り、今年もその右肩上がりの成長は継続しそうだ。

※WSTS:World Semiconductor Trade Statistics

2015年1月の世界半導体市場の売上を地域別に見ると、北米とアジアがともに前年比2ケタ増を記録。日本はドルベースで前年比8%減となっているが円ベースで換算すると前年比約5%の売上増となっている。

2015年の世界半導体市場の成長予測は様々だが、WSTSは3.4%と予測。調査会社のGartnerは5.4%、IDCは3.8%と予測しており、11%と予測する調査会社もある。

※SIA

2015.02.27

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2015.02.27

2015年2月27日、Mentor Graphicsは、2015会計年度第4四半期(14年11月-15年1月)の売上を報告した。

発表によると、Mentorの2015会計年度Q4の売上は、前年比約9.5%増、前Q3比約1.5倍の4億3910万ドル、営業利益は前年実績を上回る1億3953万ドルだった。この実績はQ3実績報告時の予測を上回るもので同社の四半期売上として過去最高となる。

Mentorの2015会計年度(2014年2月-2015年1月)の売上合計は、前年比約7.6%増の12億4413万ドルで過去最高、営業利益は前年比約2.6%増の1億8781万ドルという結果。(※GAAP基準による会計結果)

Mentorの2015会計年度の売上の内訳を見ると、製品分野別の構成は大きな変化は無いが、市場別で見るとアジア・パシフィックにおける売上が伸びているのが分かる。

MentorはこのQ4(11-1月)の間にCFD(数値流体力学)ソフト「FloEFD」、熱流体解析ツール「Flowmaster」をバージョンアップ。新製品としてはPCIe4.0向けの検証IP、ソフトウェア開発向けのバーチャル・プロトタイプ・キットを発表している。(※

関連ニュース)

また1月にはFPGAプロトタイピング向けコンパイラの仏Flexras Technologiesの買収を発表しており、FPGAベースのプロトタイピング市場への参入を匂わせている。(※

関連ニュース)

Mentorは次期2016会計年度Q1(15年2-4月)の売上を2億600万ドル程度と予測。2016会計年度は更なる成長を見込んでいる。

2015.02.25

2015年2月24日、Cadenceは高位合成ツールの新製品「Stratus High-Level Synthesis」を発表した。

Cadenceの新型高位合成ツール「Stratus」は、一言で言うと既存の高位合成ツール「Cynthesizer」と「CtoS」のいいとこ取りをした統合製品で、正式には今年の3月末にリリースされる予定となっている。

Cadenceによると「Stratus」の合成品質は、人手によるRTL設計と比較してPPA(消費電力、パフォーマンス、面積)のQoRを概ね20%改善でき、検証速度は5倍、設計生産性は10倍向上可能との事。

「Stratus」の大きな特徴はIPのインテグレーション能力とバックエンド・ツールとの親和性を兼ね備えている点で、「Cynthesizer」のユーザーから見ると論理合成ツール「RTL Compiler」とのイタレーション機能により合成結果を更に向上可能になり、「CtoS」のユーザーから見ると「Cynthesizer」で用意されていたインタフェースIPや浮動小数点IPなど各種合成用IPを用いたIPインテグレーションが可能となる。この辺りが既存ツールのいいとこ取りの部分と言える。

合成エンジンに関してその詳細は明らかにされていないが、基本的に既存の合成用Cコードを入力可能でその合成結果が劣化する事は無い。未だ「Cynthesizer」と「CtoS」の合成スクリプトやIPが完全にサポートされている訳ではないが、「Stratus」への移行をユーザーに促すためにマイグレーション対応を順次進めていくという話だ。

GUIに関しては、合成作業のGUIは「Cynthesizer」ベース、合成結果の解析GUIは「CtoS」ベースとここもいいとこ取りの形となっている。

尚、「Stratus」のリリースにより「Cynthesizer」と「CtoS」のバージョンアップは終了するが、ツールとしては引き続きサポートを継続。ユーザーは「Cynthesizer」と「CtoS」を使い続ける事ができる。ライセンスにおいても「Stratus」のライセンスで「Cynthesizer」と「CtoS」を利用可能にするなど、既存のユーザーに対して配慮する形のようだ。

聞くところによると、既に「Cynthesizer」と「CtoS」を利用したテープアウト件数はワールドワイドで1000件を超えており、現在進行形でユーザー数は伸びているとの事。中にはFPGAユーザーも含まれているという事で、「Stratus」ではFPGAターゲットの合成もサポートされている。

2015.02.24

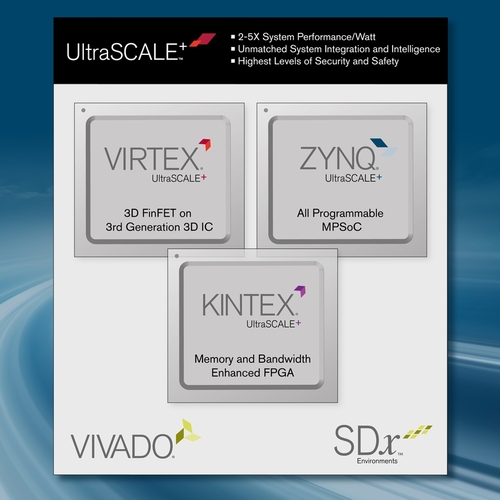

2015年2月24日、XilinxはTSMC 16nm FinFET+プロセスで製造される新FPGAファミリ「UltraScale+」を発表した。

プレスリリース文

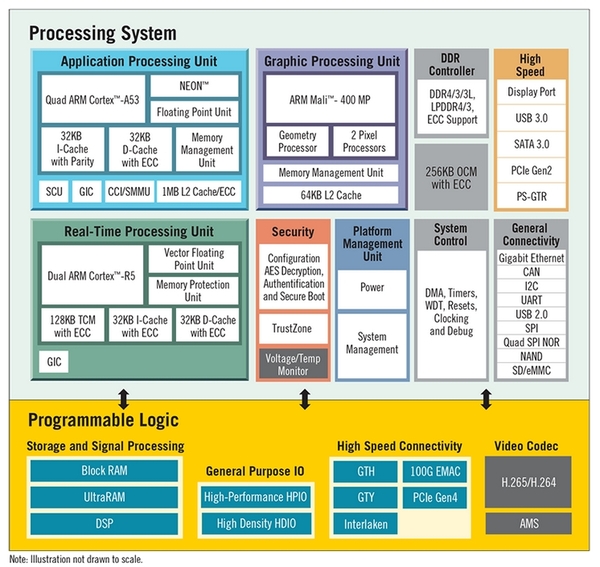

今回発表された

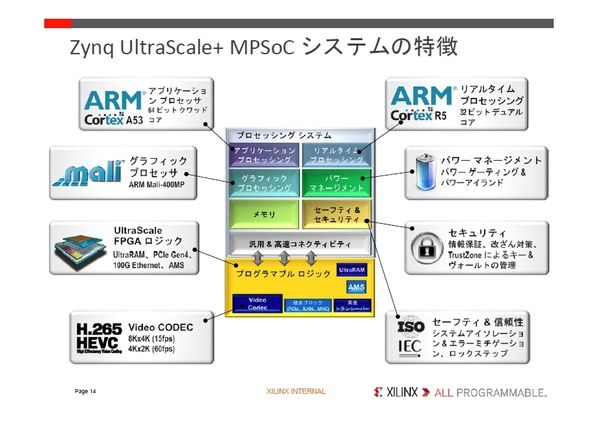

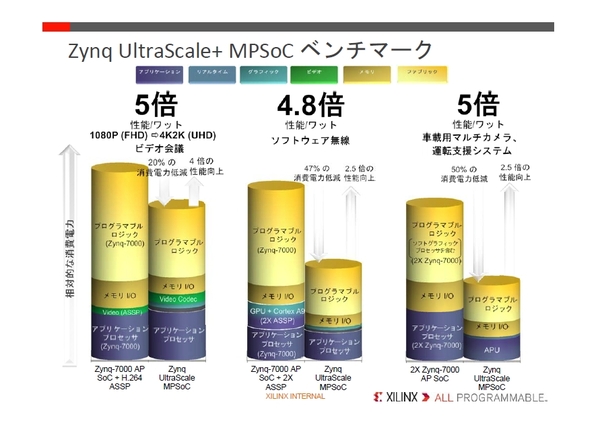

新FPGAファミリ「UltraScale+」を構成するのは、ハイエンドFPGA「Virtex UltraScale+」シリーズ、ミッドレンジFPGA「Kintex UltraScale+」シリーズ、そしてARM搭載FPGA「Zynq UltraScale+」の3系統で、新しいVirtexはシリコン・インターポーザを用いた2.5次元パッケージ技術とFinFET技術を組み合わせて実現。Xilinxはこれを「3D-on-3D」と称している。

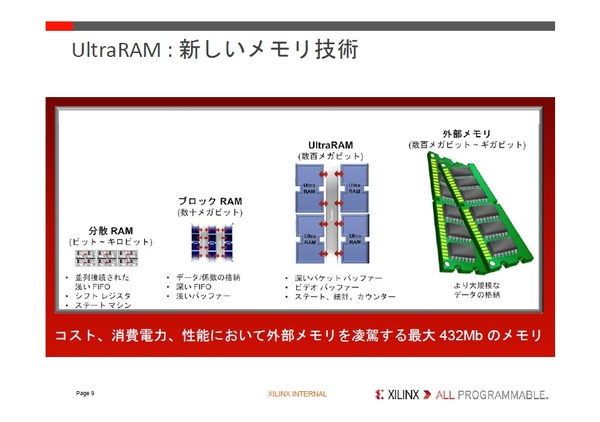

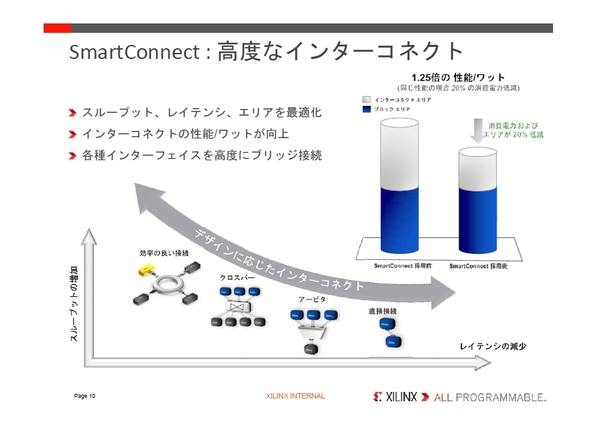

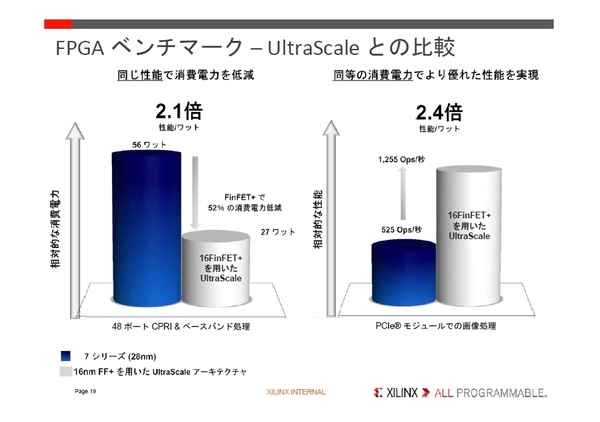

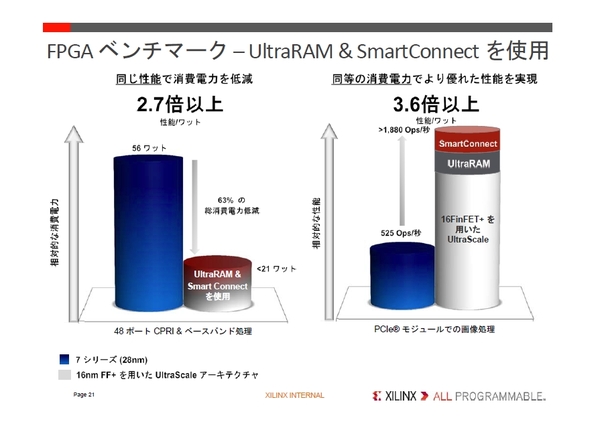

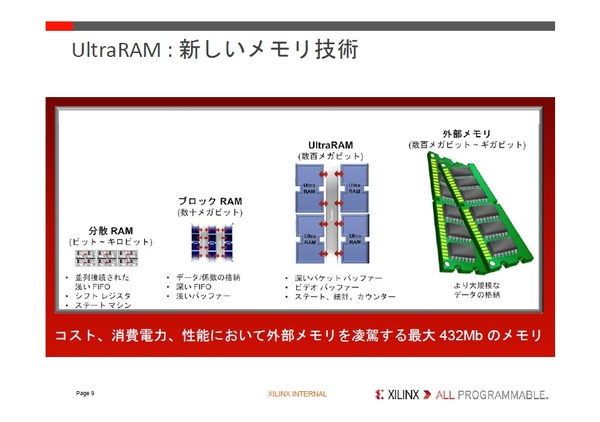

新ファミリ「UltraScale+」は既存のUltraScaleアーキテクチャをベースに新たなメモリ技術「Ultra RAM」とインターコネクト最適化技術「SmartConnect」によって性能向上が図られており、既存の28nm製品と比較して1ワット当りの性能が2-5倍向上されている。

「Ultra RAM」は、FPGAと同じダイに搭載される大容量のオンチップSRAMで最大432Mbに対応。深いパケットやバッファリングなどに対応できる。

「SmartConnect」は開発環境「Vivado」に実装された新機能で、デザインの要求性能に応じてインターコネクト・トポロジを自動的に最適化することができる。これによりパフォーマンス、消費電力、インターコネクトのロジック面積を20-30%改善する。

新しい「Zynq UltraScale+」には、最大1.3GHzで動作するARMのクワッドコア Cortex-A53、最大600MHzで動作するARMのデュアルコア Cortex-R5、そして最大466MHzで動作するARMのGPU Mali-400MP2が搭載され、既存のZynqと比較して1ワット当たりのシステム性能が最大5倍になった。

また、「Zynq UltraScale+」では、パワー・マネジメント機能が追加され、ARM TrustZoneによるセキュリティ機能が強化されたほか、リアルタイム・プロセッシングを行うCortex-R5に対して機能安全向けの対応も施された。またH.265/264ビデオ・コーデックのハードIPも用意された。このハードIPは「Kintex UltraScale+」にも搭載される。

Xilinxによる新ファミリ「UltraScale+」のベンチマーク結果は以下の通り。

新ファミリ「UltraScale+」は今年Q4から出荷開始の予定で、「UltraScale+」対応の開発環境は既に一部の顧客に提供が開始されている。

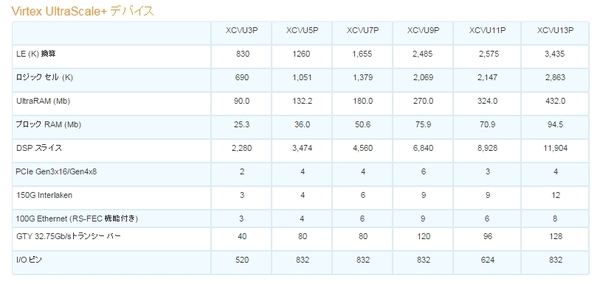

Virtexシリーズのデバイス構成は以下の通りで最上位品はUltraRAM 432Mb、ブロックRAM 94.5Mb、DSPスライス×11,904、150G Interlaken×12、32.75Gb/s トランシーバー×128と驚異的な仕様となっている。