2016.02.16

2016年2月10日、ARMは、2015会計年度第4四半期(2015年10-12月)の売上を報告した。

ARMの2015年Q4の売上は、前年比約14%増、前期比約8.6%増の4億790万ドルで四半期売上として過去最高を記録。税引き前の純利益は約2億1020万ドルで英ポンド・ベースでは前年比約17%増だった。

ARMの2015会計年度の売上合計は前年比15%増の14億8860万ドルで過去最高を記録。税引き前の純利益は約7億8634万ドルで英ポンド・ベースでは前年比約24%増だった。

2015年も順調に売上を伸ばしたARMだが、対前年比の売上推移をみると2015年Q4は僅かに失速。世界スマホ市場の停滞などの背景を考えると2016年の成長率は従来通りとはいかなそうだ。

ARMのQ3売上の内訳を見ると、プロセッサ・ライセンスの売上は前年と同等、プロセッサ・ロイヤリティの売上は前年比約30%増と前Q3に続いて大きく伸びた。全売上に対しロイヤリティ売上の占める割合は53%となっている。

2015年Q4におけるプロセッサ・ライセンスの契約数は51件で、最新のARMv8-Aアーキテクチャ・ベースのプロセッサのライセンス契約が11件、昨年11月に発表したばかりのARMv8-Mのアーキテクチャ・ライセンス契約が1件、GPU Maliのライセンス契約が8件含まれている。またプロセッサ・ライセンスとは別に同社初となる7nm プロセス向けフィジカルIPの契約が1件あったという。ライエンス契約の内訳は下記の表の通り。

2015年Q4で出荷されたARM搭載チップの総数は約40億個で前年よりも約16%増えた。

※画像はARM発表資料より抜粋

2016.02.05

2016年2月3日、Cadenceは、2015会計年度第4四半期(2015年10-12月)の売上を報告した。

Cadenceの2015年Q4売上は、前年同時期比約4.2%増、前期Q3比約1.6%増の4億4100万ドルで前Q3に続いて同社の四半期売上記録を更新。純利益は前年比約23%増の8000万ドルだった。(※GAAP基準による会計結果)

Cadenceの2015会計年度の売上合計は前年比7.6%増の17億200万ドル、純利益の合計は前年比約58%増の2億5200万ドルという結果となった。Cadenceはこの5年間で売上を約1.8倍に拡大した事になる。

Cedanceの売上拡大の原動力は、TensilicaコアをはじめとするIPビジネスの拡大と各種新製品の市場投入が功を奏した結果と言える。2015年においては配置配線ツール「Innovus」とエミュレーター「Palladium® Z1」という2種類の大型新製品を投入しており、最先端チップを設計する顧客へのアプローチを強めている。

Cadenceは、2016会計年度も更なる成長を見込んでおり、来期Q1の売上額を4億4000-5000万ドル、2016会計年度の通年売上を現時点で17.9億-18.4億ドルと予測している。

2016.02.04

2016年2月3日、Synopsysは同社の提供する全ての回路シミュレータに共通の管理/解析環境を標準装備した事を発表した。

発表によるとSynopsysは同社の回路シミュレータ「HSPICE®」、「FineSim®」、「CustomSim™」標準機能として搭載する共通の検証環境を新たに開発。各製品の2016.03バージョンから同機能の提供を開始する。

新たに用意された検証環境はGUIベースのシミュレーション管理/解析環境で、SPICE、Verilog、DSPFを直接読み込む事が可能。シミュレーションのセットアップから自動実行、結果解析(モンテカルロ解析)に至る一連のネットリスト・ベースの検証フローをサポートしており、回路シミュレーションのコックピットとして利用できる。

Synopsysはこの新しい検証環境を提供する事で、アナログ検証の工数削減を目指しており、回路シミュレーションの効率化と合わせてシミュレーション結果の抽出と解析を効率化するための複数の機能を検証環境に盛り込んでいる。

?バッチモード・シミュレーションのための先進のジョブ分散/モニタリング機能

?グラフィカル波形ビューワ Custom WaveView™との統合による高度な波形解析

?業界標準のTCLスクリプトによるリグレッション・テストの自動化

?ネットリストベースのナビゲーション、クロス・プロービング、シンタックス・チェックのための、各種言語に応じたテキスト・エディット機能

?チャート出力、統計解析、ヒストグラム、統計分布図などの検証結果ビジュアル化/データマイニング機能

?Web表示のためのHTMLベースのドキュメント化をはじめとする詳細なレポート生成機能

Synopsysの回路シミュレータのユーザーにとっては、これら豊富な機能が標準提供されることにより、あと付けで他社製のアナログ検証環境を組み込む必要が無くなり、アナログ回路の検証スループット向上と合わせてコスト面、ツールの運用面でもメリットを享受できる。

なお、既に先行ユーザーとして「FineSim」に搭載されたこの検証環境を評価利用していたSamsungのSystem LSI Business部門は、既に今後のアナログ設計プロジェクトにおける同検証環境の採用を決めているという。

2016.02.03

2016年2月3日、CadenceはDFTツールの新製品「Modus」を発表した。

「Modus」は、既存のDFTツール「Encounter Test」の後継にあたる新製品で、Cadence曰く約20年ぶりの大きな技術革新が実現されている。というのも、そもそも既存の「Encounter Test」は2002年にCadenceが買収したIBMの内製EDA技術をベースに開発された経緯があり、約20年に渡り様々な改良が加えられてきたが、今回発表された「Modus」は10種類以上にも及ぶ新たな特許申請技術を取り込み大幅な技術刷新が行われたという事だ。ちなみに「Modus」も既存の「Encounter Test」同様、IBMからCadenceに移ったR&Dメンバーを中心に開発されている。

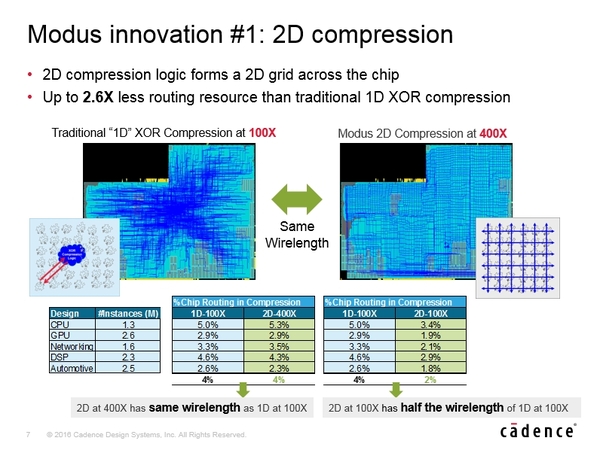

「Modus」の実現する特筆すべき機能は、デザイン・サイズやカバレッジに影響しない高いテスト圧縮率の実現で、いずれもテスト時間の大幅な短縮すなわちテスト・コストの削減を狙ったもの。それらはフィジカルを考慮する「2D Elastic Compression」アーキテクチャと呼ばれる同ツールの新たなアーキテクチャーによって実現されている。

「2D Elastic Compression」は、「2D Compression」機能と「Elastic Compression」機能の2つの機能で成り立っており、「2D Compression」機能は同社の論理合成ツール「Genus」と組み合わせて利用する事でフィジカルを考慮しながらテスト回路を挿入する事が可能。これによりフィジカルを考慮しない場合よりもテスト回路の配線長を最大60%以上短くできる。一般的に利用されているXOR圧縮手法では圧縮率を上げると配線長が伸び配線リソースに大きな影響が及んでしまうが、「Modus」を利用すれば配線リソースへの影響を抑えつつ高いテスト圧縮率を実現できる。

Cadenceの示す評価データによると、従来手法で100倍の圧縮率の場合と「2D Compression」を用いた400倍の圧縮率の場合で配線長はほぼ同一。同じ圧縮率の場合は「2D Compression」を用いる事で配線長を半減できたという事だ。

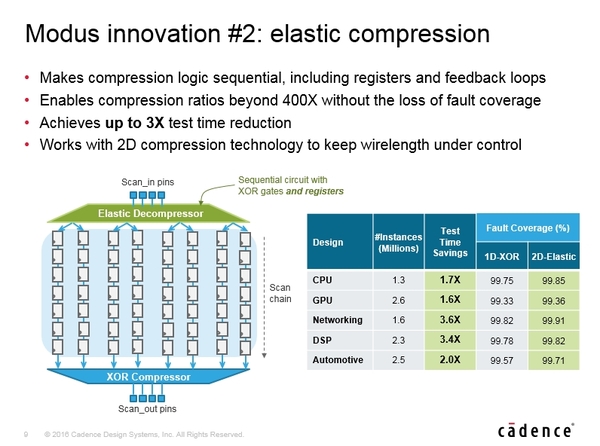

もう一つの「Elastic Compression」機能は、論理合成ツール「Genus」との組み合わせに関わらず利用できる機能でデコンプレッション・ロジックに対してレジスタやフィードバック・ループを組み込むもの。これによりATPG実行中に複数のスキャンサイクルをまたいだケアビットのコントロールが可能となり、従来手法よりも高い故障検出率を実現できるようになる。別の言い方をすると、従来、テスト圧縮率を上げると低下する傾向にあった故障検出率を高い圧縮率でも維持できるようになる。

Cadenceはこの「2D Compression」機能と「Elastic Compression」機能の2つの機能を組み合わせる事で、テスト時間を最大1/3までに削減できるとしており、既に同ツールを利用している先行ユーザーからはテスト時間を40-70%削減出来たという複数のコメントが寄せられている。

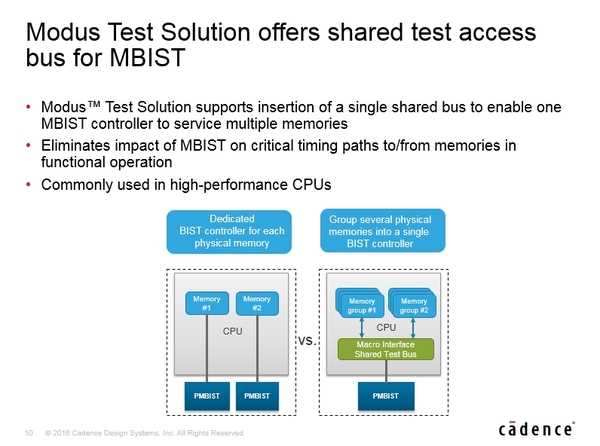

なお、「Modus」ではメモリBISTの機能として、組み込みメモリバスを用いて一つのBISTコントローラで複数のメモリを扱えるような機能もサポートされているとの事。

Cadenceは新製品「Modus」の正式出荷を今年の3月末-4月上旬に予定している。

2016.02.03

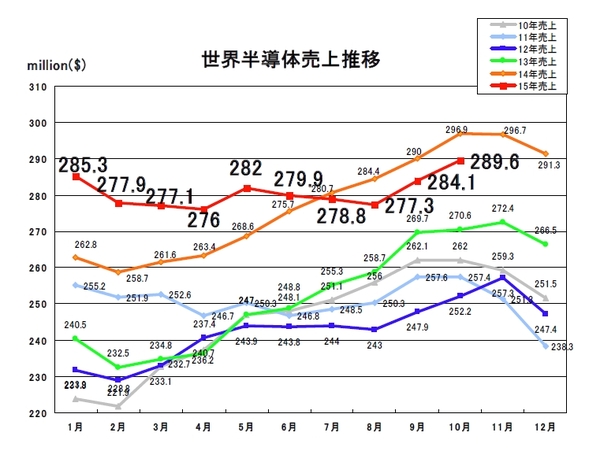

2016年2月3日、米SIA(Semiconductor Industry Association)は、2015年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年12月の世界半導体売上は前年同月比5.2%減、前月比4.4%減の276億2000万ドルで6ヶ月連続で前年実績を下回った。

2015年通年の世界半導体市場の売上額は計3352億ドルで前年比0.2%減。年初時点ではプラス3-5%の成長が予測されていたが、7月以降は市場が下降傾向に入りそのまま持ち直す事は無かった。

2015年12月の世界半導体市場を地域別の売上で見ると、中国を除く全ての市場が前年割れとなっており、中でも北米市場は前年比14.5%減と大きく売上を落とした。好調の中国は11月に続いて市場規模首位を維持した。

日本市場の売上はドルベースで前年比8.1%減となっているが、円ベースで換算すると前年比約6%減の約3133億円という計算になる。

なお、昨年12月に発表されたWSTS秋季予測によると2016年の世界半導体市場は1.4%の成長と予測されている。

2016.01.26

少し前の話となるが、2015年12月3日に米EDN誌が2015年「Hot 100 products」を発表した。

EDN誌の「Hot 100 products」は、1年間で読者と編集者の注目を集めた製品を表彰するもので、15の製品カテゴリにおいて計100製品が選出された。

EDA (IC) Tools & IP部門で選出されたのは計5製品で、EDAツールとしては以下の通りCadenceとMentor Graphicsの製品がそれぞれ2製品選出された。

・Innovus implementation system(Cadence)

2015年4月にリリースされた新型の配置配線ツール

・Perspec System Verifier(Cadence)

SoCの検証シナリオ作成ツール

・Veloce Power Application software(Mentor Graphics)

エミュレータ上で稼働するパワー解析ツール

・Xpedition Package Integrator (Mentor Graphics)

ICパッケージとPCBレイアウトの協調設計ツール

なお、PROGRAMMABLE LOGIC部門では、以下の通りAlteraおよびXilinxのFPGA開発向けツールが選出されている。

・Quartus II Spectra-Q engine(Altera)

2015年5月にリリースされたAlteraの開発環境Quartus IIの新型エンジン

・SDAccel IDE(Xilinx)

OpenCL、C、C++をサポートするシステムおよびソフトウェア設計者向け開発環境

2016.01.22

2016年1月19日、Cadenceは同社の新型配置配線ツール「Innovus」を中国Huaweiの半導体子会社Hisiliconが採用した事を発表した。

発表によるとHiSiliconは製品評価を経て「Innovus」を28nmおよび先端ノードFinFETのDSP設計プロジェクトに採用。「Innovus」を用いることで目標性能を達成しつつ従来使用していた配置配線ツールよりも面積を20%削減できたという。従来ツールが何かは不明だがHiSiliconは以前Synopsys「IC Compiler」のユーザーとして事例発表を行っている。

ここ最近HiSiliconはデジタル設計ツールだけでなく、IPやアナログ設計ツールの導入においてもCadenceと密接な関係にあるようだ。

「Innovus」は、昨年の春に発表された新製品でCadence既存の配置配線ツール「EDI」と比較して、PPA(Performance,Power,Area)を平均10-20%改善し、TATを最大10分の1に削減する事が可能としている。(※関連ニュース)

2016.01.13

2016年1月6日、米EDA Consortiumは、2015年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

EDACの発表によると2015年Q3(7-9月)の世界のEDA売上総額は、前年比7.1%増、前Q2比2.6%増の19億5750万ドルで、Q3の売上として過去最高を記録した。四半期の売上記録が前年同時期を上回るのはこれで22四半期連続となる。

2015年Q3のEDA売上を製品分野別に見るとIC Physical Design & Verification分野が前年比14%増と大きく伸びた。成長を続けるIP分野も7四半期連続の前年比2ケタ増を達成し、ついにCAE分野を抜いてEDA市場の最大分野となった。

2015年Q3のEDA売上を地域別に見ると、Q2に続いて最大市場の北米と2番手のアジア市場が順調に成長。北米市場は再び売上9億ドルを超えた。日本市場もQ2の前年割れから回復し、売上を2億ドル台に戻した。

2015年Q3時点でのEDA業界の従業員数は前年比5.6%増の33430人で過去最高記録を更新した。

2015Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億3470万ドル 5%Up

■IC Physical Design & Verification分野 4億790万ドル 14%Up

■IP分野 6億5290万ドル 11.4%Up

■サービス分野 9960万ドル 11.4%Up

■PCB/MCM分野 1億6240万ドル 3%Up

2015年Q3の地域別の売上と昨年同時期との比較は以下の通り。

■北米 9億420万ドル 7.4%Up

■ヨーロッパ 2億9030万ドル 2.2%Down

■日本 2億520万ドル 8.3%Up

■アジアその他地域 5億5780万ドル 11.6%Up

2016.01.07

2016年1月6日、米市場調査会社のIC Insightsは、2015年半導体ファウンドリのウエハ製造キャパシティのランキングを発表した。

IC Insightsのレポートによると、2015年半導体ウエハ製造キャパシティのTOP10は以下の通り。

※画像はIC Insights社のWeb公開データ

ランキングを見ると上位5社に変更は無く、昨年同様2位のTSMC以外はメモリ勢という構図となった。

前年実績に対し最もキャパシティを増やしたのは6位のGlobalFoundriesで前年比18%増、TSMCも14%増とロジック勢も積極的な投資を行った事が分かる。

上位10社で世界の半導体ウエハ製造の72%を占めているが、この中には未だ中国企業はランキングされていない。しかし、積極的な半導体投資を進める中国企業の動きを見ていると、中国最大のファウンドリSMICがランキングに上がるのは時間の問題だろう。

※IC Insights http://www.icinsights.com/

2016.01.07

2016年1月5日、米SIA(Semiconductor Industry Association)は、2015年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年11月の世界半導体売上は前年同月比3%減、前月比0.3%減の288億8000万ドルで5ヶ月連続で前年実績を下回った。

2015年の世界半導体市場は上半期は好調に売上を伸ばしていたが、7月以降は一転して売上の減少が続いている。2015年の年初時点では各関係機関は一様に数パーセントの成長を予測していたが、2015年世界半導体市場は最終的にほぼ2014年と同等の売上額に落ち着きそうだ。

2015年11月の世界半導体市場を地域別の売上で見ると、中国以外の市場は全て前年割れとなっており、市場規模としては中国が初めて首位に躍り出た。

日本市場の売上は円ベースで換算すると前年比約3.6%減の約3283億円という計算になる。

※SIA

2015.12.08

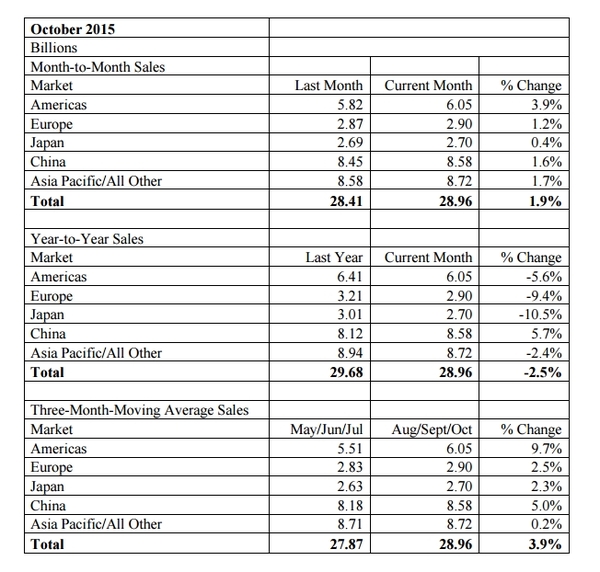

2015年12月3日、米SIA(Semiconductor Industry Association)は、2015年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年10月の世界半導体売上は前年同月比2.5%減、前月比1.9%増の289億6000万ドルで4ヶ月連続で前年実績を下回った。

世界半導体市場の停滞気調は今年7月から始まっており依然継続中。市場の動きを踏まえてWSTS秋季予測では今年の半導体市場の成長率予測を+0.4%に下方修正している。

地域別の売上を見ると欧州および日本市場が為替レートの変動で前年実績を大きく割り込んでいるが、売上額としてはそれ以上に北米市場の売上(対前年)が落ちており、3ヶ月連続の売上前年割れとなっている。中国を除くアジア市場も同様に、3ヶ月連続の売上前年割れ。

日本市場の10月売上を円ベースで換算すると前年比約0.3%減の約3241億円という計算になる。

※SIA

2015.12.07

Imagination Technologiesは現在Kickstarter上でIoTシステム開発キット「Creator Ci40」のキャンペーン・プロジェクトを実施している。

このIoTシステム開発キット「Creator Ci40」を構成するのは、「Creator Ci40 development board」、「Clicker expansion board」、「Click sensor board」の大きく3つのコンポーネント。

「Creator Ci40 development board」は、MIPSデュアルコア・ベースのCPUを搭載しており、WiFi(802.11 ac)、Bluetooth、6LoWPAN、Ethernetなど豊富な通信をサポートしている。また、セキュリティ・チップも搭載するほか、Raspberry Piのインタフェースも用意する。

このボードはキットの中心となるボードでIoTシステムのHUBの役目を果たす。

「Clicker expansion board」は単4電池2本で6LoWPANデバイスとして動作するボードでMicrochip社製のMIPSベースのマイクロコントローラ「PIC32MX」を搭載している。もう一つの「Click sensor board」をこのボードに搭載するためにmikroBUSソケットが用意されており、様々な「Click sensor board」を利用してモバイル・デバイスに各種機能を吹き込む。

「Click sensor board」はMikroElektronika社が提供する小型モジュール・ボードでセンサーなど様々な機能を実現するボードが100種類ほど用意されている。今回の「Creator Ci40 Kit」には、リレーボード、モーションセンサーボード、サーモセンサーボードの3種類がパッケージされる。

OSなどは全てオープンソースのソフトウェアをサポートしており、ベースボードの「Creator Ci40 development board」では、OpenWrt, Debian, そしてGoogleのIoT向けOS Brilloをサポート。「Clicker expansion board」では、Contiki OSがサポートされている。

また、同キットを利用したIoTシステムとして、クラウド側(サービス側)の環境としてImagination Technologiesが用意した無償の「FlowCloud」も用意される。

この「Creator Ci40」プロジェクトは12/23までとなっており、プロジェクト参加者への製品出荷は2016年4月から。プロジェクト参加者には1ポンドから1300ポンドまで複数の選択肢が用意されている。

2015.12.07

2015年12月2日、Synopsysは、2015会計年度第4四半期(15年5月-7月)の四半期決算を報告した。

発表によると、Synopsysの2015会計年度Q4の売上は、前年同時期比約8.9%増の5億8720万ドル、純利益は4976万ドルで前年実績の約80%相当だった。

Synopsysの2015会計年度の売上合計は前年比8.9%増の22億4200万ドルで過去最高を更新。純利益は前年比13%減の2億2593万ドルという結果だった。(※GAAP基準による会計結果)

Synopsysが打ち立てた22億4200万ドルという売上額は、EDA業界においても史上最高の実績となるが、それがどの程度の売上規模かというと、IPベンダのARMやFPGAベンダAlteraの売上を上回る規模となる。

Synopsysはこの8月-10月の間に、新製品としてDSP性能を向上させた「DesignWare ARC EMプロセッサ」(

関連ニュース)、Xilinx Virtex UltraScaleを搭載したプロトタイピング・システム「HAPS-80」(

関連ニュース)などを発表している。

Synopsysは次の2015会計年度Q4(15年8月-10月)の売上を5億7000-8500万ドルと予測している。

2015.12.07

2015年11月19日、Mentor Graphicsは、2016会計年度第3四半期(15年8月-10月)の売上を報告した。

発表によると、Mentorの2016会計年度Q3の売上は、前年比約0.8%減の2億9051万ドル、営業利益は前年比13%減の2569万ドルだった。この実績は前Q2実績報告時の予測通りだが、売上額が前年実績を下回るのは2014年Q1(13年2-4月)以来となる。(※GAAP基準による会計結果)

Mentorのチェアマン兼CEOのWalden C. Rhines氏は、半導体業界における事業統合が同社の業績に悪影響を与えているとコメントしているが、その一方で自動車/航空業界においては今後もEDA需要が伸びるとしている。

MentorはこのQ3(8-10月)の間に、高位合成ツールを手掛けるCalypto Design Systemsの買収を発表。新製品としてはテスト圧縮ツール「Tessent ScanPro」や自動車向けの組み込みOS「Mentor® Automotive Connected OS」を発表している。

Mentorは次期2016会計年度Q4(15年11-16年1月)の売上を3億3600万ドル程度と予測している。

2015.11.17

2015年11月16日、Cadenceは新型のエミュレーション・プラットフォーム「Palladium Z1」のリリースを発表した。

Cadenceのエミュレータ「Palladium」シリーズは、同社の検証ソリューションの大きな柱の一つ。今回の新製品「Palladium Z1」においては外寸仕様、性能、機能、ユーザビリティとほぼあらゆる面において改善が図られた。

まず筐体としての仕様が従来の独特な形状から、一般的なサーバー・ラックの縦長な形状に変更された。これにより設置面積は92%改善され、データセンター等への設置も容易になった。水冷式という点は既存製品と同じだ。

Cadenceは「Palladium Z1」に搭載する専用チップの詳細について明らかにしていないため、「Palladium XP2」とのチップの違いは定かではないが、性能面は「Palladium XP2」よりも大きく向上した。

「Palladium Z1」は1ラック当たりのデザイン容量が3億8400万ゲートのXLと5億7600万ゲートのXXLの2種類のラインナップとなっており、「Palladium Z1 XXL」を最大16ラック接続した場合のデザイン容量は92億ゲートとなる。これは市場に存在するエミュレーション環境として最大の規模で既存の「Palladium XP2」の4倍相当、競合製品を大きく上回る。この大規模リソースは400万ゲート単位で利用可能で最大2304人のユーザーが個別のジョブを実行できる。また、ユーザー・メモリ、デバッグ・メモリ共に拡張され1ラック当たり1TBを超えるメモリが搭載されるようになった。

「Palladium Z1」のデザイン・クロックは最大4Mhzと「Palladium XP2」と同等だが、デザインのコンパイル能力が約2倍の1時間当たり1億4000万ゲートに引き上げられるなど、全体的なエミュレーション・スループット効率は最大5倍に向上された。また、エミュレーション・サイクル当たりの消費電力は1/3以下に低減された。

機能面では、まず新たに用意された「Re-Shape」機能により、空いているハードウェア・リソースにジョブを自由にアロケーションできるようになった。これによりリソースを効率良く有効活用可能となる。それからもう一つの新機能「Re-Locate」によりジョブの移動も容易となった。この機能はエミュレーション環境に用意されている各種インタフェースを利用する際にケーブルの抜き差しといった物理的なセッティングを不要とするもので、ユーザーはハードウェアのコンフィギュレーションを気にせずエミュレーションを実行できるようになる。

また、複数ユーザーによる利用に向けてインターネットを通じて「Palladium Z1」にアクセスするための専用端末「Emulation Development Kit(EDK)」が用意されたほか、エミュレーション結果のデバッグ向けにオフラインのデバッグを可能とするデータベース機能「Virtual verification machine」も用意された。これによりエミュレーションの実行は1回、後のデバッグは複数名でオフラインで分担という形の作業が可能となる。

Cadenceはこれら各種機能追加により、エミュレーション環境の運用効率は他社ソリューションよりも2.5倍向上できるとしている。

エミュレーション・ソリューションはCadenceとMentorの大手2社が長くせめぎ合いを続ける分野で、SynopsysもEVE社の買収で参入。最近はS2C社も大規模システムを市場投入しており、大規模先端チップの開発に無くてはならないソリューションとなっている。様々なユースケースと機能的な側面があり、一概に製品の優劣を判断する事は難しいが、そのデザイン容量というのは最もシンプルで分かりやすいエミュレーション環境の重要指標の一つ。今回Cadenceが投入した「Palladium Z1」は、市場の製品の中で飛び抜けた容量を誇るもので、大きな投資を必要とする大手企業向けのソリューションとなるが、ゲート密度や電力効率を考えるとその所有コストに対する費用対効果は大きく、現時点で最高峰のエミュレーション環境と言って間違いないだろう。

新型のエミュレーション・プラットフォーム「Palladium Z1」はこの11月から正式に出荷が開始されており、既にNVIDIA、HUAWEIなど大手をはじめワールドワイドに複数の導入ユーザーが存在しているという。

※日本ケイデンス・デザイン・システムズ社

2015.11.10

2015年11月9日、EDAツールベンダの各社がGLOBAL FOUNDRIESの22nmFDXプロセス向けのリファレンス・フローのサポートを一斉にアナウンスした。

GLOBALFOUNDRIESの22FDXプロセスは、今年の7月に発表されたばかりのFD-SOI(完全空乏型シリコン・オン・インシュレータ)と呼ばれる技術を用いた線幅22nmのプロセスで、GLOBALFOUNDRIESは一般的な28nmプレーナー・プロセスと同等のコストでFinFETの性能と電力効率を実現できるとしている。また22FDXは一般的な28nm技術よりもチップ面積を20%、マスク数を10%削減できるとされており、液浸リソグラフィ層数はFinFETの半分に抑える事ができるという。

※画像はLOBALFOUNDRIESの公開データ

今回22FDXプロセスのリファレンス・フローのサポートを発表したのは、Ansys, ATopTech, Cadence, Mentor Graphics, Synopsysの各社で認証された主要ツールは以下の通り。顔ぶれとしてはTSMCの10nm FinFETで認証されているチームと全く同じだがその中身は若干違う。※関連ニュース

・Ansys:

-スタティック/ダイナミック電圧降下解析ツール「RedHawk」

-エレクトロマイグレーション解析ツール「Totem」の2製品

・ATopTech:

-配置配線ツール「Aprisa」

-フロアプランニング・ツール「Apogee」

・Cadence:

-論理合成ツール「Genus」

-配置配線ツール「Innovus」

-タイミング・サインオフ・ツール「Tempus」

-寄生抽出ツール「Quantus」

・Mentor:

-論理合成ツール「RealTime Designer」

-配置配線ツール「Olympus-SoC」

-フィジカル検証ツール「Caribre」製品群

※「RealTime Designer」は、2013年にMentorが買収したOasys Design Systemsが開発したフィジカル考慮の高速論理合成ツール。大手ファウンドリのリファレンス・フローに登場するのは恐らく今回が初。

・Synopsys:

-論理合成ツール「Design Compiler」

-等価性検証ツール「Formality」

-配置配線ツール「IC Compiler」

-寄生抽出ツール「StarRC」

-タイミング・サインオフ・ツール「PrimeTime」

22FDXプロセスのリファレンス・フロー確立は、先行顧客から一般顧客へのプロセス展開の始動を意味しており、来年後半に予定している22FDXの量産に向けてGLOBALFOUNDRIESは着々と準備を進めているといった様子。22FDXプロセスは独ドレスデンの300mmウエハ・ラインで活用される予定。

2015.11.09

2015年11月5日、Mentor Graphicsは、Altera社のARM搭載FPGA「Arria 10 SoC」のバーチャル・プラットフォームの提供開始を発表した。

発表によると今回提供される「Arria 10 SoC」のバーチャル・プラットフォームは、MentorのWebサイト上からダウンロードする事ができる無償のバイナリで、「Arria 10 SoC」向けソフトウェアの先行開発に利用する事が可能。今年2月に発表されたAlteraとMentorのコラボレーションが実現された格好だ。※関連ニュース

Mentorとしては「Arria 10 SoC」のバーチャル・プラットフォームを無償提供し、それを用いたソフトウェアの開発・デバッグで同社の組込みソフト開発ツール「Mentor Embedded Sourcery CodeBench Virtual Edition」や「Sourcery Analyzer」、バーチャル・プロトタイピング・ツール「Vista Architect」を使ってもらうという腹づもり。「Vista Architect」を利用することでSoC FPGAのカスタム・ロジック部も含めたバーチャル・プラットフォームを構築しハード/ソフトの相互動作をシミュレーションする事が出来るようになる。

なお、MentorとAlteraの取り組みは複数のAltera製品向けに展開される予定で、間もなくIntelの14nm Tri-Gateプロセスで製造される「Stratix 10」のバーチャル・プラットフォームもリリースされる予定となっている。

2015.11.06

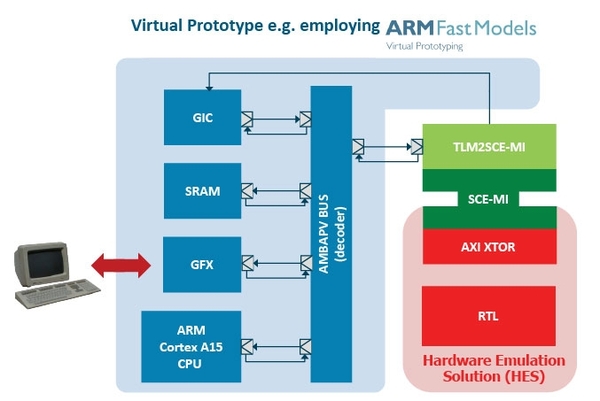

2015年10月27日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のASICプロトタイピング用FPGAボード「HES-7」による「ARM Fast Model」のサポートを発表した。

発表によるとAldecはASICプロトタイピング用FPGAボード「HES-7」にARMの Fast Modelと連携させる機能を用意。具体的には、Aldecの用意する検証用IPを利用する事で、「HES-7」上のFPGAに実装されたハードウェア・ロジックとARMの Fast Modelを連携させる事が可能となる。この検証IPには、SystemC TLMアダプタとエミュレーション用のSCE-MIインタフェースに準拠したバス・ファンクショナル・モデルとトランザクタが含まれており、原理的にはARMのFast Modelに限らず外部のSystemCモデルと「HES-7」を連携できる。

※画像はAldec社Web上のデータ

ARMのFast Modelは、ARMがARMベースSoCのソフトウェア先行開発用に提供するバーチャル・プラットフォーム用のプロセッサ・モデルで、実際のARMプロセッサ相当の最大250MIPSでARMの命令を実行する事が可能。その動作の機能的な正確性はARMが保証している。

昨今、ARMベースのSoC開発においては、ARMプロセッサ・モデルをベースとしたバーチャル・プラットフォームとRTLを実装したエミュレーターを連携させるいわゆるハイブリッド・エミュレーション・システムを利用するケースが増えているが、今回Aldecが発表したソリューションはこれと同等のエミュレーション環境を実現する。

コスト・パフォーマンスが高いAldecの「HES-7」とARMのFast Modelを連携させる事で、ユーザーは比較的低コストでハイブリッド・エミュレーション環境を実現する事が可能となり大きな投資が不要となる。また、「HES-7」とのインタフェースがSCE-MIである点も柔軟性の高さという意味でユーザーに歓迎される事だろう。

AldecはXilinxの最新の20nm FPGA Ultrascale-440を搭載するものと、28nm FPGA Virtex-7 2000Tを搭載するもの等、数種類の「HES-7」を用意している。(FPGA搭載個数は選択可能)

2015.11.05

2015年11月2日、米SIA(Semiconductor Industry Association)は、2015年月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年9月の世界半導体売上は前年同月比2.8%減、前月比1.9%増の284億1000万ドルで3ヶ月連続で前年実績を下回った。

四半期単位で見ると2015年7月-9月のQ3売上は計852億ドルでQ2実績を1.5%上回ったが、前年比では2.8%減だった。

7月以降、世界の半導体売上額は停滞気調に入っており、この1ヶ月の間に調査会社各社やファンドリ大手TSMCなどが今年の半導体売上額の予測値を下方修正している。

・IC Insights 前年比1%増から1%減に下方修正

・Gartner 前年比2.2%増から0.8%減に下方修正

・Semiconductor Intelligence 前年比1.5%増から1.0%増に下方修正

・TSMC 前年比3%増から0%に下方修正

地域別の売上で見ると前年比で売上を大きく落としているのは先月同様欧州および日本市場だが、これは為替レートの変動による影響が大きく、前月比では日欧両市場ともに売上は伸びている。(売上統計はドルベース)

気になるのは最大市場の中国を除くアジア市場と中国に次いで第3位の市場である北米市場で、両市場ともに先月に続いて2ヶ月連続の売上前年割れとなっている。

ちなみに日本市場の直近3ヶ月の平均売上は前の3ヶ月の売上平均に対して4.7%増と先月に続き上が好調に推移。9月の日本市場の売上を円ベースで換算すると前年比約4%増の約3288億円という計算になる。

2015.10.28

2015年10月21日、ARMは、2015会計年度第3四半期(2015年7-9月)の売上を報告した。

ARMの2015年Q3の売上は、前年比約17%増、前期比約5.1%増の3億7550万ドル、税引き前の純利益は約1億9830万ドルで英ポンド・ベースでは前年比約27%増だった。

ARMの2015年度の売上累計額は10億8070万ドルで、現在のところうり前年比17%増の伸びを示している。

ARMのQ3売上の内訳を見ると、プロセッサ・ライセンスの売上は前年比2%の微増、プロセッサ・ロイヤリティの売上は前年比約35%増と大きく伸びた。全売上に対しロイヤリティ売上の占める割合は54%となっている。

Q3におけるプロセッサ・ライセンスの契約数は38件で、最新のARMv8-Aアーキテクチャ・ベースのプロセッサのライセンス契約が6件、GPU Maliのライセンス契約が6件含まれている。またプロセッサ・ライセンスとは別に10nm FinFET process向けのPOP IPのライセンス契約が1件あったという。ライエンス契約の内訳は下記の表の通り。

2015年Q3で出荷されたARM搭載チップの総数は約36億個で前年よりも約20%増えた。

※画像はARM発表資料より抜粋

2015.10.28

2015年10月26日、Cadenceは、2015会計年度第3四半期(2015年7-9月)の売上を報告した。

Cadenceの2015年Q3売上は、前年同時期比約8.5%増、前期Q2比約4.3%増の4億3400万ドルで同社の四半期売上記録を更新。純利益は前年の倍以上の7762万ドルだった。(※GAAP基準による会計結果)

今年Q1は一時的に成長が停滞したCadenceだが、その後Q2,Q3と再び成長軌道に戻り同社の2015年度は過去最高売上を達成する見通し。このような背景も手伝ってか、Cadenceは先ごろGreat Place to Workがまとめる「世界働き甲斐がある会社ベスト25」に選出されている。※プレスリリース文

Cadenceの成長の原動力となっているのは、新しい配置配線ツール「Innovus」やサインオフ・ツール「Tempus」、各種IP製品群などで、「Innovus」や「Tempus」は先端プロセスでの設計においてかなり巻き返しを図っているようだ。

また、CadenceはこのQ3に同社のエミュレーター「Palladium XP」の新規採用事例を2件発表しているが、同社のCEO Lip-Bu Tan氏のコメントによると、Cadenceは次世代のエミュレーション・プラットフォームの出荷を開始したとの事だ。今のところCadenceはエミュレーターの新製品について公式なアナウンスはしていないが、エミュレーターの新製品投入はCadenceの更なる成長を後押しするだろう。

Cadenceは、来期2015年Q4の売上額を4億3400-4400万ドルと予測している。

2015.10.27

2015年10月12日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、新製品の20nm FPGA搭載ボードの出荷開始を発表した。

今回S2Cが出荷を開始したのは、Xilinxの20nm FPGA 「Virtex UltraScale 440 FPGA」を搭載するプロトタイピング・ボード「シングルVU440 Prodigy Logic Module」と、同じくXilinxの20nm FPGA「Kintex UltraScale 115 FPGA」を搭載するプロトタイピング・ボード「クァッドKU115 Prodigy Logic Module」の2製品。

「シングルVU440 Prodigy Logic Module」は、ロジック・セル数440万個のVirtex UltraScaleを1個搭載するプロトタイピング・ボードで、既存の「Virtex-7 2000T」搭載ボード「V7 Prodigy Logic Module」の倍にあたる最大4400万ゲートのデザイン容量と2割増のユーザーI/Oを提供する。この「シングルVU440 Prodigy Logic Module」は、単体での利用の他に最大32個のFPGAを搭載可能な大規模プラットフォーム「Prodigy Cloud Cube」の一部として使用することもできる。※関連ニュース

※画像はシングルVU440 Prodigy Logic Module(S2C社Web上のデータ)

「クァッドKU115 Prodigy Logic Module」は、大規模DSPアルゴリズム開発を目的としたKintex UltraScaleを4個搭載するボードで、ロジック・セル数は約460万(115万×4)、DSPスライス数は約22,000(5500×4)と大容量なDSPリソースを特徴としている。この構成により大規模MESH構造を簡単に作成可能で、「シングルVU440 Prodigy Logic Module」同様、単体のみならずS2Cの大規模プラットフォーム「Prodigy Cloud Cube」の一部として使用することもできる。

※画像はクァッドKU115 Prodigy Logic Module(S2C社Web上のデータ)

FPGAベースのプロトタイピング・ボード市場において先端FPGAの搭載は、自然かつ必須な流れで業界各社がXilinxの最新デバイスを製品に取り込んでいるが、大規模DSPアルゴリズム開発をターゲットにKintex UltraScaleのDSPリソースに着目したS2Cのアプローチは非常にユニークで市場の拡大が期待できる。

なお、S2Cは「シングルVU440 Prodigy Logic Module」、「クァッドKU115 Prodigy Logic Module」の出荷開始と合わせて、近日発表予定のクァッドおよびデュアル「VU440 Prodigy Logic Module」、「シングルKU115 Prodigy Logic Module」の受注を開始している。

2015.10.27

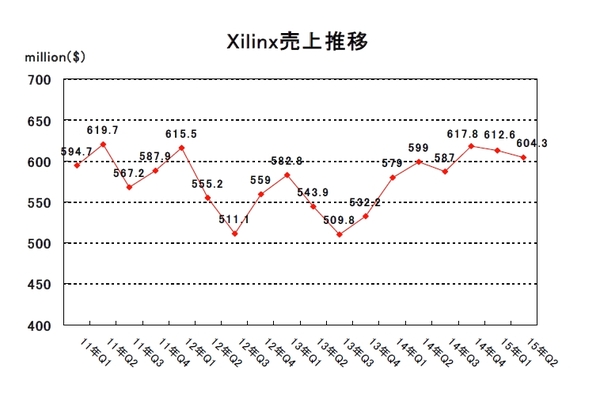

AlteraおよびXilinxの売上推移。(各四半期の売上をカレンダー上のQ1-Q4に対応)

2015.10.27

2015年10月22日、Alteraは2015会計年度第3四半期(15年7-9月)の売上を報告した。

発表によるとAlteraの2015年Q3売上は、前年比約20%減、前期Q2比約4%減の3億9960万ドル、営業利益は前年比約45%減の7776万ドルだった。Alteraの四半期売上が前年実績を下回るのは2四半期連続、前四半期売上実績を下回るのは4四半期連続となる。

Alteraの2015年Q3の売上の内訳を見ると、製品カテゴリ別ではArria 10, Stratix Vをはじめとする主力の新製品カテゴリの売上占有率が伸びた。

アプリケーション別ではテレコム&ワイヤレス向けの売上が回復し、好調なネットワーキング及びコンピューター/ストレージ向け売上と共に売上占有率を伸ばした。

地域別ではアジアおよび欧州市場の売上占有率が伸びている。

2015.10.27

2015年10月14日、Xilinxは2016会計年度第2四半期(2015年7-9月)決算を報告した。

Xilinxの2016会計年度Q2(2015年7-9月)の売上は、前年同時期比約13%減、前期Q4比約4%減の5億2800万ドル。営業利益は前年比23%減の1億5300万ドルだった。(※GAAP基準による会計結果)

四半期ごとの売上額で見るとXilinxは3四半期連続で売上前年割れとなっており、6四半期連続で四半期売上が減少している。

なお、Xilinxによると売上減が続く中、ARM搭載FPGA「Zynq」や20nm FPGA「Ultra Scale」ファミリ製品の売上は好調との事。XilinxはこのQ2において、TSMC16nm FinFET+プロセスで製造される最新の16nm FPGA「Zynq® UltraScale+™ MPSoC」を予定を3ヶ月前倒しして出荷開始している。

また、このQ2においてXilinxはQualcommとQualcommのサーバー向け事業に関するコラボレーションを発表している。

XilinxのQ2売上を地域別に見ると、前四半期よりもアジア市場の売上占有率が伸びている。

アプリケーション別では、主力の通信およびデータセンター向けの売上占有率が伸び、産業、航空、軍事向け売上占有率が減少している。

製品別では新製品カテゴリ(Virtex® UltraScale™, Kintex® UltraScale, Virtex-7, Kintex7, Artix®-7, Zynq®-7000, Spartan®6)の売上占有率が大きく伸び43%に達した。

Xilinxは、次期2016年Q3(15年10-12月)の売上は3-7%上昇すると予測をしている。

2015.10.21

2015年10月21日、ARMはウェアラブルおよびIoTデバイス向けの新GPUコア「ARM Mali-470」のリリースを発表した。

発表によると新たなGPUコア「ARM Mali-470」は、既存の小型GPU「Mali-400」よりも10%少面積で消費電力は半分、エネルギー効率は2倍、OpenGL ES 2.0に準拠しており、「Mali-400」同様コアは1コアから4コアまで拡張可能となっている。

ARMによると「Mali-400」を用いたSoCの出荷数は既に10億以上に達しており、「Mali-470」は「Mali-400」の市場を更に拡張する新たな超低消費電力コアとして、スマート・ウォッチやヘルスケア・モニタ、家電、ホーム・ゲートウェイ、産業用の制御パネルなどの用途に向けて投入される。「Mali-470」の搭載製品は2016年後半に市場に登場する予定。

2015.10.21

2015年10月21日、ARMはESLツールを手掛けるCarbon Design Systemsから製品および事業資産を買収した事を発表した。

今回の買収に関する取引条件は明らかにされていないが、事業の買収に伴いCarbonの従業員はARMに移籍する様子。

Carbonは2002年にボストンで設立されたEDAベンダで、RTLから高速なサイクル精度のシミュレーションモデルを生成する「Carbon Model Studio」と2008年にARMから買収したバーチャル・プロトタイピング・ツール「Carbon SoCDesigner+」、そしてバーチャル・プロトタイピング用の各種モデルを提供するクラウド・インフラ「Carbon IP Exchange」を提供していた。

Carbonのうりは「100% Cycle Accurateな仮想化環境」で、密接な関係にあるARMをはじめ、Imagination Technologies, CEVA, Cadence, Arteris, DMP, VeriSiliconなど業界IPベンダ各社のモデルを豊富に揃え、ARMベースSoCの開発環境としてサムスンなど大手にも活用されている。これらCarbonの提供するモデル群は将来的に「ARM Cycle Model」として「ARM IP Exchange」上で提供される予定となっている。

ARMは昨年もシステムレベルのSoC設計ツールを手掛けるDuolog Technologiesを買収しており、今回のCarbonからの事業買収も含め、システムレベルの開発環境の拡充を図っている。※関連ニュース

2015.10.13

(株)半導体理工学研究センター(STARC)は、2015年11月27日(金)に新横浜国際ホテル南館にて、「STARCフォーラム2015」を開催致します。

今回のフォーラムでは、前回のシンポジウム(2015年1月開催)のテーマである"IoT"からさらに将来にわたって高度情報化社会の礎となる"人工知能"をテーマとして取上げました。2030年に向けての未来予測、そして"知のコンピューティング"、そして人工知能の情報処理を加速するハードウェア技術に関する講演で、このテーマについてのプログラムを構成しました。さらに、これからの研究開発コンソーシアムの展望についての講演も組み入れました。

また、恒例となっております、学生ショートプレゼンテーション、ポスターセッションも行います。学生たちのフレッシュで情熱に溢れた研究の息吹を感じ取って頂ければと思います。

レセプションも準備しておりますので、歓談・懇親を楽しみ、深めて頂ければと思います。 参加は無料です。下記URLにてご案内および事前登録ができます。

多数のご参加をお待ちしております。

http://www.starc.jp/cd_event/forum2015/

2015.10.11 (株)半導体理工学研究センター

2015.10.09

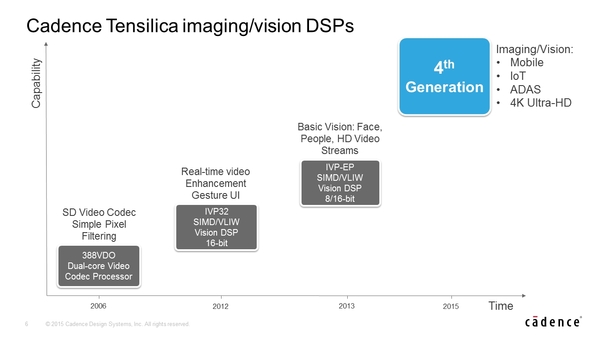

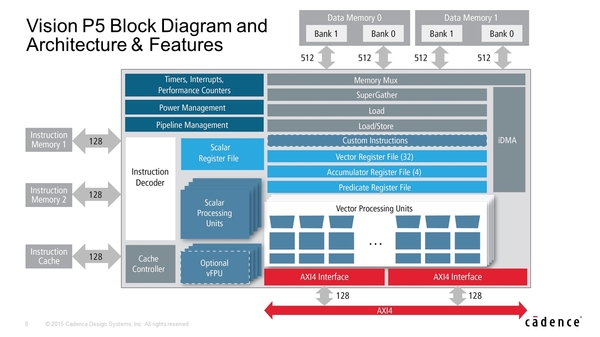

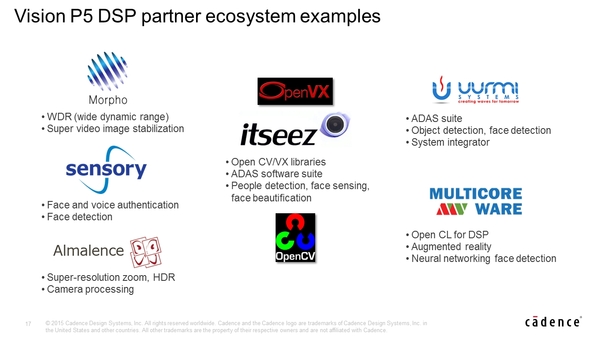

2015年10月7日、Cadenceは同社最新のDSPコア「Tensilica Vision P5 DSP」のリリースを発表した。

Cadenceによると新製品「Tensilica Vision P5 DSP」は、既存のDSPコア「IVP-EP」と後方互換の後継製品でTensilicaのイメージ/ビデオ向けDSPとしては4世代目にあたる製品。その名の通り各種ビジョン・アプリケーションをターゲットとしている。

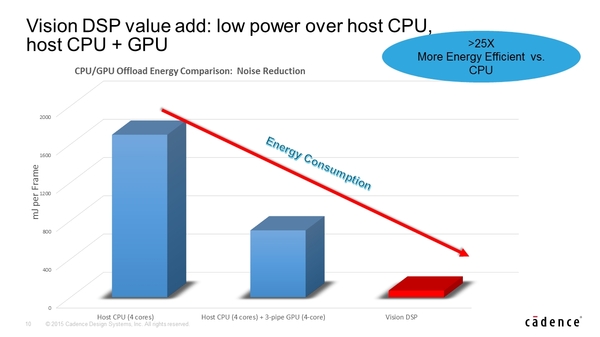

従来品と大きく違うのはそのパフォーマンスと消費電力で、「Tensilica Vision P5 DSP」は既存の「IVP-EP」よりもパフォーマンスが最大13倍にまで向上されており、16nm FinFETプロセスでの実装では動作周波数が最大1.1GHzに達する。消費電力も従来製品比で平均1/5と大きく電力効率が高められており、これら機能強化により、モバイル機器に加えてADASやドローン、セキュリティ・カメラなどの先進のビジョン・タスクにも対応可能となる。また、従来ハード処理していた部分やGPUで処理していた部分をDSPで置き換える事も可能となる。当然ながらDSPを利用すればプログラマブルに、そして低消費電力で処理できる。

「Tensilica Vision P5 DSP」の優れたパフォーマンスには幾つかの仕掛けがある。

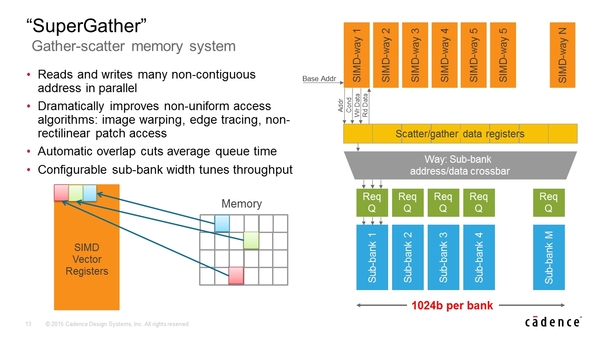

まず、16way単精度の32-bit Vector Floating-Point Unitがオプションで用意された。これはTensilicaの他のコアで培われた技術で、これによりGPUコードのポーティングも容易になった。また、「SuperGather」技術と呼ばれるメモリアクセス向上技術が取り入れられ、業界最大の1024-bitのメモリ帯域幅を更に活かせるようになった。更にISPへの接続も視野にAXI4バスのインタフェースが2チャンネルとなった。片方はHost用としての利用を想定している。その他、DSPコア全体としては命令セットの強化も進められ、更に400以上の命令が追加されている。

電力効率の向上は「Tensilica Vision P5 DSP」の大きなメリットだが、Cadenceの実例によると、ノイズ・リダクションをCortex-A9のクアッドコアCPUで実行する場合と、それにGPU(3-Pipe,4Core)と「Tensilica Vision P5 DSP」を追加した場合とでは、電力効率において25倍もの性能差が生じるとの事。一部先行顧客は「Tensilica Vision P5 DSP」の電力効率を活かし、サーバー向けの利用に取り組んでいるという話だ。

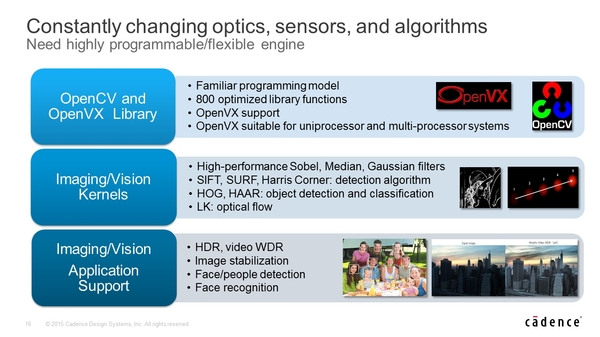

なお、Cadenceはソフトウェア面の対応として、「Tensilica Vision P5 DSP」の命令セットに最適化したOpenCV/OpenVXのライブラリ約800種を無償提供するほか、イメージ/ビジョン向けのより粒度の細かいカーネル・ライブラリも用意。また人体検出や顔認識などの内製アプリケーションも用意されている。その他各種サードパーティーによるアプリケーションのポーティングも既に進められているという。

※画像は全てCadence提供のデータ

「Tensilica Vision P5 DSP」は既に出荷が開始されており、間もなくESが出てくる先行顧客もいるという話だ。

2015.10.07

2015年10月5日、米SIA(Semiconductor Industry Association)は、2015年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年8月の世界半導体売上は前年同月比3%減、前月比0.6%減の277億3000万ドルと前年比、前月比ともに売上減少を記録した。世界半導体市場は7月に7年ぶりに売上が前年実績を下回ったが8月も前年割れとなりその減少幅は拡大している。売上が前月実績を下回るのは6月以降3ヶ月連続。

地域別の売上で見ると前年比で売上を大きく落としているのは欧州および日本市場だが、これは為替レートの変動による影響が大きく、前月比では日本市場の売上は伸びている。(売上統計はドルベース)

その他の地域についてはここ数ヶ月の間、前年比、前月比ともに売上の増減を繰り返しており際立った傾向は見えないが、直近3ヶ月の平均売上を見ると中国を除くアジア市場の売上が減少傾向であることが分かる。

ちなみに日本市場の直近3ヶ月の平均売上は前の3ヶ月の売上平均に対して5.2%増と地域別では最も売上が好調。8月の日本市場の売上を円ベースで換算すると前年比約4%増の約3290億円という計算になる。

2015年の半導体市場は上半期は前年比3.9%の成長を達成しているが、下半期に関しては合計売上で前年実績を維持できるかどうかという水準になりそうだ。

2015.10.05

2015年10月2日、新横浜のホテルで今回が2回目となるセミナー「Design Solution Forum 2015(以下DSF2015)」が開催された。

今年のDSF2015は、セッション数、参加スポンサー数、申込み人数ともに昨年を上回る規模で、会場には500名を上回る参加者が集まった。

セミナーでは昨年と同じ4つの講演トラックで40セッション、2つの特別企画トラックと展示会場で5セッションの計45セッションが実施され、セミナー終了後には展示会場にて交流会が行われた。

ここではフォト・レポートとして、Design Solution Forum 2015の様子をお届けします。

セミナーは昨年に続き同イベントの実行委員長を務めた京セラドキュメントソリューションズ株式会社岡田 充弘氏の挨拶でスタート。

基調講演は元エルピーダメモリ社長で現在ウィンコンサルタント株式会社の代表取締役である坂本 幸雄氏。日米の企業文化の差を軸に世間を賑わせた東芝問題なども取り上げ、日本半導体業界の今後の生きる道、そしてエンジニアの生きる道について語ってくれた。(※坂本氏の講演については別途レポート予定)

設計現場のエンジニアによるエンジニア・セッションの人気投票で断トツの1位となり、最優秀講演賞を受賞したのは、ブログ「FPGAの部屋」で業界では有名な筑波大学の小野 雅晃氏。同氏の講演は立ち見が出るほどだった。

スポンサー講演部門で人気投票1位に輝いたのは、CMエンジニアリング株式会社の斎藤 早苗氏と株式会社ネクストリームの川原 常盛氏。両氏は同率首位という事でともに最優秀スポンサー講演賞を獲得した。ちなみにCMエンジニアリング社は昨年の二見氏に続いて最優秀スポンサー講演賞2連覇となる。

※上の画像がCMエンジニアリング斉藤氏、下の画像がネクストリーム川原氏の講演風景

展示会場で実施されたトーク・セッションは、昨年に続いての人気企画。フォーマル検証とプロトタイピングをテーマに2つのセッションが行われ、DSF2015の実行委員長である岡田 充弘氏と実行副委員長である株式会社リコー木村 貞弘氏がそれぞれモデレータを務めた。

※画像上段がフォーマル検証トーク、下段がプロトタイピングトークの風景

特別ディスカッションとして企画された、高位合成をディスカッションする会、DSF検証研究会、高位合成チュートリアルの3セッションは、参加希望者多数で早々に申込み終了となり、当日はそれぞれ20名近くの参加者でテーマに沿った議論が行われた。これら各セッションの内容は原則非公開なので、モデレータによる個別のレポートに期待したい。

システムレベル設計に関する講演が多かったDesignトラックでは、公募による講演の他に特別招待講演としてIP500アライアンス日本代表の豊崎 禎久氏による講演も行われた。

※画像左上:ニコン松本矩尚氏の講演風景、右上:京セラ北村哲朗氏、左下:パソナテック佐々木誠氏、右下:レガートデザインコーポレーション高本博文氏

※画像はIP500アライアンスの豊崎禎久氏と豊崎氏の講演風景

検証に特化したVerificationトラックでは、協調検証、FPGA、ソフトウェア開発、IoT、機能安全など、多種多様な切り口からの講演が繰り広げられた。

※画像左上:リコー守田直也氏の講演風景、右上:富士ゼロックス三角氏の講演風景、左下:Open-Silicon社Devendra Godbole

氏、右下:東芝マイクロエレクトロニクス森誉浩氏

全ての最優秀講演賞を輩出したSoft & FPGAトラックは、事前申込み数が昨年よりも多く、受賞講演以外の講演も総じて人気が高かった。

※画像左上:京都マイクロコンピュータ若槻俊宏氏、右上:日本シノプシス井上栄理氏、左下:東京工業大学荒堀喜貴氏の講演風景、右下:イーソル権藤正樹氏

Solutionトラックでは昨年同様IPを軸とした講演が複数行われたほか、設計メソドロジやマネジメントなど広い視点から設計・検証を考える話もあった。

※画像左上:立命館大学谷口一徹氏、右上:セレブレクス鈴木眞也氏、左下:コニカミノルタ河邊恭氏、右下:東京工業大学一色剛氏

セミナー終了後の大交流会には殆どの講演者が参加。昨年以上の賑わいだった。

Design Solution Forumは、来年も引き続き開催される予定。

2015.09.30

2015年9月28日、米EDA Consortiumは、2015年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

EDACの発表によると2015年Q2(4-6月)の世界のEDA売上総額は、前年比8.5%増、前Q1比1.6%増の19億650万ドルで、Q2の売上として過去最高を記録した。四半期の売上記録が前年同時期を上回るのはこれで21四半期連続となる。

2015年Q2のEDA売上を製品分野別に見るとIP分野が成長を続けており前年比15%増。IP分野はここのところ6四半期連続で前年比2ケタ増を達成しており、このままのペースでいくと最大のCAE分野を上回る売上になりそうだ。CAE分野は四半期によりバラつきがあるものの、Q2では前年比9.6%増と好調だった。

2015年Q2のEDA売上を地域別に見ると、最大市場の北米と2番手のアジア市場が好調を維持。欧州も前年比増を達成し売上3億ドル台に戻した。日本市場はドルベースでは前年比3.4%減となっているが、円ベースでみると前年比約15%近くの売上増という結果となっている。

2015年Q2時点でのEDA業界の従業員数は前年比4.9%増の32806人で過去最高を記録した。

2015Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億5720万ドル 9.6%Up

■IC Physical Design & Verification分野 3億7920万ドル 6.0%Up

■IP分野 6億1170万ドル 15.0%Up

■サービス分野 1億310万ドル 14.7%Up

■PCB/MCM分野 1億5530万ドル 13.0%Down

2015年Q2の地域別の売上と昨年同時期との比較は以下の通り。

■北米 8億7030万ドル 9.5%Up

■ヨーロッパ 3億540万ドル 5.2%Up

■日本 1億8280万ドル 3.4%Down

■アジアその他地域 5億4810万ドル 13.2%Up

※EDAC(EDA Consortium)

2015.09.22

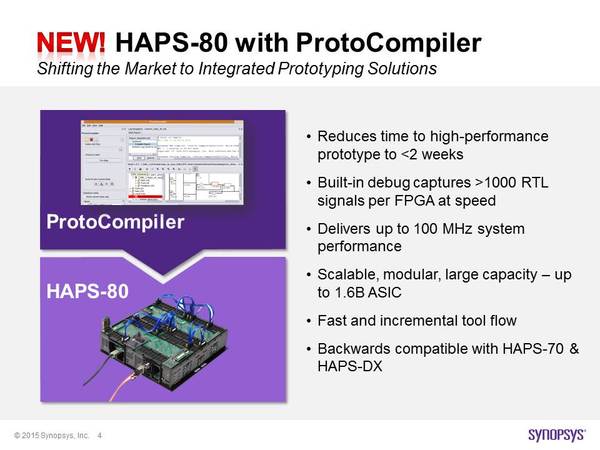

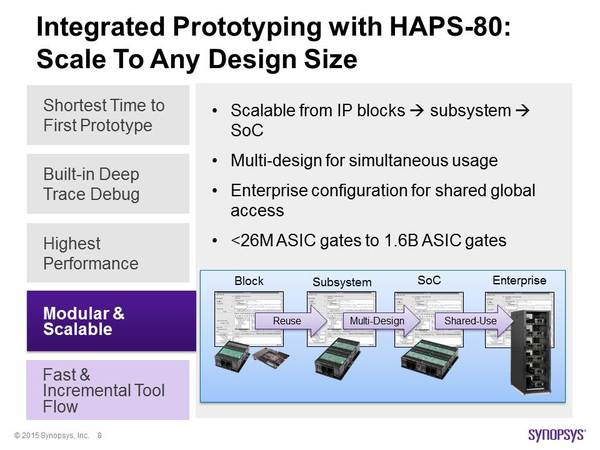

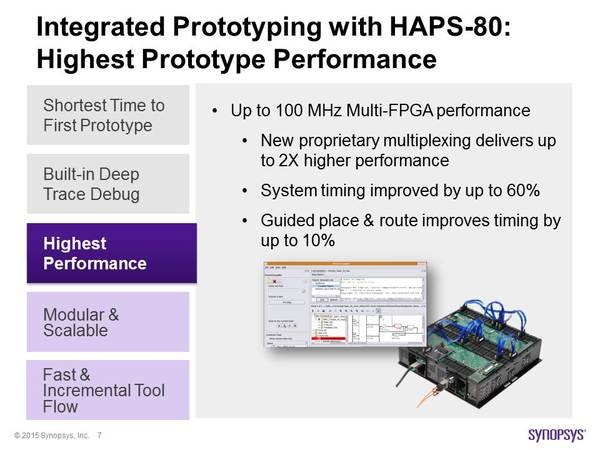

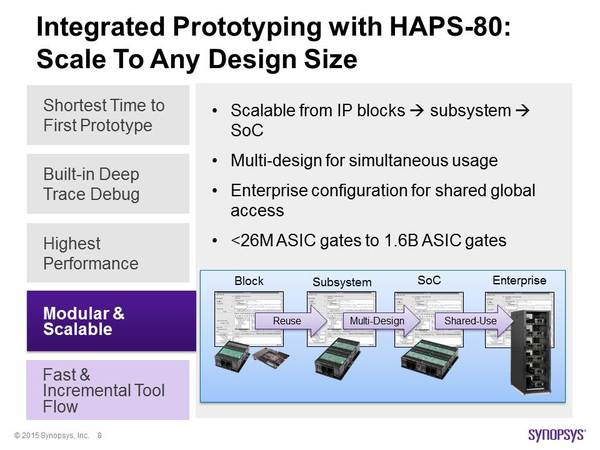

2015年9月17日、Synopsysは同社のFPGAベース・プロトタイピング・システムの新製品「HAPS-80」のリリースを発表した。

Synopsysによると新型の「HAPS-80」には、Xilinx社の20nm FPGA「Virtex UltraScale VU440」が搭載されており、最小構成のシステムで2600万ASICゲート、最大構成のシステムでは16億ASICゲートのデザインを実装する事ができる。

Xilinxの先端FPGA「Virtex UltraScale VU440」の搭載は、業界において必然的な流れであり、既にAldec,ProDesign,S2Cといった各社が「Virtex UltraScale VU440」を搭載したFPGAベース・プロトタイピング・システムの提供を開始している。

しかし、今回の「HAPS-80」で着目したいのがその最大デザイン容量だ。最大16億ASICゲートとなると、FPGAの個数からしてかなり巨大なボード積層システムになると思われるが、どうやらSynopsysはHAPS用の大型の筐体(ラック)を用意しているようだ。更に「HAPS-80」ではイーサネット接続によるリモート・アクセスが可能となり、「HAPS-80」のリソースを複数の拠点、複数のデザインでシェアしながら効率的に利用できるようになったという事である。こういった大容量のプロトタイピング環境を複数ユーザーで遠隔利用するアプローチは、HAPSの競合であるS2C社も取り組みを進めており、次世代のFPGAベース・プロトタイピング環境の大きな流れになりそうだ。

また「HAPS-80」は、昨年リリースされたHAPS向けの新たなソフトウェア環境「ProtoCompiler」によって、デザインのFPGA実装時間、システム性能ともに高速化された。

「ProtoCompiler」はデザインの自動分割実装およびデバッグのためのツールで、2億5000万ASICゲートのデザインを僅か数分で自動分割する事が可能。RTLのコンパイル時間を大幅に短縮できるなどの効果により、プロトタイプ作成までにかかる期間を平均2週間以下に短縮出来るようになったという話である。

また「ProtoCompiler」を用いることでプロトタイプのシステム性能も大きく向上。「ProtoCompiler」は、新たに改良されたFPGA間通信多重化技術「HSTDM」を活用して、HAPSのハードウェア・アーキテクチャを考慮したマルチプレクシングの自動インプリメントを実行可能で、最大30Mhzのシステム性能を実現。ピン・マルチプレキシングを行わない複数FPGAへのデザイン分割では最大100MHzのシステム性能を実現できるという。

※画像は全てSynopsys提供のデータ

更に新しい「HAPS-80」ではデバッグ機能も強化された。

「HAPS-80」には、デバッグ信号データ抽出機能、デバッグ信号データ格納メモリー、デバッグ専用回路の自動挿入機能が組み込まれており、「HAPS Deep Trace Debug Gen4(DTD4)」と呼ばれるデバッグ技術によって、1つのFPGAあたり1000以上の信号をアットスピードでキャプチャする事が可能。これらデバッグ機能はSynopsysのデバッグ・ツール「Verdi」と統合されており、複雑なデザイン動作をシミュレータ・ライクに短時間で可視化できるため、デバッグ時間を最大50%短縮できるという。

このように今回リリースが発表された

新しい「HAPS-80」は、単にFPGAが最新の20nmチップに置き換えられただけでなく、プロトタイプの運用性、システム性能、デバッグ性能など、プロトタイピング環境における重要ポイント全てが刷新され更に強力なソリューションとなった。

なお、「HAPS-80」は一世代前の「HAPS-70」との下位互換を維持しており、これまで「HAPS-70」で使用していたシステムやドーター・ボードなどのハードウェア部品を「HAPS-80」で再利用することが可能。「HAPS-80」は既に製品として出荷が開始されている。

2015.09.17

2015年9月16日、Mentor Graphicsは、Calypto Design Systemsを買収した事を発表した。

発表によると、Calypto Design Systemsは一つの独立したビジネスユニットとしてMentorにマージされ、そのマネージャーにはAxiom Design AutomationおよびFrontline Design AutomationのCEOを歴任したBadru Agarwala氏が就任するとの事。今回の買収に関する取引額などの詳細は明らかにされていない。

Calyptoは2011年に当時Mentorが提供していた高位合成ツール「Catapult C Synthesis」を買収。その際にMentorからの資本が入り、MentorはCalyptoの株式の過半数を所有する親会社となっていた。

Calyptoの提供するソリューションは高位合成ツール「Catapult」とパワー最適化ツールの「PowerPro」、そして等価性検証ツールの「SLEC」の大きく3つ。元々は独自のシーケンシャル・アナリシス技術を武器に「SLEC」でEDA市場に参入し、その技術を活かした「PowerPro」で業界における地位を固め、Mentorから「Catapult」を手に入れ更に事業を拡大していた。

高位合成ツールにしてもパワー最適化ツールにしても、Calyptoのかつての競合/同業企業は殆ど大手EDAベンダに買収されてしまっており(Forte,Synfora,AutoESL,Atrenta,Sequence Designなど)、Calyptoは同分野で唯一気を吐く中堅EDAベンダだった。EDA市場に残る大手以外の高位合成ツールはNECの「Cyber Work Bench」だけである。

ちなみに明日9/18に新横浜でCalypto User Forumが開催される予定。

2015.09.15

2015年9月10日、Synopsysは同社の「ARC EM DSP」ファミリの新製品「ARC EM9D」と「ARC EM11D」の2品種を発表した。

「ARC EM DSP」ファミリは、IoT機器など組込みデバイスのDSPアプリケーション向けに開発された超ローパワーDSPコアで、Synopsysは昨年6月に「ARC EM5D」、「ARC EM7D」の2品種を市場投入している。

今回発表した「ARC EM9D」と「ARC EM11D」は既存製品に続く上位製品で、新たな「XYメモリー」のサポートにより、既存のEMコア比で3倍もしくはそれ以上のDSP性能を超ローパワーで実現する。「XYメモリー」は、プロセッサ・パイプラインと密結合されたメモリーで、システム・メモリーへのアクセスを削減し、プロセッシング・スループットを最大化できる。

※ARC EM9/11Dのブロック図 Synopsys Webサイト上の画像

※ARC XYmemoryのブロック図 Synopsys Webサイト上の画像

Synopsysのデータによると新しい「ARC EM9D/11D」のパフォーマンスは、最高で1.77 DMIPS/MHzおよび3.41 CoreMark/MHzという値。チップの実装面積は不明だが、28nmプロセスで実装した「EM9D」で4411kHz、128kbpsでMP3データをデコードする際の消費電力は、40マイクロ・ワット以下だという。

またSynopsysはコアそのもののエンハンスと合わせてエコシステムも拡張しており、ARC プロセッサ向けソフトウェアの開発パッケージ「ARC MetaWare Development Toolkit」において「ARC EM9D」と「ARC EM11D」に対応するXYメモリーを活用するためにアルゴリズムを最適化する新機能を追加した。

SynopsysはARMに次ぐ世界2位のIPベンダとして各分野のIP製品展開を積極的に進めているが、ARCコアはその中核をなすIPの一つ。中でもIoT向けの小型ローパワーDSPコアは今後の市場拡大が見込める分野であるため、この分野で強いCadence Tensilicaコアのシェアを切り崩すべく積極的な投資を進めている。

2015.09.14

2015年8月10日、各種検証ソリューションを手掛けるAldecは、CDC検証ツール「ALINT-PRO-CDC」のバージョンアップを発表した。

発表によると今回のバージョンアップでは、スタティック検証のルール・セットが新たに10個追加されたほか、違反解析手法も強化された。また、ダイナミック検証においては、ハンドシェイク・シンクロナイザが新たにサポートされ、アサーションとカバレッジ、メタステーブルのエミュレーションも生成可能となった。既存のリセット・シンクロナイザにおいてもアサーションとカバレッジの生成、メタステーブルのエミュレーションが可能という事だ。更にダイナミック検証では、テストベンチ生成言語としてVHDLがサポートされている。

※スタティック違反解析のハイライト機能

※画像は全てAldec提供のデータ

2015.09.11

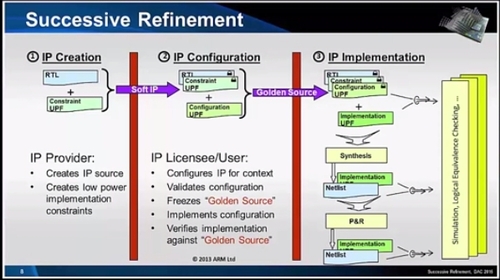

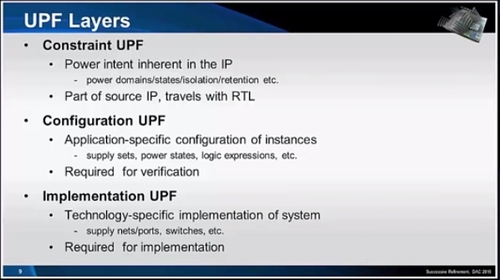

2015年9月10日、Mentor Graphicsは、同社のローパワー検証ツールがUPF Successive Refinement Methodologyをサポートした事を発表した。

UPF Successive Refinement Methodologyとは、パワー仕様記述フォーマットUPFを用いたローパワー設計のためのメソドロジで、ローパワー設計におけるUPFの利用価値をこれまで以上に高めるもの。同メソドロジはIEEE1801 UPF仕様の主査であるARMのエンジニアが提唱したもので、Mentorと共にその実現に向けて取り組んできたとの事。

その思想には、IPベンダの提供するUPFをIPユーザーがターゲット・アプリケーションやターゲット・デバイスに応じて詳細化して利用するという考えが込められており、UPFをIP/ブロック用の制約UPF、検証用のコンフィギュレーションUPF、実装用UPFの3種類に分けて設計工程に合わせて作りこみながら利用する。これによりUPF利用者の立場とターゲットに応じたより価値の高いローパワー検証をより効率的に実践できるようになる。

※画像はMentor社Web公開ビデオからの抜粋

Mentorは今回このUPF Successive Refinement Methodologyを「Questa® Power Aware Simulation」および「Visualizer Debug Environment」にてサポート。同メソドロジを用いたローパワー検証フローの加速と自動化を実現するとしている。

UPF Successive Refinement Methodologyの詳細については、Mentorが下記URLにてDAC2015での解説ビデオを無償公開している。

http://www.mentor.com/products/fv/resources/overview/successive-refinement-a-methodology-for-incremental-specification-of-power-intent-using-upf-2a5e8c03-f46c-4d78-b108-d143cb3a0073

2015.09.10

EDA上位3社Cadence,Mentor Graphics,Synopsysの売上推移グラフです。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

直近四半期の各社の売上は以下の通り。

2015.09.10

2015年9月9日、Cadence,Mentor Graphics,Breker Verification SystemsのEDA3社がEDA関連標準化団体Accelleraへの技術貢献を発表した。

発表によると3社は、単一記述から複数のターゲットに対するスティミュラスとテストを自動生成可能な新たな標準仕様言語の開発に取り組んでいるAccelleraの「Portable Stimulus Working Group」に対して技術貢献しており、同WGの目指す仕様言語の策定を加速している。この新たな仕様言語が実現するとシミュレーション、エミュレーション、FPGA、ポストシリコンなど複数の実装ごとにスティミラスやテストを個別に一から用意する必要が無くなり、SoC開発における各開発フェーズのテストの一貫性やテスト全体の効率性が高まる。

2015.09.10

2015年8月25日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けのEDAツールを手掛けるSilvacoの日本法人シルバコ・ジャパンは、国立研究開発法人 産業技術総合研究所の先進パワーエレクトロニクス研究センターが同社のTCADツールを採用した事を発表した。

発表によると産総研は今回SiCパワー半導体の研究にSilvacoのTCADを採用。産総研ではSiCデバイスの他に複数のパワーデバイス関連の大型研究プロジェクトを進めている。

TCADの市場は長年SilvacoとSynopsysの両社が独占しており、Silvacoの方が会社の規模では圧倒的に小さいながらも頑張っている状況。その技術面だけでなく、サポート面でも顧客から高い評価を得ていると聞く。

SilvacoはTCADの他にPDKやアナログ/ミックスド・シグナル/RF設計向けツールなども主力製品として提供しており、今年3月にはPower-Voltage-Thermal解析ツールのInvarianを買収。今後はパワー・サインオフも新たなソリューションとして積極的に展開していく様子である。

2015.09.07

来る2015年10月2日(金)、エンジニアによるエンジニアのための技術セミナー「Design Solution Forum2015」が開催されます。

Design Solution Forumは、昨年スタートしたハードウェア(論理)設計者、組み込みソフトウェア開発者らが集う国内最大級の技術セミナーで、2回目の開催となる今年のDSF2015は、昨年を上回る規模のスポンサー企業数、セッション数となっています。(DSF2015タイムテーブル詳細)

エレクトロニクス業界の技術情報の収集とエンジニアとの交流の場として、是非この機会にDesign Solution Forum 2015に足をお運び下さい。

【今年の見所】

・基調講演:元エルピーダメモリ 坂本幸雄氏「次に生き残る半導体メーカーは」

・特別講演:IP500アライアンス 豊崎禎久氏「IoT未来社会インフラを築くIoT3.0未来戦略」

・時間拡大!2つのトーク・セッション

-フォーマル検証トーク「フォーマル検証に対する理想と現実」

-プロトタイピング開発トーク「VirtualとRealの狭間を垣間見る」

・エンジニア同士の本音の議論!特別セッション

-高位合成をディスカッションする会「高位合成で何をするか?どうすればいいのか?」

-DSF検証研究会「検証ってナンだ?」

・全45セッション(※受講お申し込み先着順)

※参加無料!(昼食・レセプションパーティーをご用意)

※セミナー聴講登録は今すぐ!→http://dsforum.jp/2015/index.html

-------------------------------------------------------------------------------

■セミナー開催概要

会期:2015年10月2日(金)

9:00-17:15(セミナー)、17:35-19:30(パーティー)

会場:新横浜国際ホテル 南館 〒 222-0033 横浜市港北区新横浜 3-18-1

※会場へのアクセス→http://sinyokohama.khgrp.co.jp/info/access.html

参加:無料(昼食付、事前登録制)

※セミナーのお申し込みにあたり、「お申し込みにともなう個人情報の取

扱い」に同意いただく必要がございます

主催: Design Solution Forum 2015 実行委員会

一般社団法人日本エレクトロニクスショー協会

スポンサー:(アルファベット順)

アルチップ・テクノロジーズ(株)

アルデック・ジャパン(株)

日本アルテラ(株)

アーム(株)

Australian Semiconductor Technology Company(株)

Blue Pearl Software

日本ケイデンス・デザイン・システムズ社

CMエンジニアリング(株)

コーダシップ社

サイバネットシステム(株)

DOCEA POWER

ファラデーテクノロジー日本(株)

イマジネーションテクノロジーズ(株)

(株)インターバディ

日本シーバ(株)

日本シノプシス合同会社

OneSpin Solutions Japan K.K.

Open-Silicon Japan(株)

(株)パソナテック

日本リアルインテント(株)

S2Cジャパン(株)

Silexica Softwave Solutions GMBH

東芝情報システム(株)

ベンザテクノロジー(株)

ベリフィケーションテクノロジー(株)

(株)ベリフォア

ザイリンクス(株)

(株)ジィーサス

企画:株式会社EDAエクスプレス

株式会社ネクストリーム

※セミナー公式Webページはこちら

http://dsforum.jp/2015/index.html

━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━

2015.09.07

2015年9月4日、検証IPにフォーカスしたインドのIPベンダSmartDV Technologies社は、京セラドキュメントソリューションズ社が同社のAMBA検証IPスイートを採用した事を発表した。

発表によると京セラドキュメントソリューションズは、SmartDVの提供するAMBA AHB、APB3、APB4、AXI3、AXI4の検証IPを世界の開発拠点で採用。これまでは自社開発のAMBAモデルを用いていたが、コスト、リソース、更なる品質改善という観点からSmartDVの検証IPの利用へと移行した。

SmartDVは2014年にDACデビューを果たした新興のIPベンダで、その検証IPラインナップの豊富さとパフォーマンス(速さ)、そして価格の安さをウリにしている。また、SmartDVは独自の開発言語を用いて検証IPを開発しており、元となるソースから顧客のカスタム要求に対応したSystemVerilog,Verilog,SystemCの各種IPを自動生成して製品として販売しているため、顧客の検証環境に合った検証IPを迅速に提供する事が可能。もちろん標準的なUVM,VMM,OVMといった検証メソドロジは一通りサポートしている。

※SmartDV社製品に関するお問い合わせ先:kawahara@nextream.bz

2015.09.07

2015年9月3日、米SIA(Semiconductor Industry Association)は、2015年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年7月の世界半導体売上は前年同月比0.9%減、前月比0.4%減の278億8000万ドルと前年比、前月比ともに売上減少を記録した。売上が前年実績を下回るのは実に7年ぶり。売上が前月実績を下回るのは2ヶ月連続となる。

前年比で見ると売上が大きく減少しているのは欧州および日本市場で、これは為替レートの変動による影響が大きい。(売上統計はドルベース)前月比では欧州も日本も売上は伸びており、逆に売上を落としているアジアや北米市場となっている。ちなみに日本市場の売上はドルベースでは前月比2.7%増の売上26.4億ドルとなっているが、円ベースでは前年比約23%増の約3250億円という計算になる。

2015年の半導体市場は年初時点では概ね前年比数パーセント増と予測されており、上半期としては前年比3.9%の成長を達成したが、7月以降の下半期が前年水準を保てるかどうかは微妙な様相となってきた。

今回発表された7月の売上統計には中国ショックと呼ばれる中国に端を発した世界経済の動揺が未だ反映されておらず、半導体の世界最大の消費国が中国である事を考えると今後の半導体市場の冷え込み具合が気になる。

※SIA

2015.08.26

IntelおよびDocea Powerからのプレス発表は行われていないが、今年7月31日にIntelによるDocea Power社の買収が完了したとDocea Power社のWebサイトに掲載されている。

両社の取引条件に関する詳細は不明だが、Intelは買収したDocea Power社の製品販売を継続する見通し。Intelは数年前にもESLツールを手掛ける仏CoFluent社を買収したが、自社製品の開発に利用するだけでなく社外販売も継続している。

Docea Power社は、システムレベルで高速かつ正確に熱および消費電力の解析を行う「Aceplorer」と「Thermal Profiler」を提供していた。これらツールはIntelのアーキテクチャ探索ツール「CoFluent Studio」との連携も可能。また、「CoFluent Studio」はIntel配下のWindRiverが提供するシステムレベルのシミュレータ「Simics」とも連携しているため、各ツールを連携させた新たなソリューションが生まれる可能性がある。

2015.08.25

2015年8月20日、Mentor Graphicsは、2016会計年度第2四半期(15年5月-7月)の売上を報告した。

発表によると、Mentorの2016会計年度Q2の売上は、前年比約8%増の2億8110万ドル、営業利益は前年比123%増の3926万ドルだった。この実績は前Q1実績報告時の予測を大きく上回るものでQ2売上としては過去最高の数字だった。(※GAAP基準による会計結果)

売上好調の要因は設計および検証、両ソリューションにおいて強い需要があったためで、エミュレーターはこのQ2で5社の新規顧客を獲得したという。

MentorはこのQ2(5-7月)にEDAソリューションとしてエミュレーター「Veloce」を用いた新たなパワー解析フローを発表したほか、組込み向けソリューションとしてIoT/ウェアラブル・デバイス向けの「Nucleus RTOS」をリリースしている。

Mentorは次期2016会計年度Q3(15年8-10月)の売上を2億9000万ドル程度と予測している。

2015.08.25

2015年8月19日、Synopsysは、2015会計年度第3四半期(15年5月-7月)の四半期決算を報告した。

発表によると、Synopsysの2015会計年度Q3の売上は、前年同時期比約6.5%増、前期Q2比微減の5億5580万ドル、純利益は5540万ドルで前年実績を下回った。売上額は前四半期決算報告時の予測通りだった(※GAAP基準による会計結果)

Synopsysはこの5月-7月の間に、新製品として「DesignWare Hybrid IP Prototyping Kit」、「PCI Express 3.0 IP」、「USB Type-C IP」などをリリース。また、回路シミュレータ「CustomSim」のバージョンアップを行い、大幅にシミュレーション速度を向上させた。

また、RTL解析ツール「Spy Glass」をはじめとしたEDAツールを手掛けていた中堅EDAベンダAtrentaの買収を発表。同買収はつい先日8/3に完了している。

Synopsysは次の2015会計年度Q4(15年8月-10月)の売上を5億7000-8500万ドルと予測している。

2015.08.06

2015年8月3日、米SIA(Semiconductor Industry Association)は、2015年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2015年6月の世界半導体売上は前年同月比2%増、前月比0.4%減の279億9000万ドルで6月の売上としては過去最高を記録した。売上が前年実績を上回るのはこれで26ヶ月連続となる。

2015年Q2(4-6月)の世界半導体売上は計840億ドルでQ1(1-3月)よりも1%増、前年比では2%増という結果。2015年上半期としては現在前年比3.9%の成長となっている。WSTS世界半導体市場予測では今年の成長率を3.4%としている。

2015年6月の世界半導体売上を地域別に見ると、日本、中国の両市場のみ前月を上回ったが他の市場が売上を落とし全体的には前月実績を割り込んだ。前年実績と比較すると北米、中国、アジアが好調な構図には変わりはなく、日本市場はドルベースで前年比13.6%減となっているが円ベースで換算すると前年比約4.9%の成長となる。

尚、調査会社のGartner社は2015年の世界半導体市場を年初の時点で5.4%の成長と予測していたが、その後2度の下方修正を行い、最新の予測は2.2%の成長としている。

※SIA

2015.07.30

2015年7月27日、Cadenceは、2015会計年度第2四半期(2015年4-6月)の売上を報告した。

Cadenceの2015年Q2売上は、前年同時期比約9.7%増、前期Q1比約1.2%増の4億1600万ドル。純利益は前年比の約2.5倍の5800万ドルだった。(※GAAP基準による会計結果)

Cadenceは前Q1で6年連続で継続していた右肩上がりの売上増が途切れていたが、今期は再び前四半期売上を上回る結果を残した。

CadenceはQ1に旗艦EDA製品の新製品、配置配線ツール「Innovus」を市場投入していたが、このQ2においても新型論理合成ツール「Genus」と新たなデバッグ・ツール「Indago Debug Platform」を発表している。

Cadenceは、来期2015年Q3の売上額を同社の四半期売上記録を上回る4億2300-3300万ドルと予測している。