NEWS

2016.11.16

2016年11月4日、Cadenceは同社の回路シミュレータ「PSpice」とMathWorksの「MATLAB/Simulink」の統合を発表した。

発表によると「PSpice」と「MATLAB/Simulink」の統合はMathWorks社との協業によるもので、同統合環境を用いることで「PSpice®」を用いたアナログ・ミックスシグナルシミュレーションと「MATLAB/Simulink」の各種モデリング、解析、可視化、計測機能を合わせて利用できるようになる。

この統合環境の肝は、PSpiceとSimulinkの間で双方向なデータのやり取りが可能になった事とPSpice上でMATLAB機能を扱うことが可能になった点で、ユーザーはSimulinkが提供する機能ブロック及び検証モデルのライブラリと34000種のPSpiceモデルの双方を利用することもできる。これによりシステムデザイン全体の検証を大幅に効率化する事が可能となる。

※画像はCadenceが公開している動画のキャプチャ画面

2016.11.15

2016年11月14日、日本のファブレスICベンダ大手ソシオネクストは、ARMコア搭載SoCの新製品「SC2A11A」を発表した。

「SC2A11A」は1チップにARM Cortex-A53コアを24個、64ビットメモリーを搭載するSoCで、同社初のARMベースのサーバー向けSoC製品となる。ソシオネクストはARMコアの採用により「SC2A11A」は優れた処理能力と電力効率を実現するとしており、データセンター向けのサーバーシステムだけでなく、エッジコンピューティングに対しても同製品の提供を狙っている。

2016.11.15

2016年11月9日、Xilinxは新しい16nm FPGA「Virtex® UltraScale+™」4品種を発表した。

新製品は、16nm Virtex® UltraScale+™ FPGA デバイス名 VU31P,VU33P,VU35P,VU37Pの4製品で、32Gb-64Gbの積層DRAM「HBM(High Bandwidth Memory)」を搭載。合わせてアクセラレータ向けキャッシュ・コヒーレント・インターコネクト規格「CCIX」のIP/ポートを装備している。

XilinxはHBMを搭載する事でDDR4 DIMMと比較して20倍のメモリ帯域幅を提供しながら、1 ビットあたりの消費電力を4分の1に抑えることが可能としている。また、CCIXのサポートにより、CCIX対応プロセッサとFPGAによるキャッシュ・コヒーレント・アクセラレーションを実現できる。

CCIXは複数のプロセッサ・アーキテクチャとFPGAのシームレスなデータ共有を目指して、Xilinxもメンバーに名を連ねるCCIXコンソーシアムが策定した規格でデータセンター分野での利用を主な目的としている。

2016.11.15

2016年11月7日、Synopsysはソフトウェアのセキュリティ関連ソリューションを提供するCigital社およびCodiscope社の2社を買収した事を発表した。

※画像はCodiscope社のWeb画面

Synopsysの発表によると、Cigitalは、ソフトウェアのセキュリティ脆弱性の特定 / 修正 / 対策などを通じた運用管理サービス / プロフェッショナル・サービスを世界展開するセキュリティ大手企業。CodiscopeはCigitalから分離独立した会社で、Cigitalが開発したセキュリティ関連ツールや技術資産を使い易く効率的なツール・スイートとして統合し、世界中のソフトウェア開発企業に提供している。

Synopsysが今回買収した両社はともに米国企業で買収手続きは2016年12月に完了する予定。買収条件に関する詳細は明らかにされていない。

Synopsysは「Silicon to Software」というトレードマークを掲げ、ハードウェア開発向けのEDA製品に加えソフトウェア向けのソリューションを拡充中。特にセキュリティ分野については力を注いでいる。

2016.11.15

2016年11月14日、独SiemensとMentor Graphicsは、両社間の買収合意について発表した。

発表によるとSiemensは約45億ドルでMentor Graphicsを買収。来年Q2には買収手続きが完了する見込みとなっている。

Siemensは「Vision 2020」という同社の経営戦略の下で産業向けソフトウェア・ベンダの買収を進めており、今回のMentor買収もその一環としているが、約2ヶ月前の2016年9月に米ヘッジファンドのElliott ManagementがMentorの発行株式8.1%を取得した事にって、買収話が急展開したと推測される。Siemensとして今回のMentorの買収額は過去最高。MentorはSiemensのDigital Factory Divisionにジョインする予定となっている。

Mentorは現存するEDAベンダとしては最古の企業であり、かつては売上で業界首位に立っていた。(現在は業界3位)Mentorによると同社の従業員は世界32カ国で計5700名以上。かつての回路図入力ツールに代わり、現在の主力EDA製品は物理検証ツールや機能検証ツール、エミュレータなど。MentorはEDA以外にも自動車向けの開発ツールや組込みソフト開発ツール、組込みOS、熱・流体解析ツールなどを扱っており、EDAの周辺領域における事業展開に積極的に投資していた。

業界のパイオニアが買収されるという事実はEDA業界の節目とも言えるもので、一見ショッキングな出来事に映るが、その資産は巨大なコングロマリットに引き継がれる事で、これからのサイバー社会を支える基盤技術の一つとして更に進化・発展していく事だろう。

※メンター・グラフィックス・ジャパン株式会社

2016.11.08

2016年10月24日、台湾のファブレスASICベンダであるAlchip Technologiesは、中国での子会社設立を発表した。

発表によるとAlchipは、中国合肥市政府が投資を進める合肥ハイテク産業開発区に子会社を設立。同ハイテク産業開発区「Silicon City」は、IC産業開発のための機能的プラットフォームとして位置づけられるもので、Alchipは合肥市政府とのパートナーシップ契約に基いてIC設計シニア・エンジニアの育成やIC設計サービスの構築に取り組むという。

2016.11.02

2016年10月31日、米SIA(Semiconductor Industry Association)は、2016年9月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年9月の世界半導体売上は前年同月比3.6%増、前月比5%増の294億3000万ドルで、9月の売上として過去最高を記録した。売上が前年同時期の実績を上回るのは8月に続いて2ヶ月連続。一部の民間リサーチ会社は既に今年の半導体売上予測の上方修正を進めている。

2016年9月の世界半導体市場を地域別の売上で見ると、依然北米市場と欧州市場は前年実績を割り込んでいるが、今年上半期と比較すると売上は大きく回復。中国市場は前年比12%増と今年最高の伸びを示した。

日本市場の売上はドルベースで前年比4.2%増、円ベースでは前年比約11.8%減で、円ベース換算の売上は約2854億円となっている。

※SIA

2016.10.24

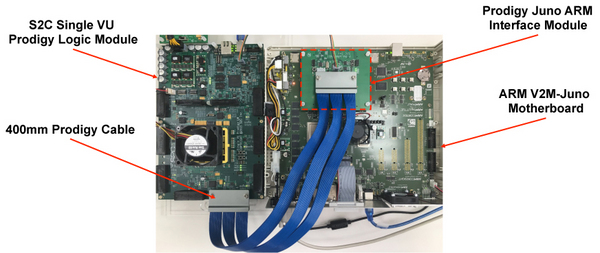

2016年10月18日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、新製品「Prodigy Interface Module for ARM Juno」のリリースを発表した。

S2Cによると、新製品「Prodigy Interface Module for ARM Juno」は、S2CのFPGAプロトタイピング・システムとARMの純正ソフトウェア開発環境「Juno ARM® Development Platform」を接続するもので、ARMv8-AアーキテクチャをベースにしたデザインのFPGAプロトタイピングに利用する事が可能。S2Cは同インタフェース・モジュールの利用者向けにリファレンス・デザインを用意している。

「Juno ARM® Development Platform」は、ARMv8-AアーキテクチャのCortex-A72およびA53ベースのSoCを搭載するARMのソフトウェア開発環境で、同環境をS2Cの「Prodigy FPGA Prototyping Platform」に接続することで、ARMベース・プロセッサとユーザーのカスタム・ロジックを含めたシステム全体のプロトタイピングが容易かつ効率的に実現できるようになる。

FPGAプロトタイピングのソリューションを提供する各社は、ARMベース・システムのプロトタイピング向けに以前からドーターボードやバーチャル・プラットフォームとの連携など様々なオプションを提供しているが、今回S2CがリリースしたようなARMの純正開発環境と直接繋がるソリューションは、ユーザーにとって最も効率的かつ低コストなソリューションと言えるだろう。

※画像はS2C社提供のデータ

※S2Cジャパン株式会社

2016.10.21

「Silvaco Japan EDA Seminar 2016」開催のご案内

シルバコ・ジャパンは11月17日(木)に横浜ランドマークタワー25Fにて

「Silvaco Japan EDA Seminar 2016」を開催します。

セミナーの見どころ

1、基調講演:リボンディスプレイ株式会社 代表取締役社長 須山 透様

現在、業界内外で注目を浴びる須山氏が登壇し、コスト競争の厳しい

LCDドライバ市場でトップを走る戦略を語ります。

2、招待講演:Silicon Creations Vice President兼CTO Jeff Galloway様

先端FinFETプロセスから成熟プロセスまで幅広く対応する、同社独自の

アナログ・ミックスド・シグナルIP設計フローをご紹介します。

3、IoT時代の設計ソリューションのご紹介

新製品のパワー・インテグリティ・ツール、寄生RC解析ツール、

ばらつき考慮設計ツールを中心に電源IC、センサ、に向けたLSI設計に欠かせない

デザイン・ソリューションをご紹介します。

4、ファンドリ、デザインハウスがブース出展

国内外のファンドリ、デザインハウスが本セミナーにて多数出展します。

一度に多くのビジネス情報を共有するチャンスです。

出展企業:Global Foundries、TowerJazz、XFAB、シリコンソーシアム(株)

内藤電誠工業(株)、(株)ブルックマンテクノロジ、他

5、ネットワーキングタイム(来場者交流会)

セミナー開催後、テーマ毎に別れ、ざっくばらんに交流していただきます。

軽食を交えご歓談ください。

参加は無料です。事前登録制となっております。

座席には限りがございますので、お早めのご登録をお願いします。

皆様のご来場お待ちしております。

――PR――

2016.10.12

2016年9月29日、米ESD Allianceは、2016年度第2四半期(4月-6月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2016年Q2(4-6月)の世界のEDA売上総額は、前年比約5.5%増、前Q1比約2.5%増の20億1260万ドルだった。四半期売上が20億ドルの大台を超えるのはこれで史上3回目。過去2回はいずれもQ4売上で記録しており、上半期のQ2で20億ドルを超えるのはこれが初めて。半導体市場の回復も影響しており、今年のEDA市場は引き続き順調に成長が続く見通しだ。

2016年Q2のEDA売上をカテゴリ別に見るとサービス分野以外の全ての分野で売上が前年実績を上回った。IP分野は継続的な成長を維持。IC Physical Design & Verification分野も好調だった。

2016年Q2のEDA売上を地域別に見ると、欧州以外の全ての地域で売上前年比増を達成した。中でも日本市場は前年比15.7%と大きく成長しているが、円ベースで換算すると為替レートの影響で売上微増という状況である。

2016年Q2時点でのEDA業界の従業員数は前年比6.7%増の34988人で過去最高記録を更新した。

2016Q2の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億6240万ドル 0.8%Up

■IC Physical Design & Verification分野 4億1500万ドル 9.5%Up

■IP分野 6億6800万ドル 9.2%Up

■サービス分野 9940万ドル 3.6%Down

■PCB/MCM分野 1億6780万ドル 8.1%Up

2016年Q2の地域別の売上と昨年同時期との比較は以下の通り。

■北米 9億840万ドル 4.4%Up

■欧州 2億8470万ドル 6.8%Down

■日本 2億1140万ドル 15.7%Up

■アジアその他地域 6億810万ドル 10.9%Up

2016.10.06

2016年10月3日、米SIA(Semiconductor Industry Association)は、2016年8月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年8月の世界半導体売上は前年同月比0.5%増、前月比3.5%増の280億3000万ドルだった。売上が前年同時期の売上を上回るのは1年2ヶ月振り。昨年末から長らくの間市場の停滞が続いていたが、回復傾向がようやく鮮明になってきた。

2016年8月の世界半導体市場を地域別の売上で見ると、前年実績に対して大きく売上を落としていた北米市場が前年比3.1%減とかなり回復。唯一成長を維持している中国市場は前年比7.1%増と7月実績を上回る活況を示した。

日本市場の売上はドルベースで前年比2.2%増、円ベースでは前年比約16%減で、円ベース換算の売上は約2764億円となっている。

※SIA

2016.09.22

2016年9月12日、Synopsysは同社のプロセッサ・コア「ARC」シリーズの新製品として、高度なセキュリティ技術を搭載する「ARC SEM」ファミリの2製品を発表した。

発表によると新製品「ARC® SEM110」および「ARC® SEM120D」は、スマートメーター、NFC決済、組込みSIM(eSIM)などの金銭的な取引を伴い低消費電力が要求される組込みアプリケーションをターゲットとしたプロセッサで、Synopsysが同製品をセキュリティ・プロセッサと呼ぶことからも分かるように、優れたセキュリティ機能を複数備えている。

具体的には、サイドチャネル攻撃への対策としてインストラクション実行サイクルを均一化したり、消費電力をランダム化する機能があるほか、強化されたメモリ保護ユニットと提供される「SecureShield Runtime Library」により容易にセキュアな実行環境(TEE:Trusted Execution Environments)を構築可能となっている。

その他には、外部からの攻撃や知的財産の盗用対策として、インストラクションとデータの暗号化による耐タンパ性パイプライン、アドレスのスクランブル処理、データ整合性チェック機能が用意されており、不正な設定変更により引き起こされるシステム障害を検知し対策を講じるウォッチドッグ・タイマーも内蔵されている。

※画像は全てSynopsys提供のデータ

「ARC® SEM110」と「ARC® SEM120D」の違いはDSP機能の有無で、「ARC® SEM120D」には、医療機器やIoT機器などより厳重なセキュリティとリアルタイム処理が要求されるアプリケーション向けに、DSPインストラクションとMUL/MACユニットが用意されている。

両製品は今年10月より出荷が開始される予定。

Synosysは屋台骨のEDAツール以外の事業としてIPやソフトウェア開発分野の事業を拡大しているが、セキュリティ関連はその主軸として積極的に投資している分野で、ハードウェア/ソフトウェアの両面からソリューションを強化している。

2016.09.20

---PR---

9月28日(水)日本時間11時より、統計的ばらつき解析ソリューションを手掛けるカナダのSolido Design Automation社と台湾TSMC社の合同Webinarが開催されます。

Webinarの対象者はIC Designers, Design Managers, CAD Managers, Directors、参加者は、バリエーションを意識した高性能、低消費電力、低コスト製品用のメモリー及びスタンダードセル設計テクニックを学べます。

【Webinar概要】

バリエーションの効果は、先進のプロセスノードでは、ますます影響力を強めており、それぞれプロセスノードにおいて、新しいバリエーションの要因が考慮されなければなりません。また、競争の激化により、高性能、低消費電力、低コストの製品を作るために緊密な設計マージンが求められます。設計者は、スケジュールを守り、競争力のあるチップを提供するため、速度、精度とカバレッジを考慮した先進的なバリエーションを意識した技術を使用して、これらのタイトなマージンを達成するため、これまで以上にバリエーションの解析を行う必要があります。

このウェビナーで、TSMCは、 Solido 最新バージョンのバリエーションデザイナー 4 を使用した、TSMCのアドバンスドプロセスでの、バリエーションを意識したメモリー設計およびスタンダードセル設計の方法について説明します。

Solido Design Automation社のWebinarに参加を希望される方は、以下のリンクからご登録下さい。(このページは英語です。)

http://www.solidodesign.com/webinar-registration/

2016.09.08

2016年9月6日、米SIA(Semiconductor Industry Association)は、2016年7月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年7月の世界半導体売上は前年同月比2.8%減、前月比2.6%増の270億8000万ドルだった。売上の前年実績割れはこれで13ヶ月連続となるが、直近の3ヶ月は僅かながら連続して売上を伸ばしている。

2016年7月の世界半導体市場を地域別の売上で見ると、中国市場を除く全ての地域で前年実績割れ。前年比2ケタ減が続いていた北米市場は回復の兆しが見え始めており前年比7.5%減にとどめた。

日本市場の売上はドルベースで前年比1.1%減、円ベースでは前年比約16.6%減で、円ベース換算の売上は約2700億円となっている。

※SIA

2016.08.26

2016年8月25日、今年で第三回目の開催となるセミナー「Design Solution Forum 2016」の開催が発表された。

同イベントは国内エレクトロニクス分野における設計者ネットワークの構築と拡大を目指す技術セミナーで、設計・開発現場で活躍するエンジニアの講演が主体となっている。

今年の「Design Solution Forum 2016」では計47のセッションが予定されており、その殆どがエンジニアによる講演。基調講演は日本のハードウェア・ベンチャーとして海外でも有名なCerevoのCTO 松本 健一氏が登壇する。

セミナーに協賛するスポンサー企業は下記計27社で、セミナーではスポンサーの展示ブースも用意される。

セミナーへの参加登録は先着順で、希望者は立食パーティー形式の交流会に参加できる。セミナー、交流会ともに完全無料だが、所定の登録数に達した時点で受付終了となる。

■Design Solution Forum 2016 スポンサー企業

アルデック・ジャパン(株)

アーム(株)

Australian Semiconductor Technology Company(株)

アバントテクノロジー(株)

日本ケイデンス・デザイン・システムズ社

キヤノンアイテック(株)

CMエンジニアリング(株)

コルタス社

ファラデーテクノロジー日本(株)

イマジネーションテクノロジーズ(株)

Intel/Docea

日本CEVA(株)

日本シノプシス(合)

日本システムウェア(株)

日本ワンスピン・ソリューションズ(株)

日本リアルインテント(株)

S2Cジャパン(株)

Silexica Software Solutions GmbH

Sky(株)

SmartDV Technologies India Private Limited

(株)ソシオネクスト

スタビリティ(株)

東芝情報システム(株)

ベリフィケーションテクノロジー(株)

(株)ベリフォア

ザイリンクス(株)

(株)ジィーサス

※Design Solution Forum 2016 参加登録はこちら

2016.08.24

2016年8月17日、Synopsysは、2016会計年度第3四半期(16年5月-7月)の四半期決算を報告した。

発表によると、Synopsysの2016会計年度Q3の売上は、前年同時期比約10.7%増の6億1520万ドル、純利益は前年比約16.8%増の6470万ドルだった。(※GAAP基準による会計結果)

Synopsysは前Q2で同社初の売上6億ドルを達成していたが、Q3においても好調な業績を維持し売上記録を更新した。Synopsysはこの活況を受けて今年3億2500万ドルの自社株買いを実施し利益を株主に還元するとしている。

Synopsysはこの5月-7月の間に、旗艦製品「IC Compiler II」のバージョンアップやATPGツールの新製品「TetraMAX® II」を発表。IP製品もARCプロセッサ、PCIe、USB、MIPIなど多数の製品をリリースした。

Synopsysは次の2016会計年度Q4(16年8月-10月)の売上を6億2100-6億3600万ドルと予測している。

2016.08.23

2016年8月18日、Mentor Graphicsは、2017会計年度第2四半期(16年5月-7月)の売上を報告した。

発表によると、Mentorの2017会計年度Q2の売上は、前年比約9.6%減の2億5400万ドル、約340万ドルの営業利益を計上した。(※GAAP基準による会計結果)

この業績は前Q1売上報告時の予測値を上回るもので、発表を受けて同社の株価は上昇に転じた。

Mentorは昨年Q3から売上の前年実績割れが続いており今期で4四半期連続。エミュレータ「Veloce」や自動車向けのビジネスは順調のようだが、全体的な業績としては売上減少が続いている。

Mentorは次期2017会計年度Q3(16年8-10月)の売上を3億1000万ドル程度と、前年実績を大きく上回る強気な業績予測している。

2016.08.16

先日、米Aldec社のハードウェア製品部門の技術サポート・マネージャーKrzysztof Szczur氏から話を聞く機会があり、同社の最新のハードウェア製品について話を聞いた。

まず同氏が紹介してくれたのは、20nmFPGA Xilinx Virtex UltraScale搭載のプロトタイピング・ボード「HES-7」。Virtex UltraScaleを搭載する「HES-7」は、1年ほど前に発表され、既に昨年Q3以降に出荷が開始されている製品である。発表当初はVirtex UltraScale VU440デバイスを6個搭載するボードの存在が明らかにされていたが、同デバイスを3個搭載するボードも販売されているという事でその実物を見せてもらった。(下の写真)

Krzysztof氏によると「HES-7」のデザイン容量は、Virtex UltraScale VU440を6個搭載するボードで約1億5800万ASICゲート、3個搭載するボードで約7900万ASICゲート、これらボードは専用のバックプレーンに最大4枚マウント可能で最大6億3300万ASICゲートのデザインに対応する事が可能との事。Xilinxの公称値から換算するとVirtex UltraScale VU440を24個使用すれば10億ASICゲート近くの容量になるはずだが、Krzysztof氏曰く「エミュレーション用途ではFPGAの容量をフルで利用するとインプリメントが大変になるので、実際の容量に対して60%程度の容量としている」という事だった。

実績としては、昨年の発売以降ワールドワイドで順調に顧客を獲得しており、「HES-7」のボードとしての拡張性および柔軟性が高い評価を得ているとの話。「HES-7」はソフトウェア環境「HES-DVM」を利用する事でエミュレーション、アクセラレーション、協調シミュレーションなどあらゆる検証ニーズに対応可能であり、VIPと呼ぶ標準バスやI/Oのアダプタも多数用意されている。また、「HES-7」は業界標準のオープンなFMCコネクターを搭載しているため顧客自身でシステムを拡張することも可能だ。

Virtex UltraScaleを搭載するボードはS2C,Synopsys,ProDesign,DINIなど業界各社からリリースされているが、ボード単体の仕様だけでなく、ボード周りの運用環境も各社各様なので、コストやパフォーマンスの他に、「やりたいことを如何に早く実現できるか」、また、「買ったものを如何に使い回しできるか」といった点も製品選びの重要なポイントとなるだろう。ちなみにAldecの「HES-7」には、業界随一とAldec自らうたう1年保証のサポートが付くという話である。

もう一つ、Krzysztof氏が紹介してくれたのがXilinxのARM搭載SoC「Zynq」を搭載する小型SoC開発ボード「TySOM」だ。

「TySOM」ボードは、Aldecの組込み向けソリューションの一つとして提供されているボードで、現在2種類の製品がリリースされている。

その一つ「TySOM-1ボード」は、XilinxのZynq XC7Z030を搭載するボードでその大きさはシングル・ボード・コンピュータ「Raspberry Pi」と同程度。小さいながらもZynqの他にメモリ、豊富なマルチメディア/通信インタフェースを備えており、Zynqの開発プラットフォームとしてFPGAおよびARM開発者向けに提供されている。

ターゲット・アプリケーションは、IoT、FA、ドローン、自動車、ロボット、コンピュータ・ビジョンと様々で、色々なアプリケーションの開発に利用可能。価格は決して安くはないようだが、Zynqベースの「Raspberry Pi」といった感じで豊富なマルチメディア/通信インタフェースを活用して各種組込み向けSoCを開発できる。

Krzysztof氏はその場で組込みLinuxを載せた「TySOM-1ボード」に「Raspberry Piカメラ」を接続したカメラ画像のリアルタイム画像処理のデモを見せてくれた。同氏によると、ADAS向けドータカードなど「TySOM」向けのドータボードも複数用意されているとの話だ。

「HES-7」とは方向性の違う製品ではあるが、組込み分野での活用が広がるZynqベースの開発ボードとして、「TySOM-1ボード」は面白い存在と言えるだろう。

ちなみにもう一種類の「TySOM」ボードは、多数のインタフェースの代わりにXilinx系の評価ボードで良く使用されているFMCコネクタを2つ搭載するもので、ユーザーのニーズに応じて他のソリューションと組み合わせてZynqベースのシステム開発に利用できる。

2016.08.16

2016年8月5日、ハードウェア設計のコンサルティング及び教育、設計サービスを手掛ける株式会社エッチ・ディー・ラボは、書籍「RTL設計スタイルガイドVerilogHDL版」の販売を開始した。

「RTL設計スタイルガイド」は、ハードウェア設計言語HDLを用いたRTL設計の基準書で、長年株式会社半導体理工学研究センター(STARC:2016年5月31日に解散)より販売されていたが、元々はエッチ・ディー・ラボが1998年に同社のコンサルティングの内容を本にまとめて半導体関連8社に販売したのが始まり。

2001年には一般書籍として販売が開始され、その後、STARCに著作権が移管され、日本のLSI設計の基準書として多数のハードウェア設計者に活用された。

この度、STARCの解散に伴い、RTL設計スタイルガイドの著作権はエッチ・ディー・ラボに返還され、休止されていた書籍販売が再開される事になった。

販売されるのはPDF付きの電子書籍でA4サイズ、642ページ、価格は3,780円。ネット出版BookWayにて購入可能。紙媒体として入手したい場合はオンデマンド印刷本を8,100円で注文できる。

※PDFは印刷不可、電子書籍の閲覧には専用アプリが必要(iOSやAndroidのタブレット等で閲覧する場合)

RTL設計スタイルガイドは国内のRTL設計の標準化に貢献した著名な書籍で、再販を望む声が多かった。

2016.08.03

2016年6月の世界半導体市場は前年比5.8%減の263.6億ドル、12ヶ月連続前年実績割れ

2016年8月2日、米SIA(Semiconductor Industry Association)は、2016年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年6月の世界半導体売上は前年同月比5.8%減、前月比1.1%増の263億6000万ドルだった。5月、6月と僅かではあるが2ヶ月連続で売上は伸びたが、売上の前年実績割れはこれで12ヶ月連続となる。

2016年のQ2(4-6月)の売上額は計791億ドルでQ1実績を1%上回ったが、前年比5.8%減となっている。

2016年6月の世界半導体市場を地域別の売上で見ると、不振の続いていた北米市場が僅かに回復するも前年比では依然2ケタ減となっている。売上が前年を上回ったのは中国市場だけだった。

日本市場の売上はドルベースで前年比1.3%減、円ベースでは前年比約14%減で、円ベース換算の売上は約2669億円となっている。

2016.07.28

2016年7月25日、Cadenceは、2016会計年度第2四半期(2016年4-6月)の売上を報告した。

Cadenceの2016年Q2売上は、前年同時期比約8.9%増、前期Q1比約1.1%増の4億5300万ドルで同社の四半期売上記録を更新。純利益は前年比約15%減の4900万ドルだった。(※GAAP基準による会計結果)同社の四半期売上記録の更新はこれで4四半期連続となる。

Cedanceによるとエミュレーターの新製品「Palladium® Z1」がQ1に続いて好調で売上高に繋がっているとの事。

Cadenceはこの4-6月において、同社の主力製品アナログ・カスタム設計環境「Virtuoso」プラットフォーム、PCB設計ツール「OrCAD」、「Allegro」プラットフォームの刷新を相次いで発表している。

Cadenceは、2016会計年度Q3の売上額を4億4000-4500万ドルと予測している。

2016.07.22

2016年7月20日、Mentor Graphicsは、Barefoot Networks社による同社のエミュレータ「Veloce」の成功事例を発表した。

Barefoot Networksは、世界最速で完全にプログラマブルなネットワーク・スイッチを実現する半導体ベンチャーで、今年6月に6.5Tbpsで動作するネットワーク・スイッチ「Tofino」を発表したばかり。「Tofino」は既存の一般的なネットワーク・スイッチよりも約2倍高速でスイッチの動作をプログラム可能。Barefoot Networksは自らをネットワーク・スイッチ業界のゲーム・チェンジャーと名乗っており、既に投資家から1億ドル以上の資金を集めている。

Mentorによると、Barefoot Networksは「Tofino」の検証用に複数のエミュレータを評価し、結果的にMentorの「Veloce」を選定。「Veloce」のキャパシティ、仮想化技術、リモートアクセス機能、ネットワーク設計での検証実績などが評価され採用されたという。

Barefoot Netwaorksは、Ethernetを含む複雑な相互接続を内包する「Tofino」の検証において、課題となるエミュレーション・プラットフォームでの配線を「Veloce」の仮想配線技術とキャパシティによって解決。また、「Veloce」のHW/SW協調シミュレーション機能やパケット・ジェネレーターを搭載するオプションのソフトICE「Veloce VirtuaLAB Ethernet」なども有効活用したという。

※メンター・グラフィックス・ジャパン株式会社

2016.07.22

2016年7月13日、Cadenceは同社の複数のEDAツールがIntelの10nm Tri-Gateプロセス向けに認証されたことを発表した。

今回Intelに認証されたCadenceのツール群は以下の通り。

認証にあたりIntelはImagination TechnologiesのGPU「PowerVR GT7200」を評価に使用した。

・Innovus™ Implementation System

・Quantus™ QRC Extraction Solution

・Tempus™ Timing Signoff Solution

・Voltus™ IC Power Integrity Solution

・Voltus-Fi Custom Power Integrity Solution

・Spectre® Classic Simulator, Spectre Accelerated Parallel Simulator (APS) and Spectre RF Simulation

Intelのファウンドリ事業の顧客はこれらCadenceのツールをIntelお墨付きのツールとして10nm Tri-Gateプロセス向けのデザインに活用できる。

2016.07.21

先ごろ初の資金調達でベンチャーキャピタルから計800万ドルの投資を受けたTempo Automationという会社がサンフランシスコにある。

Tempoは、プリント基板のプロトタイプを僅か3日間で作成し納品してくれるという会社で、独自に構築した少量生産向けの基板製造システムを武器にAmazonのようなビジネス手法で顧客を集めている。少量生産向けというのが同社の特色かつ狙いであり、大量生産向けの設備を強制させられる事にアンチな姿勢を示し、ソフトウェア開発と同等のスピード感でハード開発を進める事を目指している。

Webサイトの情報によると、プリント基板製作の見積もりは最短で2時間以内、遅くとも24時間以内に回答。プリント基板の製作から納品までの時間はサンフランシスコのベイエリアなら3日、その他アメリカ国内であれば4日としている。(※海外発送に関する情報は見当たらない)

同社にプリント基板の製作を依頼する際は、最大8層、100枚までの「STANDARD PCB」か最大30層、250枚までの「CUSTOM PCB」のいずれかを選択。デザイン・ファイルをTempoのサーバーにアップロードし、仕様書とパーツリスト/パーツ番号といった情報を送ると数日後には見積り通りのプリント基板が納品される。プリント基板の発注は1枚から可能で、その費用については情報が開示されていない。

※画像はTempo社Webサイト上のデータ

Tempoはプリント基板の発注者向けにAltium, Eagle 2 Layer/4 Layer/6 Layerのデザインルール・ファイルを提供しており、同社のWebサイトからダウンロードできる。これらツールとは別にCadence,Mentorのツールにも対応してくれるようである。

Tempoではプリント基板を製作する過程で独自のDFMチェックを行い品質を担保しており、もし納品後にプリント基板の不良が見つかった場合は無料で作りなおしてくれる。なお、同社のビジネスはあくまでもプリント基板の製作のみでデザインサービスは行っていない。

同社の主なターゲットはスタートアップ企業だが、大手企業も顧客に名を連ねているらしく、ビジネスは急成長している様子。ターンキーサービスとしての効率化を追求した独自の製造システムにTempoの強みがあるようだ。

2016.07.20

少し前の話になるが、今年5月2日、CadenceはイスラエルのEDAベンダーRocketick Technologies社の買収を発表した。

Rocketick Technologiesは、GPUを使ってVerilogシミュレーションを高速化するツール「RocketSim」と一般的なマルチコアCPUサーバーを併用してシミュレーションを高速化する「RocketSim-CPU」という大きく2種類の製品を提供するEDAベンダ。

今回の買収により同社のシミュレーション高速化技術はCadenceに移管され、RocketickのメンバーはCadenceのSystem & Verification Groupに加わった。買収に関する条件などは公開されていない。

Cadenceによると、買収したRocketickの技術を用いることにより、Cadenceの論理検証ツール「Incisive® Enterprise Simulator」の論理シミュレーション処理が、標準的なマルチコア・サーバー上で、RTL検証で6倍、ゲートレベル検証で10倍、ゲートレベルのDFT検証で30倍まで高速化されるとの事。

上述の通りRocketick社はGPUを活用した高速技術も保有していたが、その技術については発表では触れられていない。GPUによる高速化には、ユーザーがNVIDIAのGPUを搭載したボードを用意する必要があり敷居が高い。ちなみにRocketick社にはNVIDIAが出資していた。

2016.07.20

2016年7月12日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の論理シミュレータ「Riviera-PRO」のバージョンアップを発表した。

Aldecによると、論理シミュレータ「Riviera-PRO™」の最新バージョン2016.06では、メトリクス・ドリブン検証のサポートが拡充し、制約付きランダム検証(CRV)のパフォーマンスを大幅に高めたとの事。合わせて検証効率を高めるための複数のデバッグ機能を新機能として追加した。新機能としては下記のような機能が搭載されている。

・有限ステートマシン(FSM)カバレッジ

・デザインユニット・ビューア

・データセット・ウィンドウ

・カバーグループ・ビューア

・4Kディスプレイのサポート

・デバッグツール用の新コントリビュータ

→デザインのテスト対象部分に影響を与える信号を簡単にリスト化可能

なお、Aldecは今回の「Riviera-PRO™」のバージョンアップによる実例として、XilinxCoreLib シミュレーションライブラリと SystemC テストベンチ、SystemVerilog 制約付きランダム・スティミュラスを使ったデザインのシミュレーション速度を20%向上させる事に成功したと伝えている。

「Riviera-PRO™」は同社の提供する論理シミュレータの最上位製品。ASIC,FPGA向けに同社の提供する論理シミュレーション技術の全てが搭載されている。

※アルデック・ジャパン株式会社

2016.07.20

2016年6月22日、セールスツアーで日本を訪れていた仏Cortus社のセールスおよびマーケティングVPのDr Roddy Urquhart氏に話を聞く機会を頂いた。簡単ではあるが同社のソリューションについてここでご紹介したい。

Cortus社ホームページ:http://www.cortus.com/

Cortusはフランスに拠点を置くIPベンチャーで創業は2005年。CEOのMichael Chapman氏とエンジニアリングVPのChristopher A. Kopetzkyは、Intel,Bosch,Infineon,Synopsysなどで長年プロセッサ開発に従事していた経歴を持つ。

Cortusの提供するIPは32ビットRISC CPUで、その性能とコストパフォーマンスによるARM Cortex-Mシリーズプロセッサの置き換えを狙っている。台湾Andes Technology社あたりがコンペと言えるだろう。同社はフランス以外に韓国、ヨーロッパ、北米にも販売拠点を構えており、既に大手企業を含む複数のライセンサーによってSIMやスマート・カード向けなど9億個を超える同社IP搭載チップが出荷されているという。

Cortusのが現在提供しているIPのラインナップは下記図にある6品種で間もなく7品種目のハイエンド製品(APS29)がリリースされる予定となっている。

APS1は同社の最初の製品で後の製品と同様にハーバード・アーキテクチャー採用の32ビットRISC CPU。APS23とAPS25はそれぞれAPS3RとAPS25s+のエンハンスド・バージョンで、2014年にリリースされた新しい命令セット「Cortus v2」をベースとしている。また、FPS26も「Cortus v2」をベースとしておりハードウェア浮動小数点がサポートされている。

各コアはパイプライン段数、演算器、メモリ構成、バスインタフェース、マルチコア機能などの違いで用途別に仕立てられている。またCortusは、これら市販製品とは別に顧客のニーズに応じたカスタムコアの提供も行っている。

周辺環境としては、基本的なペリフェラルは一通り備えられており、自社開発のコンパイラ、ISS、コ・シミュレーション用のSystemCモデル、FPGAベースのプロトタイピング・ボードなどの開発環境が用意されている。デバッグ環境はEclipse,GDBのほかに、サード・パーティーのツールを利用する事もできる。

Cortusの提供する各コアは、高性能、小面積、低消費電力を謳っており、各種ベンチマークの結果では総じて競合製品のARM Cortex-M0,M3,M4を上回る結果を残している。

同社はライセンスの売り切りとロイヤリティの両面でビジネスを行っているが、その価格については顧客の要求に応じて別途相談。基本的にARMのコアより安いというのが彼らの謳い文句となっている。現状の製品はARM Cortex-Mシリーズをターゲットとしているが、今後はCortex-RおよびAシリーズをターゲットとした製品もリリースする計画のようだ。

2016.07.19

2016年4月26日、検証/設計サービスと機能検証用のEDAツールを手掛けるCMエンジニアリングとプロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けのEDAツールを手掛けるSilvacoは、両社製品の連携を発表した。

フロントエンド分野のEDAツールを手掛けるCMエンジニアリングと、TCADやアナログ、ミックスド・シグナル分野で有名なSilvacoのコラボレーションと言われてイメージできる人は少ないと思われるが、今回の発表はCMEのテストベンチ生成ツール「SpecInsight-TEX」とSilvacoの論理シミュレータ「Silos」の連携に関するものである。

CMEの「SpecInsight-TEX」は、タイミングチャートからテストベンチの入力情報、検証シナリオ、シミュレーション実行スクリプトを自動生成するツールで、既に業界大手3社の論理シミュレータとの連携実績(各シミュレータ向けのデータ、スクリプトの出力)がある。

今回「SpecInsight-TEX」は、新たなシミュレータの対応としてSilvacoの論理シミュレータ「Silos」をサポート。「Silos」向けの出力だけでなく、「Silos」側で「SpecInsight-TEX」の出力をプロパティ画面で設定可能となった。このシームレスな連携により、人手によるデバック環境の構築が不要となり、デバッグ工数を大きく削減可能となる。

※株式会社シルバコ・ジャパン

2016.07.08

2016年7月5日、米SIA(Semiconductor Industry Association)は、2016年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年5月の世界半導体売上は前年同月比7.7%減、前月比0.4%増の259億5000万ドルだった。これで売上の前年実績割れは11ヶ月連続となる。例年4月から5月にかけては売上が伸びる傾向にあり、今年もかろうじてその傾向に準じる形となったが、前月実績に対する売上増加率は過去5年間で最も低い。

2016年5月の世界半導体市場を地域別の売上で見ると、これまで前年実績を上回る売上を維持していた中国市場も遂に前年割れという結果に。前年を上回る結果を残したのは日本市場だけだった。北米市場は6ヶ月連続で前年比2ケタ減という深刻な状況だが、半導体製造装置の受注が回復傾向を見せ始めており、夏以降は緩やかな回復が見込まれている。

日本市場の売上はドルベースで前年比0.4%増、円ベースでは前年比約9.3%減で、円ベース換算の売上は約2781億円となっている。

※SIA

2016.07.01

2016年6月6日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、同社の提供するソフトウェア環境「Prodigy™ Player Pro」のバージョンアップを発表した。

発表によると最新の「Prodigy™ Player Pro 6.3」では、デザインをプロトタイピング・システムにインプリメントするためのパーティショニング機能が大幅に強化された。

パーティショニング機能として強化されたのは、従来から「Prodigy™ Player Pro」に備えられていた複数ボードにまたがるデザインのパーティショニング機能で、まずターゲット・デバイスとしてXilinxの「UltraScale FPGA(VirtexおよびKintex)」がサポートされた。S2Cの環境ではこれらは最新のデバイスを最大1.6GHz LVDSでピン・マルチプレキシング可能。また、ボード間のケーブル・コネクタを柔軟に選択する事が可能となったほか、パーティショニング後にケーブル設定を行い、性能に対する影響を確認する機能が新たに用意された。更に、同じFPGAファミリであればFPGAの搭載数に関わらずクァッド、デュアル、シングルと各種ボードを混合で使用しデザインをパーティショニングできるようになった。

S2Cはこの他にもパーティショニングの処理そのものを高速化したり、パーティショニングの品質を向上させる機能強化、機能追加を複数実施しており、FPGAプロトタイピングにおける工数削減を実現している。

なお、S2Cは「Prodigy™ Player Pro 6.3」におけるデバッグ機能についても予告的な発表をしており、今年の夏を目処に「マルチFPGAデバッグ」機能をサポートする予定との事。同機能は新製品としてリリースされる予定の「Prodigy Multi-Debug Module」と「Prodigy™ Player Pro」の連携によって実現されるもので、複数のFPGAボードを同時にデバッグすることができるという。

2016.07.01

2016年6月30日、米ESD Allianceは、2016年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2016年Q1(1-3月)の世界のEDA売上総額は、前年比4.5%増、前Q4比5%減の19億6200万ドルだった。前15年Q4は約6年ぶりに前年実績を下回ったが、今四半期は再びプラス成長に戻した。

2016年Q1のEDA売上を製品分野別に見るとCAE分野以外の全ての分野で売上が前年実績を上回った。中でもIP分野は前年比11.4%増と大きく成長した。

2016年Q1のEDA売上を地域別に見ると、全ての地域で売上前年比増を達成した。中でも日本市場は前年比11.9%と大きく成長し、再び売上2億ドル台に戻した。

2016年Q1時点でのEDA業界の従業員数は前年比7.4%増の34519人で過去最高記録を更新した。

2016Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億1990万ドル 2.2%Down

■IC Physical Design & Verification分野 3億7580万ドル 4.6%Up

■IP分野 6億8870万ドル 11.4%Up

■サービス分野 1億1160万ドル 6.9%Up

■PCB/MCM分野 1億6600万ドル 2.8%Up

2016年Q1の地域別の売上と昨年同時期との比較は以下の通り。

■北米 8億6300万ドル 1.1%Up

■ヨーロッパ 2億8980万ドル 4.1%Up

■日本 2億3430万ドル 11.9%Up

■アジアその他地域 5億7500万ドル 7.2%Up

2016.06.10

16th International Forum on MPSoC for Software-defined Hardware

開催期間:2016年7月11日〜15日

開催地:奈良ホテル

参加登録:http://www.mpsoc-forum.org/

Society sponsors:IEEE CAS, IEEE CEDA, EDAA

Industrial sponsors:Synopsys, ソシオネクスト, Arteris

世界最高峰のSoC・IT技術専門家60名以上の講演者を招き、次世代コンピュータシステ ムを構築する最新のSW・HW技術を5日間に渡り熱い議論を繰り広げます。皆様のご参加 をお待ち申し上げます。

MPSoC 2016 General Chair 一色 剛

MPSoC 2016ハイライト:

基調講演 (Keynote):

7/11: Zining Wu氏 (CTO, Marvel, USA)

7/12: 井上あまね氏 (President & COO, ソシオネクスト)

7/13: Charlie Janac氏 (CEO, Arteris, USA)

7/14: Sebastian Wedeniwski氏 (CTO, IBM, JAPAN)

7/15: Subramani Kengeri氏 (Vice President, GLOBALFOUNDRIES, USA)

招待講演 (In-depth presentation):

Doris Keitel-Schulz氏 (Infineon)

Yankin Tanurhan氏 (Synopsys)

廣田好彦氏、村上昌弘氏 (コニカミノルタ)

木村貞弘氏 (リコー)

Rolf Ernst氏 (TU Braunschweig)

Gabriel Loh氏 (AMD)

Jishen Zhao氏 (UC Santa Cruz)

Ren Wu氏 (Baidu Research Lab)

Jian Ouyang氏 (Baidu)

Daqi Ren氏 (Huawei)

中村裕氏 (IBM)

Xiaohua Kong氏 (Qualcomm)

Mario Traeber氏 (Intel)

Kees van Berkel氏 (TU Eindhoven)

John Goodacre氏 (ARM)

Kees Vissers氏 (Xilinx)

中村祐一氏 (NEC)

2016.06.10

2016年6月7日、米SIA(Semiconductor Industry Association)は、2016年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年4月の世界半導体売上は前年同月比6.2%減、前月比1%減の258億4000万ドルだった。これで売上の前年実績割れは10ヶ月連続となる。3月は5ヶ月ぶりに売上が前月実績を上回ったが4月は再び減少した。今年に入ってから単月売上は前年実績に対して平均6%減少しており、4月はついに2年前の2014年の売上実績を下回った。

2016年4月の世界半導体市場を地域別の売上で見ると、3月同様日本と中国以外の全ての市場が前年割れとなっており、北米市場の不振が特に依然目立っている。(北米市場は5ヶ月連続で前年比2ケタ減)

日本市場の売上はドルベースで前年比2.2%増、円ベースでは前年比約6%減で、円ベース換算の売上は約2859億円となっている。

なお、先ごろWSTSが発表した2016年春季半導体市場予測によると、今年の世界半導体市場は-2.4%のマイナス成長。日本はドルベースで-1.7%、円ベースで-6.3%のマイナス成長とされている。前回12月の秋季予測では2016年世界半導体市場は+1.5%の成長という予測だった。

2016.06.07

2016年6月2日、Synopsysはエンベデッド・ビジョン(Embedded Vision)向けのプロセッサIPコア「EVプロセッサ」の新製品「EV6x プロセッサ・ファミリー]を発表した。

Synopsysによると新製品「EV6xファミリ」は、既存の「EV5」ファミリの後継上位製品で、内部のアーキテクチャを変更しそのパフォーマンスは最大100倍にまで向上されているという話。それにより、高解像度監視カメラや車載のフロントカメラなどへの利用も可能になった。

CNN特化エンジンを搭載することにより、GPUを利用するソリューションとほぼ同等のパフォーマンスを数分の一の低消費電力で実現するというのがこの「EV6xファミリ」の特徴だ。

「EV6xファミリ」のアーキテクチャは、下の画像資料に示すように「EV5」に対して大きく変わった。ビジョン・プロセッサの部分は、32ビットのスカラユニットと512ビットのベクターDSPを組み合わせたコアを最大4個利用できる構成に。CNNエンジンの部分はオプションとなり(つまり不要であればビジョン・プロセッサ単体のみを利用可能)、これまでの最大8つのPE(processing element)を利用できる構成から、「Convolution」部と「「Classification」部に分かれた固定された構成に変更された。

※画像はEV6xの構成図

※画像はEV5の構成図

これらアーキテクチャの変更は、自由度よりもCNNエンジンのパフォーマンス向上に特化して実施されたもので、CNNエンジンの積和演算能力の向上やエンジン間のバンド幅の向上などによりそのパフォーマンスは大幅に向上。例えば、これまでの「EV5」ファミリが扱える動画はフルHD程度だったが新しい「EV6xファミリ」では4K動画も扱えるレベルになった。

更にもう一つ大きな変更点としては、「EV6xファミリ」ではCNNエンジンにインプリするディープ・ラーニングのトレーニング/ティーチング結果をユーザー自ら行えるよう専用のツール環境が用意された(これまではSynopsysに依頼する必要があった)。これにより、ユーザーはトレーニング/ティーチング結果の入れ替えや、CNN処理方法の変更などを手元で行えるようになる。

なお、ツール環境という面では、従来通りOpenCV, OpenVX, OpenCL, MetaWareといった各種標準フォーマットの言語、ライブラリ、ツールセットを利用する事が可能。ライブラリ類は年1回のペースでアップデートされており、今後も拡張されていく予定である。

Synopsysによると、新製品「EV6xファミリ」は既に2社が導入済みで量産を見据えた設計が進められているという。

※「EV6xファミリ」に関する詳細は8月23日開催予定のASIP関連のセミナーで紹介される予定(詳しくは日本シノプシスにお問い合わせ下さい)

2016.06.01

SystemC Japan 運営事務局よりSystemC Japan 2016開催のご案内です。

┌─────────────────────────────────┐

■■ SystemC関連企業が集結 6月17日(金) SystemC Japan 2016 開催!

■■ http://www.systemcjapan.com/SCJ2016/

■■

■■ 国内唯一、SystemCユーザーのための技術セミナー SystemC Japan

■■

■■【今年の見所】

■■ ・SystemCユーザーによる設計事例の講演

■■ ・基調講演:株式会社ソシオネクスト 長谷川 隆氏

■■ ・特別講演:株式会社エッチ・ディー・ラボ 長谷川 裕恭氏

■■ ・Accellera Systems InitiativeからのSystemC最新情報

■■

■■ 参加無料(昼食・レセプションパーティーをご用意)

■■ 定員200名、お申込よろしくお願い致します!

└─────────────────────────────────┘

今年で開催11周年となるSystemC Japan 2016は、システム記述言語「SystemC」にフォーカスした業界最大の技術セミナーです。

今年のSystemC Japan 2016は、Accellera Systems Inisiative主催の下、国内外10社のスポンサー企業が協力して開催致します。セミナーでは基調講演、設計者による事例講演、スポンサー講演の計10件のセッションを予定しております。

セミナー終了後には恒例のレセプション・パーティー(参加無料:事前登録制)も開催致します。

この機会に世界最大のSystemCユーザー・セミナー「SystemC Japan 2016」に是非足をお運び下さい。

SystemC Japan 2016 運営事務局

SystemC Japan 2016公式ページ→ http://www.systemcjapan.com/SCJ2016/

参加お申し込み→ http://www.systemcjapan.com/SCJ2016/privacy.html

-------------------------------------------------------------------------------

■セミナー開催概要

会期:2016年6月17日(金)

10:00-17:10(セミナー)、17:30-19:30(パーティー)

会場:新横浜国際ホテル 南館 〒 222-0033 横浜市港北区新横浜 3-18-1

セミナー会場:2F チャーチル、レセプション会場:3F クリスティ

※会場へのアクセス→http://sinyokohama.khgrp.co.jp/info/access.html

参加:無料(昼食付、事前登録制) 定員200名

※セミナーのお申し込みにあたり、「お申し込みにともなう個人情報の取

扱い」に同意いただく必要がございます

※当セミナーは設計現場のエンジニアの方の参加を優先しております。

所属や職種によりセミナーへの参加をご遠慮頂く場合がございますので、予めご了承下さい。

主催: Accellera Systems Initiative

メインスポンサー:

日本ケイデンス・デザイン・システムズ社

Magillem社

OneSpin Solutions社

協賛:

アルデック・ジャパン株式会社

株式会社インターバディ

ASTC株式会社

東芝情報システム株式会社

日本電気株式会社

株式会社プライムゲート

※セミナー公式Webページはこちら

http://www.systemcjapan.com/SCJ2016/

※セミナー参加企業の紹介はこちら

http://www.systemcjapan.com/SCJ2016/aboutshuttensha.html

※セミナーお申し込みはこちら↓

http://www.systemcjapan.com/SCJ2016/privacy.html

------------------------------------------------------------------------------

■■お問い合わせ

SystemC Japan 2016に関するお問い合わせは、下記窓口までお願い致します。

SystemC Japan 2016運営事務局 ?EDAエクスプレス info@eda-express.com

━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━

2016.05.23

2016年5月18日、Synopsysは、2016会計年度第2四半期(16年2月-4月)の四半期決算を報告した。

発表によると、Synopsysの2016会計年度Q2の売上は、前年同時期比約8.5%増の6億500万ドル、純利益は前年比約25%増の6900万ドルだった。(※GAAP基準による会計結果)

同社の四半期売上が6億ドルを超えるのは今回が初めて。

Synopsysはこの2月-4月の間に、カスタム設計向けの大型新製品「Custom Compiler」や自社の回路シミュレータ向けの共通の管理/解析環境を市場投入。また論理シミュレータ「VCS」の新たな並列処理テクノロジを発表している。

Synopsysは次の2016会計年度Q3(16年5月-7月)の売上を5億9500-6億1000万ドルと予測している。

2016.05.23

2016年5月19日、Mentor Graphicsは、2017会計年度第1四半期(16年2月-4月)の売上を報告した。

発表によると、Mentorの2017会計年度Q1の売上は、前年比約16%減の2億2700万ドル、約1200万ドルの営業損益を計上した。Mentorはここのところ売上不振が続いており、昨年度Q3から3四半期連続で売上額が前年実績を下回っている。

この2月-4月におけるMentorのニュースとしては、エミュレータ「Veloce」関連の話題が多かった。

Mentorは次期2017会計年度Q2(16年5-7月)の売上を2億4500万ドル程度と予測している。

2016.05.10

2016年5月2日、米SIA(Semiconductor Industry Association)は、2016年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年3月の世界半導体売上は前年同月比5.8%減、前月比0.3%減の260億9000万ドルだった。これで売上の前年実績割れは9ヶ月連続となるが昨年11月から続いていた単月売上の減少は5ヶ月ぶりに小休止となった。

2016年3月の世界半導体市場を地域別の売上で見ると、日本と中国以外の全ての市場が前年割れとなっており、中でも北米市場は前年比15.8%減と2月に続いて大幅に売上が減少した。北米市場が前年比2ケタ減を記録するのはこれで4ヶ月連続。市場規模首位の中国は、前年比1.3%増とかろうじて前年実績を上回った。

日本市場の売上はドルベースで前年比1.8%増、円ベースでは前年比4.6%減で、円ベース換算の売上は約2928億円となっている。

2016.04.28

2016年4月25日、Cadenceは、2016会計年度第1四半期(2016年1-3月)の売上を報告した。

Cadenceの2016年Q1売上は、前年同時期比約9%増、前期Q4比約1.5%増の4億4800万ドルで同社の四半期売上記録を更新。純利益は前年比約42%増の5100万ドルだった。(※GAAP基準による会計結果)

Cedanceによるとエミュレーターの新製品「Palladium® Z1」が好調との事。この1-3月においては、配置配線ツール「Innovus Implementation System」、Tensilica DSPコアに関するニュースが多かった。

Cadenceは、2016会計年度Q2の売上額を4億4500-5500万ドルと予測している。

2016.04.22

2016年4月20日、ARMは、2016会計年度第1四半期(2016年1-3月)の売上を報告した。

ARMの2016年Q1の売上は、前年比約14%増の3億9800万ドル、税引き前の純利益は約前年比約14%増の1億9800万ドルだった。売上額としては前記Q4を下回ったが、依然好調な業績を維持していると言える状況だ。

ARMのQ1売上の内訳を見ると、プロセッサ・ライセンスの売上、プロセッサ・ロイヤリティの売上ともに前年比2ケタの伸びを示した。全売上に対するロイヤリティ売上の占める割合は前Q4よりも増え54%となっている。

Q1におけるプロセッサ・ライセンスの契約数は39件で、最新のARMv8-Aアーキテクチャ・ベースのプロセッサのライセンス契約8件、GPU Maliのライセンス契約2件が含まれている。

2015年Q1で出荷されたARM搭載チップの総数は約41億個で前年よりも約10%増えた。

2016.04.13

2016年3月24日、米EDA Consortiumは、2015年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

EDACの発表によると2015年Q4(10-12月)の世界のEDA売上総額は、前年比1.5%減、前Q3比5.4%増の20億6450万ドルで、2010年Q1以来、23四半期ぶりに四半期売上が前年実績を下回った。

2015年Q4のEDA売上を製品分野別に見るとIP分野とサービス分野以外は前年実績を大きく割り込んだ。IP分野はこれまで7四半期連続で前年実績比2ケタ増を達成していたが、このQ4の売上は前年比9.2%増にとどまった。

2015年Q4のEDA売上を地域別に見ると、アジアその他地域以外は軒並み売上前年割れとなった。日本市場はQ3で売上2億ドル台に回復していたが再び1億ドル台に転落した。これは為替レートの変動による影響が大きい。

2015年Q4時点でのEDA業界の従業員数は前年比7.7%増の34169人で過去最高記録を更新した。

2015Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億4530万ドル 7.8%Down

■IC Physical Design & Verification分野 4億4460万ドル 8.1%Down

■IP分野 7億220万ドル 9.2%Up

■サービス分野 1億710万ドル 5.4%Up

■PCB/MCM分野 1億6530万ドル 6.2%Down

2015年Q4の地域別の売上と昨年同時期との比較は以下の通り。

■北米 9億650万ドル 3.1%Down

■ヨーロッパ 3億2320万ドル 1.7%Down

■日本 1億8930万ドル 8.4%Down

■アジアその他地域 6億4550万ドル 2%Up

※EDAC(EDA Consortium)

2016.04.12

2016年4月8日、Synopsysは、世界的な安全性の第三者認証機関UL(Underwriters Laboratories)による同社製品の採用事例を発表した。

ULは、様々な分野の製品安全規格を策定し、安全性の評価と認証を行う米国の営利企業で(2012年までは非営利組織として活動)UL認証マークの発行機関として世界的に知られている。

今回の発表によると、ULは新たに立ち上げたネットワーク接続機器向けのサイバー・セキュリティに関する安全性認証プログラム「UL CAP(Cybersecurity Assurance Program)」のセキュリティ・テストにてSynopsysのソフトウェア・セキュリティ・テスト・ツール群を採用。「UL CAP」は、米ホワイトハウスが国家のセキュリティ対策の一環として採用する信頼性の高い認証プログラムで、その認証のための作業にSynopsysのツール「Protecode」、「Coverity」、「Defensics」の3製品が利用されているという。

これらSynopsysのソフトウェア・セキュリティ・テスト向けのツールはいずれもここ数年のうちにSynopsysが買収により取り入れたソリューションで、Synopsysは新たな事業領域として、組み込みソフトウェア開発ならびにセキュリティ分野に対して積極的な投資を進めている。

2016.04.11

2016年4月6日、Cadenceは同社の旗艦製品の一つアナログ・カスタム設計環境「Virtuoso」プラットフォームのバージョンアップを発表した。※訂正あり

Cadenceが初のアナログ設計ツール「Analog Artist」をリリースしたのが1991年で、以降、同ツールをベースに確立されたアナログ・カスタム設計環境「Virtuoso」プラットフォームは今年で25周年を迎える。この25周年を記念して、Cadenceは今年「Virtuoso」のプロモーションに力を入れており、今回発表したバージョンアップはその大きな目玉として扱われている。

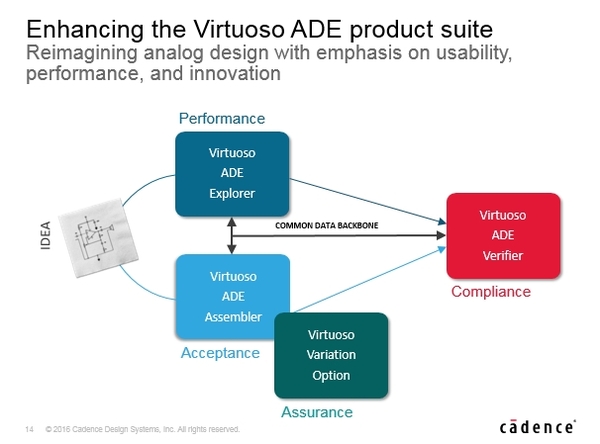

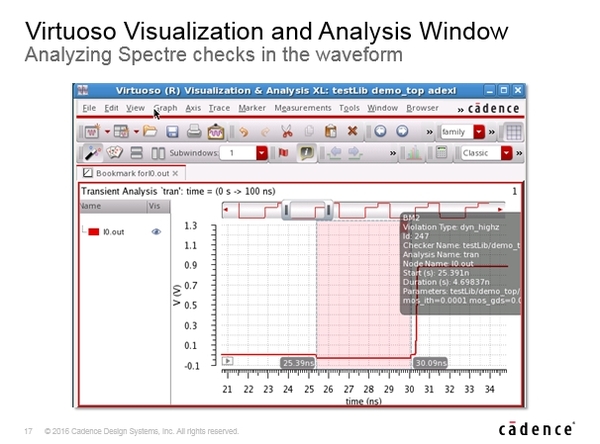

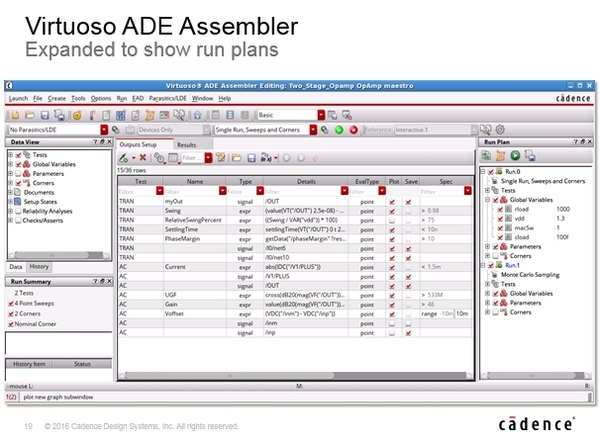

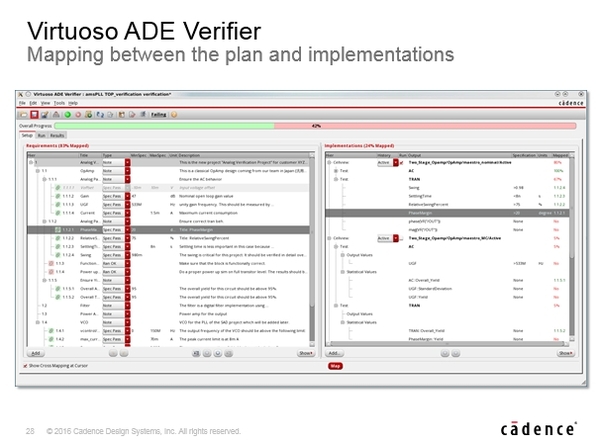

「Virtuoso」最新バージョン6.1.7では、同プラットフォームを構成するアナログ設計環境「Virtuoso ADE」が検証技術を中心に刷新され、レイアウト環境「Virtuoso Layout Suite」が大幅に機能強化された。

まず、アナログ設計環境「Virtuoso ADE」においては、次世代の製品ラインナップとして下記スライドの通り3つの新製品と1つのオプション機能が追加された。従来の「Virtuoso ADE」は、L,XL,GXLと製品の機能に応じて3種類のグレードが用意されていたが、新たに追加された各製品はそれぞれ独立した機能を担うものとなっている。

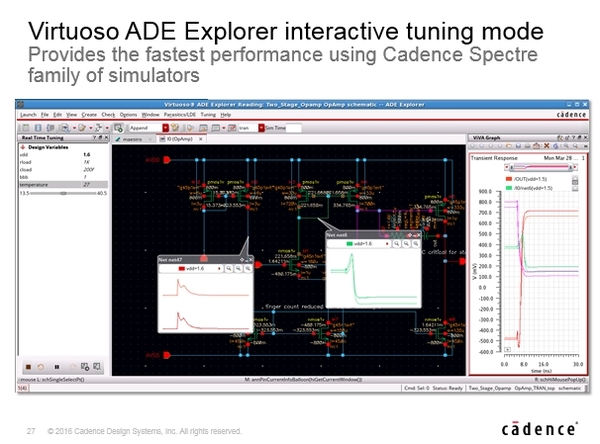

「Virtuoso ADE Explorer」は、アナログ回路の設計初期においてシングルテストベンチのコーナーケース・シミュレーションを行う環境で、オンメモリーでネットリストを再構築せずに回路のチューニングを行う事ができる「Interaractive device tuning mode」という機能を備えている。同機能を利用すれば、例えば回路の抵抗の値を変えた際の特性の変化(波形の変化)を瞬時に確認できる。(バックグラウンドでシミュレータSpectreが動いている)また、回路図上にワンクリックでノードの波形を示したり、アサートチェックや耐圧チェックなどの各種チェックをGUIベースで実施できるなど、ツール全体でグラフィカルな形で対話的かつ直感的な作業が可能となっている。

「Virtuoso ADE Assembler」は、マルチテストベンチの環境で、「Virtuoso ADE Explorer」で検証した回路を様々な入力や条件設定によってまとめてチェックする事ができる。検証のシナリオをGUIベースで簡単に管理できる機能を備えており、「Virtuoso ADE Explorer」と同じくグラフィカルな形で対話的かつ直感的に検証の順序や制御を細かく指示できる。

「Virtuoso ADE Verifier」は、「Virtuoso ADE Explorer」および「Virtuoso ADE Assembler」の検証結果を総合的に可視化する検証コックピットとしての環境で、複数の設計者のテストの項目や進捗を統合的に管理することができる。また自動車の機能安全規格ISO26262をはじめとする各種産業界の規格に対応する機能が備えられており、規格に準じたレポーティングなども「Virtuoso ADE Verifier」で対応可能だという。

なお、オプション機能「Virtuoso Variation Option」は、従来の「Virtuoso ADE GXL」に備えられていたものと同様の機能となる。

※画像は全てCadence提供のデータ

Cadenceが今回「Virtuoso ADE」の検証機能を大幅に強化した背景としては、自動車業界を中心とするトレーサビリティに対する要求やアナログ回路のより高精度な検証要求に対応するためで、ここ数年自動車業界でキーワードとなっている機能安全規格ISO26262が一つの大きなトリガーとなっている話だ。

ちなみに「Virtuoso」最新バージョン6.1.7では同ツール初の日本語対応がなされているという事だが、この辺りは日本の自動車業界を強く意識した対応と見て取れる。

アナログ検証環境と合わせて強化された「Virtuoso Layout Suite」は、L,XL,GXLという製品構成を維持しているが複数の機能強化が施されている。

まずレイアウト・エディタのエンジン・アルゴリズムが刷新され描画速度が10倍から100倍高速になった。これは同社の新たな特許技術によって実現されているという話で、エディタの高速化は設計者にとってはシンプルだが非常に大きなメリットと言える。また「Dynamic Measurement」と呼ばれる自動計測機能なども新たに用意された。

更にレイアウト関連の機能としては、回路の階層構造とレイアウトの階層構造を一致させる「階層制御」の機能が用意されたほか、「ModGen」と呼ばれる素子の自動配置機能が強化された。「ModGen」を利用すればインタラクティブかつ高速に指定したルールに沿って素子をアレイ化して自動配置する事が可能になるという。また、同じく新機能として追加された「pin-to-trunk」という機能は、電流の流れをみて「賢く自動配線」するものでアナログ回路に有効。配線の生産性を最大50%向上出来るほど効果があるという。

以上、上述した通り今回の「Virtuoso」のバージョンアップはかなり大掛かりなもの

となっており、「Virtuoso」プラットフォーム全体としての従来比10倍相当の性能向上を実現しているという話。先頃競合のSynopsysが新製品を投入したばかりだが、アナログ/カスタム設計環境の移行は同一ツールのバージョンアップでもかなりの時間と労力を要する事を考えると、これまでCadenceが築き上げてきた「Virtuoso」の牙城は今回の大幅な機能強化でより強固なものになるのかもしれない。

2016.04.08

2016年4月7日、各種設計IPを手掛ける米Arasan Chip Systemsは、MIPI Soundwire IPコアの新製品を発表した。

今回Arasanが発表したのは、「Soundwire Host IPコア」および「Soundwire Device IPコア」の両製品で、これらは同社の第二世代目のMIPI Soundwire IP製品として既に利用可能となっている。

新製品のMIPI Soundwire IPコアは、昨今市場に増え続けている各種ウルトラポータブルデバイスをターゲットに、小型かつ低レイテンシ、低消費電力をうたうもので、最新のSoundwire仕様の早期導入を目指す企業に相互運用性テストのためのハードウェア・デザイン・キットという形で提供される。

ArasanはMIPI仕様の規格開発団体MIPI Allianceの初期からのメンバーで、MIPI仕様に精通した技術力を背景に各種MIPI仕様のIPを製品化しており、既にワールドワイドで多数の実績を残している。今回発表したMIPI Soundwire IP以外にもUSB、UFS、SD、SDIO、MMC/eMMC、UFSなど各種デジタルIPコア、アナログPHYインターフェース、検証IP、ハードウェア検証キットなど幅広い製品を提供しており、同社のIPを利用した半導体製品は既に10億ユニットを超えているという。

なおArasan製品の日本国内の販売およびサポートは、今年3月からEDAツールの販売と各種設計サービスを手掛けるスタビリティ株式会社が担当している。同社は米Averant社のフォーマル検証ツールの日本総代理店でもある。

2016.04.05

2016年4月4日、米SIA(Semiconductor Industry Association)は、2016年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年2月の世界半導体売上は前年同月比6.2%減、前月比3.2%減の260億2000万ドルだった。これで売上の前年実績割れは8ヶ月連続となる。

2016年2月の世界半導体市場を地域別の売上で見ると、前月同様中国を除く全ての市場が前年割れとなっており、中でも北米市場は前年比19.3%減と大幅に売上が減少した。北米市場が前年比2ケタ減を記録するのはこれで3ヶ月連続で、景気の先行きを左右する北米市場の不振は半導体市場全体に影響を与えそうだ。市場規模首位の中国は、前年比では3.5%増となっているが、1月よりも売上を落としている。

日本市場の売上はドルベースでは1月比0.8%減、円ベースでは3.9%減で、円ベース換算の売上は約2831億円となっている。

2016.04.04

2016年3月31日、Synopsysはカスタム設計向けの新ツール「Custom Compiler」のリリースを発表した。

発表によると新製品「Custom Compiler」は、Synopsysの既存のカスタム設計ツール「Custom Designer」と「Laker」それぞれの優れた実績のある技術と、全く新たな自動化技術をベースに構築された新世代のツールで、かつて市場を一変させた幾つかの代表的なツールと同じく「Compiler」を冠した製品名となっている。Synopsysとしても相当気合の入った製品と見て間違いない。

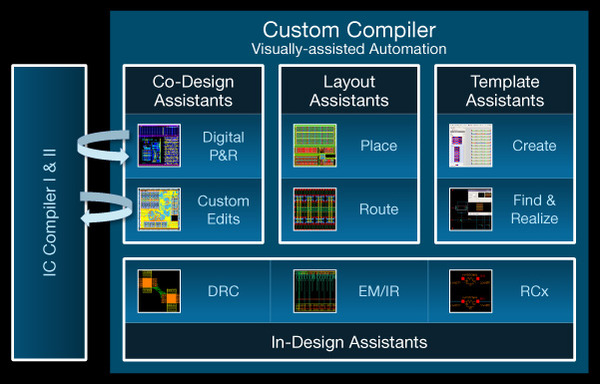

新製品「Custom Compiler」の最大の特徴は、「Visually Assisted Automation」と呼ぶグラフィカル・ベースの新たなカスタム設計自動化技術で、この技術は下記図にある通り大きく4つの自動支援機能によって実現されている。

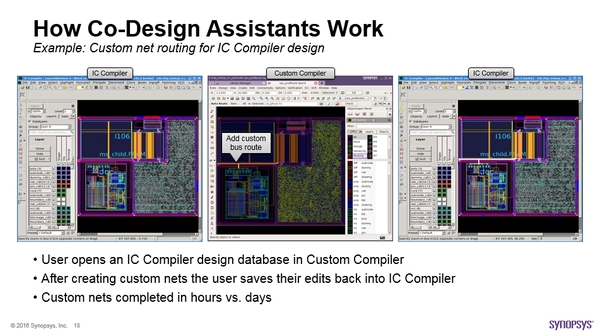

Co-Design Assistantsは、既存の製品と同じくデジタル設計の配置配線ツール「IC Compiler」との協調設計を効率化する機能で、デジタル設計とカスタム設計の間のデータの受け渡しやイタレーションを最少化する。

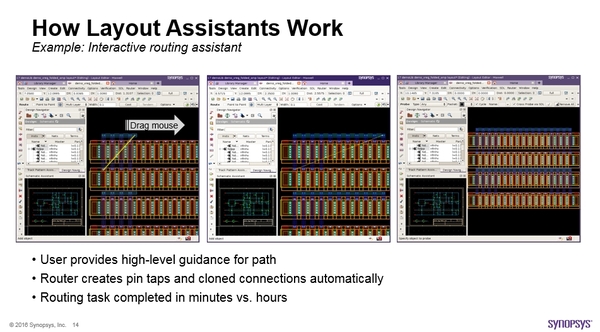

Layout Assistantsは、最新のFinFET技術にも対応するレイアウトの自動化機能で、設計者の意図する配線を自動処理することが可能。この機能は従来必要だったレイアウトに関する制約を記述するという作業を無くし、配線に関する工数を数時間単位から数分単位に削減できるという。

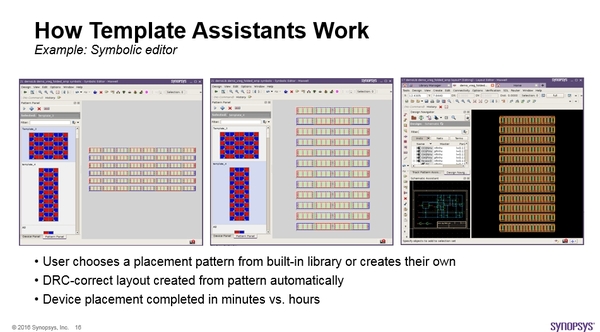

Template Assistantsは、Layout Assistantsと共にレイアウト作業を支援する機能で、予め登録されている汎用的な回路のレイアウト・パターンや、設計者が作成したレイアウト・パターンをテンプレートとして新たなデザインに再利用する事が可能。デザイン資産やノウハウを再利用する事でレイアウトの生産性を大幅に向上させる。

また、Template Assistantsには、「Custom Compiler」で作成したレイアウトを学習する機能が備わっており、既存の設計済回路と類似する回路をに認識し、テンプレートの再利用を賢く効率化してくれる。

In-Design Assistantsは、サインオフ検証前の設計段階でDRCやエレクトロマイグレーション・チェック、寄生容量抽出を行う機能で、搭載される専用エンジンによる事前のエラー・チェックによりサインオフ検証後の手戻りを削減してくれる。エレクトロマイグレーション・チェックと寄生容量抽出については、Synopsysの寄生容量抽出ツール「StarRC」と同じエンジンを使用しているという。(※デザイン容量など制限はあり)

※画像は全てSynopsys社提供のデータ

今回Synopsysが「Custom Compiler」を市場投入してきたモチベーションは、FinFET技術によって現れた新たなカスタム設計の課題解決で、既存製品「Laker」のFinFETレイアウト技術を足掛かりに大胆な自動化アプローチでFinFET市場の攻略を狙っている。カスタム設計ツールの市場はCadenceが長年の間強さを維持しているが、既にTSMCが10nm/7nm FinFETプロセスで「Custom Compiler」を認証するなど、うかうかしていられない状況になってきている。

なお、「Custom Compiler」は正式出荷が開始されており、国内の旭化成エレクトロニクスをはじめとして既に国内外の先行ユーザーによる導入が進んでいる。

2016.03.08

2016年3月3日、米SIA(Semiconductor Industry Association)は、2016年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年1月の世界半導体売上は前年同月比5.8%減、前月比2.7%減の268億8000万ドル。7ヶ月連続で前年実績を下回る結果となった。

2016年1月の世界半導体市場を地域別の売上で見ると、中国を除く全ての市場が前年割れとなっており、北米市場は12月に続いて前年比16.9%減と2ヶ月連続で前年比2ケタ減を記録した。唯一気を吐く中国も12月の売上は下回ったが、さほど大きな変動はなく市場規模首位を維持している。

日本市場の売上はドルベースでは12月比3.3%減だが、このところの為替レートの変動により12月よりも円ベースでは6%以上売上が減少しており、円ベース換算の売上は約2933億円となっている。

2016.03.07

2016年3月3日、Mentor Graphicsは、2016会計年度第4四半期(15年11月-16年1月)の売上を報告した。

発表によると、Mentorの2016会計年度Q4の売上は、前年比約23%減の3億3730万ドル、営業利益は前年比43%減の7945万ドルだった。この実績は前Q3実績報告時の予測通りだが、同社のQ4売上が4億ドルを下回るのは3年振りで、前Q3に続いて2四半期連続で売上額が前年実績を下回った。

なお同社の2016会計年度の売上合計額は、前年比約5%減の11億8100万ドル、営業利益は前年比約27%減の1億3670万ドルという結果だった。(※GAAP基準による会計結果)

数字を見るとこれまで安定して継続してきたMentorの成長に異変が生じ始めているのは確かだが、Mentorのチェアマン兼CEOのWalden C. Rhines氏も指摘する通り、自動車業界における業績が好調である事は同社の長期展望にとって明るい兆しと言える。

Mentorは次期2017会計年度Q1(16年2-4月)の売上を2億2000万ドル程度と予測している。

2016.02.26

2016年2月17日、Synopsysは、2016会計年度第1四半期(15年11月-16年1月)の四半期決算を報告した。

発表によると、Synopsysの2016会計年度Q1の売上は、前年同時期比約5%増の5億6860万ドル、純利益は前年比約8%減の6000万ドルだった。(※GAAP基準による会計結果)

Synopsysはこの11月-1月の間に、オープンソース・ソフトウェア管理ソリューションのProtecode社と静的コード解析ツールのGoanna社を買収、更にセキュリティ分野の人材を拡充するなど、EDAおよびIPソリューション以外の新規分野への投資が目立った。

Synopsysは次の2016会計年度Q2(16年2月-4月)の売上を5億9500-6億1000万ドルと予測している。

2016.02.19

2016年2月17日、Mentor Graphicsは、同社の電装システム設計ツール「Capital」を米自動車メーカーGM社が採用した事を発表した。

発表によると、GMは今後の同社の新型車両の電装システムを「Capital」で設計するという事で「Capital」を標準採用した格好。同社では、Mentorのコンサルティングチームが開発したユーティリティを使って既存車両の設計データをCapital用に変換したり、オンデマンドトレーニングを活用してツール利用者のスキルアップを図るなど、標準採用に対する取り組みも進めているようだ。

「Capital」は自動車の電装システム開発を包括的にカバーする業界唯一の統合開発環境で、ハーネス製造や車両保守整備なども含めた形で開発プロセス全体の最適化と低コスト化を図る事が可能。ここ最近の車載電装システムの複雑化に伴い「Capital」を導入する企業が増えている。