NEWS

2017.07.11

2017年7月6日、米ESD Allianceは、2017年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると2017年Q1(1-3月)の世界のEDA売上総額は、前年比約10.5%増の21億6750万ドル。さすがに前Q4の売上を上回る事はなかったが、Q4に続いて前年比2ケタ増と好調を維持した。

2017年Q1のEDA売上をカテゴリ別に見ると、サービス分野以外全ての分野で売上が前年実績を上回った。売上2大柱のCAE分野、IP分野はともに前年比14%増を超える伸びを示した。

2017年Q1のEDA売上を地域別に見ると全ての地域で売上前年比2ケタ増を達成。北米市場は初の10億ドル超えを果たし、その他の地域は軒並み前年比20%増を超える成長を示した。日本市場の売上については円ベースで換算すると前年比約8%増で248億5000万円程度となる。

2017年Q1時点でのEDA業界の従業員数は前年比7.8%増の37195人で前Q4に続いて過去最高記録を更新した。

2017Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 7億740万ドル 14.1%Up

■IC Physical Design & Verification分野 3億9600万ドル 5.4%Up

■IP分野 7億9050万ドル 14.8%Up

■サービス分野 1億360万ドル 7.2%Down

■PCB/MCM分野 1億6990万ドル 2.4%Up

2017年Q1の地域別の売上と昨年同時期との比較は以下の通り。

■北米 9億6070万ドル 11.3%Up

■欧州 3億780万ドル 6.2%Up

■日本 2億3370万ドル 0.3%Down

■アジアその他地域 6億6520万ドル 15.7%Up

2017.07.04

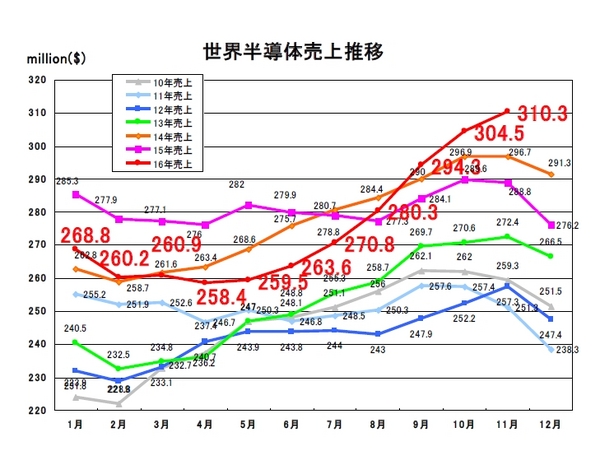

2017年7月3日、米SIA(Semiconductor Industry Association)は、2017年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2017年5月の世界半導体売上は前年同月比22.6%増、前月比2%増の319.3億ドルで5月に更新したばかりの単月売上額の記録をまたもや更新した。単月売上が前年実績を上回るのはこれで10ヶ月連続。今年に入り1月から5月まで全ての月で前年比2ケタ増の売上を記録している。これは今年の市場の活況と昨年前半の市場停滞の両側面によるもの。最新のWSTSの2017年春季半導体市場予測では、今年の市場成長率は前年比11.5%増とされている。

2017年5月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。4月同様、中国市場と北米市場は他の地域を凌ぐ伸びを見せた。中国市場は昨年12月から6ヶ月連続で前年比20%を超える売上増を記録している。

日本市場の売上も好調で、ドルベースで前年比15.8%増、円ベースで前年比19.4%増を記録。円ベース換算の売上は約3320億円となっている。

2017.06.14

2017年6月2日、Synopsysは、コニカミノルタが同社のエミュレーション・システム「ZeBu Server」を採用した事を発表した。

発表によるとコニカミノルタは、MFP向けSoCのハードウェア検証ならびに早期ソフトウェア開発にSynopsysのエミュレーター「ZeBu Server」を活用。同社は古くから「ZeBu」シリーズ製品のユーザーで定期的に最新の「Zebu」環境を導入している。その経験・ノウハウの蓄積によるところが大きいと想像されるが、コニカミノルタでは「ZeBu」を用いてブロック、チップ、マルチチップ・デザインの検証を実行しているほか、ソフトウェア開発においては、「ZeBu」により実チップ完成の数ヶ月前からソフトウェア開発に着手可能となっているという。

なお聞くところによると、Synopsysの「ZeBu」はワールドワイドで順調にユーザーを増やしており、エミュレーター市場においてトップシェアを争う程になっているようだ。

※画像はSynopsys社Web上のデータ

2017.06.14

2017年6月12日、IP-XACTベースのESLソリューションを手掛ける仏Magillemは、ルネサスエレクトロニクスが同社のEDAツールを採用した事を発表した。

発表によるとルネサスは、ハードウェアおよびソフトウェアの両分野の製品開発においてMagillemのEDAツールを採用。MagillemのIP-XACTベースのESLツールを用いることで開発の自動化環境の構築を実現するという。

Magillemは、IP-XACTとSystemCをベースとした、システムレベルの設計、検証、プロトタイピング環境と、各種ドキュメント生成およびトレーサビリティ管理のためのツールを提供している。

ルネサスは6月28日にフランス大使館で開催されるMagillemのユーザーセミナーでMagillemのツールを用いたMCU設計事例を紹介する予定。

2017.06.12

2017年6月6日、米SIA(Semiconductor Industry Association)は、2017年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2017年4月の世界半導体売上は前年同月比20.9%増、前月比1.3%増の313億ドルで単月売上額として過去最高を記録した。単月売上が前年実績を上回るのはこれで9ヶ月連続となる。半導体市場の活況を踏まえ、今年5月末に発表されたWSTSの2017年春季半導体市場予測では、今年の市場成長率の予測を前年比11.5%増と上方修正している。(2016年秋季予測では3.3%増と予測)

2017年4月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。中でもここ数ヶ月好成長を続けている中国市場と北米市場がそれぞれ前年比30%増、前年比26.9%増と驚異的な伸びを見せた。中国市場は昨年12月から5ヶ月連続で前年比20%を超える売上増を記録している。

日本市場の売上も好調で、ドルベースで前年比12%増、円ベースで前年比12.4%増を記録。円ベース換算の売上は約3200億円となっている。

2017.05.26

2017年5月24日、Synopsysは、組込みプロセッサの新製品「ARC HS4x/HS4xD」を発表した。

新製品「ARC HS4x/HS4xD」ファミリは、ハイエンド組込みプロセッサ「ARC HS」ファミリの最上位機種で、パフォーマンスの高さが最大の特徴。計5種類ラインナップされる各プロセッサは、それぞれシングル/デュアル/クワッド・コアのコンフィギュレーションが可能で、1コアあたり2.5GHzで6000DMIPS、クラスターあたり最大24000DMIPSで命令を実行できる。

「ARC HS4xD」の「D」は恐らくDSPを意味するもので、同ファミリの「HS45D/HS47D」はDSPハードウェアを搭載。150超のDSP命令を実行でき、既存の「ARC HS3x」と比較して2倍の処理性能を誇る。また同ファミリは、超ローパワー・プロセッサ「ARC EMxD」ファミリと互換性があり、同じ命令セットを使用可能である。

※画像はSynopsys社Web上のデータ 「ARC HS4xD」のブロック図

Synopsysによると、「ARC HS4x/HS4xD」ファミリは、16nm FinFETプロセスで実装した場合、面積はわずか0.06mm2、電力は37ミリワット/MHzと小面積/低消費電力を実現。ソフトウェア開発の面でもDual-issueパイプラインのサポート、最適化済みDSPライブラリの提供、C/C++コンパイラの強化など開発環境が強化されており、最小限のコード量で最大限の性能を実現できる。

新製品「ARC HS4x/HS4xD」ファミリは、今年6月より出荷が開始される予定。

2017.05.22

2017年5月8日、オープンソースの命令セットRISC-Vをベーストしたプロセッサ・コアを手掛ける米SiFiveは、資金調達第二ラウンドで投資家から850万ドルを調達した事を発表した。

発表によると今回SiFiveの資金調達をリードしたのは、Sutter Hill Ventures、Osage University Partners、Spark Capitalの3社で、SiFiveの累計調達額は1350万ドルとなった。

SiFiveはRISC-Vの発明者らが2015年に設立したファブレス半導体ベンダで、RISC-VベースのSoCおよびIPコアを提供している。2016年11月に業界初のRISC-VベースのSoCの出荷を開始し、今月始めには「Coreplex IP」と呼ぶIPコアをリリースしている。このIPコアは、NDA契約不要ですぐに入手・評価可能で、コアの使用にあたりロイヤリティは発生しない。

現在「Coreplex IP」としては、「E31」および「E51」と呼ばれる二種類のコアが提供されており、「E31」はARMのCortex-M3,M4、「E51」はARMのCortex-A53に対抗できる製品とされている。

2017.05.20

2017年5月17日、Synopsysは、2017会計年度第2四半期(17年2-4月)の四半期決算を報告した。

発表によると、Synopsysの2017会計年度Q2の売上は、前年同時期比約12.4%増の6億8010万ドルで四半期売上記録を更新。純利益は前年比約23%減の5330万ドルだった。(※GAAP基準による会計結果)

Synopsysは5四半期連続で四半期売上記録を更新している。

Synopsysはこの2-4月の間に、配置配線ツール「IC Compiler II」の最新バージョン、車載向けプロセッサ「DesignWare® ARC® EM Safety Island IP ファミリー」、仮想プロトタイピング・システム「Platform Architect」の最新バージョンなどをリリースしている。

Synopsysは次の2017会計年度Q3(17年5-7月)の売上を6億6500-6億6800万ドルと予測している。

2017.05.19

2017年5月19日、日本で初めての開催となるDVCon Japan 2017の参加登録がスタートした。

DVCon(Design and Verification Conference)は、システムレベルの設計、モデリング、および検証に関する標準規格を作成、推進する米国の非営利組織Accelleraが主催する世界的なイベントで、エレクトロニクス製品の設計および検証に焦点を当て、業界で最も包括的な技術プログラムを提供しています。

北米では25年以上の歴史を持つ同イベントは、欧州、インドでも開催されており、今年新たに中国および日本でも開催する事になりました。

初開催となる「DVCon Japan 2017」は、SystemCトラック、Verificationトラック、LPB(LSI Package Borad)トラックの3トラック構成で多彩な技術セッションを実施致します。

DVCon Japan 2017 開催概要

会期:2017年6月30日(金)セミナー 9:30?17:30、懇親パーティー 17:50?19:30

参加:無料 *昼食付き、懇親パーティー先着200名様

主催:Accellera Systems Initiative

スポンサー:

アルデック・ジャパン(株)

アンシス・ジャパン(株)

Australian Semiconductor Technology Company(株)

(株)アストロン

日本ケイデンス・デザイン・システムズ社

(株)CDC研究所

CMエンジニアリング(株)

COSEDA Technologies GmbH

富士ソフト(株)

(株)ジェム・デザイン・テクノロジーズ

(株)インターバディ

(株)ジーダット

(一社)JEITA 半導体&システム設計技術委員会

MAGILLEM Design Service

メンター・グラフィックス・ジャパン(株)

日本電気(株)

日本ワンスピン・ソリューションズ(株)

(株)PALTEK

(株)プライムゲート

S2Cジャパン(株)

SmartDV Technologies

日本シノプシス(合)

東芝情報システム(株)

(株)図研

※DVCon Japan 2017のセミナー内容はこちら

2017.05.17

2017年5月17日、Cadenceは、同社の「VirtuosoR Analog Design Environment (ADE)」製品群に関するMathWorks/MATLABとの提携拡充を発表した。

発表によるとCadenceとMathworksの両社は、「Virtuoso ADE」と「MATLAB」の緊密な統合を実現。これにより両プラットフォーム間でシームレスにデータを共有することが可能になり、双方向で大規模なデータマイニングや解析を高速化できるようになった。

例えば、MATLAB Toolboxおよび言語を使用して容易に複雑なデータ演算を実行したり、シミュレーション結果を解析・可視化したりといった作業を「Virtuoso ADE」と「MATLAB」いずれの環境でも可能となるほか、2つのツールに分担させて実行することが可能となるという。

両ツールのユーザーであるAllegro Microsystems社は、今回の「Virtuoso ADE」と「MATLAB」の統合により、アナログ領域の徹底的な検証が可能となり開発期間を短縮できるようになったとコメントしている。

2017.05.17

2017年5月8日、Cadenceは新製品となるニューラルネットワークDSP IPコア「Tensilica® Vision C5 DSP」を発表した。

「Tensilica® Vision C5 DSP」は、HWアクセラレータではなくスタンドアローンでニューラルネットワーク処理を実行可能なDSP IPで、自己完結型のニューラルネットワークDSPという意味で業界初の製品となる。

「Tensilica® Vision C5 DSP」の強みはニューラルネットワーク処理を用いるビジョン、レーダー/ライダー、センサーフュージョンなどのアプリケーション向けに最適化されたアーキテクチャを採用している点で、以下のような特徴を持つ。

・畳み込み関数だけでなく、あらゆるニューラルネットワークの演算層(畳み込み、全結合、プーリング、正規化)を高速化可能

・「Tensilica® Vision C5 DSP」が推論タスクを実行する間メインのビジョン/イメージングDSPを解放可能

・ニューラルネットワークDSPとメインのビジョン/イメージングDSP間のデータ転送が不要

これにより、毎秒1テラMACという高い演算性能とともに高い電力効率を実現(電力効率GPU比最大10倍)。シリコン実装面積は1平方ミリメートル以下に収まる。

※画像は全てCadence提供のデータ

Cadenceのベンチマーク結果では、市場で入手可能なGPUと比較して「Tensilica® Vision C5 DSP」による処理の方が、AlexNet CNNで最大6倍、Inception V3 CNNで最大9倍高速だったという事だが、CadenceはGPUとの比較よりも、電力効率、開発のし易さ、プログラマブル性など、ハードウェア・アクセラレータに対する優位性を強調している。

「Tensilica® Vision C5 DSP」は現在先行顧客とプロジェクトを進行中との話。

2017.05.16

2017年5月8日から11日の4日間、中国、上海にて第6回RISC-V Workshopが開催された。

中国でRISC-V Workshopが開催されるのは今回が初。上海交通大学とNVIDIAが共同でホストを務めた。

RISC-V Workshopが初めて開催されたのは2015年の1月で、わずか2年半の間に計6回の開催とその盛り上がりを表している。今回のWorkshopには、EDA系からCodasip社が参加。「Automated RISC-V Verification Flow Utilizing Simulation, Formal, and Emulation Technologies」というタイトルで発表した。その他にMicrosemiやSiFiveといったRISC-Vベースのチップビジネスを手掛ける企業も発表している。

日本国内では未だRISC-Vにフォーカスしたイベントは聞いた事が無いが、毎年10月に開催されているDesign Solution Forumにおいて、今年はRISC-V関連のセッションが複数計画されている。

2017.05.16

2017年4月26日、Synopsysは同社のエミュレータ「ZeBu」の顧客成功事例を発表した。

今回Synopsysが発表したのは、米Wave Computing社によるエミュレータ「ZeBu® Server-3」の成功事例。Wave Computingは独自のデータフロー・アーキテクチャによる機械学習の高速化ソリューションを手掛ける企業で、同社のデータフロー・プロセッシング・ユニット(DPU)アーキテクチャ向けソフトウェアの早期開発に「ZeBu® Server-3」を活用し、開発期間を1年短縮する事に成功した。

Wave Computingが「ZeBu® Server-3」を選択した決め手はその処理速度で、同社曰く「ZeBu® Server-3」は他社のエミュレーション・システムと比べて4倍の高速処理を実現。

Wave ComputingのDPU搭載SoCは、16nm設計で動作性能6.7GHz、60億トランジスタ、HMCメモリーへの高速アクセスを行うという先端チップで、同チップの検証環境に「ZeBu® Server-3」を組込み量産チップのテープアウトを待たずして、Linux上で動かすソフトウェア・スタック全体の開発とデバッグを実行したという。

2017.05.15

2017年5月8日、車載システム開発向けの各種ソリューションを手掛けるイーソルトリニティは、ARM社と販売代理店契約の締結を発表した。

発表によるとイーソルトリニティは、ARMとの代理店契約によりARMの「ARM® Fast Models」のライセンス販売を開始。「ARM® Fast Models」を用いたバーチャル・プラットフォーム構築やバーチャル・プラットフォームで利用するペリフェラルモデル開発などのエンジニアリング・サービスも開始する。

なお、イーソルトリニティは、バーチャル・プラットフォームを手掛ける英Imperasとも代理店契約を結んだばかりである。プレスリリース文

Imperasはバーチャル・プラットフォームの老舗と言えるツールベンダで、最近はオープンソースの命令セットアーキテクチャ「RISC-V」のモデル開発に力を注いでいる。

2017.05.15

2017年4月26日、マルチコア・システム向けのソフトウェア開発ツールを手掛けるSilexicaは、同社の「SLX Tool Suite」のバージョンアップを発表した。

Silexcaの「SLX Tool Suite」は、マルチコア・システム向けのソフトウェア開発ツールで、シングルコア向けのコードをターゲットのマルチコア・システム向けに自動分割/マッピングしてくれるというツール。パフォーマンスや消費電力に関する高度な解析機能を有しており、ハードウェアリソースに最適なソフトウェアをほぼ自動で開発する事ができる。

今回のバージョンアップでは、「SLX Tool Suite」に新たなキャッシュ解析機能が登載され、より高度なメモリの階層設計が可能となった。また、車載システム開発に特化した「SLX Automotive Developmentパッケージ」も利用可能となった。

2017.05.12

2017年4月24日、富士通研究所は、Deep Learningの学習用ハードウェアの電力効率を向上させる回路技術を開発した事を発表した。

発表によると今回富士通研究所が開発したのは、Deep Learningの学習過程において、演算器のビット幅や学習結果を記録するメモリのビット幅を削減して電力効率を向上させる回路技術で、演算に用いるデータのビット幅を削減した独自の数値表現と、Deep Learningの学習演算の特徴をもとに、演算器の動きを随時解析しながら学習に必要十分な演算精度を保つように小数点の位置を自動的に制御する演算アルゴリズムを用いている。

富士通研究所は、開発した技術を実装したDeep Learning学習用ハードウェアを想定したシミュレーションで、LeNetとMNISTのデータセットを用いて学習を行い、32ビット浮動小数点演算での学習結果98.90%の認識率に対し、16ビットで98.89%、8ビットで98.31%の認識率で学習できることを確認したとしている。

富士通研究所によると、32ビットから8ビットにビット幅を削減することで、演算器やメモリの消費電力を約75%削減できるという。

富士通研究所では、開発した技術を富士通のAI技術「Human Centric AI Zinrai(ジンライ)」の一つとして2018年度の実用化を目指す。

2017.05.12

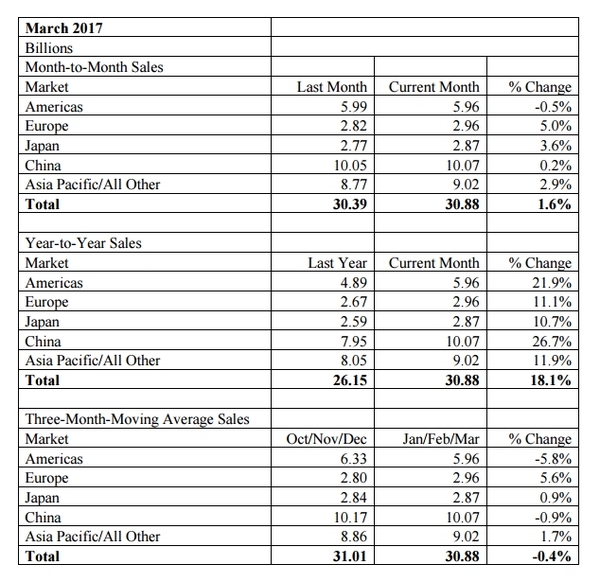

2017年5月1日、米SIA(Semiconductor Industry Association)は、2017年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2017年3月の世界半導体売上は前年同月比18.1%増、前月比1.6%増の308億8000万ドルで3月の単月売上記録を更新。8ヶ月連続で前年実績を上回った。昨年上半期の市場停滞に今年の活況が重なり、今年に入り3ヶ月連続で前年売上比2ケタ増を達成している。

2017年3月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。2月も好調だった中国市場と北米市場は共に前年比20%台の売上増となった。中国市場は政府による半導体強化政策を背景に、昨年12月から4ヶ月連続で前年比20%を超える売上増を記録している。

日本市場の売上も好調で、ドルベース/円ベースともに前年比10.7%増を記録。円ベース換算の売上は約3243億円となっている。

2017.04.27

2017年4月25日、ARMは新製品となる画像処理プロセッサ「ARM Mali-C71」を発表した。

「ARM Mali-C71」は、ARMが新たに打ち出す「Mali Cameraファミリー」の最初の製品で、クルマに搭載されるADAS向けの利用を想定して開発されたISP(画像処理プロセッサ)となる。そのため、一般的なモバイル・デバイス向けのISPとは違い以下のような仕様上の特徴がある。

画質:

・最大24ストップの超ワイドダイナミックレンジ(UWDR)を提供

・ノイズを削除し、カメラの複数の露出を処理してUWDRフレームを作成

信頼性:

・ISO26262、ASIL D、IEC 61508、SIL3などの機能安全規格に適合

・各規格のセーフティパックが提供される予定

・300以上の専用障害検出回路により、低レイテンシで高度なエラー検出機能を実現

・自動ホワイトバランス、自動露出を制御するフルリファレンスソフトウェアを提供(予定)

・ASIL適合向けの総合的な車載ソフトウェアを開発する計画

データ処理機能

・1つのハードウェアIPで、単一の画像処理パイプラインから、異なる方法で処理した2つの出力を生成可能

2017.04.27

2017年4月18日、Samsung Electronicsは、同社二世代目の10nm FinFETプロセス「10LPP (Low Power Plus)の生産準備を完了した事を発表した。

Samsungによると、「10LPP」は第一世代の「10LPE」プロセスと比べて、最大10%のパフォーマンス、15%の低消費電力を実現するという。

10nmプロセスの開発レースはSamsung,Intel,TSMCの3社がしのぎを削っているが、第二世代目の量産プロセスを立ち上げたのはSamsungが初。Samsungは自社のSoC「Exynos 9」やQualcommのSoC「Snapdragon 835」などを既に「10LPE」で量産中。TSMCはMediaTek, Huawei, AppleのSoCを10nmプロセスで量産する。対するIntelは未だ10nmプロセスでの量産開始には至っていないが、自社の10nm FinFETプロセスのトランジスタ搭載密度は競合の倍であると主張している。

2017.04.26

2017年4月25日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、新製品「Arria 10 Single Prodigy FPGA Prototyping Logic Module」の出荷を発表した。

S2Cの新製品「Arria 10 Single Prodigy FPGA Prototyping Logic Module」は、その名の通りIntel製の20nm FPGA「Arria 10」を搭載するプロトタイピング・ボードで、同ボードとパワー・コントロール・システム、電源ユニットを収納するシステム筐体は奥行き220mm,幅275mm,高さ94mm,とS2C曰く業界最小サイズ。

主な仕様は以下の通りとなっている。

・LE数:1150K個

・メモリ:53Mbps、M20K

・DSPリソース:3036個

・16Gbpsで動作する48ギガビットのトランシーバ

・4つのProdigyコネクタを介した576個の高速I/O

※画像は全てS2C提供のデータ

S2Cによると、「Arria 10 Single Prodigy FPGA Prototyping Logic Module」は、複数ボードを接続して更なる大容量を実現できるほか、同社既存の80種以上のドータカードを利用する事が可能。デザインのFPGA実装においては、OpenCLベースのIntelのSDKと互換性を持つ。

また、「Arria 10 Single Prodigy FPGA Prototyping Logic Module」は、S2C既存の各種プロトタイピング向けオプション機能にも対応可能。製品は既に出荷が開始されている。

2017.04.26

2017年4月24日、Cadenceは、2017会計年度第1四半期(2017年1-3月)の売上を報告した。

Cadenceの2017年Q1売上は、前年同時期比約6.4%増、前期Q4比約1.7%増の4億7700万ドルでQ4に続いて同社の四半期売上記録を更新した。純利益は前年比約33%増の6800万ドルだった。(※GAAP基準による会計結果)

この1-3月におけるCadenceのニュースとしては、Tensilica DSPコア関連と機能検証ソリューション関連が多かった。新製品としては並列機能シミュレーター「Xcelium Parallel Simulator」とFPGAプロトタイピング・システム「Protium S1」を発表した。

Cadenceは、2017会計年度Q2の売上額を4億7000-8000万ドルと予測している。

2017.04.21

2017年4月17日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、オープンソースのCPUエミュレーター「QEMU」を用いたHW-SW協調検証ソリューションを中国で開催されたDVcon Chinaで発表した。

AldecのアプローチはQEMUと同社のFPGAベースのプロトタイピングボード「HESボード」を繋げるというもので、そのために独自のQEMUブリッジを用意した。

QEMUはAldecに限らず複数のEDAベンダが自社のソリューションに取り込んでおり、例えばMentorの「VISTA」やASTCの「VLAB」などがシステムレベル・シミュレーション用のCPUモデルとして利用可能としていた。

現在、ARMに限らずXilinxのZynqや最近流行りのRISC-Vなど、多数のQEMUモデルが存在している。

話は逸れるが中国で開催されたDVCon Chinaは、米Accelleraが主催するワールドワイドなセミナー中心のイベントで、北米では25年の歴史を持つ。既に欧州、インドでも開催されており、今年は中国に続いてDVCon Japanも6月30日に開催される。

AldecはDVCon Japanにも出展予定なので、今回発表したQEMU&HESベースの協調検証ソリューションの展示を目にする事が出来るかもしれない。

2017.04.21

Wired誌によるGoogleの「TPU(Tensor Processing Unit)」に関する記事。

2017.04.21

2017年4月19日、XilinxはAmazonの提供するクラウドコンピューティングサービズ「AWS EC2」において、同社の16nm FPGA 「Xilinx Virtex UltraScale+」が利用可能となった事を発表した。

今回Xilinxの16nm FPGAが利用可能となったのは「AWS EC2 F1インスタンス」で、一つのインスタンスあたり最大8個のFPGAが利用可能。使えるFPGAの品種は「VU9P」でLE数約250万、DSPスライスは約6800、ローカルメモリ64GiB(DDR4 ECC)、専用PCIeインタフェース×16を備える。

また、「F1インスタンス」には、Xilinxの開発ツール「Vivado」をはじめとする各種開発ツールが含まれている開発環境「FPGA Developer AMI」とサンプルコードやスクリプトなどが含まれているハードウェア開発キット(HDK)が用意されており、コーディング、シミュレーション、デバッグ、コンパイルといった一連のFPGA開発を全てAWS上で行う事ができる。

「AWS EC2 F1インスタンス」でできる事については、下記のAWSのWebページに情報が出ている。

https://aws.amazon.com/jp/ec2/instance-types/f1/ (AWS EC2 F1インスタンスプレビュー)

https://aws.amazon.com/jp/blogs/news/ec2-f1-instances-with-fpgas-now-generally-available/ (AWSブログ)

なお、AWSの運用サポートを生業とするクラブメソッド社の情報サイトには、既にAWS上でVivadoを動かしてみたという記事も掲載されている。

http://dev.classmethod.jp/cloud/aws/aws-f1-fpga-developper-ami/

2017.04.20

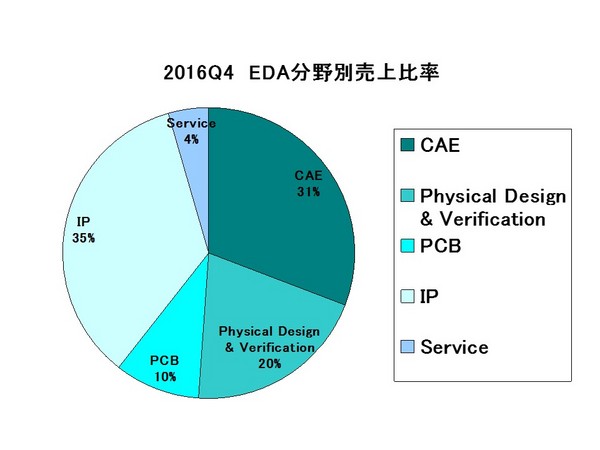

2017年3月27日、米ESD Allianceは、2016年度第4四半期(10月-12月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2016年Q4(10-12月)の世界のEDA売上総額は、前年比約18.9%増、前Q3比約17.2%増の24億5500万ドルでEDA売上市場過去最高だった。

2016年の合計売上は83億8350万ドルで前年比約10.8%増となる。

2016年Q4のEDA売上をカテゴリ別に見ると全ての分野で売上が前年実績を上回った。IP分野は遂に8億ドル超えで前年比22%増と驚異的な伸びを示した。また、Q3では前年実績を割り込んでいたPCB分野が突如前年比42.5%増と特異な伸びを示した。

2016年Q4のEDA売上を地域別に見ると全ての地域で売上前年比2ケタ増を達成。北米市場は初の10億ドル超えを果たし、その他の地域は軒並み前年比20%増を超える成長を示した。日本市場の売上については円ベースで換算すると前年比約8%増で248億5000万円程度となる。

2016年Q4時点でのEDA業界の従業員数は前年比6.6%増の36412人で前Q3に続いて過去最高記録を更新した。

2016Q4の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 7億5750万ドル 17.4%Up

■IC Physical Design & Verification分野 4億9560万ドル 11.5%Up

■IP分野 8億5640万ドル 22%Up

■サービス分野 1億1010万ドル 2.8%Up

■PCB/MCM分野 2億3540万ドル 42.5%Up

2016年Q4の地域別の売上と昨年同時期との比較は以下の通り。

■北米 10億4850万ドル 15.7%Up

■欧州 3億8990万ドル 20.6%Up

■日本 2億2770万ドル 20.3%Up

■アジアその他地域 7億8890万ドル 22.2%Up

※EDAC(EDA Consortium)

2017.04.06

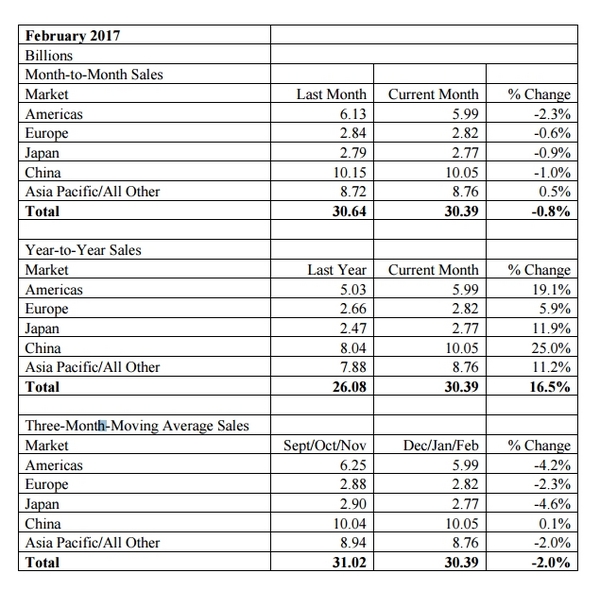

2017年4月3日、米SIA(Semiconductor Industry Association)は、2017年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2017年2月の世界半導体売上は前年同月比16.5%増、前月比0.8%減の303億9000万ドルで2月の売上記録を更新。7ヶ月連続で前年実績を上回った。

今年の世界半導体市場は昨年を上回る5%前後の成長が見込まれているが、1月、2月と2ヶ月連続で前年比2ケタ増を記録している。昨年の上半期は市場が停滞していた関係で前年実績との差が大きくなっている状況だ。

2017年2月の世界半導体市場を地域別の売上で見ると、全ての地域で前年を上回る売上を記録。中でも中国市場は25%増、北米市場は19%増と大きく前年に対して実績を伸ばした。中国は昨年12月から3ヶ月連続で前年比20%超えを記録。中国政府による半導体強化政策は更に推進される事になっており、今後も中国市場は強い成長を維持しそうだ。

日本市場の売上はドルベースでは前年比11.9%増と12月に続き3ヶ月連続で2ケタ成長を記録。円ベース換算の売上は約3130億円で円ベースでも前年比約10%の成長となった。日本市場の売上が円ベースで前年実績を上回るのは前月に続いて2ヶ月連続。

2017.03.24

2017年3月16日、Mentor Graphicsは、同社Questaファミリ製品が機能安全規格ISO 26262への対応を拡大した事を発表した。

発表によると、Mentorの検証ツール「Questa® Advanced Simulator」、「Questa Verification Management」、「Questa Clock-Domain Crossing(CDC)」の各ツール認定レポートがISO 26262に準拠している事をドイツの認証機関SGS-TÜVが認定した。

ISO 26262は、車載システムの開発ツールに関する「ツール認定レポートの作成」をツール利用者に要求しており、同レポート作成はISO 26262認証取得のための一つのタスクとなっている。

今回のMentorの対応は、認証機関に認定されたツールであれば安心して利用でき、ツール認定レポートの作成に必要なコストを削減できるというユーザー・メリットを狙ったもので、Mentorは以前からISO 26262認定のための「Mentor Safeプログラム」を立ち上げ、積極的に自社ツール顧客のISO 26262認証をバックアップしている。

2017.03.15

2017年3月14日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、中国サーバー大手のInspur社による同社製品の採用事例を発表した。

発表によるとInspurは、ルーティング制御用チップのプロトタイプ検証において、S2CのFPGAベースのプロトタイピング・システム「Prodigy」プラットフォームと共にオプションのデバッグ用モジュール「Prodigy Multi-Debug Module(MDM)」を採用。これら製品を活用することでデザインのデバッグ・プロセスを大幅に高速化する事に成功している。

「Prodigy MDM」は、複数FPGAの同時デバッグを可能とするオプション製品で、プロトタイピング・ボード上の最大16個のFPGAを1つのロジックアナライザで同時にデバッグする事が可能。また、高速GTトランシーバを用いて最速40MHzまでアットスピードでFPGAをトレースでき、2Kプローブを8グループ化し、再コンパイルすることなくFPGAごとに最大16Kプローブのトレースを可能とする。

Inspurでは、デザインに含まれる膨大なパケット送信にトリガ条件を設定し、関連するパケットをキャプチャするというデバッグ手法において「Prodigy MDM」を活用。最大16GBの波形データを保存できる「Prodigy MDM」は、サンプリングと分析に大きく役立ったという。

※画像はS2C社Web上のデータ

ちなみにInspurは日本では馴染みの薄い会社だが、サーバー・ベンダとして中国ではトップ・シェアを誇り、世界的にもトップ5に名を連ねている。同社はAppleのデータセンターにもサーバー・マシンを納入している。

2017.03.14

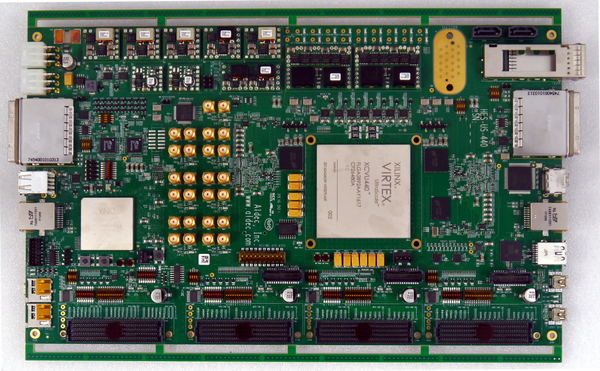

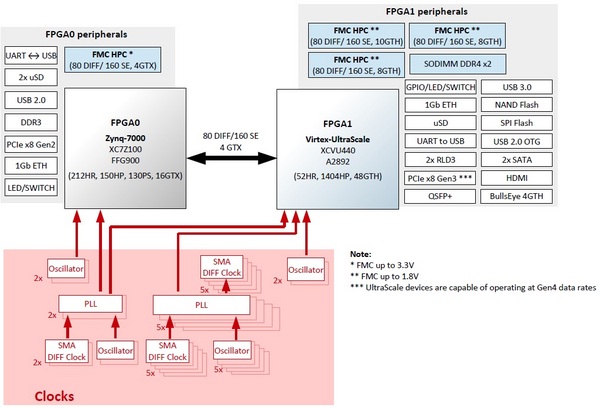

2017年2月28日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、新型のプロトタイピングボード「HES-US-440」の発売を発表した。

発表によると「HES-US-440」は、Xilinxの20nm FPGA 「UltraScale™」の一番大きな製品「XCVU440」とARM搭載FPGA「Zynq®-7000」の一番大きな製品「Z100」をそれぞれ1個搭載するプロトタイピング・ボードで、デザイン容量は最大2600万ゲート。小-中規模のASICデザインと大規模FPGAデザインのプロトタイピング・ニーズを狙うもの。

同社は既に「UltraScale™」を3個搭載する最大7900万ゲート対応の「HES-US-1320」をリリースしているが、ユーザーからの要望に応え、1つのFPGAでデザインを分割せずに利用できる汎用のデスクトップ・プロトタイピング・プラットフォームというコンセプトで「HES-US-440」を製品化した。

「HES-US-440」上に搭載される「Zynq®-7000」は、ホストコントローラとして利用されるもので、ARMを搭載する「Zynq®-7000」と最大容量の「UltraScale™」があれば、様々なニーズに対応する事が可能。Aldecはその使い方の一例として、自己完結型の埋め込みテストベンチを自分で作成できるようになると紹介している。

AldecのHESボードは、専用のソフトウェア環境「HES-DVM™」を用いることで、プロトタイピングだけでなくシミュレーション・アクセラレーションやエミュレーション・モードも使用できるというのがウリの一つ。当然ながら「HES-DVM™」もバージョンアップされ、新製品「HES-US-440」に対応している。

※画像は全てAldec社Web上のデータ

2017.03.14

2017年3月8日、Synopsysは同社の仮想プロトタイピング環境「Platform Architect」の新機能「Task Graph Generator(TGG)」の提供開始を発表した。

発表によると「Task Graph Generator」は「Platform Architect」の最新バージョンに搭載された新機能で、SoCに搭載するソフトウェアの実行状況からアプリケーション特性をプロファイリングしタスクグラフを生成するというもの。生成したタスクグラフを負荷モデルとして仮想プロトタイピングを行うことで、ターゲットとするアプリケーションに最適なSoCアーキテクチャを検討する事が可能となる。

「Task Graph Generator」によるアプリケーション特性のプロファイリングは、下記の実行トレースを元に行われ、抽象的な負荷モデルとして生成されるタスクグラフは、実行可能な仕様書としてシステム・メーカー/半導体メーカー間で利用できるという。

・Linux、Android、QNX ベース・システム上で実行したプログラムのOS レベル実行トレース

・Intelのピン・インストラクション・ツールを用いてx86 ベース・システム上で実行したプログラムの機能レベル実行トレース

・SynopsysのVirtualizer Development Kit(VDK)を用いてARMベース・システム上で実行したプログラムの機能レベル実行トレース

・ARM® DS-5 Development Studio を用いてARMベース・システム上で実行したプログラムの機能レベル実行トレース

「Task Graph Generator」の追加は、仮想プロトタイピング環境「Platform Architect」の利用価値を高める大きなアップデートと言えるだろう。

2017.03.08

2017年3月8日、SynopsysはARCプロセッサの車載向け新製品「ARC EM Safety Islands」プロセッサ・ファミリのリリースを発表した。

Synopsysは2013年10月に機能安全規格ISO 26262への対応を狙った車載システム向けのプロセッサ「ARC EM SEP (Safety Enhancement Package)」を発表しているが、今回発表した「ARC EM Safety Islands」プロセッサは「ARC EM SEP」を改良した新製品で、車載SoCの開発工数と共にISO 26262の認証取得の工数削減を狙うもの。

その製品名からも分かるように、「ARC EM Safety Islands」には機能安全を担保する幾つかの機能が予め実装されているが、既存製品に対する大きな改良点の一つと言えるのがデュアルコア・ロックステップ用の「セルフチェッキング・セーフティ・モニター」の搭載。(下図参照)同モニターは既存の「ARC EM SEP」には無かったもので、これにより設計者が回路を追加する事無くロックステップの実行状況を監視・確認することが可能になる。その他にもメモリー(バスを介さずにモニターに繋がる)上のデータ/アドレス・エラーを検出/修正するECC機能やウォッチドッグ・タイマー、オーバーラン・バッファなど様々な安全機能が備えられている。

デュアルコアによるロックステップは、ISO 26262の定める最も高い安全性レベルASIL Dを達成するために一般的に利用されている手段であるが、32ビット組込み小型プロセッサとして完全な形でロックステップをサポートするのは、この「ARC EM Safety Islands」が世界初だという。

なお、「ARC EM Safety Islands」は、ASIL D向けのロックステップ・モードの他にASIL B向けのデュアルコア・モードが用意されており、用途に応じて性能を追求することも可能。ベースとなるARCコアは、超小型の「EM4」を含めてDSPやキャッシュの有無など計4種類のコアを選択することができる。また、各コアにはオプションとしてμDMA、外部データ通信用の暗号化パック(アクセラレータ)、MPU,FPUも用意される。

※画像は全てSynopsys提供のデータ

「ARC EM Safety Islands」自体はISO 26262の認証を受けている訳ではないが、同プロセッサの開発環境である「MetaWare」はISO 26262認証済であり、「ARC EM Safety Islands」のユーザーには認証取得のためのドキュメント類が提供されるため、認証取得にかかる労力、工数を大幅に削減できる。

ちなみに工数削減の観点で言うと、予め安全機能が実装された「ARC EM Safety Islands」を利用する事で、車載SoCの開発/検証工数を約6人月近く削減可能とSynopsysは見積もっている。また、工数削減もさることながら、ARCプロセッサはコードサイズを抑える事ができるためROMの削減効果も非常に大きいという。

「ARC EM Safety Islands」は、既に4品種のうち2品種が出荷中。残り2品種は今年Q2から出荷が開始される予定となっている。

2017.03.07

2017年3月6日、米SIA(Semiconductor Industry Association)は、2017年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2017年1月の世界半導体売上は前年同月比13.9%増、前月比1.2%減の306億3000万ドルで1月の売上記録を更新。6ヶ月連続で前年実績を上回った。

今年の世界半導体市場は昨年を上回る5%前後の成長が見込まれており、幸先の良いスタートを切る形となった。

2017年1月の世界半導体市場を地域別の売上で見ると、全ての地域で前年を上回る売上を記録。欧州以外はどこも二桁成長となった。中でも中国市場は勢いを維持し続けており12月に続いて前年比20%超えを達成。北米市場も4ヶ月連続で売上前年超えとなり、市場の安定を取り戻した格好だ。

日本市場の売上はドルベースでは前年比12.3%増と12月に続き2ヶ月連続で2ケタ成長を記録。円ベース換算の売上は約3200億円で円ベースでも前年比約8.6%の成長となった。日本市場の売上が円ベースで前年実績を上回るのは2015年9月以来となる。

2017.03.01

2017年2月28日、Cadenceは検証分野の新製品「Xcelium Parallel Simulator」と「Protium S1」を発表した。 ※訂正あり

新製品「Xcelium Parallel Simulator」は、「Verilog XL」、「Incisive」に続く第三世代のシミュレータと謳われる製品で、Cadenceが昨年買収したRocketick社のマルチコア並列シミュレーション技術をベースに開発されたもの。同技術は簡単に表現するとシミュレーション処理を並列化して自動的にコアに割り当てるもので、シングルコアでも平均2倍、マルチコアでは3-10倍以上高速なシミュレーションを実現。用途で比較すると、その実行時間はRTLシミュレーションで平均3倍、ゲートレベル・シミュレーションで平均5倍、DFTの並列シミュレーションで平均10倍の高速化が可能だという。(ユーザーデータに基づく第2世代製品との性能比較結果)

「Xcelium Parallel Simulator」は既に先行ユーザーに利用されており、ARMとSTMicroelectronicsがそのパフォーマンスについて以下のようにコメントしている。

ARM:「Xcelium Parallel Simulator」によってARMベースのSoC設計において、ゲートレベルのシミュレーションが4倍、RTLシミュレーションが5倍高速になることを確認。

STMicroelectronics:「Xcelium Parallel Simulator」によってシリアルモードのDFT検証時間を8倍高速化できた。

もう一つの新製品「Protium S1」は、既存のFPGAプロトタイピング・システム「Protium」の上位新製品という位置付けで、ボード上にXilinxの20nm FPGA「Virtex™ UltraScale™」を搭載。Cadenceは「Protium S1」のデザイン容量を明らかにしていないが、既存製品の6倍という表現から想像すると最大6億ゲートのデザイン容量という事になる。

「Protium S1」の特長としてCadenceが強調するのは「検証環境立ち上げ期間の早さ」で、「Protium S1」は同社のエミュレータ「Palladium® Z1」と共通のコンパイル・フローを採用しているため既存の検証環境を再利用する事が可能。これにより検証環境の立ち上げが楽になる。ちなみにCadenceによると既存の検証環境を最大80%再利用できるという事だ。

ハードウェア・ベースの検証ソリューションとしては、大きくエミュレータとFPGAプロトタイピング・システムの2種類の製品が市場にあり、エミュレータではCadence,Mentor,Synopsysの製品が、FPGAプロトタイピング・システムではSynopsysの製品が市場を牽引している。

そういった市場の中で、エミュレーションとFPGAプロトタイピングの両製品を提供し、それら製品の柔軟な使い分けを謳っているのはCadenceのソリューションだけで、今回発表した「Protium S1」はハードウェア・ベース検証ソリューションにおける競合製品との差別化のためのCadenceの更なる一手と言える。

2017.02.28

2017年2月17日、Mentor Graphicsは、新型のエミュレータ「Veloce Strato」を発表した。

発表によると今回新製品としてリリースされたのは、「Veloce StratoM」と呼ばれるエミュレータで同社としては「Veloce」,「Veloce 2」に続く三世代目の製品。「Veloce StratoM」のデザイン容量は既存の「Veloce 2」を上回る最大25億ゲートで、Mentorは今後のロードマップとして「Veloce Strato」プラットフォームのデザイン容量を最大150億ゲートにまで引き上げるとしている。具体的なところは不明だが、「Veloce Strato Link」と呼ぶエミュレータの連結技術を用いてスケールアップを図るようだ。

MentorのエミュレータにはFPGAではない独自設計したカスタム・プロセッサ「Crystal」が搭載されており、前世代の「Veloce2」には、TSMC 65nmプロセスで製造される「Crystal2」が搭載されていた。今回発表された「Veloce StratoM」については、その搭載チップに関する詳細は不明だが、一部海外メディアではTSMC 28nmプロセスの「Crystal3」が載っているのでは?という情報もある。

いずれにしても確かなのは、「Veloce StratoM」には最大64枚の独自プロセッサ搭載ボードを挿す事が可能で、ボード1枚当りのゲート数は約4000万ゲート。64枚フル装備すれば約25億ゲートのデザイン容量に対応でき、フル装備時の消費電力は最大50KW(22.7 W/Mgate)という事だ。

「Veloce StratoM」のパフォーマンスについては、コンパイル、ランタイム、デバッグの一連の総スループットが最大5倍高速になったとの事。個々に見るとコンパイル時間最大3分の1、デバッグにおける結果表示までの時間最大10分の1、コ・シミュレーション用のモデルの速度が最大3倍となっている。

なお、Mentorは今回「Veloce Strato OS」と呼ぶ「Veloce」向けの新たなソフトウェア環境も発表。同環境は「Veloce2」と「Veloce Strato」で共通利用可能で、デザインを実装するコンパイラ、エミュレータ上で動作する各種検証用アプリおよびモデル、デバッグツールで構成されている。Mentorのエミュレーション・ソリューションは、目的に特化した検証用アプリ「Veloce Apps」や検証用のモデル「VirtuaLAB」/「iSolve」の幅広いラインナップがウリの一つとなっており、「Veloce Apps」は今年も更に拡充される計画だという。

※画像は全てMentor Graphics提供のデータ

Mentorは独Siemensによる買収が決まっており、同社のEDA事業の今後については色々な意味で業界の注目が集まっているが、同社の主力製品の一つである今回の新型エミュレータの発表は、同社のユーザーに対するメッセージとしても大きな意味が有ったと思える。ちなみに新製品「Veloce StratoM」は、既に大手顧客において採用が進んでいるとの事。

2017.02.20

2017年2月15日、Synopsysは、2017会計年度第1四半期(16年11月-17年1月)の四半期決算を報告した。

発表によると、Synopsysの2017会計年度Q1の売上は、前年同時期比約14.8%増の6億5280万ドル、純利益は前年比約44%増の8660万ドルだった。(※GAAP基準による会計結果)

今回Synopsysが報告したQ1売上額は同社の四半期売上として過去最高。Synopsysは2016会計年度のQ2以降4四半期連続で売上記録を更新し続けており、収益も大きく増やしている。

Synopsysはこの11月-1月の間に、7nmプロセス向けテスト/歩留まり解析ソリューション、スタティック・タイミング解析ツール「PrimeTime」の新機能、静的コード解析ツール「Coverity」のバージョンアップなどを発表している。

Synopsysは次の2017会計年度Q2(17年2月-4月)の売上を6億6500-6億6800万ドルと予測している。

2017.02.20

2017年2月1日、Cadenceは、2016会計年度第4四半期(2016年10-12月)の売上を報告した。

Cadenceの2016年Q4売上は、前年同時期比約6.3%増、前期Q3比約5.1%増の4億6900万ドルで同社の四半期売上記録を更新。純利益は前年比約53%減の3800万ドルだった。(※GAAP基準による会計結果)

Cadenceの2016会計年度(2016年1月-12月)の売上合計は前年比6.7%増の18億1600万ドルで過去最高を記録。純利益は前年比19.5%減の2億300万ドルだった。

Cadenceはこの10-12月において、新たな検証IP、ISO 26262に対応するTCL1ドキュメント、MathWorksとの協業によるシステムレベル検証ソリューション、OrCAD Capture向けXJTAG DFT Assistantなどを発表している。

Cadenceは、2017会計年度Q1の売上額を4億7000-8000万ドルと予測している。

2017.02.16

2017年2月7日、ルネサス エレクトロニクスは、車載マイコン向けのモータ制御専用回路「IMTS」の開発を発表した。

ルネサスが開発した「IMTS (Intelligent Motor Timer System)」は、EV向け車載マイコンに搭載する専用回路でEVモータ制御の必須処理であるフィールド指向制御演算を高速に処理する事が可能。ルネサスによるとその処理速度は0.8μsでソフトウェアによる処理時間の1/10以下で同社の調べでは世界最速との事。この性能は次世代EVモータ制御で求められる高速スイッチングにも余裕をもって対応できるという。

EV,HEV,PHVなどモータ駆動車のエネルギー効率の向上には、モータ制御ECUの機能向上、性能向上も重要であり、今回ルネサスはマイコンにおけるモータ制御の中で高い応答性能が求められる固定的な処理をCPUから独立した自律可能な専用回路「IMTS」としてハード化。これによりCPUの負荷は大きく軽減され、エネルギー効率の向上に貢献する別のモータ制御アルゴリズムに割り当てることが可能となるという話だ。

※画像はルネサスWeb上の公開データ

なお、ルネサスは上記専用回路の開発と合わせて、独自の機能安全技術をマイコンに採用。具体的にはマイコンに搭載するCPUコアを二重化する「ロックステップデュアルコアシステム」によってIMTS回路内部を定期的に監視する形とした。この手法はマイコンやマイコンの内部回路を二重化するよりも低コストでCPUへの負荷も少なく機能安全を担保できるという。

ルネサスは開発したこれら一連の技術について、先ごろサンフランシスコで開催されたISSCC 2017で発表した。

2017.02.15

2017年1月19日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のFPGA設計向けシミュレータ「Active-HDL」の新機能リリースを発表した。

発表によると論理シミュレータ「Active-HDL」の最新バージョン10.4のリリースに伴い、新機能となる「有限ステートマシン(FSM)カバレッジ機能」が装備された。

同機能は高い安全性の確保が求められるセーフティクリティカルなFPGAの設計をターゲットに用意されたもので、シミュレーション中にステートマシン図の中のどのステートと遷移が実行されたかを判別する事が可能。実行するHDLコードにSystemVerilogまたはAldec専用のプラグマを挿入することでFSMカバレッジの統計データを収集し、カバレッジエンジンが解釈する。

Aldecによると、航空関連のRTCA/DO-254、自動車関連のISO 26262、原子力発電所関連のIEC 62566など、セーフティクリティカルなデザインの保証ガイドラインや標準規格では、どれも検証プロセスの一環としてFSMカバレッジを使用することを推奨しているとの事だ。

もう一つ、Aldecは2017年2月1日にFPGA/SoC向け要求ライフサイクル管理ツール「Spec-TRACER」の最新バージョン 2016.12のリリースを発表し、同ツールにおいて航空用電子機器の開発ガイドラインRTCA/DO-254に対応する認証文書のテンプレートとレビュー用チェックリストの提供を開始した。

同テンプレートとリストを用いることで、DO-254対応のFPGA設計においてライフサイクルデータの管理と生成を簡略化できるという。

2017.02.14

2017年2月2日、Cadenceは同社のエミュレータ「Palladium Z1」をCavium社が採用した事を発表した。

Caviumはネットワーク、サーバー向けに様々なプロセッサ/SoCを提供しているが、今回「Palladium Z1」の採用に伴う具体的な製品ターゲットは不明。明らかにされているのは採用した理由で、多様性、コスト・パフォーマンス、短TATの3つが挙げられている。※詳細はCadenceプレスリリース文参照

発表に寄せられたCaviumのコメントを見ると特定の製品開発向けという訳ではなく、社内の検証インフラの拡充を目的に「Palladium Z1」の導入を決定したようだ。

「Palladium Z1」は2015年11月に発表されたエミュレータで、最大16ラックの構成で92億ゲートのデザイン容量に対応。400万ゲート単位で最大2304人のユーザーが個別のジョブを実行できる。

2017.02.14

2017年2月1日、Mentor Graphicsは、同社の提供するAUTOSAR BSWスタックの使用をトヨタ自動車が承認した事を発表した。

AUTOSAR準拠のBSW(Basic Software)は、ECU開発の一つのソリューションとして確立されており、Mentorの他に独Vector,独Elektrobitなどが先行して市場を形成。日本国内でもSCSK, APTJ, オーバスなどが提供を開始している。

今回トヨタはMentorの提供する「Volcano VSTAR BSWスタック」を同社全ての車両開発に使用する事を承認したという。

MentorはBSWの他にブートローダ、ランタイム環境(RTE)、カスタマイズ診断、カスタマイズSWC(ソフトウェア・コンポーネント)も提供している。

※画像はMentor社Web上の掲載データ

2017.02.13

2017年1月13日、配置配線ツール「Aprisa」を手がけるEDAベンダATopTechは、デラウェア州連邦破産裁判所へ破産保護申請した事を発表した。

ATopTechはSynopsysに著作権侵害で提訴され係争を続けていたが、昨年3月に裁判に敗訴しSynopsysへの賠償金3000万ドルの支払い命令が下り、昨年12月にはカリフォルニア州の米連邦裁判所からATopTechに恒久的な製品差し止め命令が出されていた。

両社の間には複数の裁判が起こされていたようだが、その発端であり敗訴、製品差し止めの直接的な原因となったのは、ATopTechがSynopysのタイミング解析ツールPrimeTimeのコマンドセットをコピーして自社製品に組み込んだという事にあるようだ。

ATopTechは破産裁判所の管理下で事業をオークションで売却する予定。これによりATopTech社のEDAベンダとしての事業活動に終止符が打たれる。

ATopTechの配置配線ツール「Aprisa」は先端プロセス向けツールとして韓国大手などが採用。デザインによっては大手EDAベンダの製品を凌ぐ性能を発揮すると言われ、日本国内にもユーザーが存在していた。配置配線というEDAの中でも本流と呼べる分野において、大手2社に挟まれながらも実績を積み重ねてきた同社であったが、裁判所の判決にあがらう事は出来なかった。

2017.02.13

2017年1月19日、高位合成ツール「CyberWorkBench」を手がける日本電気株式会社は、台湾のファブレス半導体ベンダ、ファラデーテクノロジーによるツールの採用事例を発表した。

発表によるとファラデーは、通信制御用ASICのプロトタイプのFPGA設計で「CyberWorkBench」を採用。低遅延・低レイテンシな回路の合成を実現し、設計工数を従来の人手による工数の1/6に削減した。

一般的に高位合成ツールの成功事例としてはデータパス系回路の事例が多いが、今回のケースは通信制御用の回路というところが興味深い。

「CyberWorkBench」は元々はASIC設計をターゲットとしたツールだが、FPGA設計に特化したFPGA専用版の製品も用意しており、デバイスに最適な高度な合成品質でユーザーから一定の評価を得ている。

ファラデーは今回のFPGA設計の成功を受けて「CyberWorkBench」の活用範囲をASICに拡大する予定との事。NECはASICにもFPGAにも対応可能な「CyberWorkBench Enterprise」というライセンスも用意している。

なお、NECでは来る3月29日に同社品川セミナールームにて「高位合成ツール体験セミナー」を開催する予定。(定員20名)同セミナーのプログラムを見ると制御回路設計の講義と演習も含まれている。

2017.02.08

2017年2月3日、米SIA(Semiconductor Industry Association)は、2016年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年12月の世界半導体売上は前年同月比12.3%増、前月とほぼ同等の310億1000万ドルで5ヶ月連続で前年実績を上回った。

2016年の世界半導体売上の合計は、前年比1.1%増の3389億ドルで過去最高を記録。上半期の売上は振るわなかったが下半期の猛烈な巻き返しにより、前年比プラス成長という結果に終わった。

ちなみに昨年11月に発表されたWSTSによる昨年の秋季予測によると、2017年の世界半導体市場は約3.3%のプラス成長となっている。

2016年12月の世界半導体市場を地域別の売上で見ると、全ての地域で前年を上回る売上を記録。中国市場は活況を維持し続けており前年比20.4%と売上大幅アップ。北米市場も前年比10.1%増と強さを取り戻した。北米市場はこれで3ヶ月連続で売上前年超えを達成した。

日本市場の売上はドルベースでは前年比10.5%増と地域別では首位中国に次ぐ成長率を達成。円ベースでは前年比約3%減で、円ベース換算の売上は約3056億円となっている。

2017.01.10

2017年1月5日、米SIA(Semiconductor Industry Association)は、2016年11月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年11月の世界半導体売上は前年同月比7.4%増、前月比2%増の310億3000万ドルで、10月に続いて単月売上記録を更新した。売上が前年同時期の実績を上回るのはこれで4ヶ月連続となる。2016年の上半期は売上停滞期であったが、下半期は一転して成長基調となり、11月の時点でほぼ2015年実績に並ぶ状況となっている。

2016年11月の世界半導体市場を地域別の売上で見ると、欧州市場以外は全ての地域で前年比プラス成長を達成。中国市場に勢いは止まらず10月に続いて前年比2ケタ成長、長らく復調の兆しが見えなかった北米市場も2ヶ月連続で売上前年超えを維持した。

日本市場の売上はドルベースでは前年比8.2%増と10月を上回る今年最高の伸び。円ベースでは前年比約5%減で、円ベース換算の売上は約3120億円となっている。

2016.12.25

2016年12月22日、米ESD Allianceは、2016年度第3四半期(7月-9月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2016年Q3(7-9月)の世界のEDA売上総額は、前年比約6.9%増、前Q2比約4%増の20億9370万ドルだった。前Q2においてQ4以外で初の20億ドル超えを達成していたが、このQ3においても20億ドルを突破しQ2売上を上回った。今年のEDA市場は昨年以上に見通しが明るい。

2016年Q3のEDA売上をカテゴリ別に見るとPCB分野以外の全ての分野で売上が前年実績を上回った。IP分野は依然勢いが衰えず再び7億ドル超え。IC Physical Design & Verification分野も好調だった。

2016年Q3のEDA売上を地域別に見ると全ての地域で売上前年比増を達成。中でも中国を中心とするアジア市場は前年比16.6%と圧倒的な伸びを示している。日本市場はドルベースでは前年比微増となっているが、円ベースでは13%以上のマイナスとなっている。

2016年Q3時点でのEDA業界の従業員数は前年比6.2%増の35515人で過去最高記録を更新した。

2016Q3の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億6670万ドル 5%Up

■IC Physical Design & Verification分野 4億4130万ドル 8.2%Up

■IP分野 7億2090万ドル 10.4%Up

■サービス分野 1億260万ドル 3%Up

■PCB/MCM分野 1億6220万ドル 0.1%Down

2016年Q3の地域別の売上と昨年同時期との比較は以下の通り。

■北米 9億3290万ドル 3.2%Up

■欧州 2億9700万ドル 2.3%Up

■日本 2億1320万ドル 3.9%Up

■アジアその他地域 6億5060万ドル 16.6%Up

2016.12.23

2016年11月17日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けツールを中心に各種EDAソリューションを展開するSilvacoの日本法人シルバコ・ジャパンは、同社のプライベートセミナー「Silvaco Japan EDA Seminar 2016」を開催した。

ここでは「Silvaco Japan EDA Seminar 2016」の様子をレポートする。

セミナーの会場はシルバコ・ジャパンがオフィスを構える横浜ランドマークタワーの会議スペースで、セミナーにはざっと100名以上の参加者とパートナー企業9社が集まった。

セミナーの冒頭に行われたのは、「日本の強みと残すべきもの!」と題した、リボンディスプレイジャパン株式会社 代表取締役社長 須山 透氏による基調講演。

リボンディスプレイジャパンは、元パナソニックの須山氏が2014年に設立したLCDドライバに特化したファブレス・ベンチャーで社員は現在22名。創業3期目にもかかわらず既に売上50億円以上と驚異的な実績を叩き出している。

須山氏は講演を通じて、同社の成功に繋がったと思われる考え方を幾つか紹介してくれたが、「日本メーカーが負けてしまったのはセットであって部品では負けていない」というのが持論で、リーマンショック後の為替高を乗り越えた強い製造会社らとチームを作る事で、大手メーカーに頼らない垂直統合/水平分業のハイブリッド運営体制を実現し、圧倒的な低価格化によって台湾・韓国の競合企業からLCDドライバのシェアを取り戻しているという話だった。ちろん同社はSilvaco製品のユーザーの一社である。

※リボンディスプレイジャパンの須山社長

続いて登壇したSilvaco本社CEOのDavid L.Dutton氏は、テクノロジ・アップデートとして同社の実績と今度の展望について講演した。

David氏によると、同氏がCEOに就任した2014年以降、Silvacoの業績は順調に推移しており、2015-2018年において売上倍増を目指しているとの事。その実現に向けてこの2年で既に関連企業を計4社買収しており、既に次の買収ターゲットも確定している事を示唆。同社の主戦場であるディスプレイ、先端CMOS、パワーデバイス以外の自動車やIoTといったドメインにおいても、EDA、TCAD、IPをはじめとするSilvacoのソリューションの更なる浸透・成長を見込んでいるという。

※Silvaco CEO David L.Dutton氏の講演資料(近年のM&Aについて)

ちなみにIPextreme社の買収によって力を入れ始めたIP事業は、現在のところ自動車を大きなターゲットとしており、半導体ベンダとの協業によりマイクロコントローラIPやネットワークIPなどを手掛けているという話で、具体的にはNXPをはじめとする大手IDMからLSIとして量産実績のある内部回路をIPとして抜き出し製品化するというユニークなビジネスモデルのIP販売を展開している。

※Silvaco CEO David L.Dutton氏の講演資料(IPビジネスモデル)

招待講演として登壇したのは、USアトランタに本社を構えるアナログIPベンダーSilicon Creations社 Vice President兼CTO Jeff Galloway氏。同氏は「Robust 7nm to 350nm Design flow with Silvaco」と題してSilvacoツールを使用した自社の設計環境の取り組みと先端プロセスでの設計において対応すべき事について紹介した。

アナログ設計のエンジニアに向けて様々な技術ノウハウが紹介されたが、興味深かったのは同社におけるPDKの扱いで、ファンドリが提供するPDKを用いるという一般的なデザインハウス各社の設計手法と違い、Silicon CreationsではベースとなるPDKをSilvacoツールを使用して自社で開発しているとの事。これは9社にもおよぶファンドリの各プロセスに対して設計資産を再利用するための工夫なのだという。

また、検証手法についてもSERDES回路を例にとり、独自のVerilogモデル化によるシステム検証手法を紹介。Jeff氏によると、独自のVerilogモデルを用いたシステム検証結果は、SPICEシミュレーション結果と波形の上で差が無く、SPICEで4日かかる検証をわずか1分と大幅に検証工数を減らす事が可能という話だ。

更にJeff氏は、プロセスの複雑さに伴うDRCルール項目の増加、検証時間の増大などFinFETをはじめとする最先端プロセスの設計課題についても触れ、今後懸念される寄生RCの影響増加やばらつきの問題に対しての取組についても紹介した。

※Silicon Creations、Jeff Galloway氏(Vice President兼CTO)

※Silicon Creations、Jeff Galloway氏の講演資料(Silvacoツールを利用した独自PDK開発の説明)

その後のSilvacoからの技術セッションでは、低消費電力設計LSIやPMICなどに向けたパワー解析ツールInVar、先端プロセスでの設計で効果的な寄生素子リダクションツールJivaro、ばらつき考慮設計に対応するツールVariation Manager、最後にIPの紹介と続き、近年のM&Aで取得した新しい製品を中心に紹介が行われた。

パワー・インテグリティ セッションで紹介された3D熱解析

寄生RC解析セッションで紹介されたリダクション後の精度評価

Variation Awareセッションで紹介されたFast Monte Carloでの削減効果

IPセッションでのラインナップの紹介

※セミナー終了後の交流会にて (左から、シルバコ・ジャパンGM古井氏、Silvaco Chairman Pesic氏、Silicon Creations CTO Galloway氏、Silvaco CEO Dutton氏)

2016.12.08

2016年11月29日、FPGAベースのプロトタイピング・システムを手掛けるS2Cは、Intel(Altera)製FPGAを搭載する同社の新製品について発表した。

発表によるとS2Cは現在、Intel(Altera)の20nm FPGA「Arria 10」を搭載するプロトタイピング・システムの新製品「Arria 10 Prodigy FPGA Prototyping Logic Module」を開発中で、来年前半に市場投入を計画している。

同新製品に搭載されるFPGAは「Arria 10」ファミリとして最大のロジック容量を誇る「GX 1150」で、同FPGAには1チップに150万個のロジック・エレメント、53MbsのM20Kメモリ、3036個のDSPリソースが載っている。まずは「Arria 10 GX 1150」が1個搭載されている製品が出てくるようだが、複数ボードを連結する事でデザイン容量の拡張は可能。S2Cは簡単に複数ボードを繋ぐ事ができるハード/ソフトのインフラを用意している。

S2Cによると、「Arria 10 Prodigy FPGA Prototyping Logic Module」は、Intel(Altera)のOpenCL向け Software Development Kit (SDK)と互換性があり、OpenCLベースのFPGA実装が可能。システムを容易に活用できるだけでなく、優れたコストパフォーマンスをユーザーに提供可能だという。

市販のFPGAベース・プロトタイピング・システムは、Xilinx製のFPGAをベースにしたものが主流となっており、Intel(Altera)製FPGAを搭載する製品はかなりの少数派となっている。今回発表されたS2Cの試みは市場の隙間を突いた戦略と言えるが、多数のAlteraユーザーの存在やOpenCLサポートをはじめとするIntel(Altera)製FPGAの独自性考えると今後の展開が楽しみな製品と言えるだろう。

2016.12.07

2016年11月30日、Synopsysは、2016会計年度第4四半期(16年8月-10月)の四半期決算を報告した。

発表によると、Synopsysの2016会計年度Q4の売上は、前年同時期比約7.9%増の6億3370万ドル、純利益は前年比約46%増の7270万ドルだった。(※GAAP基準による会計結果)

今回Synopsysが報告したQ4売上額は同社の四半期売上として過去最高。2016会計年度のQ1は若干売上を落としたが、それ以降は3四半期連続で売上記録を更新し続けている。

なお、Synopsysの2016会計年度(2015年11月-2016年10月)の売上総額は24億2000万ドル、純利益は2億6600万ドルとなっている。

Synopsysはこの8月-10月の間に、組み込みプロセッサ、Bluetooth LE、車載向けFoundation IPなど主力のIP新製品を投入。合わせて大手ファウンドリTSMCとのIP開発に関する協業やリファレンスフロー対応についてもアナウンスしている。

Synopsysは次の2017会計年度Q1(16年11月-17年1月)の売上を6億3000-6億4500万ドル、2017会計年度の年間売上を25億7000万?26億ドルと予測している。

2016.12.07

2016年11月22日、Mentor Graphicsは、2017会計年度第3四半期(16年8月-10月)の売上を報告した。

発表によると、Mentorの2017会計年度Q3の売上は、前年比約11%増の3億2250万ドル、約4176万ドルの営業利益を計上した。(※GAAP基準による会計結果)

この業績は前Q2売上報告時の予測値を1000万ドル近く上回るものだった。

Mentorは本業績報告の約1週間前に、独Siemensによる買収に合意したことを発表し業界を驚かせた。

SiemensのMentor買収取引は総額45億ドルとなる見通しで、現在のところ2017年Q2(4-6月)に手続きが完了する予定となっている。

当サイトで報じてきた大手EDAベンダMentor Graphicsの売上報告は今回が最後となる。

2016.12.07

2016年12月5日、米SIA(Semiconductor Industry Association)は、2016年10月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2016年10月の世界半導体売上は前年同月比5.1%増、前月比3.4%増の304億5000万ドルで、10月の売上として過去最高を記録。単月売上が300億ドルを超えるのは史上初となる。売上が前年同時期の実績を上回るのはこれで3ヶ月連続。今年上半期は売上の停滞が続いていたが、8月以降は急激に売上が回復しており年間売上で前年実績を上回る可能性が高まってきた。

2016年10月の世界半導体市場を地域別の売上で見ると、長らく前年実績を割り込んでいた北米市場が遂に前年超え。為替の影響のある欧州市場以外は全ての地域で前年比プラス成長を達成した。中でも中国市場は勢いを取り戻し前年比17%増と今年最高の伸びを示した。

日本市場の売上はドルベースでは前年比7.2%増と今年最高の伸び。円ベースでは前年比約11%減で、円ベース換算の売上は約3000億円となっている。

※SIA

-45°-thumb-500x328-4402.jpg)