NEWS

2018.05.19

2018年5月8日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けツールを中心に各種EDAソリューションを展開するSilvacoは、Arm Approved Design Partner Programへの加盟を発表した。

「Arm Approved Design Partner Program」は、Armに承認されたデザイン・サービス企業の世界的なネットワークで、加盟にあたりデザインサービスに関するプロセス、品質規格、財務の安定性などArmの監査を受ける。当然ながらArm IPの使用実績が無ければ承認されない。

Silvacoは近年IP事業への投資を強化しており、2016年にIPextreme、2017年にSoC Solutionsを買収。両社を買収したことによりArmベース設計を行う顧客の支援も同社の業務の一環となっている。Silvacoは車載、IoTといった分野向けにArmのバスのIPやサブシステム等を提供している。

2018.05.19

2018年5月17日、Reutersの記事:

Intelが買収したイスラエルのMobileyeが自動運転技術の供給に関する大型契約を獲得した。契約相手は明らかにされていないが欧州の自動車メーカーで、2021年以降車両800万台でMobileyeの自動運転技術が採用される。

2018.05.18

2018年5月18日、Bloombergの記事:

マイニング・チップの最大手の中国Bitmainは中国における仮想通貨の規制を受けて、収益源をAIチップにシフトしていく計画。昨年10月にはAIチップ「Sophon BM1680」を発売している。目標は5年以内に売上の40%をAIチップにすること。Bitmainは創業わずか4年だが昨年の営業利益は35億ドルだという。

2018.05.18

2018年5月16日、BARRON'Sの記事:

NANDより1000倍高速で信頼性が高く高密度なIntelのOptaneメモリは、NANDとDRAMの中間に位置し、サーバーコンピュータに適切な「キャッシュ」として機能することができる。将来的にはPCの主なストレージとしてSSDを置き換える可能性もある。

2018.05.18

組み込みプロセッサのベンチマークを行なう非営利団体EEMBCは、機械学習推論のアクセラレーションを行なうエッジ向けAIプロセッサの性能および電力効率のベンチマークを開始する計画で新たなワーキング・グループのメンバーを集めている。

・Almotive Alware

・Cadence Vision P6

・Cambricon CPU

・Ceva NeuPro

・Imagination PowerVR 2NX

・Nvidia NVDLA

・Synopsys EV64

・VeriSilicon VIP

・Videantis v-MP6000

5月11日時点で下記11社がワーキング・グループに参加することになっている。

・Analog Devices

・ARM

・Flex

・Green Hills Software

・Intel

・Nvidia

・NXP Semiconductors

・Samsung

・STMicroelectronics

・Synopsys

・Texas Instruments

2018.05.18

2018年5月17日、IntelはIntel Xeonスケーラブル・プロセッサー 6138Pの提供を開始した事を発表した。

Xeonスケーラブル・プロセッサー 6138PはFPGAを統合したXeonプロセッサーの最初の量産製品で、Arria10 FPGA GX1150を搭載し、ソケットあたり最大160GbpsのI/O帯域と、高度に連携したアクセラレーションのためのキャッシュ・コヒーレントなインターフェースを提供する。

2018.05.17

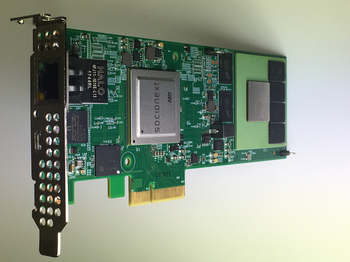

2018年5月17日、Socionextは映像データのコーデックシステムの新製品「M820L」の発売を発表した。

「M820L」は、専用ハードウェアによる高性能処理と汎用CPUによる柔軟なソフトウェア処理を組み合わせたハイブリッドコーデック製品「M820シリーズ」の新製品で、PCI-e Low Profileに準拠したカードにハイブリッドコーデック・システムが実装されている。同カードをPCやサーバーのPCI-eスロットに挿せばCPUのアクセラレーターとして活用することができる。

Socionextは「M820L」の利用方法として既存システムのエンコード性能の向上、新たに要求される機能・性能に応じたシステムの拡張などを想定していて、そのアプリケーション事例としてクラウドAIと連携させた高画質・リアルタイム映像解析のデモを開発。「M820L」を利用することで従来のクラウド映像処理だけでは実現が難しかった高解像度・高画質の効率的なリアルタイムでの解析が実現できたという。同デモは今日明日と東京国際フォーラムで開催される「富?通フォーラム 2018 東京」で展示している。

2018.05.17

2018年5月8日、インターコネクトIPを手掛けるNetSpeed Systemsは、各種設計IPを手掛けるNorthwest Logicとの協業を発表した。

発表によると両社は自動車およびデータセンター・セグメントで利用されるハイパフォーマンスSoC向けに、NetspeedのインターコネクトIPとNorthwestのメモリコントローラIP(HBM2およびGDDR6)を組み合わせたプラットフォームを提供していくという。

Northwest LogicのHBM2メモリコントローラは高性能で定評があり、NetspeedのインターコネクトIPはコヒーレンシ対応の面で顧客の評価が高い。

2018.05.17

2018年5月14日、Synopsysは同社の物理検証ツール「IC Validator」がGLOBALFOUNDRIESの14LPPプロセスのフィジカル・サインオフツールとして認定された事を発表した。

DRC、LVSおよびメタルフィル・テクノロジファイルを含む「IC Validator」の認定済ランセットは既にGLOBALFOUNDRIESから入手可能となっている。

2018.05.16

2018年5月16日、Armは韓国最大の公益事業会社、韓国電力公社(KEPCO)による採用事例を発表した。

発表によるとKEPCOはメーターシステムの変革プロジェクトにおいてArmのソリューションを採用。具体的には「Mbed IoT Device Platform」、「Arm® Cortex®-M33プロセッサ」、ArmのIoTデバイス向けセキュリティ・アーキテクチャ「Platform Security Architecture(PSA)」を活用することで、数百万台のセキュアなコネクテッド・ユニットの開発、導入、管理を実現する計画だという。

2018.05.16

2018年5月9日、設計IPベンダのArasanは、業界初となるMIPI I3C仕様準拠の設計IPのリリースを発表した。

MIPI I3Cは、デバイス内のすべてのセンサーをアプリケーション・プロセッサに接続できるチップツーチップインターフェースで、Arasanがリリースした「MIPI I3C Host Controller Interface Master IP」は、リリースされたばかりの「MIPI I3C HCI Specification Ver 1.0」に準拠。仕様への準拠はサードパーティ製の検証IPならびにMIPIの実施した相互運用性テストによって保証されている。

Arasanの「MIPI I3C Host Controller Interface Master IP」は既に先行顧客によって利用されており、同設計IPを搭載したチップが年内に発売される予定。

ArasanはMIPI以外にも幅広く設計IPを提供しており、Arasan製IPを搭載したチップの出荷数は10億を超えているという。

2018.05.16

2018年5月15日、MIPI AllianceはMIPI Display Serial Interface 2 (DSI-2)およびMIPI Display Command Set (DCS)仕様の新バージョンのリリースを発表した。

リリースされたMIPI DSI-2 v1.1およびMIPI DCS v1.4は、Video Electronics Standards Association (VESA®)とMIPI Allianceが共同開発した新しいビデオインタフェース圧縮規格「VESA Display Compression-M (VDC-M)」をサポートしている。VDC-M規格は、最大5:1の圧縮を実現するという。

2018.05.16

2018年5月15日、IC Insightsの記事:

今月下旬にリリース予定のIC Insightsのレポートによると、半導体上位15社の2018年Q1(1-3月)の売上合計額は前年比26%増と昨年からの好調を維持しており、上位15社のうち13社が前年比2ケタ増の売上を記録している。

2018.05.15

2018年5月8日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社の高機能シミュレータ「Riviera-PRO」のバージョンアップを発表した。

AldecによるとRiviera-PRO™の最新リリース2018.02に追加された主な新機能は下記3つ。

・UVMレジスタジェネレータ

・ユニットリンティング機能

・VHDLの拡張機能

UVMレジスタジェネレータを利用することで、レジスタモデルを自動作成でき工数と合わせてUVMクラスを書く際のコーディングミスを削減可能。Aldecの担当者はエラーがなく再利用できるUVMテスト環境をできる限り早く、シームレスに作れるため、非常に有効だとしている。

ユニットリンティング機能は、作業中のコードブロック (ユニット) だけを別のアプリケーションを起動することなくリントチェックできる機能。VHDLの拡張機能とは、VHDL 2018の正式リリースで採用される可能性が高い拡張機能のサポートを意味している。

その他にも今回の最新リリースでは様々な機能、オプションのエンハンスやアップデートが実施されている。

2018.05.15

2018年5月15日、富士通は組合せ最適化問題を高速に解く「デジタルアニーラ クラウドサービス」の提供開始を発表した。

発表によると現在の「デジタルアニーラ」は、コンピュータ内部で1024個のビット値が全結合で相互接続されており、さらにビット間の結合の強さを65536階調で表現可能。これにより現行の量子アニーリングマシンでは困難な複雑で大規模な問題も解ける。また、デジタル回路を用いていることからノイズの影響も受けにくく、特別な冷却装置を用いること無しに室温で安定動作させることが可能。

富士通は今後、「デジタルアニーラ」専用プロセッサ「Digital Annealing Unit(DAU)」を開発し、ビット間全結合の規模を現在の1024ビットから8192ビットへ、結合精度を16ビットから最大64ビットの1845京階調まで拡張する計画で「DAU」を実装したクラウドサービスの提供を2018年度中に予定している。

「Digital Annealing Unit(DAU)」:富士通HP上で公開している画像

2018.05.15

2018年5月11日、NECと産総研は発生確率が極めて低いため設計段階で事前に発見が難しい不具合を、AI(人工知能)が学習をしながらシミュレーションを繰り返して効率的に見つけ出す「希少事象発見技術」を開発したことを発表した。

発表された「希少事象発見技術」はNECの最先端AI技術群「NEC the WISE」の1つで、AI技術とシミュレーション技術を融合させ、複雑な条件の組合せでまれに起こる不具合の探索を効率化し、製品設計段階で熟練の専門家が費やしていた検証時間の大幅な短縮と複数不具合の見落としリスクを軽減するとしている。

実際に「希少事象発見技術」を光学機器の設計検証に適用したところ、熟練の専門家が1週間を要していた検証作業を約1日に短縮し、発生確率が1億分の1程度とまれな「迷光」を見落とすことなく発見できたという。

2018.05.15

2018年5月2日、CadenceはDDR5メモリ・インタフェースIPのプロトタイプについて発表した。

発表によるとCadenceはTSMC 7nmプロセスでDDR5のPHYおよびコントローラのプロトタイプを作成。MicronのDDR5 DRAMのプロトタイプと共に動作する事を確認した。プロトタイプによるデータ転送レートは4400Mbpsを達成したという。

DDR5規格は未だ完成していないが今年の夏にはJEDECが最終仕様を策定する計画。

CadenceによるDDR5 IPのシリコン化は業界初でその詳細は4月末に開催された「TSMC Technology Symposium」で発表された。

2018.05.15

2018年5月14日、SEMIは2018年Q1(1-3月)の世界シリコン・ウエハ出荷量を発表した。

発表によると2018年Q1の世界シリコン・ウエハ出荷量は、前年比7.9%増、前Q4比3.6%増の計30億8400万平方インチで過去最高を記録した。

2018.05.14

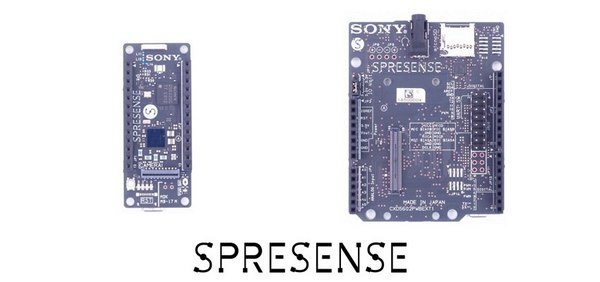

2018年5月14日、ソニーは、IoT向けスマートセンシングプロセッサ搭載ボード「SPRESENSE」(スプレッセンス)を7月31日に発売することを発表した。

発売するのはメインボード(5500円)と拡張ボード(3500円)の2点で、メインボードにはARM® Cortex®-M4F 6コア構成のスマートセンシングプロセッサが搭載されており、GNSS受信機やハイレゾ音源対応のオーディオコーデック等が内蔵されている。このプロセッサはFD-SOIを採用しており、動作電圧を下げることで低消費電力を実現している。拡張ボードにはヘッドホン端子、マイク端子、SDカードスロットが備えられている。

2018.05.14

2018年5月14日、ソニーは、IoT向けスマートセンシングプロセッサ搭載ボード「SPRESENSE」(スプレッセンス)を7月31日に発売することを発表した。

発売するのはメインボード(5500円)と拡張ボード(3500円)の2点で、メインボードにはARM® Cortex®-M4F 6コア構成のスマートセンシングプロセッサが搭載されており、GNSS受信機やハイレゾ音源対応のオーディオコーデック等が内蔵されている。このプロセッサはFD-SOIを採用しており、動作電圧を下げることで低消費電力を実現している。拡張ボードにはヘッドホン端子、マイク端子、SDカードスロットが備えられている。

2018.05.14

2018年5月8日、グラフィックスIPを手掛ける日本のIPベンダ、ディジタルメディアプロフェッショナル(DMP)は、同社の人工知能(AI)/ディープラーニングに対する研究、製品開発の取り組みに関するホームページを新たに開設した。

Cyber AI Labホームページ: https://www.cyberailab.com/

DMPはエッジ向けのDeep Learning推論処理に特化した超低消費電力プロセッサーIP「ZIA™ DV700」やAIを用いた動画像認識ソフトなどを手掛けている。

2018.05.14

2018年5月14日、ザイ・オンラインの記事:

2018.05.14

2018年5月7日、Cadenceは検証IPの新製品3品種を発表した。

今回発表された新製品とその詳細説明URLは以下の通り。

・UFS 3.0向け検証IP : http://www.cadence.com/go/vipU

・CoaXPress向け検証IP: http://www.cadence.com/go/vipC

・HyperRAM向け検証IP : http://www.cadence.com/go/vipH

新たな検証IP製品は、Cadenceのシミュレータ「Xcelium™ Parallel Logic Simulation」向けに最適化されており、他社のシミュレーターにも対応している。

JEDECの策定するUniversal Flash Storage(UFS) 3.0は今年1月に仕様が公開されたばかり。

2018.05.14

2018年5月9日、Cadenceは新製品「Legato Reliability Solution」を発表した。

発表によるとCadenceの新製品「Legato™ Reliability Solution」は、回路シミュレータ「Spectre® Accelerated Parallel Simulator」およびカスタムIC設計プラットフォーム「Virtuoso®」をベースに開発されたアナログIC向けの信頼性考慮設計ソリューションで、以下の3つの解析機能を単一のコックピットに統合している。

・アナログ故障解析

・電気-熱解析

・経年劣化解析

アナログIC製品を対象に初期テストから稼動期間、経年劣化まで、製品のライフサイクル全体で設計の信頼性を管理するツールは業界初。

故障解析に使用されるシミュレーション・エンジンは新しいテスト手法「defect-oriented testing (欠陥指向テスト)」 に対応する新型のエンジンで、これによりテスト数を最大30%削減することが期待可能。実際にツールを評価したInfineonは故障シミュレーションを100倍以上高速化する事に成功したという。

2018.05.14

2018年5月8日、エッジ向けAIプロセッサを手掛けるベンチャー米SyntiantはIntel Capitalらからの資金調達を発表した。

Syntiant社はカリフォルニア州アーバインに本拠を置くAI半導体ベンチャーで、フラッシュメモリを利用したアナログ・ニューラルネットワーク技術によって超ローパワーのAI処理を実現する「Neural Decision Processor」を手掛けている。

今回発表した資金調達は同社初のラウンドでIntelが主導。Intel以外にもSeraph Group, Danhua Capital, Embark Venturesが出資に参加している。

Syntiantによると同社は既に「Neural Decision Processor」を用いた製品開発でInfineon Technologiesと契約を結んでいるという。

2018.05.14

2018年5月8日、米SiFive社はIntelによる出資を発表した。

SiFive社はオープンソースの命令セット・アーキテクチャ「RISC-V」をベースとしたプロセッサ・コアやSoCを手掛けるファブレス半導体ベンダで、RISC-Vを用いたビジネスの草分け的な存在。同社は今年4月に実施した資金調達第三ラウンドで計5,060万ドルをベンチャー・キャピタルから調達。出資者の中にIntel Capitalも含まれていた。

2018.05.11

2018年5月8日、Anandtechの記事:

標準7nmプロセスと比較してトランジスタ密度は大きく向上するも、性能とパワーに劇的な向上は見られない。

2018.05.11

2018年5月10日、アーム株式会社がArmのIoTプラットフォーム「Arm® Mbed™ Platform(アーム・エンベッド・プラットフォーム)」に関する最新動向を発表した。

主な内容は以下の通り。

・対前年比30%増となる30万人以上の開発者を擁し、パートナー80社以上の支持を得て、Arm Mbed Platformの採用が急速に拡大

・IBM Watson IoTとの連携を拡大、また、サイバートラストおよびGMOグローバルサインと協業し、BYOC(Bring-Your-Own-Certificate)方式による柔軟なIoTセキュリティ認証を実現

・各社がインダストリー4.0へと移行する中、物流やエネルギー・公益、スマートシティの分野で、MbedがIoTによるビジネス価値創出の原動力に

2018.05.11

2018年5月3日、Synopsysの発表「Cambricon社、次世代AIプロセッサ開発にシノプシスのHAPSを採用」

中国Cambricon社は、Huaweiのモバイル向けSoC「Kirin970」のニューラルエンジンを作った事で知られる中国のAIチップベンチャー。国家プロジェクトでクラウドコンピューティング向けのAIチップ「MLU100」を開発した実績があり、既に投資家から1億ドルを集めている。

Synopsysの「HAPS」はFPGAベースのプロトタイピング・システムでソフトウェア開発やシステム・バリデーションに活用されている。Synopsysのヒット製品として急速に顧客を増やしている。

2018.05.11

2018年5月11日、ソシオネクストがエッジコンピューティング向けAIアクセラレーターエンジンを開発??型・低消費電?で幅広いアプリケーションを実現

ソシオネクストの開発したエンジン「NNA (Neural Network Accelerator)」は、ディープラーニングの論処理の専用アクセラレーターで、画像認識な

どを?うコンピューター・ビジョン処理において従来型のプロセッサーの約100倍の性能を発揮。

今年Q3にNNA をFPGAに搭載したソフトウェア開発キット (SDK) の提供を開始する予定。さ

らに同エンジンを実装したSoC製品の開発も計画している。

2018.05.07

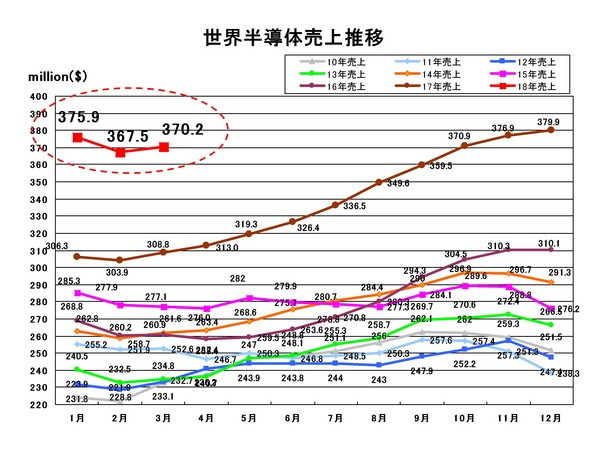

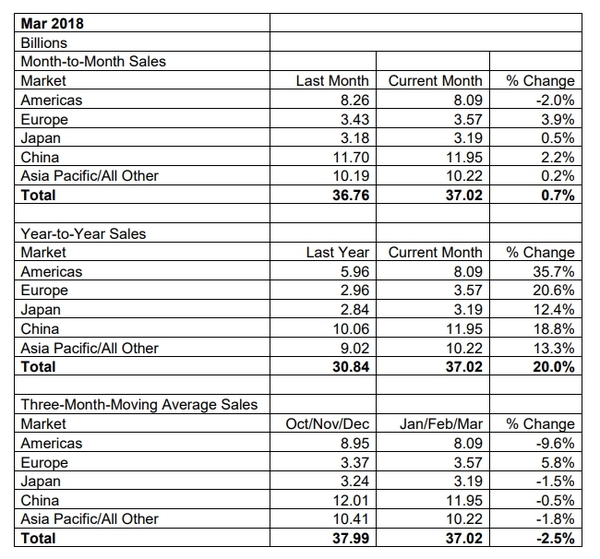

2018年4月30日、米SIA(Semiconductor Industry Association)は、2018年3月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年3月の世界半導体売上は前年同月比20%増、前月比0.7%増の370.2億ドルを記録した。同実績は3月の単月売上としては過去最高で、単月売上が前年実績を上回るのは20ヶ月連続となる。

四半期毎の売上で見ると2018年Q1(1-3月)売上は1110億ドルで前年を20%上回る実績。但し直近の2017年Q4(10-12月)売上に対しては2.5%マイナスとなっている。

2018年3月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。これは8ヶ月連続となる実績。前年比で最も成長したのは北米市場で前年比35.7%増。北米市場は2017年9月から5ヶ月連続で前年比40%増以上の成長を継続していたが、この数ヶ月で成長率が徐々に緩やかになってきている。

日本市場の売上は前年比12.4%増の31.9億ドルで2月実績をわずかに上回った。売上を円ベースで換算すると前年比約5.3%増の約3381億円で前月比約1.5%減となる。

2018.04.19

2018年4月18日、Synopsysは同社のFPGAベースプロトタイピング環境「HAPS」シリーズの新製品「HAPS-80D」を発表した。

Synopsysによると新製品「HAPS-80D」は、既存HAPSシリーズの最上位製品「HAPS-80」をベースに開発されたデスクトップ向けの小型製品で、主に中規模SoCのプロトタイピングをターゲットとしている。既存の「HAPS-80」が搭載するFPGAの個数に応じて最大16億ASICゲートのデザインに対応するのに対して、「HAPS-80D」のFPGA搭載数は最大4個という事だ。

※HAPS-80Dの画像(幅, 奥行き, 高さ = 334.6mm, 373.5mm, 124mm)

「HAPS-80D」の特長として挙げられるのが、デザイン間の相互通信用のインターフェイスが予めシステムに組み込まれている点で、これによりFPGA上に実装したデザインと他のデザインとの相互通信を即座に開始できる。インタフェースとしてはGPIO、UARTsなど、多様なSoCぺリフェラルが用意されている。

既存の「HAPS-80」は、世界的にかなりのヒット製品として知られており、Synopsysによると1500以上ものシステムで活用されているという話だ。

2018.04.19

2018年4月16日、ArmはセキュアなIoTデバイスの開発を狙うSoC設計フレームワーク「Arm SDK-700 System Design Kit」を発表した。

「Arm SDK-700 System Design Kit」の内容詳細は明らかにされていないが、Armの説明によると同キットはArmが提唱するセキュリティ・アーキテクチャ「PSA:Platform Security Architecture」をベースに開発されたSoC開発キットで、Arm Cortex-AおよびCortex-Mプロセッサ、Armサブシステム、プリビルドされたセキュリティIP、プロセッサ間通信のための標準プログラミング・インタフェースなどで構成されている。利用するプロセッサ、サブシステム、セキュリティIPなどはユーザーのニーズに応じて選択可能なようだ。

今回発表された「Arm SDK-700 System Design Kit」の最も重要なポイントは、Armの提唱するPSAに基づいているという点で、急増するIoTデバイスのハードウェアにおけるセキュリティ問題を設計段階でクリアにするという狙いがある。SoCベンダは「Arm SDK-700 System Design Kit」を活用する事でセキュリティ・リスクに関するある種の保証を得られるという寸法だ。

Armは「Arm SDK-700 System Design Kit」の最初の事例としてMicrosoftとのコラボレーションについて発表。「Arm SDK-700 System Design Kit」はMicrosoftが先日発表したセキュリティにフォーカスしたクラウドベースのIoTプラットフォーム「Microsoft Azure Sphere」のセキュリティ要件に対応しており、「Arm SDK-700 System Design Kit」を使用する事で「Azure Sphere」向けのSoCをいち早く市場投入することができるという。

※Microsoft Azure Sphereは、セキュリティ機能を組み込んだMCU、MicrosoftのカスタムLinux、Microsoftのクラウド・セキュリティ・サービスで構成されており、MCUについてはその技術をチップベンダにロイヤリティフリーで提供している。

2018.04.16

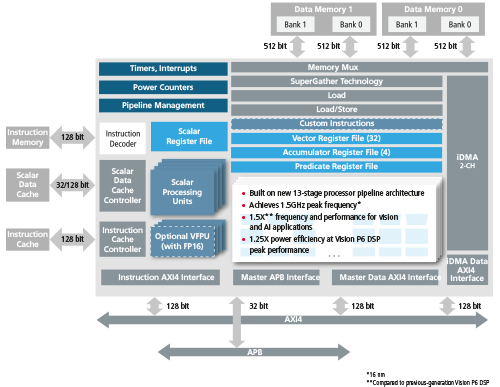

2018年4月12日、Cadenceは、組み込みビジョンおよびAI向けDSPコアの新製品「Cadence® Tensilica® Vision Q6 DSP」のリリースを発表した。

「Tensilica® Vision Q6 DSP」は、組み込みビジョン向けDSPとして5世代目にあたる製品で、前世代の「Vision P6 DSP」を元に開発された新製品。「Vision P6 DSP」は、HiSiliconのAI搭載AP「Kirin 970」にも採用されている。

Cadenceによると前世代の「Vision P6 DSP」のピーク性能と比較して、コンピュータ・ビジョンおよびAI性能は1.5倍、電力効率は1.25倍の向上を実現。「Vision C5 DSP」と共に使用することで、毎秒384GMACを超えるAIパフォーマンスを必要とするアプリケーションにも対応することが可能だという。また、「Vision Q6 DSP」は、「Vision P6 DSP」と同じフロアプラン面積で、1.5GHzのピーク周波数と1GHzの標準周波数を16nmプロセス上で実現するという事だ。

※画像はVision Q6 DSPのブロック図 Cadence webページ公開データ

「Vision Q6 DSP」はAI向けDSPとして、Caffe、 TensorFlow、TensorFlowLiteで開発されたAIアプリケーションサポートをしており、Tensilica Xtensa® Neural Network Compiler (XNNC)によってニューラルネットワークを「Vision Q6 DSP」向けに高度に最適化されたハイパフォーマンスなコードにマッピングし、最適化されたニューラルネットワーク関数ライブラリを活用して「Vision Q6 DSP」の実行ファイルを生成することが可能。Android Neural Network (ANN) APIもサポートしている。

また「Vision Q6 DSP」は、1500以上のOpenCVベースのコンピュータ・ビジョン関数およびOpenVXライブラリ関数に完全に対応しており、既存のコンピュータ・ビジョン・アプリケーションを最適な形で迅速に移行することが可能。「Vision P6 DSP」と後方互換性で既存のソフトウェア資産も「Vision Q6 DSP」に容易に移行できる。

市販のエッジ向け組み込みAIソリューションは、パフォーマンスと電力効率の両面で競い合う状況となっており、各社新製品の投入が相次いでいる。今回Cadenceが発表した「Vision Q6 DSP」は、13段のディープパイプラインに加え、システムデータの帯域幅やメモリー帯域幅を向上させるなど、アーキテクチャを刷新することで大きな性能向上を実現している。

2018.04.11

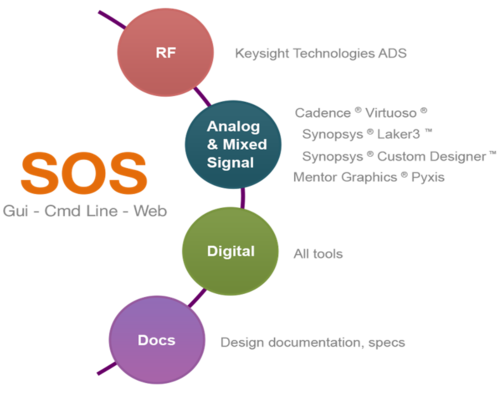

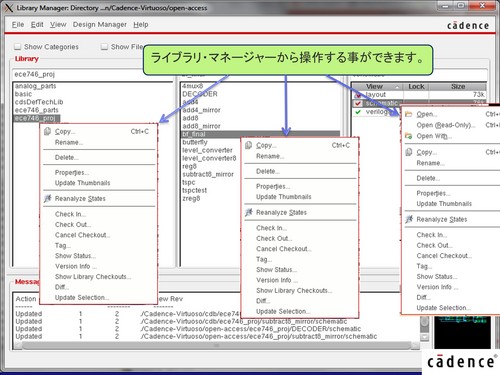

2018年3月、来日していたClioSoft社のCEO Srinath Anantharaman氏に同社の旗艦製品である設計データ管理ツール「SOS」と新製品「Design HUB」について話を聞いた。

Srinath Anantharaman氏

Srinath Anantharaman氏によると、ClioSoftは同氏が1997年に設立したプライベート企業で本社はカリフォニア州フリーモントにある。ClioSoftのビジネスの中心は設計データの管理ツール「SOS」の開発・販売で、同ツールの顧客企業はワールドワイドで250社以上、日本にも10社以上のユーザーが存在しているという話だ。

「SOS」はEDAツールで扱う設計データに特化したデータ管理ツールで、大きく下記4つのデータ管理機能を備えている。

・リビジョン管理

リビジョン管理を自動で行い古いデータを保持

・履歴管理

データ作成、変更の時間とユーザを記録

・ステータス管理

データの状態を把握しユーザに告知

・付属情報管理

必要なコメントやラベルをデータと共に管理

「SOS」は設計データフォーマット、「OpenAccess」を使用するEDA各社のツールに対し統合されたインターフェースを用意しているため、アナログ、デジタル、ミックスド・シグナル、RFとあらゆるデザインへの対応が可能である。中でもCadenceのアナログ/カスタム設計環境「Virtuoso」のユーザーには重宝されており、様々な設計データを「Virtuoso」のコックピットからCellレベルで管理できる点などが高く評価されているという。

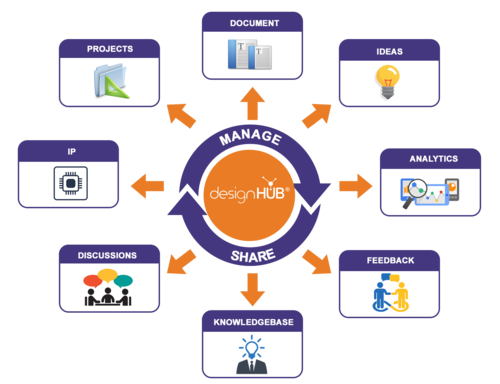

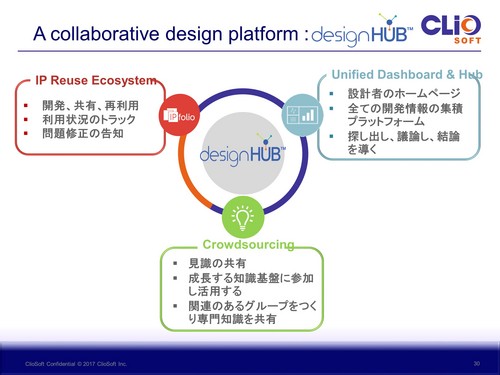

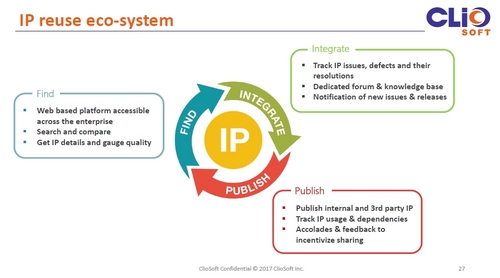

この「SOS」による設計データ管理の実績を踏まえ、企業内における設計IPのデータ管理すなわちIP再利用に目を付け開発したのが、昨年のDesign Automation Conferenceで発表されたClioSoftの新製品「designHUB」である。

Srinath Anantharaman氏によると「designHUB」は、「SOS」同様チーム・コラボレーションを念頭に置いた製品で、企業内のユーザーが設計データとIPをより簡単に作成、共有、再利用できるIP再利用エコシステムの構築を目指すもの。ここで言うIPには設計IPだけでなく、検証IPや各種ドキュメント、スクリプト、ライブラリ、更にはアイデアや知識、メソドロジなども含められているという。

Srinath Anantharaman氏の説明によると「designHUB」はWebベースのプラットフォームで、下記図の通り3つの要素で構成されている。

・IP再利用:IP再利用のためのエコシステム

・ダッシュボード:デザイン・プロジェクトのための情報共有機能

・クラウドソーシング:社内の専門知識を共有するための情報共有機能

IP再利用のためのエコシステムは「designHUB」の中核とも言えるもので、単なる社内IPカタログではなくフォーラム機能が備えられているのが面白いところ。このフォーラム機能を通じてIPユーザーが過去のIP利用者のレビューを参照したり、利用者に直接質問を投げたりする事ができる。Srinath Anantharaman氏曰く、Amazonでレビューを参考に買い物するような感じで社内IPを探すことができるという事だ。また、「designHUB」ではIP再利用に関するセキュリティにも配慮がなされており、社内IPを登録・利用するための承認システムも用意されている。

※画像は全てClioSoft社提供のデータ

ダッシュボードは、プロジェクト管理とプロジェクトのナレッジベースを兼ね備えたもので、プロジェクトのスケジュール管理やタスク管理、ドキュメント共有などの他に、メールや各種電子ファイルなど様々なアプリケーションに分散して存在しているプロジェクトに関する情報を集約しIPリポジトリにアップロードする機能も備えている。これによりプロジェクトに関する作業の知識を設計者個人に頼らず社内に保持できるという事だ。

クラウドソーシングは、社内に散らばる設計者の専門知識を共有するためのもので、これにより部署や事業所を跨いだ社内コラボレーションや共同作業を実現する事ができる。例えば設計者が何か技術的な問題に遭遇した際に、社内の誰かに解決策を質問したり、助けを求めたりできる設計者向け社内SNSのようなものだ。

実際にSrinath Anantharaman氏に「designHUB」のデモを見せてもらった印象としては、非常に洗練されたシステムで、その使い勝手はSlack/FacebookにIP再利用のための豊富なインフラ機能が組み合わさったような感じ。(表現は分かり難いかもしれませんが、使い勝手が良さそうという意味)文字通りデザインのハブとして様々な情報を共有するという機能がビジュアル的にもわかり易く実現されている。

Srinath Anantharaman氏によると既に複数の大手企業が「designHUB」の導入を進めているという事で、その背景にはデザインの大規模化・複雑化への対応と合わせて、人材の流動化に伴う知識の喪失を防ぐという狙いもあるという。確かに「designHUB」のようなプラットフォームがあれば、仮に設計者が辞めてもその知識を会社に残しておく事が可能かもしれない。

情報の共有/シェアという概念が一般化した今日において、ある意味「designHUB」は有りそうで無かったツールと言えるが、Srinath Anantharaman氏はWikipediaが生まれる前から「designHUB」の原点と言える同社の設計データ管理ツール「SOS」の構想を持っていたとの話。一人一人の設計者の知識を共有し、グループ全体の生産性の向上を目指すというClioSoftのアプローチは、これからのハードウェア設計でより重要となって行く事だろう。

2018.04.03

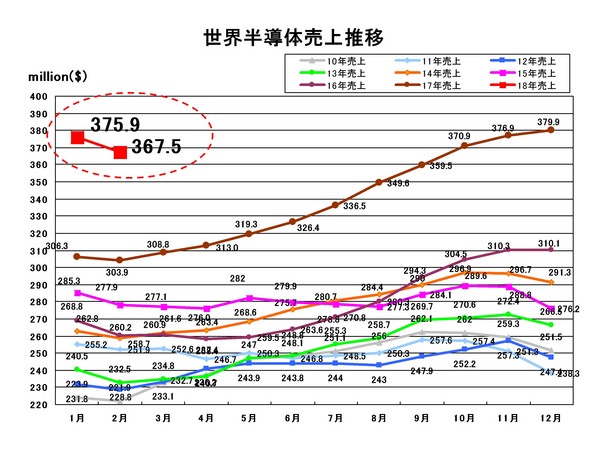

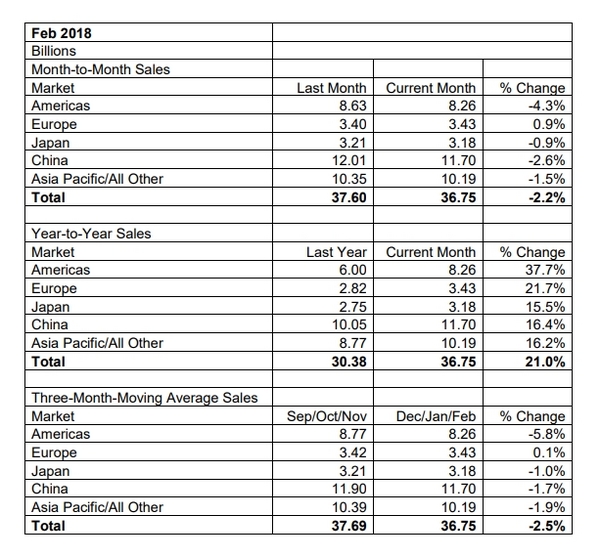

2018年4月2日、米SIA(Semiconductor Industry Association)は、2018年2月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年2月の世界半導体売上は前年同月比21%増、前月比2.2%減の367.5億ドルを記録した。同実績は2月の単月売上としては過去最高で、単月売上が前年実績を上回るのは19ヶ月連続となる。

2018年2月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。これは7ヶ月連続となる実績。前年比で最も成長したのは北米市場で前年比37.7%増。北米市場は2017年9月から5ヶ月連続で前年比40%増以上の成長を継続していた。

日本市場の売上は前年比15.5%増の31.8億ドル、1月実績を下回った。売上を円ベースで換算すると前年比約10.3%増の約3431億円で前月比約3.5%減となる。

2018.03.27

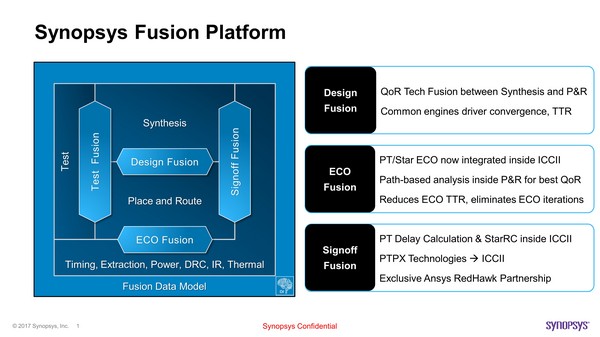

2018年3月19日、Synopsysはシリコンバレーで開催したユーザー・イベントで新たな設計技術「Fusion Technology」を発表した。

Synopsysによると「Fusion Technology」は同社の最適化テクノロジと業界標準となっているサインオフ・テクノロジを融合させる新技術で、設計品質を確保しながら開発期間の短縮を実現するもの。同技術の対象の中心となるのはSynopsysの下記ツール群で、Synopsysは具体的に4つの「Fusion Technology」を提案している。

・Design Fusion:共通の設計エンジンによる論理合成と配置配線の融合

・ECO Fusion:配置配線工程におけるサインオフ技術の融合

・Signoff Fusion:サインオフ工程とデザイン最適化工程の融合

・Test Fusion:テスト容易化のためのRTL解析と論理合成の融合

【Fusion Technologyの主な対象ツール】

-配置配線ツール IC Compiler™ II

-論理合成ツール Design Compiler® Graphical

-スタティックタイミング・サインオフ・ツール PrimeTime®

-RC 抽出サインオフ・ツール StarRC™

-フィジカル検証サインオフ・ツール IC Validator

-テスト圧縮ツール DFTMAX™

-テストパターン自動生成ツール TetraMAX® II

-テスタビリティ解析ツール SpyGlass® DFT ADV RTL

-機能等価性検証ツール Formality®

※画像はSynopsys提供のデータ

Synopsysの「Fusion Technology」の狙いは、従来のRTL to GDSII設計フローにおける各工程間の境界線を無くし「設計のやり直し」を防ぐことにあり、それを実現するためにSynopsysはツール間で共有できるエンジンや独自の「Fusionデータモデル」を用意している。

また、この「Fusion Technology」はSynopsysのツール内に閉じたものではなく、サードパーティー製ツールとの融合も視野に入れられており、Synopsysの配置配線ツール「IC Compiler II」とAnsysのパワー解析ツール「RedHawk」を融合する「RedHawk Analysis Fusion」という新製品が発表されている。

発表に寄せられたSamsung Electronics ASIC&IP事業部 上級副社長 Jaehong Park氏のコメントによると、Design Fusionを使うことで結果品質が10%向上し、ECO Fusionを使うことでECO終了までにかかる期間を1日以内に短縮することができたという。

2018.03.23

2018年3月19日、SynopsysはAnsysとのコラボレーションによる新製品「RedHawk Analysis Fusion」の提供開始を発表した。

今回発表された新製品「RedHawk Analysis Fusion」は、Synopsysの配置配線ツール「IC Compiler II」にAnsysのパワー解析ツール「RedHawk」の機能を融合するもので、Synopsysが自社の「IC Compiler II」ユーザーに向けて提供するもの。SynopsysはAnsysのパワーインテグリティ/信頼性解析技術についてAnsysと独占提携しており、「RedHawk Analysis Fusion」は両社のパートナーシップによる最初の製品となる。

「RedHawk Analysis Fusion」を利用する事で「IC Compiler II」ユーザーは以下のような作業が可能となる。

・IC Compiler IIを使いながら設計フローの要所要所でRedHawkのスタティック/ダイナミック・パワー解析を実行

・IC Compiler IIを使いながら設計早期段階でRedHawkのパワーグリッド・インテグリティ・チェックを実行

※いずれの作業も「IC Compiler II」のコックピット上で実行可能

Synopsysは「IC Compiler II」と「RedHawk」を融合したこれら作業により、ECOの発生数と期間を削減する事が可能で、開発期間を最大1/5に短縮できるとしている。

「RedHawk Analysis Fusion」は、既に先行ユーザーが複数存在しているようで、先頃シリコンバレーで開催されたSynopsysのユーザー・イベントにて東芝デバイス&ストレージ社が「RedHawk Analysis Fusion」の活用事例を発表したようだ。

2018.03.23

2018年3月15日、AIチップを手掛けるシリコンバレーのタートアップSambaNova Systemsは、資金調達Aラウンドで複数のベンチャー・キャピタルから5600万ドルを調達した事を発表した。

今回SambaNova Systemsの資金調達を主導したのは、Walden InternationalとGoogle Venturesの2社。Walden Internationalは、CadenceのCEOであるLip-Bu Tan氏が率いるベンチャー・キャピタルで、Lip-Bu Tan氏はSambaNova Systemsのチェアマンに就任する。

SambaNova Systemsは、Olacleのプロセッサー開発部門の元シニアVP Rodrigo Liang氏が2017年に設立したスタートアップで、プロセッサーの専門家でありマルチコア・プロセッサーの父と称されるスタンフォード大学のKunle Olukotun教授とデータベース理論/機械学習の専門家であるChris Ré教授の技術をベースとしている。

詳細は明らかではないが、同社のソリューションは独自の機械学習アルゴリズムとソフトウェア定義型のハードウェアを組み合わせたコンピューティング・プラットフォームで、機械学習や大規模なデータ解析アプリケーションで前例のないパフォーマンスの実現を目指すという。

2018.03.20

2018年3月19日、ハードウェア設計言語・技術の標準化団体米Accellera Systems Inisiativeは、IPのセキュリティ保証要件の定義を目指す新たな「IP Security Assurance Proposed Working Group (PWG)」 の始動をアナウンスした。

今回Accelleraが立ち上げたIP Security Assurance PWGは、IPのセキュリティ保証要件の必要性や実現可能性を議論するもので、WG(ワーキンググループ)発足前のフォーメーションと言えるもの。同分野への関心、標準化の必要性の認識、技術的な見通しが固まれば、今後同PWGはIPのセキュリティ保証要件の定義をゴールとするワーキンググループへと発展していく。

IPのセキュリティ保証要件の標準化が求められる背景には、世の中のIoT化と共に深刻化するセキュリティへの脅威があり、サードパーティ製IPの利用におけるセキュリティ面でのリスクを最小限に抑えたいという半導体業界における横断的な要求がある。標準化されたセキュリティ保証基準が策定されれば、個々のIPのセキュリティ品質を認証する事が可能となり、半導体ベンダは通常ブラックボックスとして扱うサードパーティ製IPをセキュリティの面で安心して使用できるようになる。

IP Security Assurance PWGの最初の会合は来月17日にサンタクララで開催される予定。同会合にはAccelleraのメンバーに限らず誰でも参加可能で、既にCadence、Intel、Mentor(Siemens)、Sonics、Synopsys、Qualcommといった企業が参加に関心を示している。

■ポータブル・スティミュラス

標準化団体米Accellera Systems Inisiativeの動向としてもう一つ。

同団体は標準化作業を進めている「Portable Test and Stimulus Standard」のEarly Adopter IIバージョンのパブリックレビューを開始した。同バージョンは昨年公開したEarly Adopterのユーザー・フィードバックを反映したもので2018年3月30日までダウンロード可能。

「Portable Test and Stimulus Standard」は、SoC開発における各開発フェーズのテストの一貫性やテスト全体の効率性向上を目的とした新たな標準仕様言語で、同言語を用いる事で単一記述からシミュレーション、エミュレーション、FPGA、ポストシリコンなど複数のターゲットに対するスティミュラスとテストを自動生成できるようになる。

「Portable Test and Stimulus Standard」の詳細(DVCon2018で公開されたチュートリアル資料)はこちら

「Portable Test and Stimulus Standard」Early Adopter IIのダウンロードはこちら

2018.03.13

2018年3月7日、機械学習向けのコンピューティング・システムを手掛けるWave Computingは、同社の次世代チップにMIPSコアを採用した事を発表した。

Wave Computingはシリコンバレーのベンチャーで「Dataflow Processing Unit(DPU)」と呼ぶ独自のアーキテクチャによって高性能な機械学習を実現する。

Wave Computingは既にDPUを実装した独自のディープラーニング・チップを提供しているが、次世代のDPUチップにMIPSの64bitマルチスレッド・コアを採用する事を決定したという。

MIPSはImagination Technologiesから分離独立し独立企業としてシリコンバレーで再始動している。

2018.03.13

2018年3月5日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けツールを中心に各種EDAソリューションを展開するSilvacoは、スタンダード・セル・ライブラリ開発向けのEDAソリューションを手掛ける米Nangateの買収を発表した。

米Nangateはデンマーク生まれのEDAベンダで、250nmから14nmまで幅広いCMOSプロセスに対応したスタンダード・セル・ライブラリ開発ツールと開発サービスを提供。ワールドワイドに多数の顧客を持つ老舗のEDAベンダと呼べる存在で、日本国内にもNangateのユーザーが存在している。

Silvacoは大手の寡占が進むEDA業界において独自の路線で積極的な買収を進めており、この3年間でNangateを含めて6社を買収している。

2018.03.07

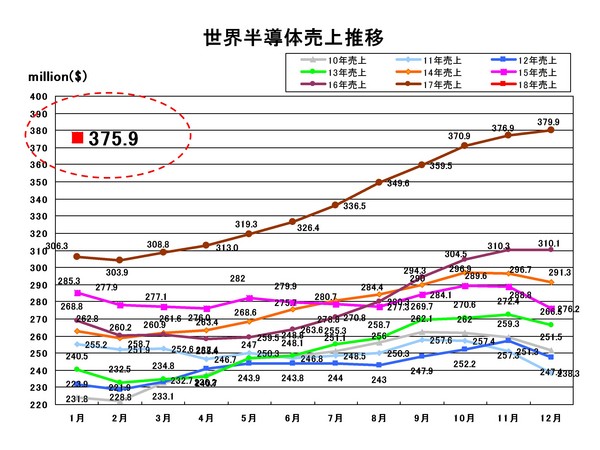

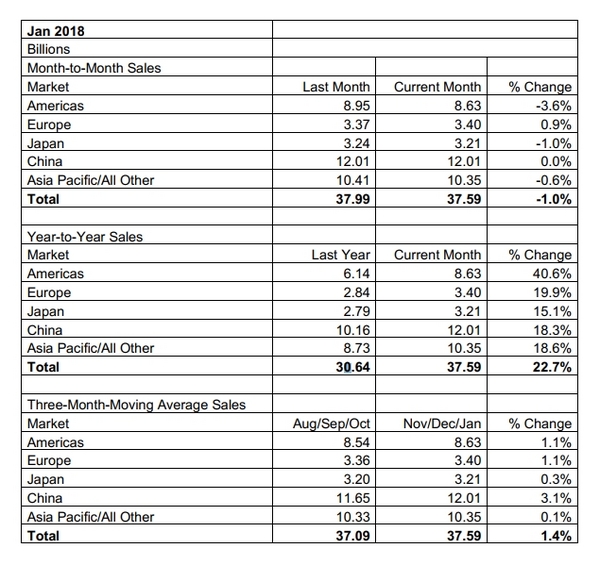

2018年3月5日、米SIA(Semiconductor Industry Association)は、2018年1月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年1月の世界半導体売上は前年同月比22.7%増、前月比1%減の375.9億ドルを記録した。同実績は1月の単月売上としては過去最高で、過去の実績と比較すると非常に高いものとなる。単月売上が前年実績を上回るのは18ヶ月連続となるが、2017年4月から続いていた単月売上記録の更新は2017年12月で止まった。

2018年1月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。これは6ヶ月連続となる実績。前年比で最も成長したのは北米市場で前年比40.6%増。北米市場は2017年9月から前年比40%増以上の成長を継続している。北米に次ぐ成長を見せたのは中国市場で前年比23.3%増だった。

日本市場の売上は各地域の中では最も低い32.1億ドル、対前年比は15.1%増と1月を上回った。売上を円ベースで換算すると前年比約11%増の約3555億円で前月比約2.9%減となる。

2018.02.28

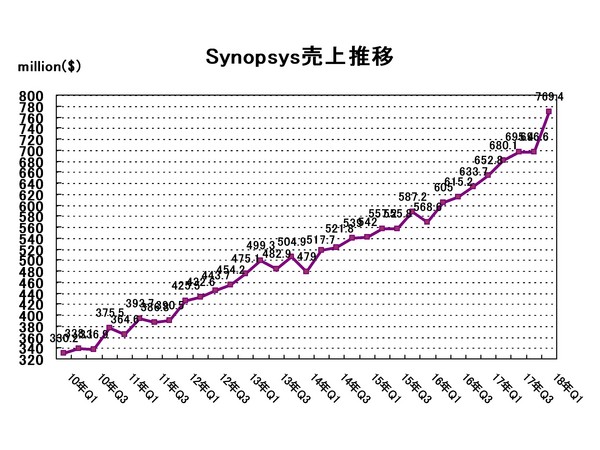

2018年2月21日、Synopsysは、2018会計年度第1四半期(17年11-18年1月)の四半期決算を報告した。

発表によると、Synopsysの2018会計年度Q1の売上は、前年同時期比約17.9%増の7億6940万ドル、収支は370万ドルの損益を計上した。(※GAAP基準による会計結果)

同社は前期Q4において四半期売上記録を更新していたが、今期Q1はQ4実績を10%ほど上回り再び四半期売上記録を更新した。

Synopsysはこの11-1月の間に「HDMI 2.1 IPソリューション」、ARCプロセッサ開発キット「ARC HS Development Kit」などのリリースを発表している。

Synopsysは次の2018会計年度Q2(18年2月-4月)の売上を7億6500-7億9000万ドルと予測している。

2018.02.15

2018年2月14日、三菱電機は同社のAI技術「Maisart(マイサート)」をベースとしたハードウェアAIの開発を発表した。

発表によると今回三菱電機が開発したのは、ディープラーニング推論用のFPGAで同社のAIアルゴリズムを最適化してFPGAに実装したもの。FPGAへの実装にあたりAIアルゴリズムの計算順序を効率化することで、従来の推論の精度を維持しながら処理にかかる演算時間を10分の1に短縮した。

※画像は三菱電機Web上のデータ

三菱電機は小規模なFPGAにAI技術を実装することで、推論処理のリアルタイム性の向上、ハードウェアコストの低減、低消費電力化といったメリットが得られ、AI技術の適用分野を拡大できるとしている。

2018.02.09

2018年1月31日、Cadenceは、2017会計年度第4四半期(2017年10-12月)の売上を報告した。

Cadenceの2017年Q4売上は、前年同時期比約7%増、前期Q3比約3.5%増の5億200万ドルで四半期売上記録を更新した。この結果はQ3売上報告時の予測を上回るもので、四半期売上記録の更新はこれで5四半期連続となる。Q4の収支は1400万ドルの損益を計上した。(※GAAP基準による会計結果)

Cadenceの2017年度の売上合計は前年比7%増の19億4300万ドルで過去最高を記録。純利益は昨年とほぼ同等の2億400万ドルだった。Cadenceはこの7年間で売上を倍以上に伸ばしている。

Cadenceはこの10-12月に、超高速SerDesの専門IPベンダーnusemi社の買収、PCI Express 5.0検証IPのリリース、チーム設計向けのPCB設計プラットフォーム「Allegro® Pulse」のリリースなどを発表している。

Cadenceは、2018会計年度Q1の売上額を5億-5億1000万ドルと予測している。

2018.02.08

2018年1月29日、Synopsysは、ハイエンド組込みプロセッサ「ARC HS」の開発キットの提供開始を発表した。

Synopsysによると今回発表した開発キット「ARC HS Development Kit」は、ARC HS34,ARC HS36,ARC HS38をベースとしたシステムをターゲットとしたもので、ARC HSプロセッサを搭載したボードとソフトウェアが提供される。

ボードにはTSMC 28 HPMプロセスで実装したマルチコアARC HSベースのチップが搭載されており、ARC HS34プロセッサはシングルもしくはデュアル・コア構成で、ARC HS36/HS38プロセッサはシングル/デュアル/クワッド・コア構成でコンフィギュレーション可能。以下のような豊富なペリフェラルが用意されている。

・Ethernet、USB、SDIO、I2C、SPI、UART、GPIO

・Vivante GC7000 Nano Ultra GPU

・WiFi,Bluetoothモジュール

・4GB DDRメモリ

各種ドライバ、FreeRTOSなど開発キット用のソフトウェアは、全てオープンソースでSynopsysの「embARCウェブサイト」で入手可能。「ARC HS Development Kit」はLinuxカーネル、Yocto、Buildrootシステムもサポートしている。

また「ARC HS Development Kit」は、SynopsysのFPGAベース・プロトタイピング・システム「HAPS」と容易に接続することが可能なほか、Digilent Pmod、Arduino、mikroBUSなど各種ボードモジュールを接続して拡張することもできる。

「ARC HS Development Kit」は既に入手可能で、ARC HS3xプロセッサ・ベース・システムのソフトウェア開発に利用できる。

2018.02.06

2018年2月5日、米SIA(Semiconductor Industry Association)は、2017年12月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2017年12月の世界半導体売上は前年同月比22.5%増、前月比0.8%増の379.9億ドルで9ヶ月連続の単月売上記録更新を達成。単月売上が前年実績を上回るのは17ヶ月連続となる。

最終的に2017年1-12月の売上合計は前年比21.6%増の4122億ドルで史上最高額。ついに4000億ドルの大台を突破した。2017年の売上を大きく伸ばしたのは何と言ってもメモリで、前年比61.5%増の1240億ドルを記録。DRAMの売上は前年比76.8%増、NAND flashの売上は前年比47.5%増と急成長した。メモリに次いで売上の大きいLogic製品は前年比11.7%増の1012億ドルだった。

2017年12月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録しており、これは5ヶ月連続となる実績。7月以降急成長を継続している北米市場は前年比41.4%増と11月を上回る結果を残した。欧州市場は前年比20.2%増と北米に次ぐ成長率を10月以降維持している。トップシェアの中国市場は欧州に次ぐ前年比18.1%増の成長だった。

日本市場の売上は各地域の中では最も低い32.4億ドル、対前年比は14%増と11月を上回った。売上を円ベースで換算すると前年比約11.2%増の約3659億円で前月比約0.8%増となる。

2018.02.05

2018年1月17日、FPGAベンダAchronix Semiconductorは、同社のSoC組込型FPGA「Speedcore IP」を実装したテストチップの検証完了を発表した。

発表によると「Speedcore IP」を実装したテストチップはTSMC 16nm FinFET+プロセスで製造したもので、同チップを搭載したボードを用いてAchronixの先行顧客が500MHz動作のアプリケーションで検証したという。

Achronixは元々1.5Ghz動作の高速FPGAで市場に参入したFPGAベンダで、Intelの22nm FinFETプロセスを用いた通信向けの高速FPGA「Speedster22i」が注目を集めていた。

同社がSoC組込型のFPGA「Speedcore IP」をリリースしたのは2016年10月とそう古くはないが、AI/ML, HPC, データセンターなどのアクセラレーション・ニーズに乗り上手くビジネスを拡大。2017年の売上は前年比700%の1億ドルに到達した。

「Speedcore IP」はハードウェア・アクセラレータとして1-200万個のLUTと組込みメモリ、DSPブロックをSoCに追加する事が可能。スタンドアロンのFPGAを使用するよりもダイエリアの小型化、高性能化、低消費電力化が可能で、システム全体のコスト削減を実現できるという。

「Speedster22i」と「Speedcore IP」は共通の専用開発ツール「ACE」で設計を行うが、同ツールの中ではSynopsysの「Synplify-Pro」が利用されている。

なお、Achronixは今年「Speedcore IP」を用いたカスタムチップの新製品「SpeedChip」と「Speedster22i」の後継となる通信向けの新型FPGAをリリースする計画のようだ。

2018.02.02

2018年1月23日、Synopsysは同社のDFTソリューション「DFTMAX LogicBIST」の採用事例を発表した。

今回発表したのはルネサス エレクトロニクスによる採用事例で、ルネサスは車載向けミックスドシグナル製品のデジタル・ロジック部のパワーオン・セルフテストに「DFTMAX LogicBIST」を採用した。その背景には、機能安全対応において、ミックスドシグナル製品の比較的規模の小さい論理部においても起動時の高い診断カバレッジが要求されるという事情があるようだ。

「DFTMAX LogicBIST」には、チップ起動時の製造故障をチェックしてレポートするパワーオン・セルフテスト(POST)機能が備えられており、少ない工数で高い故障テスト・カバレッジを達成可能。Synopsysの「DFTMAX™」ベースのテスト圧縮フローに容易に統合できる点もユーザーにとってのメリットとなっている。

なお、ルネサスではより故障カバレッジを上げる手段として、RTLレベルで故障検出率を解析する「SpyGlass DFT」も活用する場合があるという。