NEWS

2018.06.20

2018年6月18日、フォーマル検証技術をベースとしたEDAソリューションを手掛ける米Real Intentは、新製品「Verix PhyCDC」を発表した。

発表によるとReal Intentの新製品「Verix PhyCDC」は、ゲートレベルのネットリストでCDC違反のデバッグを行うツールで同社のRTLサインオフ向けCDCソリューションを補完するもの。RTLでのCDCの結果を活用してCDCのパスと制約を識別し、ゲートレベルでのCDC分析を最適化。制御信号、クロック・ネットワーク、データシグナル・パスのグリッチなどの誤動作やクロック・シンクロナイザー・ロジックの誤った最適化などに対処する。

CDC検証は一般的にRTLサインオフを対象としているが、「Verix PhyCDC」のアプローチは合成の段階で生まれるCDCの問題に着目している点が特徴。「Verix PhyCDC」によるネットリストの検証はRTLの制約を再利用して簡単にセットアップする事が可能で、ランタイム削減のための並列処理機能や差分分析機能なども備えている。

Real Intentは、6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceにて新製品「Verix PhyCDC」を展示する予定。

2018.06.20

2018年6月19日、Fudzillaの記事:

Samsungは以前からGPUの内製を進めており、それは最終ラインに近づいている。SamsungはQualcommとのクロスライセンス契約によりGPU開発に必要なソースを入手した可能性がある。

2018.06.20

2018年6月19日、ZDNetの記事:

Hewlett-Parckard EnterpriseがArmベースのスーパーコンピューター「Astra」を開発した。「Astra」はCaviumのサーバー向けSoC「Thunder X2」をベースに構築されており、Arm v8ベースのカスタムCPUを5,184個搭載。理論上のピーク性能は2.3PFLOPS以上に達する。「Astra」は米Sandia National Laboratoriesと米エネルギー省National Nuclear Security Administrationに納入される。

2018.06.20

2018年6月19日、Digitimesの記事:

SamsungがEUVを用いた10nmクラスのDRAM開発を開始。2020年までに量産に入る見通し。

2018.06.20

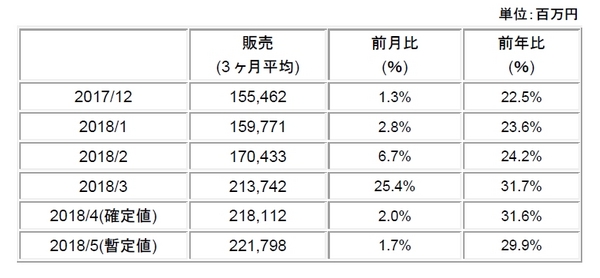

2018年6月19日、日本半導体製造装置協会は2018年5月の半導体製造装置速報値を発表した。

発表によると2018年5月の日本製装置(輸出を含む)の販売高は、前月比1.7%増、前年同月比29.9%増の2217億9800万円だった。

2018.06.19

2018年6月18日、Synopsysはエミュレーターの新製品「ZeBu Server 4」のリリースを発表した。

発表によると「ZeBu Server 4」はXilinxの20nm FPGA「Virtex UltraScale VU440」をベースとしたエミュレーターで、競合製品の2倍のエミュレーション性能を誇る。またその所有コストは業界最小で競合製品の半分程度の筐体面積で5倍のローパワー性能を実現する。

Synopsysのエミュレーター「ZeBu」シリーズは、専用プロセッサを用いる他社のエミュレーターと異なるFPGAベースのエミュレーターで、FPGAの進化と共に性能のスケールアップを続けており、ここ数年の急速な販売実績により現在エミュレーター市場でトップシェアを誇っている。

新型の「ZeBu Server 4」に関する詳細は、6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceで披露される予定。Synopsysは6月26日に「SoC Leaders Verify with Synopsys luncheon」を開催し、その場で「ZeBu Server 4」の説明を行う。

2018.06.19

2018年6月18日、標準化団体CCIX Consortiumは、CCIX Base Specification 1.0のリリースを発表した。

CCIXはCCIX Consortiumが標準化を進めるハードウェア・アクセラレータ向けのチップ間インターコネクト仕様で、プロセッサとハードウェア・アクセラレータがキャッシュ・コヒーレントな形でシームレスにメモリーを共有できるようにすることを目指している。CCIX Consortiumの創設メンバーにはAMD, Arm, Huawei, Qualcomm, Xilinxらが名を連ねており、データセンターでの利用が想定されている。

2018.06.19

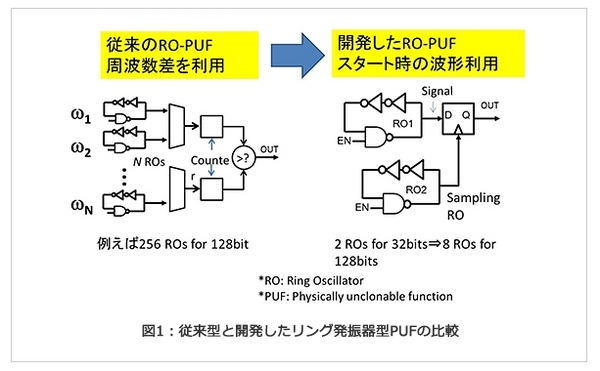

2018年6月14日、東芝はIoT機器の個体認証向け新たなPUF技術を開発した事を発表した。

PUF(Physical Unclonable Function)はチップのばらつきを利用して暗号を生成する技術で安全性が高く低コストなセキュリティ技術として知られているが、実装が複雑で回路の配線に対称性が求められるなどの制約もある。

今回東芝が開発したPUF技術は、回路の対称性等の制約がなく、FPGAのように書き換え可能な回路にも容易に実装できるもの。発振回路の初期出力波形をIDとして採用する方式により、回路に電流を流し続ける必要がないことから消費電力を抑える事もできるという。

東芝は開発したPUF技術により、IoT機器における個体認証やデバイスの複製・偽造防止が簡単に実現できるとしており、自走ロボットによる相互認証の実証実験を行った。

2018.06.18

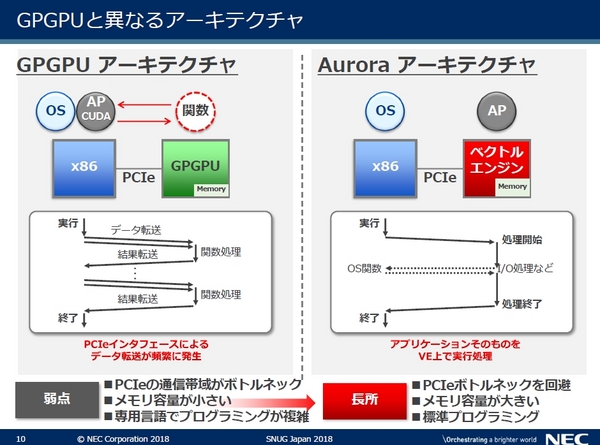

2018年6月13日、Synopsysのユーザーミーティング「SNUG Japan 2018」で行われたNECによるセッション、新プラットフォーム「SX-Aurora TSUBASA」開発におけるHAPS活用事例のレポート。

講演者:日本電気株式会社 AIプラットフォーム事業部 技術エキスパート 内堀 修作氏。

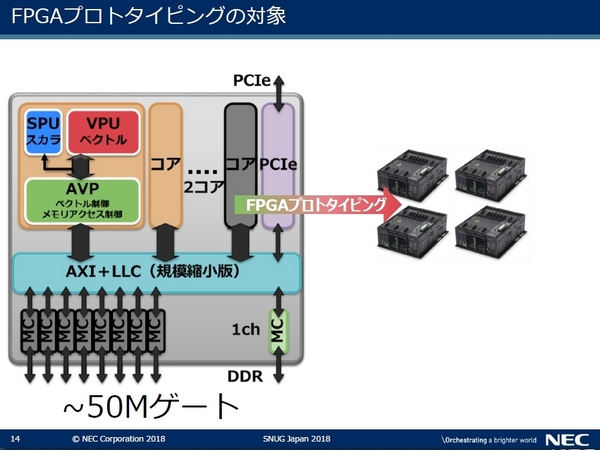

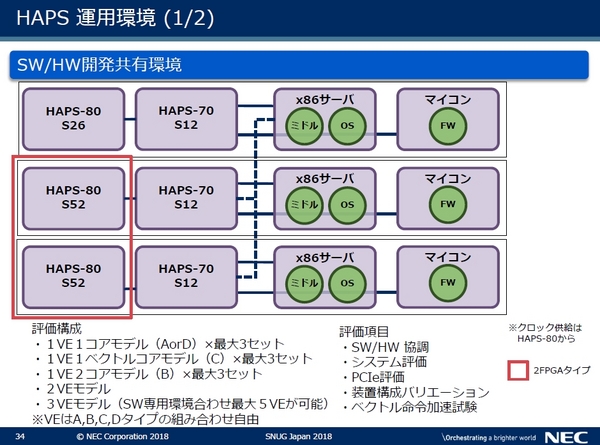

同セッションは、NECのスーパーコンピュータ「SX-Aurora TSUBASA」に搭載されている新型のベクトルプロセッサのFPGAプロトタイピングの事例である。使用したのはSynopsysのFPGAプロトタイピング環境「HAPS-70」と「HAPS-80」で、NECは最終的に「HAPS」を計10台近く導入した。

内堀氏によると「SX-Aurora TSUBASA」は従来のSXシリーズ製品とは異なる思想で開発された新アーキテクチャ、新ベクトルプロセッサを用いたPCI Expressカード型のシステムで、Linux上のプロセスをHW化したようなイメージでアプリケーションを丸ごとベクトルプロセッサ上で実行できる。これによりPCI Expressのボトルネックを回避した高速演算が実現できる他、これまで開発していたスパコン専用OSの開発が不要になるなどのメリットがある。

今回NECは、「SX-Aurora TSUBASA」の新しいアーキテクチャの実証やベクトルプロセッサをLinux上のプロセスに見せかけるためのソフトウェアの検証などを目的に、初めてRTLベースのFPGAプロトタイピング環境の導入を考えた。

「HAPS」導入前に8コア構成のベクトルプロセッサのプロトタイピングを検討した結果、デザインの大きさからベクトルプロセッサの構成を2コアにしペリフェラルも縮小した形でプロトタイピングする事にした。当初はプロトタイピング・ボードの内製も検討したがスケジュール的に厳しく、市販のプロトタイピング環境の導入を検討。外部I/Fの自由度やSynopsys製の設計IPの利用を考えていた事から「HAPS-70」を導入することにした。

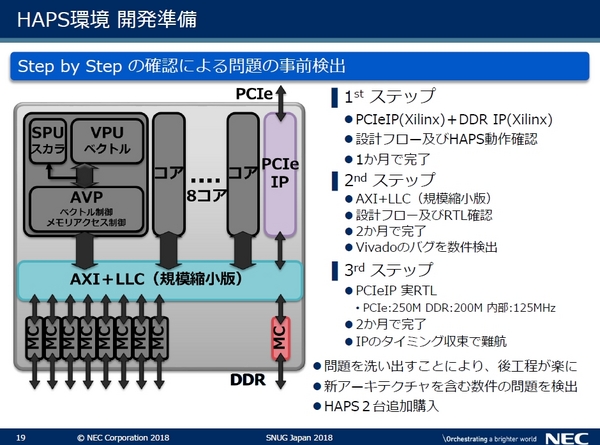

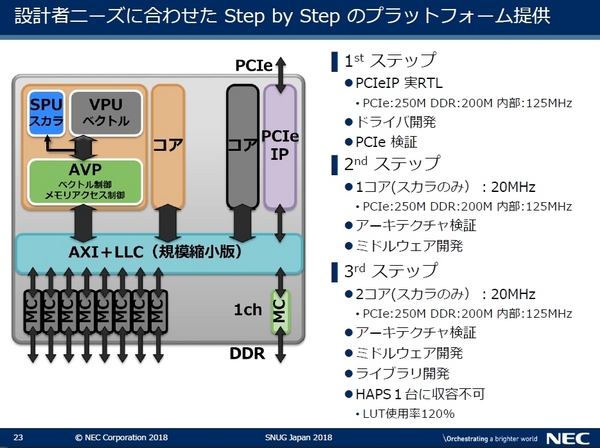

「HAPS-70」を用いたプロトタイピングは3つのステップに分けて計5ヶ月かけて実施した。その結果、新アキーテクチャを含む数件の問題を検出。HAPS自体の問題は特に無く、これは使えるという判断で更に「HAPS-70」を2台追加で導入した。なお、社内ユーザーへのHAPS環境の提供にあたっては事前にSWおよびHW開発者と意識合わせを行い、設計者のニーズに合わせた形で出来上がった環境をステップバイステップで提供していく形をとった。また、HAPSへのデザインの分割は環境の使い回しを重視した。

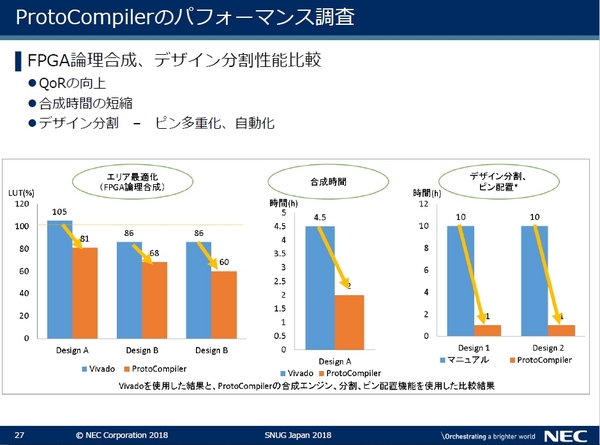

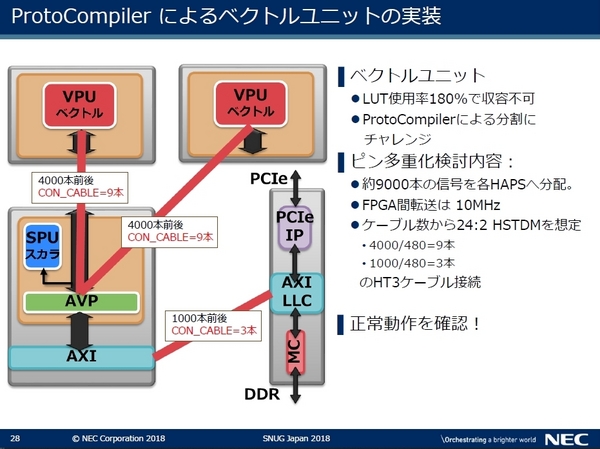

デザインの実装については、HAPSのデザイン環境「ProtoCompiler」とXilinxのデザイン環境「Vivado」の両方を試して比較した。ベクトルプロセッサのベクトルユニットの実装においては「ProtoCompiler」の方が優れた結果を出し、デザイン分割もスムーズに完了した。新型の「HAPS-80」を使った例では「Vivado」で配線NGでも「ProtoCompiler」を使えば配線を完了できたという。

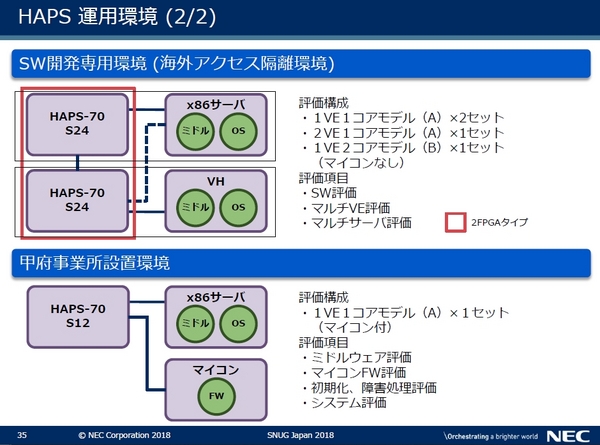

NECでは最終的に評価環境に合わせて10種類のモデルを準備し、海外を含む4拠点でコンフィグレーションを切り替えてHAPS環境を運用。運用の管理にはHAPS専用の「ConfPro」というソフトを用いてほぼ24時間の稼働を実現した。結果的にHAPSを導入した事で開発期間の短縮を実現。製品の出荷を約6ヶ月前倒しすることができたという事だ。

内堀氏は最後に「HAPS活用でわかったFPGAプロトタイピング3つのポイント」を挙げて講演を終えた。

・Reality いかに実機に近づける事ができるか?

・Accessibility いかに早く構築、そして簡単に使えるか?

・FPGAならではの付加価値 不具合解析、トレース機能などの活用

2018.06.18

クラウドベースのシミュレーション環境を提供するMetrics Technologiesは、6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceに初出展する。

Metricsは、デザイン及び検証サービスを手掛けるカナダXtremeEDAのメンバーがスピンアウトして設立したEDAベンチャーでカナダのオタワに本拠を構える。

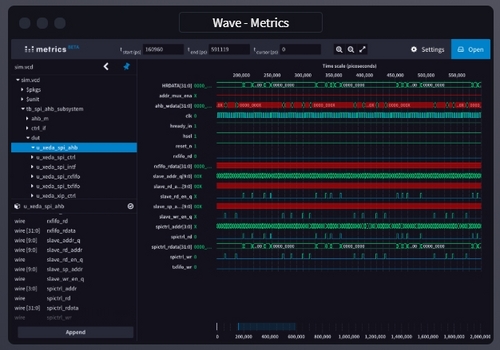

Metricsが提供するのは「Cloud Simulator」と「Verification Manager」の2製品で、

いずれもMetricsが構築したGoogleのクラウド・プラットフォームベースの環境で稼働する。「Cloud Simulator」はUVMをフルサポートするSystemVerilogシミュレータで1分あたり4セントからの料金で利用可能。検証ピーク時のシミュレーション需要に即座に対応できる。「Verification Manager」はシミュレーションのマネジメント環境で検証結果の確認、デバッグなどが可能。多拠点によるチーム作業に対応している。

2018.06.18

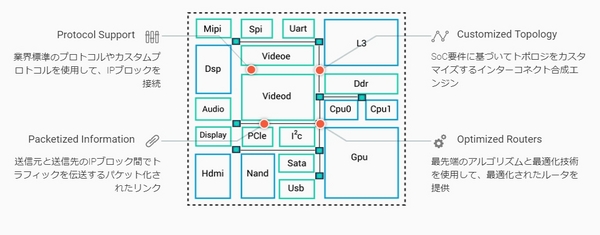

インターコネクトIPを手掛けるNetSpeed Systemsの案内によると、同社は6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceにて新製品を披露する計画のようだ。

その詳細は明らかにされていないが、案内に添えられていた「Join the AI Revolution with NetSpeed!」というキャッチフレーズから連想すると、「AI」をキーワードとした何かかもしれない。NetSpeedはIPと合わせてSoCの開発環境を提供しているが、SoCのアーキテクチャ探索において独自のマシンラーニング技術を用いており、それにより優れたSoCアーキテクチャを実現する。NetSpeedはキャッシュコヒーレンシの対応に自身を持っており、AI技術を取り入れた同社のソリューションは大手自動車メーカーや車載チップベンダ、新興のAIチップベンダに相次いで採用されている。

2018.06.18

2018年6月16日、Fudzillaの記事:

2019年1月のCESで発表されると見られているMicrosoftの新しいARゴーグル「HoloLens 2」は、QualcommのAR/VR向けのSoCプラットフォーム「Snapdragon XR1」を搭載していると言われている。初代HoloLensではIntelの「Atom x5-Z8100P」が搭載されていた。

2018.06.16

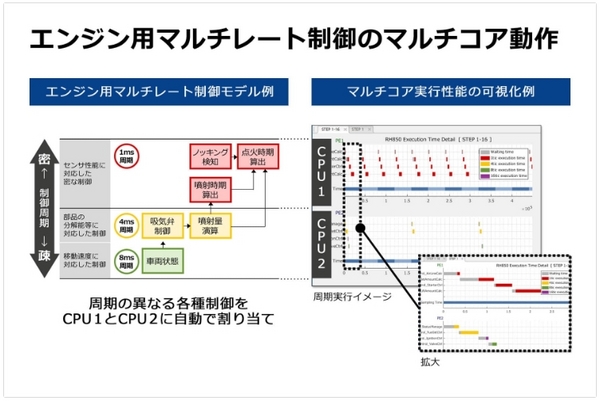

2018年6月14日、ルネサス エレクトロニクスは、車載制御用マイコンのモデルベース開発環境「Embedded Target for RH850 Multicore」のアップデートを発表した。

発表によると今回のアップデートにより「Embedded Target for RH850 Multicore」を用いて複数の制御周期(マルチレート)を持つシステムの開発が可能になった。エンジン制御やボディ制御などの車載システムではマルチレート制御が一般的。これまではマルチレート制御を含む複雑なシステムは実機に実装して検証する必要があったが、今回のマルチレート制御対応によりマルチレート制御モデルからマルチコア用のソフトウェアコードを直接生成可能になり、その実行性能をシミュレーションで検証できるようになった。ルネサスは、実行性能を開発の初期段階で見積ることができるだけでなく、検証結果に基づいたモデルへのフィードバックも容易になるとしている。

モデルベース開発環境「Embedded Target for RH850 Multicore」の最新版は、2018年秋から提供開始の予定。

2018.06.16

2018年6月15日、日本経済新聞の記事:

今月引退したTSMC元会長モリス・チャン氏が3nm製品は2年以内に開発できる、25年までに2nm製品も世に問うことができるだろうとコメントしたという。当然ながら2nm製品の量産時期は未定。

2018.06.16

2018年6月15日、AIチップを手掛けるシリコンバレーのベンチャーWave Computingは、MIPS Technologiesの買収を発表した。

今回の買収に関する取引条件などは明らかにされていないが、Wave Computingは世界350以上の特許と200のライセンシーを獲得。MIPSは今後Wave ComputingのIPビジネス・ユニットとして機能しMIPS IPソリューションのライセンスを継続する。

Wave Computingは2010年に設立されたAIチップベンチャーでサンタクララを拠点としている。同社は独自のデータフロー技術を用いたディープラーニング・システム「WaveFlow」に基づいた「DPU(Dataflow Computing Unit)」と呼ぶAIチップを開発しており、直近の資金調達第4ラウンド時点でSamsungなどから累計1億1700万ドルの資金調達に成功している。

Wave Computingの「DPU」は一般的なディープラーニング・アクセラレータのようなホストCPU+コプロセッサというアーキテクチャではなくプロセッシング・エレメントを1チップあたり16,000個搭載する単一の巨大なプロセッサアレイの構造をとる。Wave Computingは「DPU」を用いることでデータセンターでの学習からエッジの推論に対応する共通のAIプラットフォームを実現できると主張。今回のMIPSの買収により同社の戦略は加速するとしている。

2018.06.15

2018年6月13日、Synopsysのユーザーミーティング「SNUG Japan 2018」で行われたSynopsysによるキーノート「総合的な開発効率、品質、コスト削減を向上させるマシン・ラーニング・ベース検証」によると、Synopsysでは社内プロジェクトで「Forsight」と呼ぶバグや不具合の自動トリアージ・システムに取り組んでいるという話。

「Forsight」は過去のバグ、不具合に関するドキュメントやテスト資産、テスト結果のログなどを元に学習し、バグや不具合の発生時に自動的にトリアージを行い、最優先で叩くべきバグの特定や不具合のパターン解析、最適なテストの選択などに対してアドバイスを提供してくれる。

Synopsysは「Forsight」で実現しているマシンラーニング技術を様々なツールに連携させる事を考えており、フォーマル検証ツール「VC Formal」との連携などを実際に試して成果を出している。例えば「VC Formal」において同じ時間でより多くのプロパティ処理を実行するなどスループット向上が果たせたほか、スタティック検証におけるバイオレーション・レポートの精度向上によりバグ解析の大幅な工数削減などを実現している。

講演したSynopsysのArun Venkatachar氏(Verification Group Group Director, R&D)によると、こういった成果を受けてSynopsysは実際にマシンラーニング技術を用いたフォーマル検証ツールの製品化を進めているという。

2018.06.15

2018年6月13日、Synopsysはユーザーミーティング「SNUG Japan 2018」を品川のホテルで開催した。

ここではイベントの冒頭に行われたSynopsysによるキーノートについてレポートする。

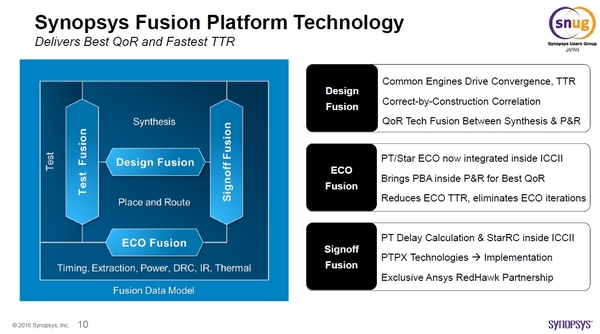

シノプシス Fusionプラットフォームが実現する最高の結果品質と開発期間短縮

Synopsys, Inc. Design Group Sr. Director of Marketing Sanjay Bali

同キーノートは発表間もない「Fusion Platform」の話題を中心としたもので、先端プロセス・デザインにおける同社の圧倒的な実績を示しつつ、「Fusion Platform」によってその強みを更に拡張するという同社のメッセージが色濃く出ていた。

先端プロセス・デザインにおけるSynopsysの実績

今年3月に発表した「Fusion Technology」は大きく4つある。

・Design Fusion:共通の設計エンジンによる論理合成と配置配線の融合

・ECO Fusion:配置配線工程におけるサインオフ技術の融合

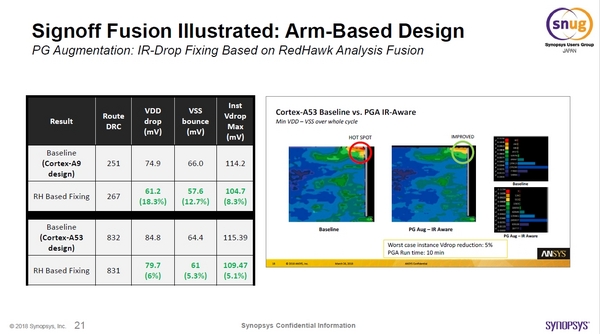

・Signoff Fusion:サインオフ工程とデザイン最適化工程の融合

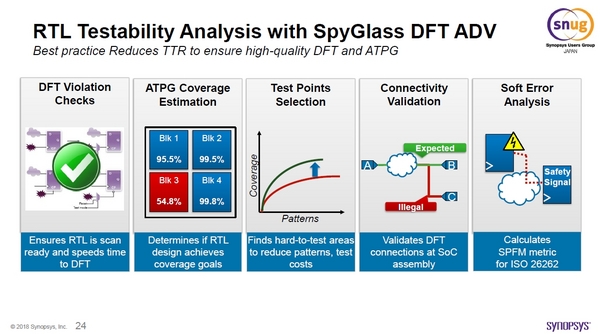

・Test Fusion:テスト容易化のためのRTL解析と論理合成の融合

「Fusion Technology」は文字通りツールや技術を融合させる事で作業の境界を無くし、設計のやり直しやイタレーションを防ぐことを目的にしている。

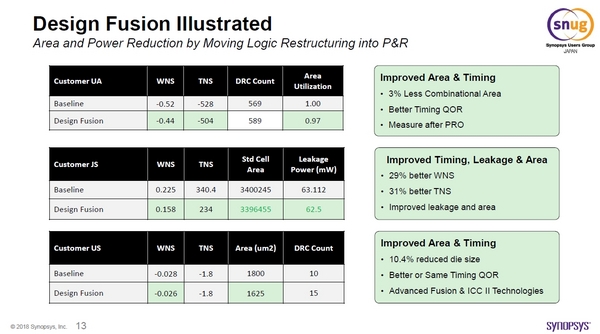

論理合成と配置配線のDesign Fusionによる恩恵。デザインによりエリア、パワーを削減。タイミングが改善された事例もある。

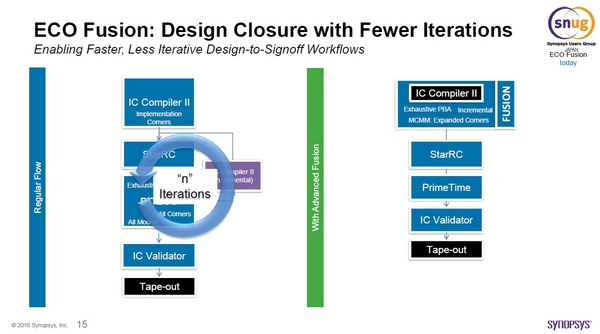

ECO Fusionは「IC Compiler」と「PrimeTime」間のイタレーションを無くす。

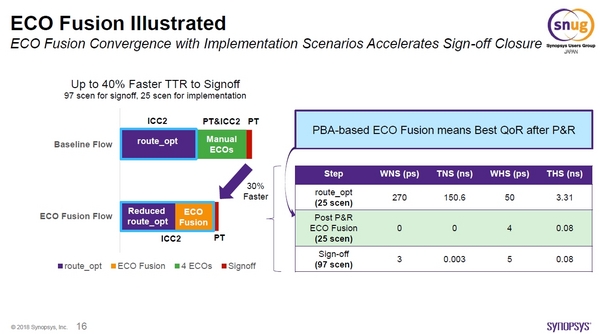

ECO FusionによってTATを30%削減した事例もある。

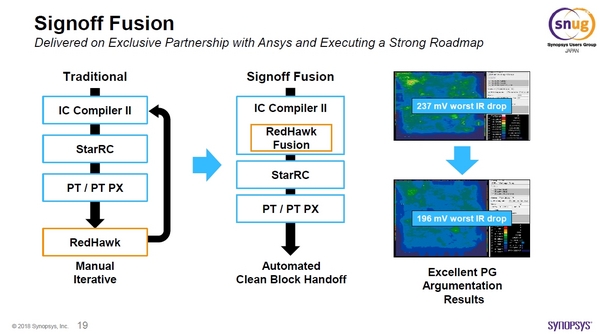

Signoff Fusionは業界デファクトとなっているAnsysのダイナミック・パワー解析ツール「RedHawk」をフローに取り込む。「RedHawk」をFusionできるというメリットは非常に大きい。

「RedHawk」を用いたSignoff Fusionの恩恵。

Test Fusionは「SpyGlass DFT ADV」を用いてDFT違反のチェックやATPGカバレッジに見積もりなどを行う。

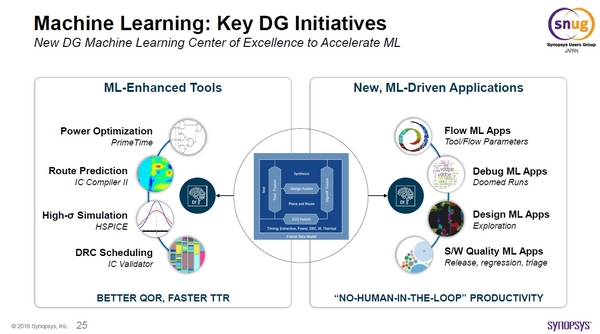

講演の最後にはMachine Learningを用いたツールの機能向上に関するSynopsysの取り組みが紹介された。既にML技術を実装している「PrimeTime」に続いて「IC Compiler II」、「HSPICE」、「IC Validator」においてもML技術の適用に取り組んでいるとの事。またツールのエンハンスとは別にパラメータ設定アプリ、デバッグアプリ、フロアプラン探索アプリなど設計フローの中で縦断的に利用できるML技術ベースのアプリ開発も進められているという。

※画像は全てSynopsysの公開データ

2018.06.15

2018年6月12日、デザインサービス大手の台湾Faradayは6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceの展示内容を発表した。

Faradayの展示の目玉はAI機能の実装にも対応するFPGA-to-ASIC変換サービスとIoT向け超低電力SoC開発プラットフォーム「Uranus+™」の2つ。

FPGA-to-ASIC変換サービスでは、特定のAI要件を満たすためのローパワー化、パフォーマンス向上、システムコスト削減などに対応。包括的なIPソリューションスイートと最先端のFinFETプロセスノードで帯域幅とレイテンシの低いインターフェイスを必要とするAIチップの実装に対応するという。

「Uranus+™」はUMC 55ULPテクノロジで実装されたIoTアプリケーション向けの32ビットMCUベースの超低消費電力SoCで、DVFSパワーモードを備えておりパフォーマンスと消費電力のトレードオフが可能。ターボモードではMCUコアが同じ動作電圧で2倍の性能を達成できる。

2018.06.15

2018年6月13日、Synopsysは同社のツール群がSamsung 7nm LPPプロセス向けに認証されたことを発表した。

今回Samsungに認証されたのは、Synopsysの下記ツール群およびそれらツールで構成されるリファレンスフローで、ツール群にはSynopsysのFusionテクノロジーで「PrimeTime」とサインオフ検証で連携しているAnsysの「RedHawk」も含まれている。EUVを用いた最先端のSamsung 7nm LPPプロセスにおけるツール認証は今回のSynopsysが業界初。通常ファウンドリの先端プロセスでのツール認証はEDA各社が同時に発表するが、今回他社からの同時発表は無い。

・IC Compiler II

・Design Compiler Graphical

・IC Validator

・PrimeTime

・StarRC™

・RedHawk™ Analysis Fusion

・DFTMAX™ and TetraMAX® II

・Formality®

なお今回のツール認証はARMv8アーキテクチャベースの64ビットARM Cortex-A53プロセッサのインプリによって行われた。Synopsysは同社のキャラクタライズ・ツール「SiliconSmart®」がプロセスおよびリファレンスフローに使用されるライブラリ開発のキーであったとコメントしている。

2018.06.14

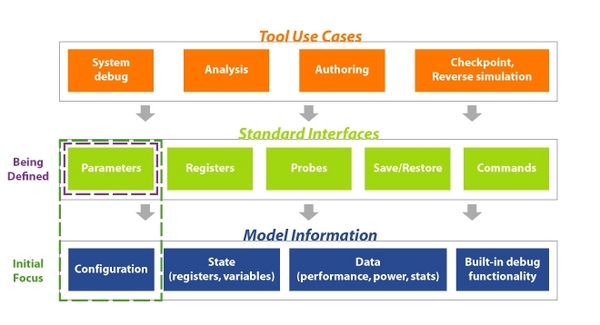

2018年6月13日、ハードウェア設計言語・技術の標準化団体米Accellera Systems Inisiativeは、SystemC CCI 1.0仕様の承認を発表した。

SystemC Configuration, Control and Inspection (CCI) 1.0は、SystemCモデルとEDAツール間の相互運用性を高める事を目的に策定されたAPI規格で、最初のバージョンとなるCCI 1.0ではモデルとツール間の情報交換のためのモデルのコンフィグレーション仕様が定義されている。

2018.06.14

2018年6月13日、NXPは自社デバイスにAI機能を実装するためのマシンラーニング環境を発表した。

NXPが発表したマシンラーニング環境は、エッジデバイスにAI機能を組み込む顧客向けに提供されるもので、同環境には学習済みのTensorFlowまたはCaffeモデルをインポートし、最適化された推論エンジンに変換する無償ソフトが備えられており、NXPの各種デバイスに容易にAI機能を実装できる。

NXPは幅広い顧客のニーズに応えるためにMachine Learningパートナーエコシステムを構築しており、下記2社がパートナーとして参画している。

・Au-Zone Technologies

業界初のエンドツーエンドの組み込みMLツールキットおよび推論エンジンDeepviewを提供

・Pilot.AI

MCUからGPUまで様々なプラットフォーム向けに様々な認識タスクのフレームワークを提供

2018.06.14

2018年6月13日、Armは英Stream Technologies社を買収した事を発表した。

Stream Technologiesは2000年に設立されたIoTデバイスのコネクティビティ管理ソリューションを提供するプロバイダー。ロケーションやネットワークに関係なくIoTコネクテッド・デバイスのコネクティビティ管理を可能にするプラットフォームを提供している。

ArmはStream Technologiesの技術と同社の「Mbed IoT Device Management Platform」を組み合わせることにより、シームレスなオンボーディング、コネクティビティ、およびデバイス管理のソリューションを実現するとしている。

2018.06.14

2018年6月13日、Nextplatformの記事:

Wave ComputingがMIPS Technologiesの買収を発表する予定。Wave Computingは次世代のAIチップ開発でMIPSコアを採用しており、既に1億ドル以上の資金調達に成功している。

2018.06.14

2018年6月13日、Fudzillaの記事:

Qualcommの社長はサーバー向けチップの開発部門の人員削減を行っているが、Alibaba、Tencent、Baiduなど中国の大手IT企業にターゲットを絞ってチップの開発を継続するつもりであると述べている。

2018.06.14

2018年6月13日、IC Insightsの記事:

2018年のIoTシステム市場は933億ドルに到達する見通しで、最も成長率の高い分野は「IoT-connected vehicle」で売上は前年比21.6%増の45億ドル。2016年から2021年までの平均成長率予測で見ると「IoT-connected vehicle」の22.9%が最も高く、次いで「industrial Internet」分野が17.8%と高い成長率が見込まれている。

2018.06.13

2018年6月12日、SoCのテストケース自動生成ツールを手掛けるBreker Verification Systemsは、同社最新のツールスイート「Trek5」を発表した。

「Trek5」は、SoCのテストケース自動生成ツール「TrekSoC™」および「TrekSoC-Si」、UVMのテストケース自動生成ツール「TrekUVM」、特定の検証にフォーカスした自動化ソリューション「TrekApps」で構成されており、今回Accelleraの「Portable Stimulus Specification(PSS)1.0」を完全にサポートした。これによりTrekを用いたテストシナリオのモデリングにおいて、Accellera PSS 1.0のDSL(ドメイン固有言語)とPSS C++が使用可能となった。

また 「Trek5」ではテスト合成機能がエンジンを含めて強化されたほか、自動的にPSSコードを生成するシナリオモデルをグラフとして描画できるビジュアルエディタが新たに追加された。 「Trek5」に関する詳細は、6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceで展示される予定。

Breker Verification Systemsは、AccelleraのPortable Stimulus Specificationのワーキングの中心メンバーとして仕様策定に参加している。

2018.06.13

2018年6月12日、インターコネクトIPを手掛けるNetSpeed Systemsは、中国Cambriconによる採用事例を発表した。

発表によるとCambriconは、次世代AIチップの性能要件と周波数ターゲットを達成するための新機能実現に向けてNetSpeedのインターコネクトをライセンス。IPのスケーラビリティと、最小限の労力でAIアプリケーションが必要とする高度なトポロジを構成してくれる能力がNetSpeedのインターコネクトを採用した理由だという。

CambriconはAIチップベンダとして存在感を高めている企業で投資家から1億ドルを集めている。NetSpeedはCambricon以外にもAIチップベンダ米Esperanto Technologiesによる採用事例を発表している。※関連ニュース

2018.06.13

2018年6月12日、Fudzillaの記事:

Intelのチーフ・アーキテクトRaja Koduri氏が2020年にIntelのディスクリートGPUが登場することをTwitterで明らかにした。

2018.06.12

2018年6月12日、CNETの記事:

画像技術をベースとしたソリューションを手掛けるRevatron株式会社がカメラが見ているものをチャットやテキストでユーザーに知らせる世界初のスマートカメラを発表した。同カメラはオブジェクトの三次元形状を学習し、学習した三次元情報に基づいてオブジェクトを・分類し、見ているものを人間に伝える機能を持つAIエンジンを搭載。オブジェクトの説明、位置、速度、そしてオブジェクトに何らかの懸念点があるかどうかを伝えることが可能。AIエンジンはソシオネクストのA11プロセッサとFPGAアクセラレータで構成されている。

2018.06.12

米SIA(Semiconductor Industry Association)が米国および世界半導体市場の様々なデータをまとめた「2018 SIA Factbook」を公開した。メールアドレスの登録で無償のPDFデータを入手できる。

2018 SIA Factbook掲載データの例

・2017年世界半導体市場における米国企業のシェアは46%、日本は10%

・2017年世界半導体市場の30%はメモリの売上で前年比61.5%増

・2017年世界半導体市場の60.4%はアジア・パシフィック地域の売上、日本は8.9%

・2017年の米国企業による半導体への研究開発投資額は608億ドル

2018.06.12

2018年6月11日、Digitimesの記事:

Huaweiの子会社HiSiliconはミッドレンジ・スマートフォン向けの新型SoC「Kirin 710」を7月に発表する予定。同SoCはQualcommの「Snapdragon 710」に対抗するものと見られるがそのスペックは異なり、Kirin 710はCortex-A73ベースでTSMC 12nmプロセス、Snapdragon 710はCortex-A75/55ベースでSamsung 10nmプロセス。いずれのSoCもAI処理の専用エンジンを搭載している。

2018.06.12

2018年9月26日からカリフォルニア州ラグナヒルズで、IEEEによる初の産業向けAIの国際学会「ai4i 2018」が開催される。

「ai4i 2018」は、金融、サービス、貿易、医療、教育、芸術、人文、メディア、製造、運輸、建設、農業など様々な産業におけるAI技術に焦点をあてる国際学会で現在論文を募集中。以下のような技術分野をスコープとしている。

・Semantic and cognitive aspects in different industries

・Innovative operations using artificial intelligence

・Immersive environments

・Multimodal interactions

・Human/agent interactions

・Domain specific problem solving

・Machine and deep learning

・Modelling of behaviour and activity generation

・Big data and analytics

・Dialogue modeling and generation

・System components of intelligent platforms for industries

・Robotic intelligence

2018.06.12

2018年6月11日、IPベンダMIPS Technologiesは、同社のセーフティクリティカル・システム向けコア「MIPS I6500-F」が機能安全規格ISO 26262 ASIL B(D)ならびにIEC 61508 SIL 2の認証を獲得した事を発表した。

発表によるとMIPSコア「I6500-F」は、ISO 26262で定義されているSEooC(Safety Element out of Context)に基づいて開発されているため、ASIL D準拠のSoCの一部となり得るとの事。ISO 26262 ASIL B(D)の認証獲得は64ビット・マルチクラスタCPUとして業界初となるという。「I6500-F」はMobileyeの自動運転用ビジョン処理システム「EyeQ®5」に採用されている。

2018.06.11

2018年6月9日、Fortuneの記事:

6月8日に米オークリッジ国立研究所が新型のスーパーコンピュータ「Summit」を発表した。「Summit」は毎秒20万兆回/200ペタフロップの計算能力があり、同研究所の旧型スーパーコンピュータ「Titan」の約8倍、世界最速の中国のスーパーコンピュータ「TaihuLight」の性能93ペタフロップを大きく上回る。「Summit」はIBMのPower9 CPUとNvidia Tesla V100 GPUを使用してIBMによって構築された。

2018.06.11

2018年6月8日、半導体製造装置メーカーの大手Applied Materialsは、銅やタングステンに代わる金属としてコバルトを利用するソリューションを発表した。

発表によるとApplied Materialsは、7nmノード以降における深刻な性能ボトルネックの解決に向けトランジスタのコンタクトと配線にコバルトを導入するソリューションを開発。「インテグレーテッド コバルト製品群」として半導体ファウンドリ、半導体ベンダへの出荷を開始した。

コバルトはインテグレートするのが難しい金属だが、微細寸法において低抵抗でばらつきが少ない、超微細寸法でギャップフィル性能を改善、信頼性が高い等のメリットがあり、7nmノード以降のチップ性能を最大15%向上できるという。

2018.06.11

2018年6月8日、Mentor Graphicsは、クラウド環境Amazon AWSのオプションとして利用可能なハードウェア・エミュレーション・プラットフォーム「Veloce Strato」を発表した。

「Veloce Strato」はMentorとAmazonの協業によって実現したオンデマンドのクラウド型エミュレーション・プラットフォームでAmazonのクラウド環境AWSのオプションとして利用することが可能。その詳細についてはサンフランシスコで開催するDesign Automation Conferenceで6月27日に発表される予定。

2018.06.09

2018年6月8日、Imagination Technologiesは、新型のニューラルネットワーク・アクセラレータ・コア2品種を発表した。

Imagination Technologiesの新しいアクセラレータ「PowerVR Series2NX AX2185」は、パフォーマンス重視のコアで、ハイエンドのスマートフォン、監視カメラ、自動車などをターゲットとしており業界最高の4.1TOPSの演算性能を発揮する。もう一つの「PowerVR Series2NX AX2145」はコスト重視のコアでミッドレンジのスマートフォン、DTV/セットトップボックス、スマートカメラ、コンスーマ向けセキュリティ市場などをターゲットにしており、超低帯域幅システム向けに最適化されている。両コアともにパフォーマンス効率が高く少面積。ビット精度は16ビットから4ビットまでサポートしており、帯域幅/電力要件を削減しながら、推論精度を高く保つことができる。

Imagination Technologiesは、AIアプリケーションの開発用に「Network Developer Kit(NDK)」を用意。PowerVR Series2NX AX2185およびAX2145はAndroid Neural Networks API(NNAPI)をフルサポートしている。

2018.06.09

2018年6月8日、TECHABLEの記事:

Kickstarterで電子回路の基礎を学べるノートブック「HACK YOUR NOTEBOOK」が資金を集めている。子どもや学校の教師に、入門レベルの設計を習得させるために生まれたプロジェクト。4冊のノート型小冊子と、LEDやセンサーを搭載した特殊なステッカーなどで構成されている。プレオーダー価格は、ブック4冊のセットで85ドルから。受け付け6月30日まで。出荷2018年9月予定。

2018.06.08

2018年6月7日、Aldecは6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceの展示内容を発表した。

今年のAldecのブースでは下記5つのトラックテーマで終日プレゼンテーションを実施する予定。

・Single Platform for ASIC/SoC Emulation and Prototyping

・Mixed-Signal and Mixed-Language Simulation Solutions

・Static Design Verification Methodologies

・Machine Learning, High Performance Computing & Embedded Vision

・Traceability and Reusability for Safety Critical Projects

Mixed-Signal Simulationの話としては、Silvacoとのツール連携も紹介。Aldecが力を入れているVHDL 2018の話も同じトラックで聞けるようだ。Static VerificationのトラックではFPGA向け検証というトピックスも。Machine Learning, High Performance Computing & Embedded Visionのトラックでは、Zynq搭載ボード「TySOM」を使った事例やHPCアプリケーション向けの新ボードが紹介される予定。

2018.06.08

2018年6月8日、ロイターの記事:

米国際貿易委員会(ITC)が米半導体大手Broadcomの申し立てによりトヨタ自動車、パナソニック、デンソーの米関連会社デンソーテン、ルネサスエレクトロニクス、日本無線などを調査する。情報娯楽システムや同システムを搭載した自動車に関連する特許侵害の疑いがあるという。

2018.06.08

2018年6月7日、インターコネクトIPを手掛けるAlteris IPは新製品となるスタンドアロンのLLC(Last Level Cache)「CodaCache」を発表した。

発表によると「CodaCache」は様々なサイズ・構成でチューニング可能なスタンドアロンのLLCで相互接続を必要とせずSoC上の任意のAXIバスに追加する事が可能。専用パーティション、共有パーティション、分散パーティショニング、オンチップ・スクラッチパッドストレージとしての使用など、様々なユースケースをサポートしており、システム全体のパフォーマンスの向上、パワー削減、物理レイアウトの混雑度の緩和を実現する。

Arteris IPは「CodaCache」をハイパフォーマンスSoC向けのLLCとうたっており、

ADAS、機械学習アプリケーション、サーバ/データセンター処理、ネットワークといったアプリケーションをターゲットとしている。

2018.06.08

2018年6月7日、Digitimesの記事:

Unigroup Spreadtrum&RDAはIntelと5Gモデム搭載チップを共同開発する一方、自社内でもモデムの開発を進めている。また5G分野のチップ設計技術の向上に向けてHisiliconと提携している。5Gモデム搭載チップについては先頃MediaTekも2019年の市場投入を発表している。Unigroup Spreadtrum&RDAは合併により今年誕生した企業で従業員約4500人、年間売上は約15.6億ドル。

2018.06.08

2018年6月7日、日本経済新聞の記事:

米商務省は中国ZTEに対する米企業との取引禁止措置を解除する事を発表した。米商務省が科す罰金額として過去最大となる預託金を含む最大14億ドルの罰金、経営陣の刷新、米国が選んだ法令順守担当者の受け入れが条件。ZTE問題の解消により中国政府が待ったをかけていたQualcommによるNXP買収が進むと見られている。

2018.06.07

2018年6月7日、日本経済新聞の記事:

Qualcomm前会長のポール・ジェイコブス氏がQualcommの元幹部らと5G技術の新会社「XCOM」を設立した。XCOMの本社はサンディエゴで5G関連の研究開発や投資を行う。

2018.06.07

2018年6月6日、Deepchipの記事:

Amazon AWS上で動くCadenceのシミュレータやMentorのエミュレータがDACで発表されるかもしれない。状況証拠からすると信憑性が高い話。

2018.06.07

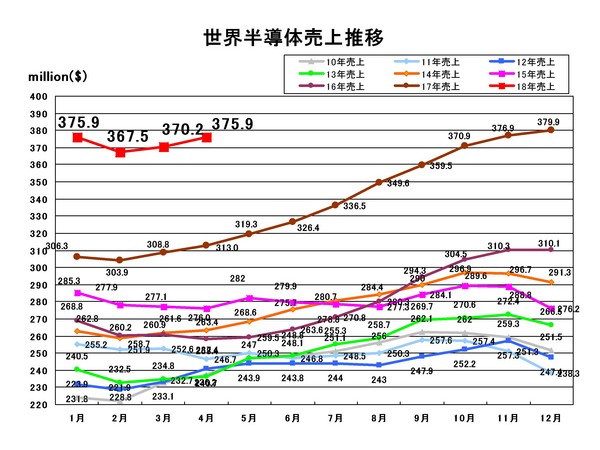

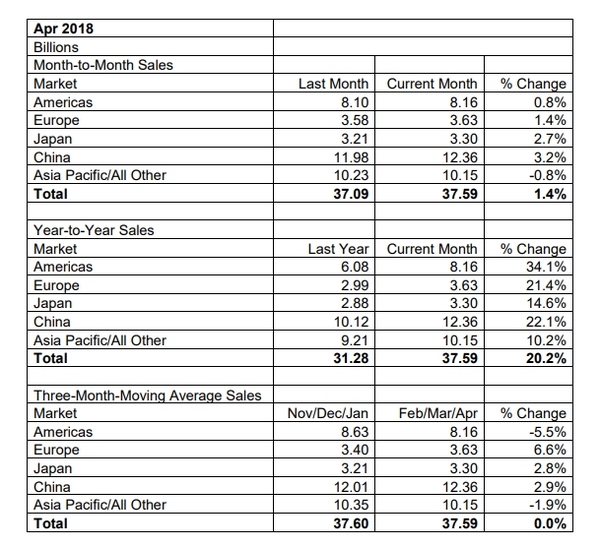

2018年6月6日、米SIA(Semiconductor Industry Association)は、2018年4月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年4月の世界半導体売上は前年同月比20%増、前月比1.5%増の375.9億ドルを記録した。同実績は4月の単月売上としては過去最高で、単月売上が前年実績を上回るのは21ヶ月連続となる。

空前の活況を記録した昨年に続き今年も世界の半導体市場は好調を維持。つい先日発表されたWSTSの2018年春季半導体市場予測では、2018年世界半導体市場は12.4%増の4634億ドルに到達すると予測されている。※関連ニュース

2018年4月の世界半導体市場を地域別の売上で見ると、全ての地域で前年比2ケタ増の売上を記録。これは9ヶ月連続となる実績。前年比で最も成長したのは3月に続き北米市場で前年比34.1%増。北米市場は2017年9月から5ヶ月連続で前年比40%増以上の成長を継続していたが、この数ヶ月で成長率が徐々に緩やかになってきている。

日本市場の売上は前年比14.6%増の33億ドルで3月実績を上回った。売上を円ベースで換算すると前年比約11.9%増の約3548億円で前月比約4.9%増となる。

2018.06.07

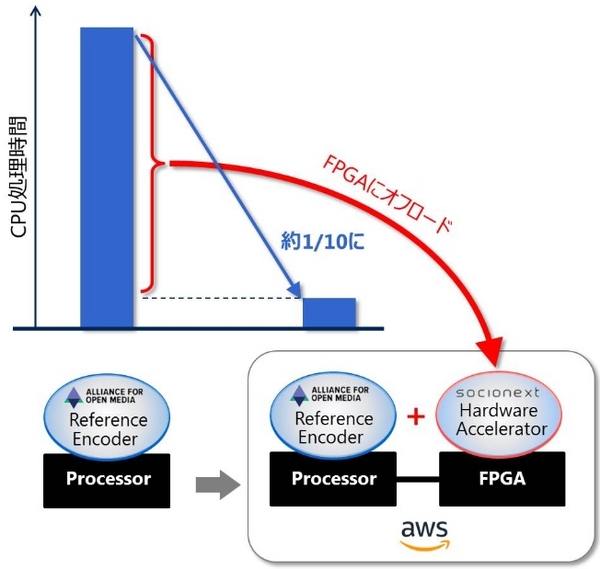

2018年6月6日、Socionextは、クラウド環境を用いた取り組みについての事例を発表した。

発表によるとSocionextは、オープンソースの映像データ圧縮規格「AV1」のエンコード処理?アクセラレーターをAmazonのクラウド環境「Amazon EC2 F1 インスタンス」上のFPGA(16nm Xilinx UltraScale Plus)に実装。AV1規格の映像エンコード処理をCPU単体動作と比較して約10倍高速化する事に成功した。実装に要した時間はわずか1.5ヶ月だった。

Socionextは今回の取り組みの成果を受けて、専用ハードをチップ化して顧客に販売するというビジネスだけでなく、顧客がクラウドから半導体製品の機能を利?できる仕組みや、クラウド上のアプリケーションの処理能?を向上させる各種アクセラレーターの構築・運?など、サービス提供を中心とした新しいビジネスを提案していくという。

2018.06.07

2018年6月6日、Sonicsはデザインサービスを手がける日本企業シンコムとの提携を発表した。

発表によるとシンコムは同社のデザインサービスを通じてSonicsのNoC(Network-on-Chip)およびEPU(Energy Processing Unit)を顧客に提供。Sonicsと協力して顧客のサポートも行う。シンコムは国内外でデザインサービスを提供する一方で様々なEDAツールの代理店として販売・サポートも行っている。

2018.06.07

2018年6月6日、Techcrunchの記事:

イスラエルのスタートアップで組み込みデバイス用のディープラーニングチップを開発しているHalio Technologiesが資金調達の第一ラウンドで1250万ドルの資金を調達した。

HalioのAIチップは自動車がメインターゲットでAIチップのサンプル出荷は2019年前半の予定。独自のアーキテクチャによりディープラーニングの高速化を実現する。

2018.06.06

2018年6月5日、SynopsysはAI技術を組み込んだデジタル・デザイン向けソリューションについて発表した。

発表によるとSynopsysは業界標準のサインオフツールであるスタティック・タイミング解析ツール「PrimeTime」にAI技術を搭載。デザイン・インプリメンテーション工程におけるパワー・リカバリーの大幅な効率化を実現した。その技術に関する詳細は明らかにされていないが、パワー・リカバリーに関する学習結果をパワー・リカバリーのECOに応用するもののようだ。

この取り組みはパートナー企業との協業の一環として行われたもので、その背景には設計自動化におけるAI投資の拡大というSynopsysの戦略がある。

発表に寄せられたルネサスエレクトロニクス岡部秀之氏(ブロードベースドソリューション事業本部 共通技術開発第二統括部 デジタル設計技術部 部長)のコメントによると、AIを組み込んだ「PrimeTime」を大規模SoCで試したところ、タイミングとパワーの最適化品質を落とすことなく、パワー・リカバリーのECOを4倍以上の速さで実現。数日を要していたECOを数時間で完了できたとの事。Synopsys自身も顧客企業の最先端プロセス・デザインでパワー・リカバリーの5倍高速化を達成したとしている。

なお、ルネサスによるAIを組み込んだ「PrimeTime」の活用事例については、今月6月13日に開催されるSynopsysのセミナーイベント「SNUG Japan 2018」の下記セッションにてその詳細が紹介されるようだ。