NEWS

2018.07.12

2018年7月11日、ZDNet Japanの記事:

ファブレス半導体ベンダ業界2位の米Broadcomが企業向けソフトウェアを手掛けるCA Technologiesを189億ドル(約2兆1200億円)で買収すると発表した。CAの買収によってエンタープライズ分野で規模を拡大し、インフラ技術に重点を置く企業となることを目指すという。

Broadcomの売上は2017年実績で約160億ドル。今回買収したCA Technologiesの売上規模は直近の2018会計年度で約42億ドルなので、買収が完了するとBroadcomの売上規模は200億ドル超となり、買収を試みていたファブレス首位Qualcommを上回る規模となる。買収は第4四半期に完了する見通し。

2018.07.12

2018年7月10日、AmazonはAmazon EC2 F1インスタンスの性能改善と新機能の追加を発表した。

発表によるとAmazonがEC2 F1インスタンスのユーザー向けに提供するソフトウェア開発者向けの開発環境「FPGA Developer AMI」がバージョンアップされ、カーネル数が既存の最大16カーネルから最大60カーネルに拡張された。これによりC/C++で記述されたソフトウェアの更なるアクセラレーションが可能となる。また、ユーザーのフィードバックによりDMA性能が5倍向上し、FPGAアクセラレーション・エンジンとCPU間でのより高速なデータのやり取りが可能となった。

Amazonはその他のトピックスとして、FPGAアプリケーションの構築を容易化する「Amazon FPGA v1.4シェル」のリリースや特定のAFI(Amazon FPGA Images)のロード時間を効果的に短縮する新機能などをアナウンスしている。

2018.07.12

2018年7月10日、RISC-V Foundationは7/18からインド チェンナイで開催予定のRISC-V Workshopのアジェンダを発表した。

インド工科大学マドラス校の主催による今回のRISC-V Workshopでは2日間で計23のセッションが予定されており、キーノートはイベントのメインスポンサーWestern Digitalが行う。RISC-V Workshopは米国、中国、スペインでも開催されており、日本でも今年10月にRISC-Vのイベント「RISC-V Day Tokyo」が開催される予定。

2018.07.12

2018年7月9日、GLOBALFOUNDRIESは同社の22nm FD-SOI (22FDX®)プロセステクノロジの実績について発表した。

発表によるとGLOBALFOUNDRIESの22FDX®は50社以上の顧客を獲得し、その売上は20億ドルを超えた。業界最先端のローパワーチップ向けプラットフォームとして、車載、5G、IoTなど成長著しいアプリケーションで幅広く活用されているという。

GLOBALFOUNDRIESの22FDX®は、FD-SOI(完全空乏型シリコン・オン・インシュレータ)と呼ばれる技術を用いた線幅22nmのプロセスで、GLOBALFOUNDRIESは一般的なバルクCMOSプロセスよりも大幅に消費電力とダイサイズを削減できるとしている。また22FDXは一般的な28nmプロセスよりもマスク数を10%削減できるとされており、液浸リソグラフィ層数はFinFETの半分に抑える事ができるようだ。

2018.07.11

2018年7月10日、キヤノンは1.2億画素の超高解像度CMOSセンサー「120MXSM/MXSC」の発売を発表した。

新製品「120MXSM」はAPS-Hサイズのモノクロ対応CMOSセンサーで、フルHDの約60倍にあたる解像度を実現。多数の画素から信号を高速で読み出す並列信号処理技術により、最高速度11.3Gbpsで1秒間に最高約9.4コマのスピードで出力できる高速読み出しが可能。大型有機ELパネルや8Kパネルなど、次世代の超高精細パネル検査での活用を見込む。

「120MXSC」はカラー対応のCMOSセンサーでパネル検査用途以外の映像制作やデジタルアーカイブ、特殊監視などの用途でも活用することが可能。 キヤノンは7月下旬より「120MXSM/MXSC」の量産を開始する予定。

2018.07.10

2018年7月9日、HEXUSの記事:

AMDのサーバーCPU「EPYC」とほぼ同じと言われている中国Hygon Dhyana社のx86サーバーCPU「Dhyana」が中国で流通しはじめている。Hygon Dhyana社はAMDと中国THATIC (Tianjin Haiguang Advanced Technology Investment Co., Ltd)の合弁会社で「Dhyana」は中国でのみ販売される。AMDがTHATIと交わしたHygon DhyanaによるCPU開発のライセンス契約(x86およびSoC IP)は総額293億ドルとされている。

2018.07.10

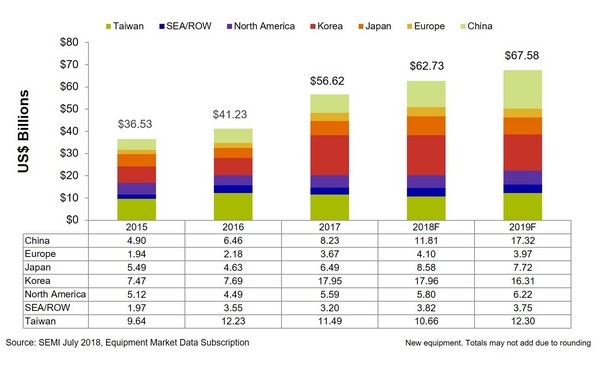

2018年7月9日、SEMIは今年の世界半導体市場の見通しを発表した。

発表によると、今年の世界半導体市場は過去最高を記録した昨年実績を10.8%上回る627億ドルに到達する見通し。来年は更に出荷額を伸ばし676億ドルに達すると予測している。地域別の出荷額では韓国が2年連続で首位をキープ。中国が台湾に代わり2位に浮上。中国は成長率の伸びで群を抜いており、2019年には地域別の出荷額で首位に躍り出ると見られている。

2018.07.09

2018年7月9日、Mentor Graphicsは、同社の物理検証ツール「Calibre」が機能安全規格ISO 26262のツール認証を取得した事を発表した。

発表によると、独立系の認定企業として有名な「SGS-TÜVSaar」によって、Mentor Graphicsの物理検証ツール「Calibre」のツール認定レポートが機能安全規格ISO 26262に準拠していることが認証された。今回の認証はASIL Dを含む全てのクリティカル・レベル、そして物理検証、DFM、回路検証を含む全ての「Calibre」製品群が対象となっている。ISO 26262認証済のMentorツールを利用する事で、ツールのユーザーは開発した製品の機能安全認証の取得が容易になる。

Mentorは積極的に自社ツールのISO 26262対応を進めており、「Mentor® Safe」と呼ぶ機能安全認定プログラムを通じて殆どの主力製品のISO 26262ツール認証を取得している。

2018.07.06

2018年7月5日、Cadenceは日立製作所によるフォーマル検証ツール「JasperGold®」の適用事例を発表した。

発表によると日立製作所は安全保護系コントローラ「νCOSS® S-zero®」の開発において「JasperGold®」を使用。具体的には「JasperGold®」のフォーマル検証技術を用いてIEC 61508の安全要件を満たすフェールセーフメカニズムのための複数のハードウェア検証作業を行った。日立製作所は、DUTを解析する「JasperGold®」のProofCoreテクノロジがコントローラの検証環境を改善するのに役立ったとコメント。同検証環境は安全保護系コントローラが安全性を維持しながら入力に対して正しく動作していることを確認するためのもので、機能安全の国際規格IEC 61508 SIL 4要件に準拠する。

なお、日立製作所は「JasperGold®」と合わせてCadenceのシミュレータとエミュレーションソリューションも併用し機能安全要件の100%検証を実現。その結果開発した「νCOSS® S-zero®」はIEC 61508 SIL3の認証取得に成功した。

今回の日立製作所の事例の詳細は、7月20日にみなとみらいのホテルで開催されるCadenceのイベント「CDNLive Japan 2018」にて発表される予定。

2018.07.05

2018年7月3日、SynopsysとMentor Graphicsを傘下に持つSiemens PLM Softwareは、両社のコラボレーションについて発表した。

発表によるとSynopsysとSiemensは両社のお互いの顧客の利益のために、設計から検証まで幅広いEDA製品において製品の相互運用性プロジェクトに取り組む。

詳細は明らかにされていないが、Mentor Graphicsの主力製品である物理検証ツール「Calibre」シリーズがSynopsysのインプリメント・ツールと繋がるといったツール連携が実現する可能性が高い。

合わせてSynopsysとSiemensは、SynopsysとMentor Graphicsの間の特許訴訟を和解した事を発表。和解には、SynopsysとSiemens間およびSynopsysとMentor Graphics間の7年間の特許クロスライセンスとSynopsysからSiemensへの和解金6500万ドルの支払いが含まれているという。

2018.07.05

2018年7月2日、NIMS(物質・材料研究機構)は、2種類の異なる有機トランジスタを組み合わせることで、3つの値をスイッチできる多値論理演算回路の開発に成功したと発表した。

発表によるとNIMSの研究グループは異なる電流特性を持つアンチ・アンバイポーラートランジスタと通常のトランジスタを組み合わせた素子を開発。これにより3つの値のスイッチングできる多値論理演算回路の開発が可能となり、同じトランジスタサイズで集積度とデータ処理能力を大幅に向上させることができるという。

これまで有機材料は高集積化が困難だったため、今回の研究成果は有機トランジスタを用いた回路の大幅な計算機能の向上に寄与することが期待されている。

2018.07.05

2018年7月4日、DigiTimesの記事:

Digitimes ResearchによるとCMOSおよびCCDイメージセンサーの世界市場は2020年に150億ドルを超える見通し。2017年は前年比15%増の122億ドルだった。業界トップのソニーは2016年、2017年と市場シェア45%を獲得しているが、自動車向けCMOSイメージセンサーの市場シェアはわずか9%(2017年)。既にトヨタのサプライチェーンに組み込まれたソニーは今年、ボッシュ、日産、ヒュンダイなど自動車分野の顧客基盤を拡大する予定。

2018.07.04

2018年7月3日、CadenceはSamsungファウンドリの7LPPプロセスにおけるツール認証の取得を発表した。

Samsungの7LPP(Low Power Plus) プロセスはEUVを用いるSamsung最先端のプロセス技術。今回Samsung7LPPプロセス技術で認証されたCadenceのRTL-to-GDSIIデザインフローは、OpenRISC OR1200デザインを使用するSamsung FoundryのDM (Design Methodology) をベースとしている。

Samsung 7LPPプロセスのツール認証はMentor, SynopsysなどEDA大手各社が発表している。

2018.07.04

2018年7月3日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けツールなど各種EDAソリューションを展開するSilvacoは、OKIエンジニアリングとの協業を発表した。

発表によると両社は「SPICEモデリングサービス」で協業。OKIエンジニアリングのデバイス特性データの高度な測定技術とSilvacoのSPICEモデリング技術を組み合わせる事で、正確なデバイス特性データを基にしたSPICEモデルの作成を実現する。Silvacoはこの協業による新サービスとして「パワーデバイス搭載回路向けSPICEモデリングサービス」を7月4日から開始する。

2018.07.04

2018年7月4日、Bloombergの記事:

UMCがMicronに対して起こした特許侵害訴訟により、MicronのDRAM、NAND、SSDなど一部製品の中国での販売が禁止されるとUMCが述べている。中国の裁判所が暫定的な差し止め命令を出したとされているが事実関係は不明。米中貿易紛争の影響を受けた一時的な措置かもしれない。2017年のMicronの売上の約半分は中国での売上。

2018.07.03

2018年7月2日、オンチップ・ネットワークのSonicsとRISC-VベースプロセッサのSiFiveは両社のパートナーシップを発表した。

発表によると両社のパートナーシップにより、SiFiveのRISC-VベースプロセッサとSonicsのNoCの相互運用が可能に。すでにSiFiveの「EシリーズCPU」とSonicsのNoC「SonicsGN」によってその相互運用性を実証済みだという。両社は業界で広く支持されているプロセッサIPとNoCの組み合わせにより、RISC-VベースのSoCを迅速に統合可能な「アジャイルRISC-Vデザイン・プラットフォーム」が実現できるとしている。

2018.07.03

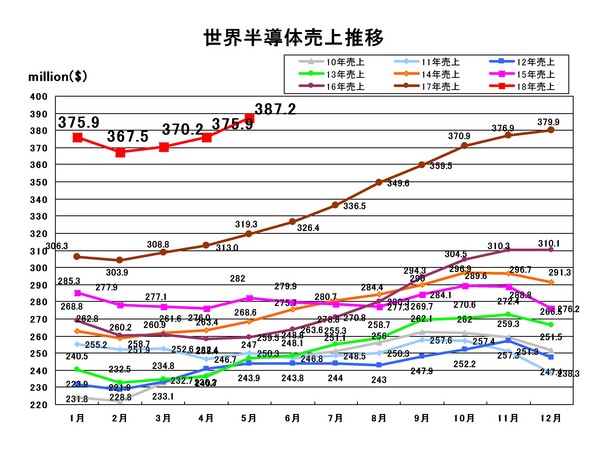

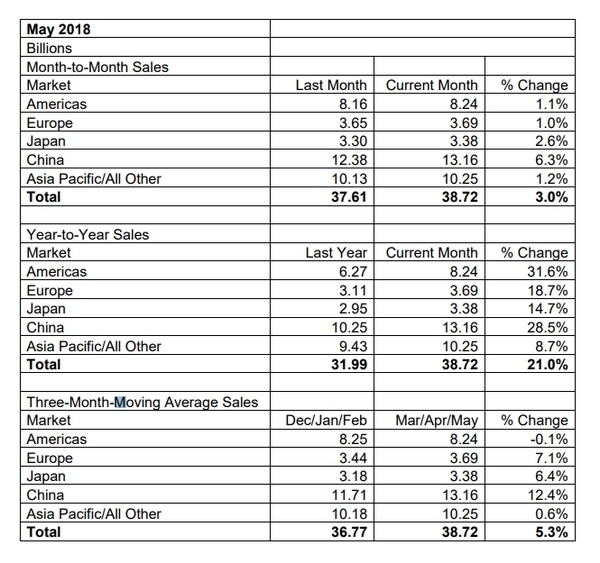

2018年7月2日、米SIA(Semiconductor Industry Association)は、2018年5月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年5月の世界半導体売上は前年同月比21%増、前月比3%増の387.2億ドルを記録した。同実績は単月売上としては史上最高額で、単月売上が前年実績を上回るのは22ヶ月連続となる。

2018年5月の世界半導体市場を地域別の売上で見ると、売上高トップは中国市場で前年比28.5%増の131.6億ドル。全売上の約34%を占めた。2番手の北米市場は前年比31.6%増の82.4億ドルで全売上の約21%だった。これまでの直近9ヶ月間は全ての地域で前年比2ケタ増の売上を記録していたが、この5月はアジアおよびその他地域が前年比8.7%増と成長率を落とした。

日本市場の売上は前年比14.7%増、前月比2.4%増の33.8億ドル。売上を円ベースで換算すると前年比約12%増の約3708億円で前月比約4.5%増となる。

2018.07.02

2018年7月2日、NTTデータと日本シノプシスはステム開発分野における静的解析ツール「Coverity」の利用領域拡大・機能拡張に向けた取り組み開始を発表した。

発表によるとNTTデータは今年度の公共・社会基盤分野の数十のシステム開発プロジェクトにおいて、Synopsysのソフトウェア開発向け静的解析ツール「Coverity」を用いた大規模なフィールドテストを行い、幅広いソースコードに対する客観的かつ定量的な評価メトリックスとモニタリング手法の確立を目指す。更に評価結果を蓄積・分析することで、「Coverity」を用いた高品質・高セキュリティなシステム開発プロセスの実現を目指す。SynopsysはNTTデータの取り組みに協力し、フィールドテストから得られるフィードバックを基に「Coverity」の更なる機能拡張や技術開発を行っていくという。

2018.07.02

2018年7月2日、Cadenceは同社の低消費電力プロセッサ「Tensilica Fusion F1 DSP」がIoT向けのモデムに採用された2つの事例を発表した。

発表された事例はXinyi Information Technology社とRafael Micro社によるもので、いずれもナローバンドを利用するIoT向けのモデムの開発でCadenceの「Fusion F1 DSP」を採用。Xinyi Information Technology社の開発した「Xinyi Marconi X1」モデムは、パワーアンプをシングルダイに統合した業界初のモデムで、「Fusion F1 DSP」を用いることで他のプロセッサ・アーキテクチャーよりもプロトコル・スタックのコードサイズを20%縮小することに成功した。Rafael Micro社は、「Fusion F1 DSP」を用いることで競合プロセッサーよりも消費電力36%減、コードサイズ45%減でモデムを実装できた。いずれの事例においても「Fusion F1 DSP」の採用により、将来のNB-IoT規格に合わせて更新やアップグレードが容易になると共通のメリットがうたわれている。

Cadenceの「Fusion F1 DSP」は音声ウェイクアップなど常時稼働のIoTアプリケーションやウェアラブル・デバイス向けのセンサーフュージョン機能などをターゲットにしたプロセッサで低消費電力でありながら高性能なプロセッシング能力を強みとしている。Cadenceによると、「Fusion F1 DSP」には無線通信に効率の良い命令セットが搭載されており、NB-IoTモデムソリューションに最適なソリューションだという。

2018.06.29

2018年6月28日、Bloombergの記事:

6月27日IntelがAppleと結ぶモデム契約を失う恐れが新たなデータで示唆された。アナリストはIntelに代わりMediTekがApple向けにモデムを製造する可能性があると指摘。Appleはモデムの内製を進めているという臆測もある。

2018.06.28

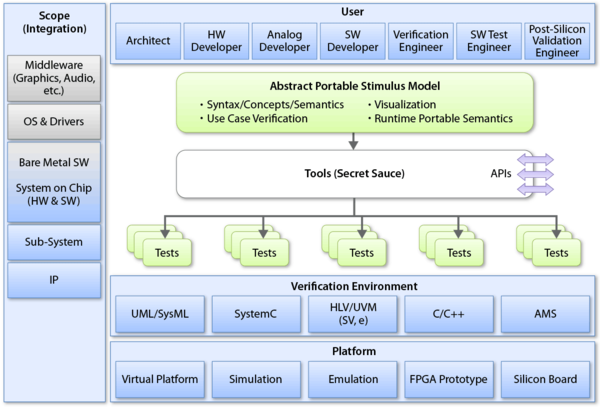

2018年6月26日、ハードウェア設計言語・技術の標準化団体米Accellera Systems Inisiativeは、Portable Test and Stimulus 1.0仕様の承認を発表した。

PSS(Portable Test and Stimulus Standard)は、シミュレーション、エミュレーション、FPGAプロトタイピング、ポストシリコン検証など様々なレベル、プラットフォームで利用できるスティミュラスおよびテストシナリオの記述仕様で、スティミュラスおよびテストの再利用性と可搬性の向上を目指すもの。同仕様に準拠したテスト仕様を記述することで、それを複数のプラットフォーム間で移植できる。PSS仕様は約3年前にワーキンググループが発足。ようやく標準仕様の策定・承認に漕ぎ着けた。

PSS1.0のLRMは下記URLより無料でダウンロード可能。

http://www.accellera.org/downloads/standards/portable-stimulus

今回のPSS1.0標準化の発表を受けて早速CadenceとMentor Graphicsが自社ツールによるPSS1.0サポートを発表している。

2018.06.28

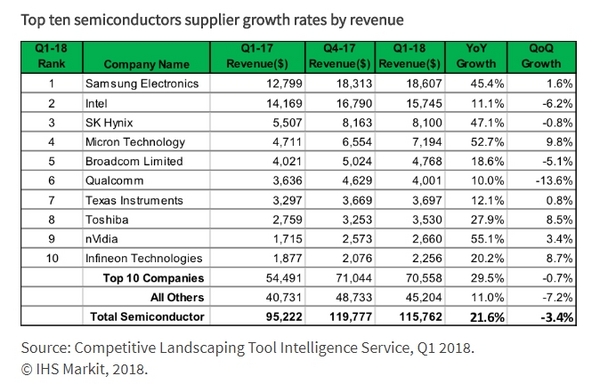

2018年6月26日、市場調査会社IHS Markitは2018年Q1(1-3月)の世界半導体市場の売上額を発表した。

発表によると2018年Q1(1-3月)の売上額は1,158億ドルで前年比3.4%のマイナスだった。IHSによると無線通信分野の売上が減少した。米SIAは同時期の売上額を前年比20%増の1,111億ドルと報告している。

製品分野でみるとメモリは前年比1.7%増の397億ドルと好調だった。

企業別でみると上位3社はSamsung, Intel, SK Hynixと変わらず。無線通信分野のBroadcomとQualcommは売上を落とした。売上TOP10は下記表の通り。

2018.06.27

2018年6月25日、MagillemとArteris IPは両社のパートナーシップとツールのインテグレーションについて発表した。

発表によるとMagillemのSoCアーキテクチャ設計環境においてArteris IPのインターコネクトIP「FlexNoC」および「Ncore」をIP-XACT形式でインポート可能となった。これにより両社製品の共通ユーザーは、単一のMagillem環境内にて複数の「Ncore」および「FlexNoC」インスタンスを使用してSoCアーキテクチャを容易に構築できるようになる。

両社製品のインテグレーション環境は、6月24日からサンフランシスコで開催されている第55回Design Automation CconferenceのMagillemブースで展示されている。

なおArteris IPは6月26日に同社の顧客企業が累計100社に達したことを発表している。

2018.06.27

【DAC2018】Cadenceが機械学習を用いたキャラクタライゼーションツールの新製品を発表

2018年6月26日、Cadenceは、新製品「Cadence® Liberate™ Trio Characterization Suite」を発表した。

発表によるとCadenceの新製品「Cadence® Liberate™ Trio Characterization Suite」は、statisticalキャラクタライゼーションとnominalキャラクタライゼーションを並列に実行できる業界初の統合ライブラリ・キャラクタライゼーションツールで、機械学習を用いてキャラクタライズする必要がある重要なコーナーを判断するという機能を持つ。また、クラウド上での実行に最適化されており、パブリッククラウドまたは社内のプライベートクラウドいずれの環境でもツールの処理を数千CPUに分散可能。通常数週間要する処理を数日に短縮することができるという。

Armによると自社のフィジカルIP「Artisan」を用いて「Liberate Trio Characterization Suite」を試したところ、同じCPU数でキャラクタライゼーションTATが大幅に改善されたとの事。

2018.06.27

2018年6月25日、Synopsysは、理研による「ASIP Designer」の採用事例を発表した。

発表によると理研はSynopsysのカスタム・プロセッサ開発環境「ASIP Designer」を用いて、分子動力学(MD)シミュレーション用のカスタム・プロセッサを開発する事に成功した。MDシミュレーションは大規模なバイオロジカル・システムの解析において実行するもので、今回開発したカスタム・プロセッサにより既存のプロセッサよりも30倍高速なシミュレーションが可能となった。

理研の開発したMDシミュレーション用カスタム・プロセッサは、ASIPコア8000個で構成されるという大規模なものだが、「ASIP Designer」の利用によりその開発期間はコンセプトレベルからインプリメンテーションまで6ヶ月以内で収まったという。

2018.06.27

2018年6月25日、中国のIPベンダGeneral Processor Technologiesは、新製品となるAIアクセラレータ「GPT」とDSP「VLVm1」を発表した。

発表によるとAIアクセラレータ「GPT」はCNN推論用に設計されたコンフィギュラブルIPで、コンボリューション、プーリング、ドロップアウト、パディングおよびプログラム可能なアクティベーション機能を提供。28nmテクノロジで最大1GHzで実行される各CNNビルディングブロックには288個のMACユニットが搭載され、最大8ユニット、2000MACを超える拡張が可能。性能、消費電力、および精度は、組み込み整数データ型または16ビット浮動小数点演算を使用して最適化することができる。「GPT」は一般的なCNNネットワークのライブラリを提供する。

「VLVm1」は、動的にベクトル長を指定できる可変長ベクトルDSP実行ユニットとスーパースカラ型アウトオブオーダーCPU「Unity」組み合わせた画像処理用DSPで最大3GHzで動作。ヘテロジニアス・プロセッサの共通プログラミングビューを提供するUnity 1.0 ISAをベースとしている。

General Processor TechnologiesのAIアクセラレータとDSPは中国ファブレスベンダOptimum Semiconductor社のSoC「GP8300」に搭載され今年Q3に市場に登場する予定。

2018.06.27

2018年6月26日、IC Insightsの記事:

IC Insightsによると、今年中国の半導体企業の設備投資額が日本および欧州企業の設備投資額の合計額を上回る見通し。中国企業による設備投資は110億ドルに達する見通し。中国企業の投資額は過去5年で7倍以上に増加。日本および欧州企業の投資額を上回るのは初めて。

2018.06.27

2018年6月26日、XilinxとDaimlerは車載システム開発に関する両社の提携を発表した。

発表によるとDaimlerは、車載アプリケーションのAI処理にXilinxの提供するオートモーティブ・プラットフォームを採用。その最初の事例としてメルセデスベンツの新型車に搭載される超高効率なAIソリューションをXilinxと共同で開発している。Xilinxのオートモーティブ・プラットフォームは、SoC「Zynq」とAIアクセラレーション・ソフトウェアで構成されており、低レイテンシかつ電力効率に優れたAI処理を実現する。

2018.06.27

2018年6月26日、富士通セミコンダクターは新製品8MビットFRAM「MB85R8M2T」を開発し今月から量産を開始した事を発表した。

8MビットFRAM「MB85R8M2T」は富士通セミコンダクターのFRAM製品としては最大容量。1.8V-3.6Vのワイドレンジで動作し、SRAM互換のパラレルインターフェースをもつ。不揮発性メモリであるFRAMをSRAMの代わりに利用する事で瞬断対策用のバッテリーが不要となり、場合によりメモリ部の実装面積を約90%削減可能。またFRAMの書換え保証回数は10兆回と同じ不揮発性メモリのEEPROMの約1,000万倍の耐性がある。富士通セミコンダクターのFRAMは、コスト削減効果と合わせて頻繁なデータ書換えが必要な産業機械用途を狙っている。

2018.06.26

2018年6月25日、SoC組み込み型のFPGAコアを手掛けるFlex Logix Technologiesは、新製品となるAI向けのeFPGA「EFLX4K AI」を発表した。

FlexLogixによると新製品「EFLX4K AI」は、面積あたりのニューラルネットワーク処理性能に特化して最適化された組込み型FPGAコアでディープラーニングのパフォーマンスを10倍向上する事が可能。「EFLX4K AI」は他社製品よりも1平方ミリメートルあたりのDSP MAC数がはるかに多く、個々のMACがAI向けに最適化されているのが特徴。具体的には必要に応じて16ビットMAC、16×8 MACまたは8×16 MACとして再構成可能な8ビットMAC(アキュムレータ付き8×8乗算器)が各コアに441個搭載されており、16nmのシングルコアで面積は約1.2平方ミリメートル、最大7x7の「EFLX4K AI」アレイはワーストケースで20TeraMACs/secondを超えるという。「EFLX4K AI」の再構成可能なアーキテクチャは同社の特許取得済のインターコネクト技術によって実現されている。

FlexLogixによると既にハーバード大学が同社のeFPGAをディープラーニング用に採用しており、開発したAIチップを来月開催されるHotChipsで発表する予定との事。ハーバード大は更に後続の16nm AIチップの開発に取り組んでいるという。

「EFLX4K AI」コアは、顧客の要求に応じて6-8ヶ月で任意のプロセスノードに実装可能。既存のEFLX4Kロジック/DSPコアと互換性をもつ。

FlexLogixの新コアは6月24日からサンフランシスコで開催されている第55回Design Automation Cconferenceで展示されている。

2018.06.26

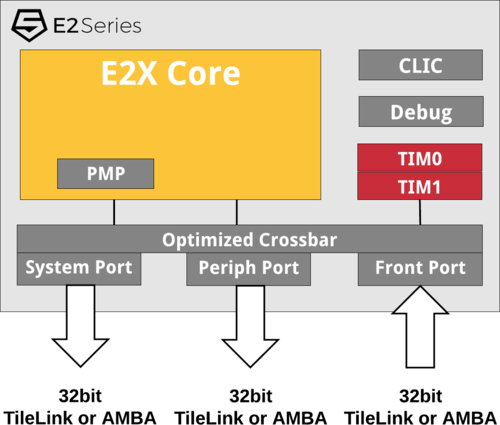

2018年6月25日、オープンソースのISA「RISC-V」ベースのプロセッサIPを手掛ける米SiFiveは新製品「E2」コアシリーズを発表した。

発表によるとSiFiveの新コア「E2」シリーズは省面積、ローパワーに特化して最適化されたRISC-Vベースの32ビットMCUコアでIoTやウェアラブル・デバイスへの利用をターゲットとしている。最初の「E2」シリーズコアとして発表されたのは「E20」と「E21」の2品種。合わせてSiFiveは既存のコア「E3」および「E5」コアの強化を発表。新しい拡張乗算ユニットが追加され、コヒーレントなマルチコア構成をサポートたという。

SiFiveの新コアは6月24日からサンフランシスコで開催されている第55回Design Automation Cconferenceで展示されている。

2018.06.26

2018年6月25日、Caenceはクラウドベースの設計環境を実現する「Cadence® Cloud portfolio」を発表した。

「Cadence® Cloud portfolio」はクラウド上のスケーラブルなコンピューティング・リソースを活用して分単位、時間単位でのツール利用を実現するためのソリューション群で、ベースとなるクラウド環境としてはAmazon Web Services(AWS)、Google Cloud Platform(GCP)、Microsoft Azureを利用することができる。

「Cadence® Cloud portfolio」の中身としては大きく下記2つがある。

・ユーザーが独自に管理するクラウド環境向けソリューション

・Cadenceが管理するクラウド環境向けソリューション

「Cadence Cloud Passport Model」は、独自にクラウド環境を管理する顧客に向けたソリューションで、クラウドでの使用に対応したCadenceのEDAツール、クラウドベースのライセンスサーバー、CadenceのEDAツールにアクセスするためのダウンロードメカニズムなどが含まれる。

「Cadence Cloud-Hosted Design Solution」は、Cadenceが完全に管理するクラウド環境ソリューションでAWSまたはMicrosoft Azure上で運用される。「Cadence Cloud-Hosted Design Solution」には、Cadence独自のセキュリティ技術やクラウド上でツールを利用するための各種自動化機能などが含まれている。自動化機能としてはクラウド環境のセットアップ、メンテナンス、ジョブ管理などを簡単にユーザー提供するために開発されたポータルが用意されており、これを利用することで例えばロジック・シミュレーションやライブラリのキャラクタライズなどのピーク要件に迅速に対応できる。

クラウド環境で利用できる初期のツールとしては、回路シミュレータ、パワー及びEM解析ツール、論理シミュレータ、フォーマル検証ツール、物理検証ツール、タイミングサインオフ・ツール、寄生抽出ツール、パワー・インティグリティ解析ツール、ライブラリ・キャラクタライゼーション・ツールなどが挙げられている。

また、Cadenceはエミュレータをクラウドベースで利用可能とする「CadencePalladium®Cloud Solution」も発表。同ソリューションはCadenceが管理するエミュレータのリソースを必要に応じてCadenceが直接ユーザーに割り当てるものだという。

今回発表されたCadenceのクラウドソリューションは、既に100社以上の顧客で試験運用されたもので既に利用可能な状態になっている。TSMCは独自の検査でCadenceのクラウド環境のセキュリティを認証し、Cadenceのクラウド環境上でTSMCのプロセスモデルとルールデッキを配布しているという。

2018.06.26

2018年6月25日、Micron Technologyは8GB GDDR6メモリの量産開始を発表した。

次世代GDDR6メモリは、AI, networking, automotive, GPUなどのハイパフォーマンス・アプリケーションで利用される見通し。NVIDIAはGPU「GeForce 20」シリーズでGDDR6の採用を予定している。

2018.06.26

2018年6月22日、Digitimesの記事:

TSMCが7nmプロセスを用いた量産を開始。年内50チップ以上をテープアウトする予定でその大半はAI,GPU,仮想通貨マイニングチップ。5Gやアプリケーションプロセッサがこれに続く。TSMCに7nmチップを発注している顧客はApple, AMD, Bitmain, Nvidia, Qualcommなど約20社。TSMCは2018年後半にEUVを用いた7nmチップのテープアウトを計画している。Qualcommは7nmチップの製造はSamsungからTSMCに乗り換える見通し。

TSMCは独自開発のパッケージ技術「InFO( Integrated Fan Out)」を強みに7nmプロセスでもシェアを拡大すると見られている。

2018.06.26

2018年6月25日、Digitimesの記事:

Digitimes Researchによると2018年の中国のIC生産額は前年比28.8%増の約28億ドルに到達する見込み。国内需要の継続、Fab増強による生産能力の拡大、メモリ価格の高騰などが後押し。中国は2020年までに自国内で消費するICの自給率を40%に引き上げる計画。

2018.06.25

2018年6月18日、Mentor Graphicsは物理検証ツールCalibreシリーズの新製品「Calibre® RealTime Digital」を発表した。

発表によると「Calibre® RealTime Digital」は、Mentorが2011年にリリースした「Calibre RealTime Custom」の姉妹製品でフル・チップおよびブロック・レベルのデジタル・デザインをターゲットにした新しい物理検証ツール。配置配線後のフルDRCで検出した違反を再度配置配線ツールを用いて修正する際に追加のエラーを生んでしまう事がしばしばあるが、「Calibre® RealTime Digital」は配置配線ツールと連携してデザインに軽微な変更を行うことで追加のエラーを発生させずにDRC違反を解決・収束させる事ができる。これによりフルチップ・パスの反復回数を減らす事が可能でサインオフ・スケジュールを数週間短縮することができるという。

Mentorは新製品「Calibre® RealTime Digital」を6月24日からサンフランシスコで開催されている第55回Design Automation Cconferenceで展示予定。

2018.06.25

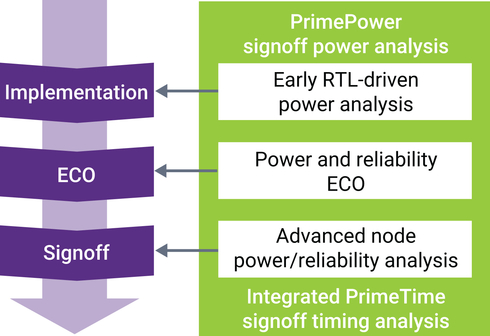

2018年6月21日、Synopsysは新製品「PrimePower」を発表した。

発表によるとSynopsysの新製品「PrimePower」は、同社の静的タイミング解析ツール「PrimeTime®」の技術をベースに開発されたパワー解析ツールで、設計者はRTLシミュレーション・ベクタを使用して実装フェーズの早期段階で正確なパワー解析およびパワー最適化を実行可能。パワーおよび信頼性のサイオンオフとECOのTATを短縮できる。

「PrimePower」には「PrimeTime」およびエミュレーター「ZeBu」とのネイティブ・インタフェースが備えられており、「PrimeTime」と連携した効率的な信頼性サインオフ解析が可能なほか、「ZeBu」を活用したアクティビティ・プロファイルによってピーク・パワーを正確に解析する事も可能。 アベレージ・パワー、クロックネットワーク・パワー、リーク・パワー、マルチボルテージ・パワーの解析もサポートしている。

新製品「PrimePower」の詳細は、6月24日からサンフランシスコで開催されている第55回Design Automation Cconferenceで紹介される予定。

2018.06.25

2018年6月21日、SoCのオンチップ解析ソリューションを手掛けるUltraSoCとバーチャル・プロトタイピング環境を手掛けるImperasは、両社の協業を発表した。

発表によるとUltraSoCは自社のツール環境にImperasのツールの重要な要素を取り込み、システムレベルのプリおよびポストシリコン開発フローを構築する計画。UltraSoCは、オンチップのモニタリング、解析、デバッグソリューションを、Imperasはバーチャル・プロトタイピングのためのシミュレータと各種モデルを提供している。

UltraSoCとImperasの両社はともにRISC-V Foundationに加盟する企業で、昨今ビジネス面でも熱を帯びつつあるRISC-VベースのSoC開発に勝機を見出しており、今回の協業はRISC-Vをスコープにしたものとなる。

両社の協業ソリューションは、6月24日からサンフランシスコで開催されている第55回Design Automation Cconferenceの展示会場内RISC-V Foundation Pavilionで展示される。

2018.06.23

2018年6月22日、ARMとSamsungは業界初となる「eMRAM compiler IP」と先端プロセス向けの新しいフィジカルIPを発表した。

発表によると「eMRAM compiler IP」は、Samsungファウンドリの28nm FDSOIプロセステクノロジ向けに利用できるソリューションで、Flash、EEPROM、低速SRAM/データバッファメモリを単一のeMRAMに置き換えるインスタンスを生成することが可能。ユーザーはわずか3つの追加マスクでeMRAMをインテグレーションできる。ARMは「eMRAM compiler IP」で作成したテストチップのテープアウトを完了しており、今年Q4に先行顧客に提供を開始する予定としている。

Samsungファウンドリ向けの新しい「Artisan physical IP」は、Samsung 11LPP, 7LPP そしてEUVを用いた5LPEプロセスに対応するもので、11LPP向けのフィジカルIPは既に先行顧客向けに提供可能。7LPP向けは2018年Q3から、5LPE向けは2019年初旬から先行顧客への提供が開始される予定となっている。

2018.06.23

2018年6月22日、Fudzillaの記事:

2018年9月に発売予定の新型iPhoneのモデムはIntelとQualcommの両社から供給される。Intelが殆どのシェアを奪うという噂もあったがCDMA対応などによりQualcommのモデムも使われる可能性がある。Qualcommの供給するモデムはダウンロード速度1.2Gbpsだが性能の低いIntelのスペックに合わせ1.0Gbpsに抑える。Intelのモデム技術はQualcommの技術よりも約2年遅れている。

2018.06.22

2018年6月21日、インターコネクトIPを手掛けるNetSpeed Systemsは新製品「Orion AI」のリリースを発表した。

発表によるとNetSpeedの「Orion AI」は、同社の実績あるインターコネクトIP「Orion IP」をベースに構築された新製品でAI機能を備えるSoCやAIアクセラレータの性能および効率アップを狙うもの。AIシステムでは中央のメモリを介さず迅速かつ効率的なピアツーピアのデータ交換が求められるため、「Orion AI」はそれに対応するマルチキャストやブロードキャストなどの高度な機能を提供。何千もの計算エンジンをサポートできる基盤アーキテクチャを備えており、最大1024ビットのインターフェイスを備えたデータパスを提供し、最大4Kバイトのバーストをサポートする。

なお、「Orion AI」のベースとなっている「Orion IP」は既にHorizon Robotics, Cambricon, Baidu, EsperantoなどのAI企業にライセンスされた実績がある。

NetSpeedは新製品「Orion AI」を6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceで展示すると見られる。

2018.06.22

2018年6月21日、バーチャル・プロトタイピング・ソリューションを手掛けるImperasとIPベンダAndes Technologyは、新しいシミュレーション用のCPUモデルについて発表した。

発表によるとImperasは同社のバーチャル・プロトタイピング環境「Open Virtual Platforms」で動作するAndesのN25およびNX25プロセッサの命令精度のシミュレーション・モデルを用意。同モデルがAndesによって認証された。AndesのN25およびNX25プロセッサは、オープンソースの命令セットアーキテクチャRISC-Vをベースに開発された商用の32/64ビットCPUコアである。

Imperasは今回発表したAndesのN25およびNX25プロセッサモデルを6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceにて展示する予定。

2018.06.22

2018年6月21日、マルチコア・システム向けのソフトウェア開発ツールを手掛けるSilexicaは、資金調達Bラウンドの成功を発表した。

発表によるとSilexicaは、同社2度目となる資金調達Bラウンドで投資家らから計1800万ドルを調達した。2016年に実施した資金調達Aラウンドの調達額を合わせると同社に対する投資家の出資は計2600万ドルになる。

Silexcaはワールドワイドでマルチコア・システム向けのソフトウェア開発ツールを展開しており、THALES、Huaweiといった大手に加え日本でも富士通やデンソーなどを顧客に持つ。富士通では4G/5G基地局プロジェクトで、デンソーでは車載マルチコアプラットフォームの開発で同社の「SLX Tool Suite」が活用されているようだ。

今回の資金調達によりSilexcaは更なる製品の強化を進めるとの事。同社は昨年車載システム開発に特化した「SLX Automotive Developmentパッケージ」をリリースしている。

2018.06.22

2018年6月21日、Bloombergの記事:

Intelは同社のCEOブライアン・クルザニッチ氏の退任を発表した。

過去に社員との間で同意の上での親密な関係にあり社則に反したというのが退任に関するIntelの説明。後任のCEOが決まるまでCFOのロバート・スワン氏が暫定CEOを務める。

2018.06.21

2018年6月11日、RTL静的解析ツールを手掛けるBlue Pearl Softwareは、新製品「HDL Creator」を発表した。同製品は6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceにて披露する。

発表によるとBlue Pearlの新製品「HDL Creator」は、「最新のコードエディタに期待される全ての機能を提供する」という謳い文句のコードエディタで、リアルタイムの構文チェックやスタイルチェック機能、コンパイルの依存関係や依存関係の欠落などをリアルタイムで分析するファイル分析機能、オートコンプリート機能やエラー修正の提案機能など、コーディングのミスを回避しコードの理解とデバッグを支援するリッチな機能を提供してくれる。

「HDL Creator」は、スタンドアロンのエディタとして利用できるが、Blue Pearlの「Visual Verification Suite 2018.2」にも統合されており、同検証ツールの顧客にも提供される。現在は早期顧客向けにツールを提供中で正式出荷は今年の夏を予定している。

2018.06.21

2018年6月18日、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)は、パナソニックセミコンダクターソリューションズ(株)、北海道大学とともに、アナログ抵抗変化素子を用いたAI半導体向けの脳型情報処理回路を開発し、世界最高水準の低消費電力動作の実証に成功したと発表した。

発表によると今回NEDOらが開発したAIチップは、データ保存用のメモリーと積和演算器を用いる代わりに、アナログ抵抗変化素子(Resistive Analog Neuro Device: RAND)を用いてデータ保存機能と積和演算機能を一体化した回路を開発。RANDを用いたAIチップはすでに製品化されているパナソニックのReRAM(不揮発性抵抗変化メモリー)をベースにパナソニックのReRAM製造プロセスを応用して開発した。40nmプロセスで開発したRANDのテストチップは66.5 TOPS/Wという世界最高水準の低消費電力で動作する事が確認された。

NEDOは今回の成果を、クラウド学習用、クラウド学習・推論兼用、クラウド推論用、エッジ推論用と分類分けしていたAI半導体に、新たに「エッジ学習・推論兼用」のカテゴリを切り開くものと位置付けている。

2018.06.21

2018年6月20日、ZDNetの記事:

Hewlett-Parckard Enterpriseはインテリジェント・エッジ・デバイスの開発に向こう4年間で40億ドルを投じる計画。同社のCEO Antonio Neri氏はリアルタイム体験を提供するために、エッジ・ツー・クラウド・アーキテクチャを構築しなければならないとコメント。

2018.06.21

2018年6月20日、プロセス/デバイス・シミュレータおよびアナログ、ミックスド・シグナル、RF設計向けツールを中心に各種EDAソリューションを展開するSilvacoは、6月24日からサンフランシスコで開催される第55回Design Automation Cconferenceの展示内容を発表した。

発表によるとSilvacoはDACにて機械学習を利用した複数のソリューションを展示する予定。ばらつき考慮のデザイン検証ツール「Varman」、SPICEモデリングツール「TechModeler」、スタンダードセルライブラリ自動作成・マイグレーションツール「Cello」などにおいて機械学習を活用しているようだ。

説明によると「TechModeler」は、ニューラルネットワーク・アルゴリズムを使用して、少ないサンプルで非常に正確な動作のVerilog-A SPICEモデルを作成可能。「Cello」はこれまでのSilvacoのEDAラインナップに無い製品名で新製品なのかもしれない。

2018.06.21

2018年5月31日、エッジ向けのAIソリューションを手掛けるベンチャーKneronは、1800万ドルの資金調達に成功したことを発表した。

Kneronは2015年にサンディエゴで設立されたAIベンチャーで経営者は台湾系、エッジ向けのAIプロセッサおよび独自のニューラルネットワーク技術をベースにした視覚認識ソフトを手掛けている。

発表によると同社は資金調達A1ラウンドでベンチャー・キャピタルHorizons Venturesらから計1800万ドルを調達した。Kneronは獲得した資金を元にスマートフォン、スマートホーム、監視システムをターゲットとしたパートナーとの製品開発とコラボレーションを加速するとしている。同社のパートナーにはAlibaba, Baidu, TencentやQualcommなどの大手が名を連ねている。

Kneronのエッジ向けAIプロセッサ「NPU」は超低消費電力をうりにしており、現在「KDP 300/500/700」と3種類の製品を提供。スマートフォンの顔認識用に開発された「KDP 300」は5mW未満で動作する。Kneron今年の後半に画期的な3D AIソリューションを発売する計画だという。

2018.06.20

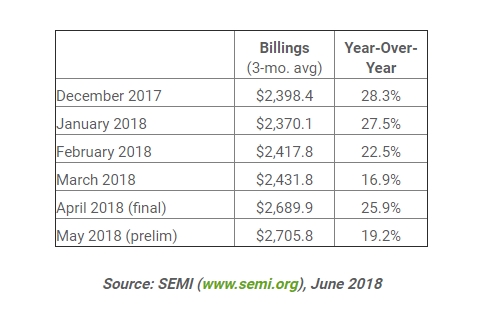

2018年6月19日、SEMIは2018年5月の北米製装置(輸出を含む)の販売高速報値を発表した。

5月の北米製半導体製造装置の販売額は前年比19.2%増の27億580万ドルで4月の販売額を0.6%上回った。販売額20億ドル超えは15ヶ月連続。