NEWS

2018.08.24

2018年8月22日、市場調査会社IHSは2018年Q2(4-6月)の世界半導体市場の統計を発表した。

IHSによると、2018年Q2(4-6月)の世界半導体市場はQ1比4.4%増の1,208億ドルで過去最高を記録した。うちメモリの売上は420億ドルで、その恩恵に預かるSamsungは企業別売上ランキング首位で半導体市場のシェア15.9%を獲得した。2位のIntelはシェア13.9%。Q1売上に対する成長率では、メモリよりも各種マイクロコンポーネントの成長率がわずかに上回った。

ちなみにSIAの統計では2018年Q2(4-6月)の売上は1,156億ドルとなっている。

2018.08.23

2018年8月20日、オープンソースのISA「RISC-V」ベースのプロセッサIPを手掛ける米SiFiveは、RISC-VとNVDLAをベースとしたオープンソースのSoC開発プラットフォームを発表した。

発表によるとSiFiveが発表したSoC開発プラットフォームは、SiFiveのRISC-V processor「Freedom U540」と、NVIDIAのオープンソースのディープラーニング・アクセラレータ「NVDLA(NVIDIA Deep Learning Accelerator)」を組み合わせたもので、エッジデバイス向けのディープラーニング推論アプリケーションの開発をターゲットとしている。SiFiveは先ごろ開催れたHot Chipsで同プラットフォームのデモを実施。同社のプラットフォームを利用すればSoC開発に伴うIPコストを大幅に削減できるようになる。

なお、NVIDIAは今年3月、ディープラーニング・アクセラレータ「NVDLA」の普及に向けてArmとの提携を発表している。

2018.08.23

2018年8月21日、Electronics Weekly.comの記事:

Allied Market Researchのレポートによると、マシンラーニング・チップ市場の2018年から2025年までの平均成長率は40.8%で、2025年には市場規模が378億ドルに到達する。

2017年時点でのマシンラーニング・チップ市場の主役はGPUで、総収入の3分の1を占めているが、2025年までにASIC/SoCが市場の半分を占める見通し。ASIC/SoC市場は2018年から2025年にかけて21.33%の成長が見込まれている。地域的に最も伸びるのはアジアで2025年までの成長率は21%。現在は北米が市場を支配している。

2018.08.23

2018年8月22日、Qualcommは7nmプロセスで製造する次世代モバイルSoCのサンプル出荷開始を発表した。

Qualcommがサンプル出荷を開始した新型SoCは、同社初の5G対応モバイルSoCで、Qualcomm®Snapdragon™X50 5Gモデムを搭載。Snapdragonのフラッグシップ製品として2019年前半には市販のスマートフォンに搭載される見通し。

2018.08.23

2018年8月20日、IPA(独立行政法人情報処理推進機構)は、同団体の主催する「次世代計算機講座」についてアナウンスした。

IPAの「次世代計算機講座」は、ゲート式量子コンピュータやアニーリングマシン等の次世代計算機に関する最新動向を捉え、技術的知見を深めることを目的とした講座で、無料で参加することが可能。<入門編>と<実践編>に分かれている。

<実践編>では、フィックスターズ社にて、富士通、日立製作所、D-Wave、各社のアニーリングマシンを使用したプログラミング実習が行われる。

■開催日程

<入門編>2018年9月15日(土)開催

<実践編>2018年10月12日(金)、13日(土)開催

2018.08.23

2018年8月20日、IC Insightsの記事:

IC Insightsが発表した2018年上半期の半導体売上ランキングTop15によると、下記7社が前年比20%以上の成長を達成。7社中5社はメモリベンダで、昨年に続いてメモリ市場の活況が各社の業績を大きく押し上げている。

Samsung 1位 前年比36%増

SK Hynix 3位 前年比56%増

Micron 5位 前年比45%増

東芝 8位 前年比25%増

Nvidia 10位 前年比53%増

WD/Sandisk 11位 前年比27%増

ST Micro 14位 前年比20%増

2018.08.23

2018年8月22日、CNET Japanの記事:

スパコン「京」の後継機に搭載される富士通製のCPU「A64FX」は、Armv8-A命令セットアーキテクチャをスーパーコンピュータ向けに拡張する「SVE(Scalable Vector Extension)」を世界で初めて採用したCPUで、CPUとCPUの間は独自のTofuインターコネクトで直結する。メモリバンド幅性能を引き出すハードウェア技術も組み合わされる事で、64ビット浮動小数点演算のピーク性能は、2.7TFLOPS以上に達する。

富士通と理研は2021年頃の実用化を目指して「京」の後継機を開発している。

2018.08.17

2018年8月16日、CadenceはTSMCの設計子会社GUC(Global Unichip Corporation)による同社エミュレータ「Palladium Z1」の採用事例を発表した。

発表によるとGUCは、Cadenceのエミュレータ「Palladium Z1」とシミュレータ「Xcelium™ Parallel Logic Simulation」を組み合わせて使用することにより、検証作業を最大795倍加速。デバッグの完全な可視性を保ちつつ、より複雑なSoC検証テストシナリオを適用することができた。更に「Palladium Z1」の利用は設計変更の探索においても大幅な工数削減効果をもたらしたという。

なおGUCはエミュレータ、シミュレータの他にCadenceの提供する検証IPやフォーマル検証ツール(JasperGold® Formal Verification Platform)なども活用しているとのこと。

2018.08.17

2018年8月15日、韓国最大の通信キャリアSK Telecomは自社データセンターにXilinxのFPGAを採用した事をXilinxと共同で発表した。

発表によるとSK Telecomは、AIアクセラレータとしてXilinxのFPGA「Kintex UltraScale KCU1500」を採用。自動音声認識アプリケーションの実行にFPGAを利用することにより、GPUでの処理と比較して最大5倍のパフォーマンスを達成。1ワットあたりのパフォーマンスは16倍向上した。

FPGAの配備は、既存のCPUサーバーの空きスロットにFPGAアドインカードを挿入する形で実施。1枚のFPGAカードでサーバの性能が最大5倍になり、大幅なコスト削減を実現したという。

2018.08.17

2018年8月16日、WSTS(世界半導体市場統計)が最新の市場予測を発表した。

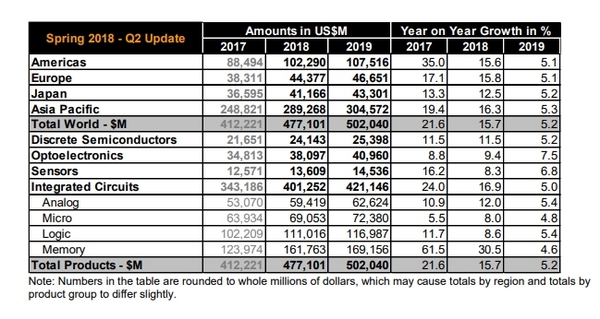

発表によると今年の世界半導体市場は前年比15.7%増の4771億ドルに達する見通し。前回春季市場予測(前年比12.4%増、4634億ドル)を上方修正する形となった。全ての地域、全ての製品分野で売上予測が上方修正されているが、地域別で最も予測値が増えたのはアジア・その他地域、製品分野で最も予測値が増えたのはメモリとなる。

2018.08.16

2018年8月15日、高位合成ツールを手掛ける米Bluespecは、オープンソースのRISC-Vプロセッサの提供開始を発表した。

発表によるとBluespecは小型でIoTアプリケーションをターゲットとしたRV32IMベースのプロセッサ・ファミリ「Piccolo」を開発。「Piccolo」はオープンソースのプロセッサ・コアとしてGitHub上で公開されており、誰でも無料で合成可能なVerilogコードを利用できる。

Bluespecは「Piccolo」を積極的に維持・サポートすると同時にRISC-Vコアのカスタマイズと検証のための商用ツールを提供。Bluespecは、エンベデッド・コントローラの全機能を提供するための設定を継続的に追加していくとしており、プロセッサ・コアの無料提供を推し進めその開発環境の販売をビジネスとする格好だ。

Bluespecは、SystemVerilogベースの専用言語「Bluespec SystemVerilog」で記述した抽象度の高い回路記述をRTLに合成するESLツールを提供している。

2018.08.10

2018年8月9日、IC Insightsの記事:

半導体市場の調査会社IC Insightsによると、今年のDRAM売上は前年比39%増で1,000億ドルを突破する見込み。NAND Flashの売上は620億ドルを超える見通しで、DRAMおよびNANDの売上は全半導体売上の38%を占めると予測される。

半導体出荷ユニット数では、今年出荷される予定の3181億ユニットのうち54%がアナログ・ユニットと予測されており、最も出荷ユニット数が多いのはパワーマネジメント・デバイスで全出荷ユニット数の22%を占める見通し。

2018.08.10

2018年8月5日、アナログ半導体のSkyworks Solutionsは、ファブレス半導体ベンダAvneraを買収することを発表した。

Avneraはオレゴンに本社を置く2004年設立のファブレス半導体ベンダで、独自のアナログ技術を用いた無線オーディオチップや音声処理チップをアナログSoCと呼んで提供している。同社の主要顧客はHarman、JBL、Panasonic、Philips、Pioneer、Polk、Samsung、Sennheiser、Sony、Vizio、Yamahaなど。

発表によるとSkyworksは9月末までにAvneraの買収を完了する計画で、買収額は現金4億500万ドル。Skyworksはこの買収により、AIスピーカー/マイクロフォン、仮想アシスタント、インテリジェントゲームコントローラ、車両インダッシュシステム、有線/無線ヘッドセットなど新たに50億ドル以上の市場拡大効果を見込んでいるという。

2018.08.09

2018年8月7日、SoC組込型のFPGAを手掛けるAchronixは、高位合成を用いた開発フローを発表した。

発表によるとAchronixはMentor Graphics(Siemens)とのパートナーシップにより、Mentorの高位合成ツール「Catapult HLS」を用いた開発フローを実現。AchronixのSoC組込型FPGA「Speedcore」のユーザーは既存の開発環境「ACE design tools」と「Catapult HLS」を組み合わせてC++からのFPGA実装が可能となる。同フローは既に5Gワイヤレス・アプリケーションの実装に使用され、TAT短縮とQoR向上を実現した実績があるという。

AchronixのSoC組込型FPGAは高性能かつ高密度をうりとしており、SoCの仕様変更や機能追加に対応するするほか、データセンターのコンピューティング、ネットワーキング、ストレージなど様々なハードウェア・アクセラレーション・アプリケーションに利用できる。

2018.08.08

2018年8月7日、DigiTimesの記事:

調査会社Strategy Analyticsによると、2018年Q1のスマートフォンAP(アプリケーション・プロセッサ)市場は前年比0.3%減の45億米ドルだったが、AI機能を搭載したスマートフォンAPは前年比約3倍に増加した。主要なAI搭載のAPは、Apple A11 Bionic、HiSilicon Kirin 970、Qualcomm Snapdragon 845/835、Samsung Exynos 9810など。AI搭載APが伸びる中、MediaTekはスマートフォンAPのシェアを5四半期連続で失っている。

2018年Q1のタブレットAP市場は前年比6%減の4億8500万ドル。市場シェアはApple36%、Intel20%、Qualcomm17%。

2018.08.07

2018年7月20日にCadenceが開催したユーザーイベント「CDNLive Japan 2018」のレポート。

ここでは同イベントで行われた株式会社エヌエスアイテクス(以下、NSITEXE)のセッション「先端プロセッサIP開発における設計効率化」-Genus/Conformal Smart LECによる実装フロー改善-について紹介する。

同セッションの講演者は、株式会社エヌエスアイテクスの大久保 直昭氏(開発部 開発1課)である。

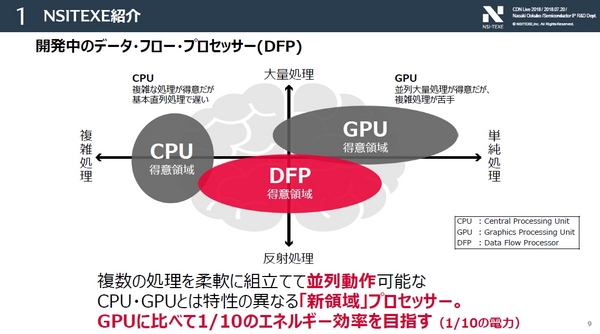

NSITEXEは2017年9月に設立されたデンソー100%子会社の車載向けの半導体IPベンダで、メイン事業として自動運転向けの高性能プロセッサーの開発を行っている。大久保氏によると同社が開発しているのは、自動運転における「瞬時の判断」を担うプロセッサーで既存のCPUやGPUとは異なる領域をターゲットとするもの。NSITEXEはそれをデータフロー・プロセッサー(DFP)と呼んでいる。

大久保氏によるとDFPの開発(RTLの設計)は、DFPのコア技術を持つ米AIチップベンチャーのThinCI社と共同で進めており、NSITEXE側ではRTLの修正がかかる毎に物理的な実装性の確認を行っている。そのため、社内での実装性確認フローを出来るだけ早く回すために、以下のような課題への対処が必要になってくる。

・フロントエンド・エンジニアによる一気通貫な実装確認フローの構築

・短TAT化(合成およびフォーマル検証の実行時間の削減)

・限られた計算機リソースでの様々なパラメータによる実装性の確認

・最適なフロアプランの早期探索

そこでこれら課題への対応策として、Cadenceの論理合成ツール「Genus」と等価性検証ツール「Conformal Smart LEC」を試用してみた。

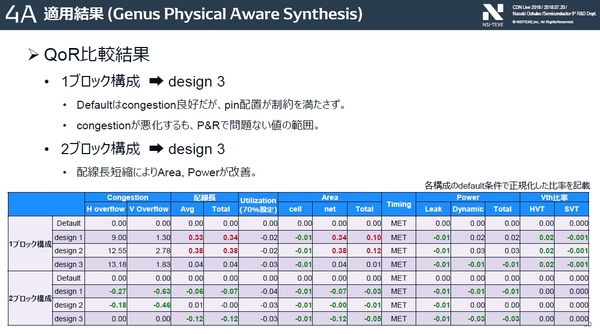

■「Genus」の試用:複数フロアプランの傾向分析

キャッシュメモリを持つメモリ比率の高いプロセッサIPの回路(43万インスタンス)をモチーフに、複数のフロアプランの傾向分析を以下の手順で実施した。

1.Genusでフィジカル合成を行いフロアプランを作成

2.アスペクト比、ポート位置、マクロ位置などを変更して任意のフロアプランを作成

3.再びフィジカル合成を行い結果を確認

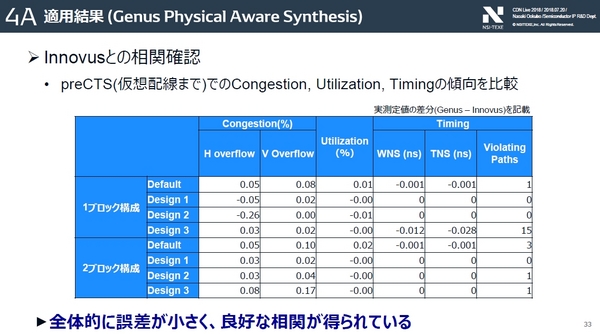

4.配置配線ツール「Innovus」による実行レポート(プレCTSまで)とGenusのレポートを比較

試行の結果、2パターン各4通りのフロアプランでQoRの分析を行い、フロアプラン制約を考慮しても配置配線で問題のないこと、Cell Densityが目標値の範囲内である事を確認。合わせて「Innovus」の結果とも誤差の少ない良好な相関関係が得られている事を確認した。これらは全てフロントエンド・エンジニアによって行われた。

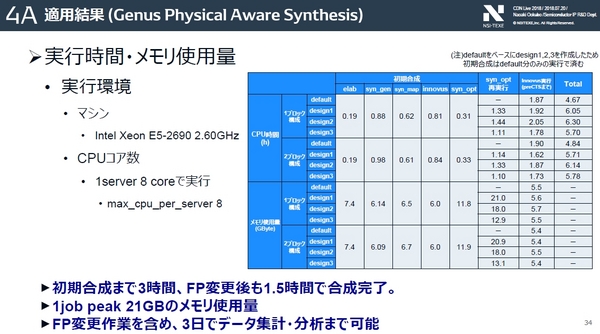

ツールの実行時間とメモリ使用量については下記スライドの通りで、「Genus」による初期フロアプラン合成まで3時間以内、フロアプラン変更後は1.5時間以内で合成が完了。ピークのメモリ使用量は21GBである事を確認した。大久保氏によるとこれら一連の作業はデータ集計、分析を含めて3日あれば十分だったとの事。大久保氏はこの結果から「Genus」を利用することでフロントエンド・エンジニアでも意図するフロアプランを自由に作成可能であり、Innovusとの相関性が高いフロアプランの探索が可能と結論付けた。

■「Conformal Smart LEC」の試用:CPU実行時間と等価性確認フローのTAT比較

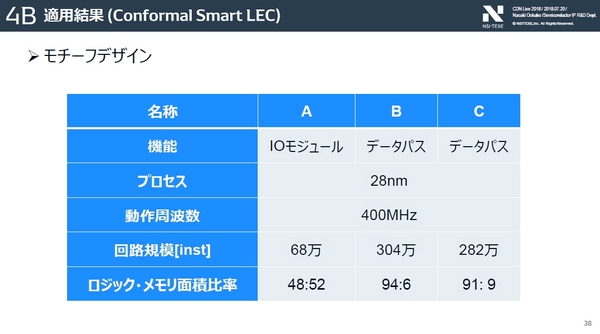

異なる3つの回路をモチーフに、「Conformal LEC」と「Conformal Smart LEC」CPU実行時間とデバッグを含む等価性確認フローのTAT比較を実施した。

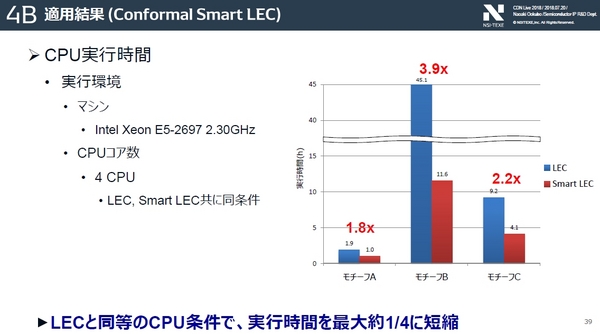

CPU実行時間を比較した結果、下記図の通り「Conformal Smart LEC」の利用により同等の条件下で実行時間を最大約1/4に短縮できる事を確認した。

合成から等価性確認までのフローを比較した結果、他社ツールを用いたフローでは合計217時間かかった作業が「Conformal Smart LEC」を用いたフローでは約1/3程度の計75時間で完了できた。大久保氏によるとその大きな違いは合成時間とデバッグに要する時間で、「Genus」による合成時間の短縮効果もさることながら、「Conformal Smart LEC」によるデバッグ時間の短縮が大きかったとの事。「Conformal Smart LEC」によるデバッグは、スクリプトの書き換え、合成オプションの見直し、リネーミングルールの見直しだけで短時間で完了できたという。

今回の試用結果を受けて大久保氏は、「Genus」および「Conformal Smart LEC」の利用でフロントエンド・エンジニアの守備範囲が広がり、バックエンドの実装容易性の向上が可能となり、更に手作業によるデバッグ時間の削減によって、継続的な受け入れ確認/プロダクション・テストを短TATで実現できるようになったとまとめた。

2018.08.07

2018年8月6日、ANSYSはHuaweiの半導体設計子会社HiSiliconとの契約について発表した

発表によるとHiSiliconとANSYSはANSYSの提供するシミュレーション・ツールの利用に関して複数年契約を締結した様子。その中には電源ノイズのサインオフツール「RedHawk-SC」も含まれており、HiSiliconは次世代のパワーインテグリティおよび信頼性サインオフ・ソリューションとして「RedHawk-SC」を使用し、7nmおよび5nmを含む全ての先端プロセスノードの設計を成功させているとの事。HiSiliconの担当者によると、「RedHawk-SC」の最新バージョンは旧バージョンよりも高精度でランタイムは10倍以上高速、メモリ使用量は15分の1に改善されているという。

2018.08.07

2018年8月7日、GloTech Trendsの記事:

マイニングASICの世界Top3である中国企業のBitMain、Canaan、億邦通信がほぼ同時期に香港市場での上場を実現する。Canaan(杭州嘉楠耘智)は既に5月に香港市場へIPO申請を行なっており、億邦通信は6月に香港市場IPO計画を発表。BitMainは今秋にも香港市場に上場する見通しとなっている。

創業5年のBitMain社の2017年末の営業利益水準は、創業25年のNVIDIAの営業利益と匹敵する。同社は5年後に会社の収益の40%をAIチップ製造分野から得られるようビジネスモデルの再構築を模索しており、2016年にAIチップの開発をスタートさせ2017年4月に最初のAIチップ製品を完成している。

2018.08.06

2018年9月12日(水)にDesign Solution Forum 2018(以下、DSF2018)がパシフィコ横浜アネックスホールで開催される。

今年で5回目の開催となるDSF2018では、下記6つのテーマのセッション・トラックにて計45のセッションが実施される予定となっている。

・Software&Test Track

・RISC-V/IoT Track

・Automotive Track

・DeepLearning Track

・SystemC Track

・Armテクノロジー Track

またDSF2018では新たな試みとして、DSF挑戦企画「スタートアップ企業×成熟企業のエンジニアネットワークで新ビジネスを創ろう!」を実施。先端技術領域で活躍するベンチャー企業による講演/展示ゾーンを会場内に用意する。その他にエンジニアにとっての働き方改革について議論する特別企画なども実施される予定。

基調講演は「スタートアップ・マインド - 未来を創る挑戦者になろう、IoT x AI時代の新たなチャンス」というタイトルで、TomyK代表/株式会社ACCESS共同創業者の鎌田 富久氏が行う。

なお今年の6月よりDesign Solution Forumの公式サイトがリニューアルされ、エンジニア向けニュースのキュレーションサイト「News for Engineer」として生まれ変わった。公式サイトを通じて同イベントの「創ろう拡げようエンジニアネットワーク」というコンセプトをネット上でも展開していく。

※DSF2018のプログラム詳細および参加登録は下記URLより。

https://dsforum.eventcloudmix.com/

2018.08.06

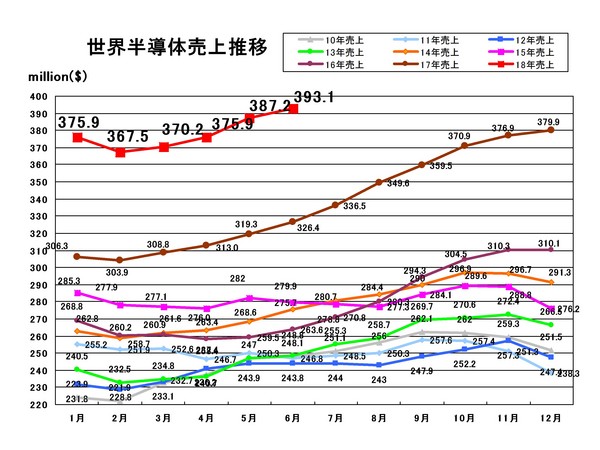

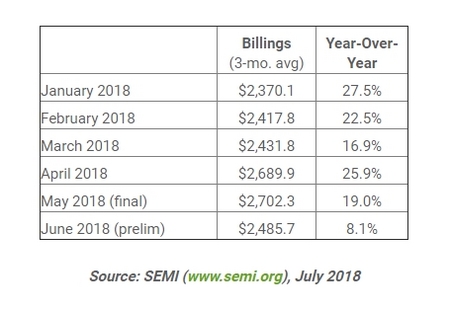

2018年8月3日、米SIA(Semiconductor Industry Association)は、2018年6月の世界半導体売上(3ヶ月移動平均)を発表した。

SIAの報告によると、2018年6月の世界半導体売上は前年同月比20.5%増、前月比1.5%増の393.1億ドルで過去最高。先月に続いて単月売上記録を更新した。単月売上が前年実績を上回るのはこれで23ヶ月連続となる。

四半期単位で見ると、2018年Q2(4-6月)の売上合計額は1179億ドルで前年比20.5%増。半年単位で見ると、2018年上半期(1-6月)の売上合計額は2292億ドルで前年比20.4%となっている。

2018年6月の世界半導体市場を地域別の売上で見ると、中国市場が好調を維持しており5月を上回る前年比30.7%増の135.9億ドルで売上高トップ。北米市場も前年比26.7%増の83.4億ドルと好調だった。全世界的に売上水準は昨年を上回っているが、5月以降、はアジアおよびその他地域の売上高が対前年比1ケタ台の伸びに留まっている。

日本市場の売上は前年比14%増、前月比0.3%増の33.9億ドル。売上を円ベースで換算すると前年比約11.8%増の約3697億円で前月比約0.3%減となる。

2018.08.06

2018年8月5日、DigiTimesの記事:

TSMCは8月3日に発生が確認された同社システムのウイルス感染により工場の操業を一時停止。その影響により2018年第3四半期の売上が約3%減少する見通しである事を発表した。ウイルスによって影響を受けたツールの約80%は既に復旧済で6日には完全復旧の見通し。ウイルスは新しいツールのソフトウェアをインストール中に誤動作が起こり発生、そのツールがTSMCのネットワークに接続されたことで広がった。

2018.08.03

2018年8月2日、MIPI Allianceは新しいフィジカルレイヤ仕様「MIPI A-PHY」について発表した。

「MIPI A-PHY」は自動車業界が求める高速データ・インタフェースに対応するための新仕様でデータ伝送距離は最大15m、データ転送レートは48Gpbs以上を視野に入れている。現在開発が進められている「MIPI A-PHY 1.0」はデータ転送レート12-24Gbpsに対応するもので、2019年後半にリリースされる予定。早ければ2024年には「MIPI A-PHY」を使用した車両が生産される。

「MIPI A-PHY」仕様は、高速データ、制御データ、オプションの電源が同じ物理配線を共有するため、配線、コスト、重量の要件を最適化可能。またその仕様により全体的に複雑さが緩和され、システムコストや消費電力の削減も実現できるという。

2018.08.02

2018年8月1日、AIチップを手掛けるシリコンバレーのベンチャーWave Computingは、Broadcomとの戦略的提携を発表した。

発表によるとWave ComputingとBroadcomの両社は、Waveの次世代データフロー処理ユニット「DPU」を市場投入するために協力。Waveは「DPU」をTSMC 7nmプロセスで製品化する計画でその設計をBroadcomが支援する。Broadcomは既にhigh speed SerDesやHBM PHYなどシリコン実証済のTSMC 7nm向けIP群をリリースしており、同社の実績に裏付けされた設計ノウハウをWaveが活用する格好だ。

Wave Computingの「DPU」は独自のデータフロー技術を用いたAIチップで学習/推論の双方に対応。1チップにプロセッシング・エレメントを16,000個搭載する単一の巨大なプロセッサアレイの構造をとる。

Wave Computingは資金調達額から見ると世の中のAIチップベンチャーのトップランナーの1社と言える存在で、今年6月にMIPS Technologiesの買収を発表し業界を驚かせている。

2018.08.01

2018年7月25日、半導体製造装置を手掛ける米Applied Materialsは、人工知能向けにヒトの脳の働きを模した新型電子スイ ッチの開発をDARPA(アメリカ国防高等研究計画局)から請け負ったことを発表した。

発表によるとApplied MaterialsはARMおよびリサーチ・ファームSymetrixと協働して、同一材料内でデータの保存・処理が可能なCeRAMメモリベースの新しいニューロモーフィックスイッチを開発する計画。このプロジェクトの目標は、現行のデジタル方式ではなくアナログ信号処理を利用して、AIのコンピューティング性能と電力消費効率を大幅に向上させることにある。

同プロジェクトはDARPA ERI(Electronics Resurgence Initiative)のFRANC(Foundations Required for Novel Compute)プログラムのプロジェクトとして実施されるもので、新材料の特性を生かした回路設計とインテグレーションスキームを通じて、データ移動を除外ないし最小化しながらデータ処理を行うという考えを中心に、ノイマン型コンピューターアーキテクチャーをしのぐイノベーションを追求する。

2018.08.01

2018年7月31日、CNET Japanの記事:

マサチューセッツ工科大学の研究チームが半導体チップに実装可能で安価に製造できる分子時計を開発した。硫化カルボニル(OCS)分子を含むガスに高周波(231.060983GHz)を照射してOCS分子を回転させ、その共振状態を基準クロックとして時間計測する。既存のCMOS製造プロセスを使ってLSIに組み込める。1時間当たりの平均誤差は1マイクロ秒未満で精度は小型の原子時計に匹敵。消費電力は66mWと原子時計よりも極めて少ない。研究チームは、この分子時計がスマートフォン用GPSの高精度化につながると考えているという。

2018.07.31

2018年7月30日、Bloombergの記事:

ソフトバンク傘下のArmがデータ分析を手掛ける米Treasure Dataを6億ドルで買収することを発表した。Treasure Dataはカリフォルニア州マウンテンビューに本拠を置き、企業のデータ分析向けの製品を開発しており、自動車、小売、IoT、エンターテイメント業界で使用されている。Armはこの6月にもIoTデバイス管理ソリューションのStream Technologies社の買収を発表している。Armにとって今回の買収は2004年のArtisan買収に次ぐ大型買収となる。

2018.07.31

2018年7月30日、SEMIは2018年Q2(4-6月)の世界シリコン・ウエハ出荷量を発表した。

発表によると2018年Q2の世界シリコン・ウエハ出荷量は、前年比6.1%増、前Q1比2.5%増の計30億1600万平方インチで四半期記録を更新した。

2018.07.30

2018年7月24日、Synopsysは新製品となるSoC向けの設計IP「DesignWare 56G Ethernet PHY IP」の提供開始を発表した。

発表によるとSynopsysの新製品「DesignWare 56G Ethernet PHY IP」は、400Gbpsの伝送能力を持つ超大規模データセンター向けSoCの開発をターゲットとする製品で、以下のような仕様・特長を持つ。

・シリコン実証済みのデータ・コンバータ、コンフィギュラブルなトランスミッタ、DSPベース・レシーバで構成

-開発対象のアプリケーションに対して最適な消費電力/性能バランスを実現

・リーフ&スパイン型ネットワーキング・アーキテクチャで必要になる伝送容量に対応

-10Gから400Gイーサネットのシングル/アグレゲート・リンクレートをサポート

-PAM-4/NRZデータ伝送方式をサポート

・チップ間/バックプレーン/光学および銅ケーブル接続に関してOIF/IEEE規格が定める基準をしのぐ性能

・レシーバーにフル機能のDSPを搭載

-より強固なタイミング・リカバリーと優れたジッター・パフォーマンスを実現

・独自アーキテクチャのPAM-4トランスミッタにより、正確なフィードフォワード・イコライゼーションが優れた伝送特性を実現

・拡張性の高い独自のPHYアーキテクチャ

-次世代の800Gイーサネット・アプリケーションにも対応

「DesignWare 56G Ethernet PHY IP」の16nm/7nm FinFETプロセス・シリコン・デザインキットは、それぞれ2018年Q3、Q4の提供開始を予定している。

2018.07.27

2018年7月26日、Bloombergの記事:

QualcommはNXPの買収を断念せざるを得なくなった。両社の合意で定められた期限までに中国独禁当局から承認が得られなかった。買収予定価格は440億ドル(約4兆8700億円)、破談ならQualcommはNXPに違約金20億ドルを支払うとともに、300億ドル相当の自社株買いを行う計画。中国当局は米国との貿易摩擦の高まりを背景に、承認を先延ばししてきた。

2018.07.26

2018年7月24日、Cadenceは、米DARPA(アメリカ国防高等研究計画局)の研究開発プログラムに採択されたことを発表した。

今回Cadenceが採択されたのは、DARPAのERI(Electronics Resurgence Initiative)が2017年9月に発表した新しい研究開発プログラム「IDEA(Intelligent Design of Electronic Assets)」で、機械学習技術を用いたSoC、SiP、PCBのインテリジェントな統合設計フローの開発を目的としている。

Cadenceは「IDEAプログラム」のゴールに向けて独自の研究開発プログラムを立ち上げ、カーネギーメロン大学やNVIDIAの機械学習エキスパートらと共にインテリジェントな設計フローの実現を目指すという。

2018.07.26

2018年7月24日、SEMIは2018年6月の北米製装置(輸出を含む)の販売高速報値を発表した。

6月の北米製半導体製造装置の販売額は前年比8.1%増の24億8570万ドル。前月比では8%のマイナスだった。販売額20億ドル超えは16ヶ月連続。

2018.07.26

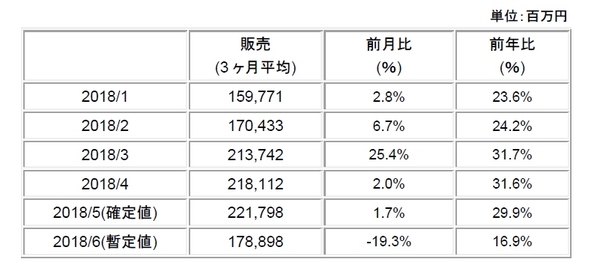

2018年7月19日、日本半導体製造装置協会は2018年6月の半導体製造装置速報値を発表した。

発表によると2018年6月の日本製装置(輸出を含む)の販売高は、前月比19.3%減、前年同月比16.9%増の1788億9800万円だった。例年6月は売上高が落ち込む傾向にあるが今年は特に大きく落ち込んだ。

2018.07.25

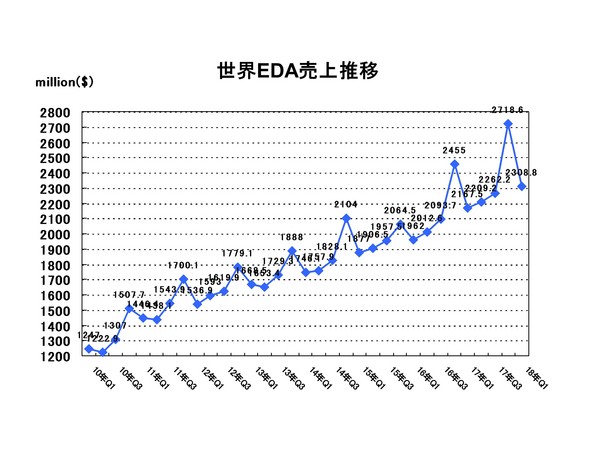

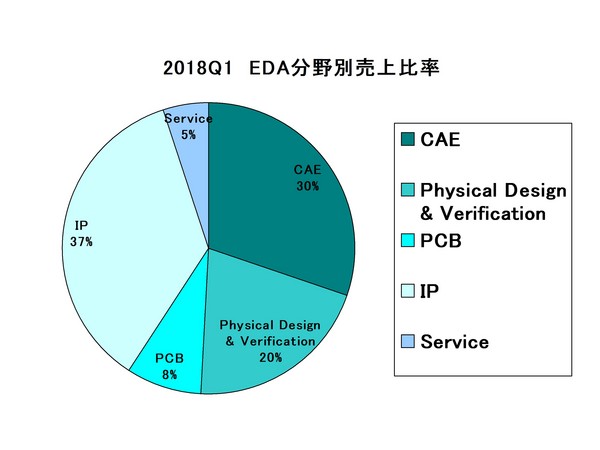

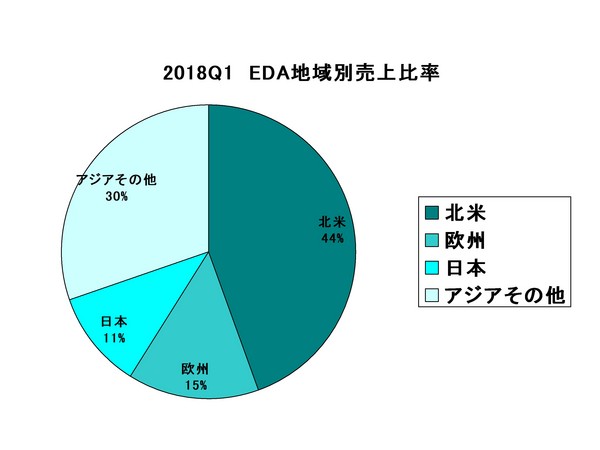

2018年7月24日、米ESD Allianceは、2018年度第1四半期(1月-3月)の世界EDA売上報告を発表した。

ESD Allianceの発表によると、2018年Q1(1-3月)の世界のEDA売上総額は前年比約7.8%増の23億880万ドルで、Q1売上として過去最高を記録した。

2018年Q1のEDA売上をカテゴリ別に見ると、全ての分野で売上が前年実績を上回った。目立って伸びたのはIC Physical Design & Verification分野とPCB/MCM分野で、それぞれ前年比19.3%増、13.8%増だった。

2018年Q1のEDA売上を地域別に見ると全ての地域で売上前年比増を達成。中でも欧州市場は前年比10%増を超える好結果を残した。日本市場の売上については円ベースで換算すると前年比約1.1%増で268億5066万円程度となる。

2018年Q1時点でのEDA業界の従業員数は前年比10.4%増の41,110人で過去最高記録を更新した。

2018年Q1の分野別の売上と昨年同時期との比較は以下の通り。

■CAE分野 6億9970万ドル 2.4%Up

■IC Physical Design & Verification分野 4億7260万ドル 19.3%Up

■IP分野 8億3070万ドル 5.1%Up

■サービス分野 1億1250万ドル 9.7%Up

■PCB/MCM分野 1億9340万ドル 13.8%Up

2018年Q1の地域別の売上と昨年同時期との比較は以下の通り。

■北米 10億2440万ドル 8.4%Up

■欧州 3億3640万ドル 12.4%Up

■日本 2億4810万ドル 5.8%Up

■アジアその他地域 6億9990万ドル 5.4%Up

2018.07.24

2018年7月24日、Cadenceは同社のパワー・インテグリティ解析ツール「Voltus」の機能強化を発表した。

発表によるとCadenceは「Voltus」向けに新たな大規模並列処理オプション「XP (extensively parallel)アルゴリズム」を用意。これは先端プロセス・テクノロジーにおけるパワーグリッドのサインオフ処理に対応するもので、パフォーマンスは最大5倍向上、マシン数百台、CPU数千個での並列処理においてもほぼリニアなスケーラビリティを実現するという。

元々「Voltus」には並列処理機能が備えられており、最大10億インスタンスの大規模デザインに対応していたが、今回の「XPオプション」により更に大規模なギガスケールのデザインに対応可能となった。なお「Voltus」は先日発表されたCadenceのクラウド環境でも利用する事ができる。

発表には「Voltus」のユーザーであるHiSiliconが歓迎のコメントを寄せている。

2018.07.24

2018年7月23日、CNET Japanの記事:

7月23日、Qualcommは新しいアンテナモジュールファミリとしてミリ波対応の「QTM052」と6GHz未満の無線周波数に対応する「QPM56xx」を発表した。同社の「Snapdragon X50 5G」に対応し、スマートフォンに超高速のネットワーク速度をもたらすという。これらのモジュールにより端末メーカーは短距離だが高速なミリ波帯やより信頼性が高いが低速な6GHz未満の帯域など、5G帯の全範囲をカバーすることができる。これらのモジュールは、2018年のうちにモバイルホットスポットに搭載され、2019年上半期にスマートフォンに搭載される見込み。ピーク下り速度は、理論的にはミリ波版で最大5Gbpsにものぼるが、スマートフォンで1.4Gbps近く。

2018.07.24

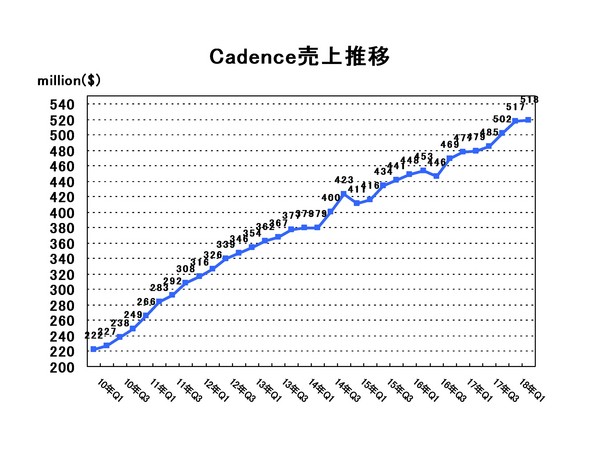

2018年7月23日、Cadenceは、2018会計年度第2四半期(2018年4-6月)の売上を報告した。

Cadenceの2018年Q2売上は、前期Q1比約0.2%増の5億1800万ドルでまたしても四半期売上記録を更新した。四半期売上記録の更新はこれで7四半期連続となる。営業利益は7500万ドルとQ1実績をわずかに上回った。(※GAAP基準による会計結果)会計ルールが異なるが前年実績と比較すると売上は前年比約8.1%増、営業利益は前年比約8.7%増となる。Cadenceは2018会計年度決算報告から収益算出ルールを変更した。

Cadenceは、2018会計年度Q3の売上額を5億1000-2000万ドルと予測している。

2018.07.23

2018年7月18日、Cadenceは各種イメージングソフトウェアを手掛ける米ArcSoftとの協業事例を発表した。

発表によるとArcSoftとCadenceは協業によりArcSoftのビューティーショット、HDR、bokeh(ボケ)、顔認証アプリケーションをCadenceの「Vision P6 DSP」に移植。「Vision P6 DSP」を利用する事で各アプリの高性能化、低消費電力化に成功した。例えば「Vision P6 DSP」の高度なビジョンおよびAI技術によってカメラ1つでbokehが使用可能となり、低消費電力化だけでなく低コスト化も実現。HDのパフォーマンスはCPUとの比較で6倍向上できた。共同開発された同ソリューションは世界的大手のアプリケーション・プロセッサーに組み込まれ、市販のスマートフォンで利用されているという。

なおCadenceによると「Vision P6 DSP」は、モバイル向けアプリケーション・プロセッサーのトップベンダー5社のうち2社に採用されているという話だ。

2018.07.21

2018年7月20日、DigiTimesの記事:

TSMCは2018年の売上成長率の予測をこれまでのプラス10%からプラス5-9%に下方修正した。マイニングチップの需要後退が要因。売上の内訳としてはスマートフォン部門の売上が減る一方でHPC部門の売上は伸びる見通し。設備投資については最低投資額を115億ドルから110億ドルに修正。先端ノード向けの新しい機器の設置を2019年に延期する。TSMCは今月から量産を開始した7nmチップの売上は2019年に売上全体の20%以上を占めると予測している。

2018.07.21

2018年7月20日、東芝メモリはQLC技術を用いた96層積層プロセスの「BiCS FLASH™」を試作した事を発表した。

東芝はこれまでTLC(3ビット/セル)96層積層プロセスの「BiCS FLASH™」やQLC(4ビット/セル)64層積層プロセスの「BiCS FLASH™」の開発に成功しているが、96層積層プロセスを適用したQLC製品の試作は今回が初。試作した製品は1チップあたり1.33テラビットの業界最大容量を実現。更に1.33テラビットのチップをひとつのパッケージに16段積層することで2.66テラバイトの大容量を実現することが可能だという。同製品は9月上旬からサンプル提供を開始し2019年に量産開始の予定。

2018.07.21

2018年7月20日、東芝メモリはQLC技術を用いた96層積層プロセスの「BiCS FLASH™」を試作した事を発表した。

東芝はこれまでTLC(3ビット/セル)96層積層プロセスの「BiCS FLASH™」やQLC(4ビット/セル)64層積層プロセスの「BiCS FLASH™」の開発に成功しているが、96層積層プロセスを適用したQLC製品の試作は今回が初。試作した製品は1チップあたり1.33テラビットの業界最大容量を実現。更に1.33テラビットのチップをひとつのパッケージに16段積層することで2.66テラバイトの大容量を実現することが可能だという。同製品は9月上旬からサンプル提供を開始し2019年に量産開始の予定。

2018.07.20

2018年7月19日、DigiTimesの記事:

Bitcoinマイニング用ASICのサプライヤBitmainは、遅くとも2019年初頭に香港でIPOを開始する予定であり、IPOによる10億ドルの資金調達を見込んでいる。Bitmainは7月初めに投資家から3?4億ドルの資金調達を完了しており、同社の評価額は140億ドルに拡大。IPOが成功すれば評価額は150億ドルに引き上がる。

Bitmainの2017年売上は25億ドル。Bitmainは先行き不透明なBitcoin市場を背景にAIチップ市場への参入を昨年発表しているが、2018年Q1の売上は18億7000万ドルとかなりの実績を残している。

2018.07.19

2018年7月18日、IC Insightsの記事:

2018年に電子システムで使用される半導体コストが過去最高になる。電子システム市場の売上に対する半導体市場の売上比率は今年過去最高の31.4%に到達。今後数年間は30%以上を維持すると見られている。今年30%超えとなる大きな要因はメモリで使用される量と価格の両面で影響を及ぼしている。

2018.07.19

2018年7月18日、Fudzillaの記事:

Texas InstrumentsのCEOが同社の行動規範規則の違反で辞任した。詳細については不明。ここのところ半導体業界においても同種の辞任劇が連続している。6月にIntelのCEOとRambusのCEOが辞任している。

2018.07.19

2018年7月17日、Xilinxは、ディープラーニング推論プラットフォームを手掛ける中国DeePhi Technology社を買収した事を発表した。

DeePhi Techは2016年に中国清華大学と米スタンフォード大学の研究者によって設立された機械学習ソリューションのベンチャーで、エッジおよびクラウド向けの各種ディープラーニング推論アクセラレータ・モジュールを提供。そのコア技術は「DeePhi DPU™」と呼ぶ独自のDeep Learning Processing Unitで同技術はMediaTek, Amazon, Samsungといった大手に採用されている。DeePhiの推論アクセラレータはXilinxのFPGAで実装されており、Xilinxは早くからDeePhi Techに出資していた。(MediaTekやSamsungもDeePhi Techに出資している。)

今回の買収に関する取引条件等は明らかにされていないが、DeePhi Techの200名を超える従業員はXilinxの従業員として引き続き北京オフィスで活動を続ける。XilinxはDeePhi Techへの投資を継続し、クラウドおよびエッジにおける機械学習アプリケーションの導入を進めていくとしている。

2018.07.18

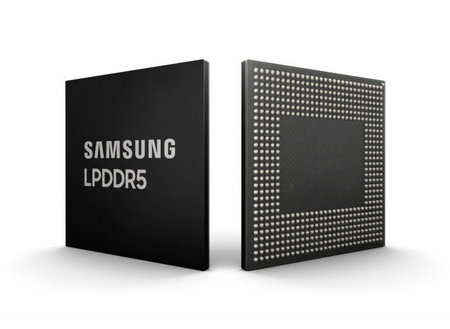

2018年7月17日、Samsung Semiconductorは、業界初となる10nmクラスの8Gb LPDDR5 DRAMを開発した事を発表した。

Samsungの発表によると、新しい「8Gb LPDDR5」のデータレートは既存のフラッグシップ製品「LPDDR4X」の1.5倍の最大6,400Mb/sで1秒間に51.2GBのデータを送信可能。動作電圧1.1V(6,400Mb/s)および1.05V(5,500Mb/s)の2つの帯域幅で利用できる。また、低消費電力機能としてアプリケーション・プロセッサの動作速度に応じて電圧を下げるアクティブモード、既存の「LPDDR4X」のアイドルモードの約半分に電力消費量を削減するディープスリープモードを提供。最大30%の消費電力を削減するという。

これら新しい「8Gb LPDDR5」のパフォーマンス向上は、DRAMセル内のメモリバンクの数を8から16に変更することや、チップの超高速性能を検証し保証する速度最適化回路アーキテクチャを使用することなどにより実現されているという話。

なお、今回発表された「8Gb LPDDR5」は未だプロトタイプの機能テストと検証が完了した段階で、量産開始時期は発表されていない。

2018.07.17

2018年7月16日、Bloombergの記事:

Amazonのクラウド事業部門Amazon Web Serviceがスイッチ機器市場への参入を計画しているという報道を受け、13日の米株式市場でCiscoやJuniperなどネットワーク機器関連の銘柄が下落した。AWSはいわゆるホワイトボックス・スイッチの価格を互換性のあるCisco製品よりも70?80%低い水準に設定する見込みで、JuniperやAristaなど既存のメーカーにとって手ごわいライバルになり得る。

2018.07.13

2018年7月12日、Cadenceはロームによる「Cadence® Automotive Solution」の採用事例を発表した。

発表によるとロームは車載LSI製品の開発フローにCadenceのAutomotive Solutionを採用。具体的には車載LSIの安全性検証にCadenceの検証プラットフォーム「Insicive」の故障注入シミュレーション技術を導入した。同ロームのフローは第三者認証機関テュフ ラインランドによる機能安全規格ISO 26262 ASIL D認証を取得しており、2018年に改定される予定のISO 26262第2版準拠への対応も考慮しているという。

ロームによるとCadenceのAutomotive Solutionは、既存のテストベンチ、デザイン、デバッグ環境を再利用した故障注入シミュレーションが可能で、検証プロセスを大幅に効率化することができるとの事。ロームの事例に関する詳細は、7月20日に開催されるCadenceのセミナーイベント「CDNLive Japan 2018」で発表される予定。

2018.07.13

2018年7月12日、ZDNetの記事:

IntelはeASICを買収しプログラマブル・ソリューショングループを強化すると発表した。Intelは、Intel FPGAとeASICのストラクチャードASICをシステムインパッケージ・ソリューションで組み合わせ、Intelのエンベデッド・マルチダイ相互接続ブリッジ(EMIB)技術を活用した新しいクラスのプログラマブル・チップの設計を計画しているという。

eASICは1999年設立のファブレス半導体ベンダで社員120名、本社はサンタクララ。同社のストラクチャードASICは、たった一つのマスクレイヤのカスタマイズで配線が可能。ASICよりも短期間、低コストでFPGAよりも消費電力の低いチップを開発できる。

2018.07.13

2018年7月10日、TheRegisterの記事:

Armは6月末にWebサイト「riscv-basics.com」を立ち上げ、競合するプロセッサー・アーキテクチャー「RISC-V」を攻撃する情報を発信した。しかし、社員の反対などもあり数日後にはサイトを閉鎖した。

2018.07.13

2018年7月13日、Bloombergの記事:

米Broadcomの株価が12日の米株式市場で上場来最大の下げとなった。企業向けソフトウェアを手掛けるCA Technologiesを189億ドル(約2兆1200億円)で買収するの発表に、戦略ないし財務上の根拠が見いだせないと当惑する声がアナリストから相次いだ。

CA Technologiesの買収は全く異なるエレクトロニクス分野への参入を意味し、タンCEOが刷新に貢献した半導体業界との主な重複はない。