Synopsysが組み込み向けハイエンド・プロセッサの新製品「ARC HS」ファミリを発表

2013年11月6日、Synopsysは、同社のプロセッサ・コアの新製品「DesignWare ARC HS」ファミリを発表した。

Synopsysの発表によると、新製品「DesignWare ARC HS」ファミリは同社ARCプロセッサ・コアの中で最も高性能な32ビット・プロセッサで、標準的な28nmプロセスでの実装で最高2.2GHzで動作し4200DMIPSの性能を実現。パフォーマンスもさることながら、85ミリワット以下という低消費電力と0.15mm2という小面積(※標準的28nmプロセスにおいて)を実現しており、既に同ファミリ最初の製品として「ARC HS34」および「ARC HS36」がリリースされている。

「DesignWare ARC HS」ファミリは、既存の「ARC 700」ファミリを上回る10段パイプラインの新アーキテクチャ(ARCv2)で実現されており、「ARC HS34」と「ARC HS36」の違いは命令及びデータ用キャッシュの有無のみ。いずれの製品もクローズリー・カップルド・メモリーが備えられているほか、レジスタ・ファイルをI/Oに直接マッピングする仕掛けや、パイプラインの後段にALUを配置する仕掛けなどパフォーマンス向上のための機能が用意されており、信頼性向上のためのオプションとして、内蔵メモリに対するECC機能の追加も可能となっている。

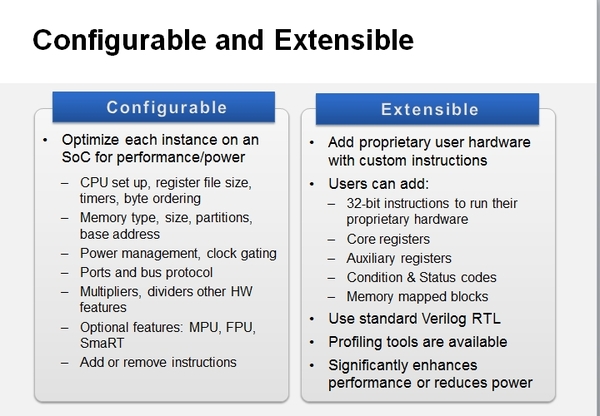

開発にあたっては、Verilog-HDLのRTLで追加命令を記述可能で、用意されているプロファイリング用のツール「MetaWare」でボトルネックを解析し命令追加を検討できる。追加した命令はそのままCコンパイラで利用可能。プロファイリングは、開発環境「ARChitect」からコンフィギュレーションに応じて出力されるISS「xCAM」を用いて行うが、当然この「xCAM」も追加命令に対応する。また、ISSと合わせてSystemC環境で利用できる高速シミュレーション用のモデル「nSIM」も出力される。

※画像は全てSynopsys提供のデータ

「DesignWare ARC HS」ファミリのターゲットとしては、従来製品で実績のあるSSDやモバイル機器、メディアプレーヤーやデジカメ、デジタルTVなどのデジタル家電製品の他に、今後ネットに繋がる白モノ家電や車載分野、FA分野なども視野に入っており、競合製品を上回る性能、消費電力、実装面積で更に市場を開拓していく構えだ。

尚、SynopsysはARMとの強固なパートナーシップから、ARMプロセッサを競合と見るつもりは無いようで、Cadenceが買収したTensilicaあたりを競合製品と見ている様子。しかし既に組み込みプロセッサの市場シェアでは、ARMに次いでARCコアが19%のシェアを握っているという事で、主なところではSSDコントローラ、デジタルTVチューナー、ミドル/ローレンジのデジカメなどの他、PCチップセット向けとしての利用も多く、一般的なノートPCには平均して8-10個のARCコアが使用されているという事だ。

= EDA EXPRESS 菰田 浩 =

(2013.11.07

)