CadenceがARM搭載SoCのインターコネクトの性能解析をサイクル精度で行うツール環境を発表

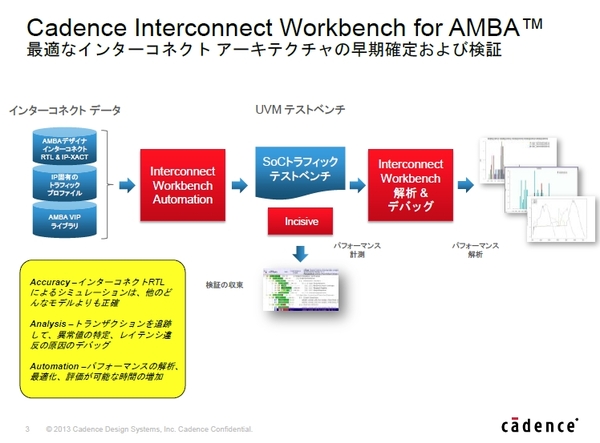

2013年10月30日、CadenceはARM搭載SoCの性能解析をターゲットとした新製品「Interconnect Workbench」のリリースを発表した。

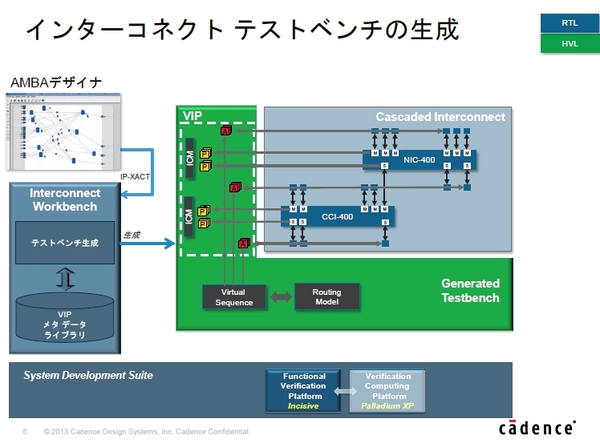

Cadenceによると、「Interconnect Workbench」は、ARM搭載SoCのインターコネクトの性能解析をサイクル精度で実現するEDAツールで、具体的にはARMのインターコネクトIP「CoreLink CCI-400、NIC-400、NIC-301、ADB-400」を搭載したSoCをターゲットに、インターコネクトの性能解析用のテストベンチを自動生成することができる。

実はこの「Interconnect Workbench」は、以前からCadenceのセミナーやイベント等で紹介されていたソリューションで、今年4月に開催された「MemCon Japan 2013」においても「ARMベースSoCのインターコネクトおよびメモリサブシステムのRTL性能解析によるアーキテクチャ探索」と題した日本ケイデンスの講演で紹介されていた。

当時の講演で聴いた説明によると、「Interconnect Workbench」はARMの純正システムIP設計環境「AMBA Designer」が生成するインターコネクトのRTLをターゲットにテストベンチを生成。テストベンチは、「AMBA Designer」から出力されるRTLのIP-XACT記述とIP固有のトラフィック・プロファイル、AMBA VIPメタ・データ・ライブラリから自動生成される。今回の発表によると、テストベンチはCadenceの「Interconnect Validator(インターコネクトの検証IP)」とAMBA検証IP一式を組み込んだ生成されるようだ。

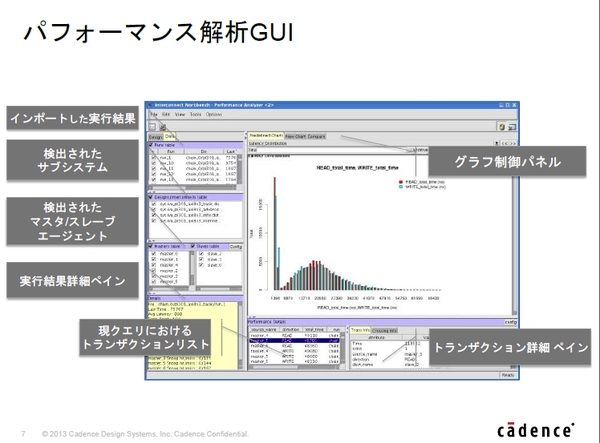

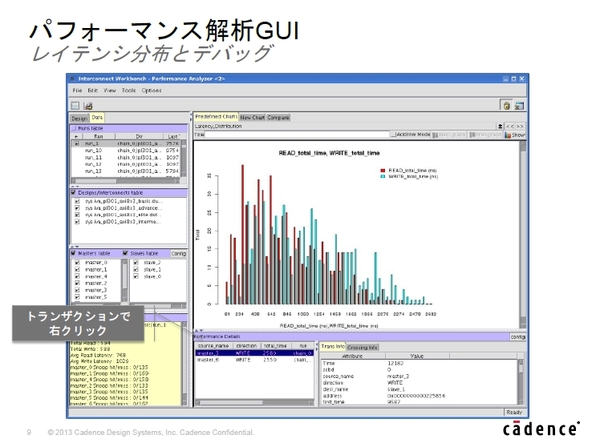

「Interconnect Workbench」で生成したテストベンチを用いたシミュレーション結果は、専用のパフォーマンス解析GUIでトランザクション・ベースのパフォーマンスの解析とデバッグが可能。レイテンシ分布の解析やトランザクションの追跡による異常値の特定やレイテンシ違反の原因のデバッグが可能だという。

Cadenceは「Interconnect Workbench」を用いることで、テスト環境構築の工数を減らせるだけでなく、サイクル精度のシミュレーションによって様々なアーキテクチャの性能検証を様々なシナリオで実現できると主張する。

※画像は全てCadence提供のデータ(MemCon Japan 2013日本ケイデンス講演データ)

= EDA EXPRESS 菰田 浩 =

(2013.10.31

)