【DAC50】6/2よりオースティンで第50回Design Automation Conference開催

2013年6月2日より、テキサス州オースティンにて第50回Design Automation Conferenceが開催される。

50回という節目となる今年のDACの開催地オースティンは、半導体関連の企業が多数集まる土地で、半導体売上トップのIntel、2位のSamsungをはじめ、IBM、Freescale、Apple、AMDなどの大手が数千人単位でハード設計/検証エンジニアを抱えており、その数は3万人以上にのぼると言われている。(※WebサイトDeepChipの記事データ参照)

主催者の発表によると、今年の50回DACで採択された論文数は計158本。ベスト・ペーパー候補となっているのは下記8本の論文。今年も昨年に続いてESS関連(組込みシステムおよびソフトウェア関連)の論文が多く、採択された論文の35%はESS関連。ワークショップ、チュートリアル、スペシャル・セッションなどにおいてもESS関連のものが含まれており、カンファレンスにおけるESSの取り込みは継続されている。

・ベスト・ペーパー候補の論文タイトル

-Aging-Aware Compiler-Directed VLIW Assignment for GPGPU Architectures

-An ATE Assisted DFD Technique for Volume Diagnosis of Scan Chains

-Proactive Circuit Allocation in Multiplane NoCs

-A High-Level Synthesis Flow for the Implementation of Iterative Stencil Loop Algorithms on FPGA Devices

-ABCD-L: Approximating Continuous Linear Systems Using Boolean Models

-Scalable Vectorless Power Grid Current Integrity Verification

-Spacer-Is-Dielectric-Compliant Detailed Routing for Self-Aligned Double Patterning Lithography

-Rapid Exploration of Processing and Design Guidelines to Overcome Carbon Nanotube Variations

今年のキーノートには、Freescale, National Instruments, Samsung, Qualcomm, TI, UC Berkeleyからのスピーカーが登壇。FreescaleはIoT(Internet of Things)分野、Samsung, Qualcomm, TIはモバイル分野の話をする予定で、初日はNational InstrumentsのCEOから、そして最終日は業界の重鎮であるUC BerkeleyのAlberto Sangiovanni-Vincentelli氏から、DAC50周年にふさわしいEDAと設計コミュニティの進むべき未来について語られる予定となっている。

また今年は、「Sky Talk」というテクニカル・セッションの新カテゴリが設けられ、Barcelona Supercomputing Center, Cadence, DARPA, D.E. Shaw Research, IBM, NVIDIAおよびStanford Universityより計6講演、30分間のショート・キーノートが行われる。

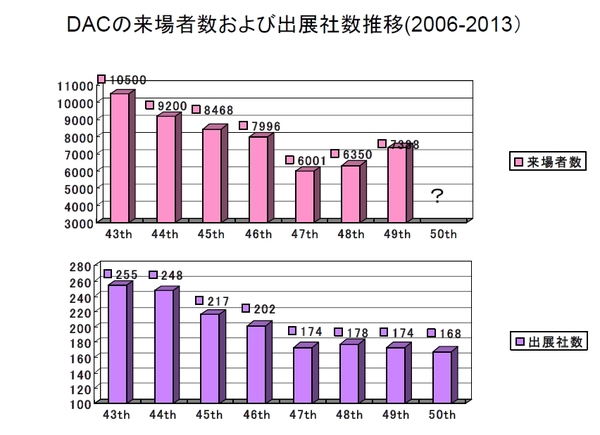

今回のDACには展示会の出展企業が175社という事だが、重複を除いた実数は168社で昨年より微減。(EDA-EX調べ)うち、実質的に初出展となる企業は計21社で昨年と同数。ちなみに日本からの出展は、TOOLおよびジーダットの2社で毎年出展していたNECは今年はAldecのブースにパートナーとして参加するという。

DACの来場者数は昨年7388人を数え2年連続で上昇に転じたが、今年はどう推移するか予測するのは難しいところ。上述したように設計者の多い土地柄であり、DAC50週年記念という事でカンファレンス自体、様々な企画に力が入っているのがプラス要因と言えるが、シリコンバレーを離れた開催地では集客数が減るという傾向もあり、どの程度人が集まるかは蓋を空けてみないと分からない。

但し、ただ一つ高い確度で言えるのは、日本からの参加者は過去最低の数十名程度であろうという事。かつては大手企業1社から20名以上のエンジニアをDACに送り込むような時期もあったが、今年は大手レベルでも各社から数名程度の参加で、中には人を出さない企業もある。これは国内の半導体業界の現状を表したものと思われるが、国内の設計スタイルが時代に取り残された悪い意味での「ガラパゴス設計」とならないよう願いたい。

今年のDACの展示会で注目したいのは、やはり各社の新製品で、DACでのアピールを狙いEDA各社が直近発表した新製品としては、以下の様な製品がある。

・Forte 高位合成ツール「Cynthesizer 5」

・Oasys Design Systems 等価性検証ツール「Oasys RealTime Parallel EC (equivalency checking)」

・Oasys Design Systems フロアプラン自動生成ツール「Floorplan Compiler」

・Aldec 設計要求管理ツール「Spec-TRACER」

・Cadence タイミング解析ツール「Tempus」

・Jasper Design Automation 複数パワードメイン対応のフォーマル検証ツール「JasperGold(R) Low Power Verification App」

・Sage Design Automation DRCデック開発自動支援するツール「iDRM (integrated design rule management)」

・OneSpin Solutions クラウドベースのフォーマル検証ソリューション

・Real IntentおよびDeFacTo CDC検証とDFTソリューションを組み合わせたRTLサインオフ・フロー

・Berkeley Design Automation アナログ・キャラクタライゼーション環境「ACE」

・Berkeley Design Automation メモリ・CMOSイメージ・センサー向けSPICE 「Analog FastSPICE Mega」

・Intel ESLツール「CoFluent Studio」※高位合成ツール向けのSystemCコードを出力機能

・ジーダット 先端アナログプロセス向け回路・レイアウト自動生成ツール「Anchor/TXA 」および「Anchor/RVT」

・G-Analog Design Automation GPUベースのキャラクタライゼーション・ツール「GChar」

尚、毎年恒例となっているGary Smith EDA社の「DAC要チェックリスト2013年版」は既に公開済みで、計34社がリストアップされている。これらリストに挙げられた企業

の製品については、Gary Smith氏の月曜日のセッション「Gary Smith on EDA: Trends and What's Hot at DAC」にてトレンド解説と合わせて紹介されるだろう。ちなみに、日本のEDAベンダ、ジーダットは昨年に続き今年も同リストにリストアップされている。

の製品については、Gary Smith氏の月曜日のセッション「Gary Smith on EDA: Trends and What's Hot at DAC」にてトレンド解説と合わせて紹介されるだろう。ちなみに、日本のEDAベンダ、ジーダットは昨年に続き今年も同リストにリストアップされている。

また、今年はEDA関連情報サイト「SemiWiki」においても、「SemiWiki Top 10 Must See @ #50DAC List!」として10の製品が紹介されている。 その他、業界の辛口評論家John Cooley氏のサイト「DeepCHIP」でも恒例の注目製品の紹介記事が発表されるだろう。

当サイトでは、50回DACの現地の状況を取り急ぎTwitterで配信するほか、各種レポート記事を順次アップしていく予定です。

= EDA EXPRESS 菰田 浩 =

(2013.05.31

)