AldecがASIC/FPGA設計における設計要求を管理・追跡するツール「Spec-TRACER」を発表

2013年5月20日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、新製品「Spec-TRACER」を発表した。

発表によると「Spec-TRACER」は、ASIC/FPGA設計における設計要求を管理・追跡するツールで、設計に対する要求を取り込み、それら要求がどのようにハードウェアに実装・テストされているかを管理、分析、追跡、レポートする事が可能。これら機能をWindowsベースのAldecのHDL設計ツールやシミュレータと統合することができる。

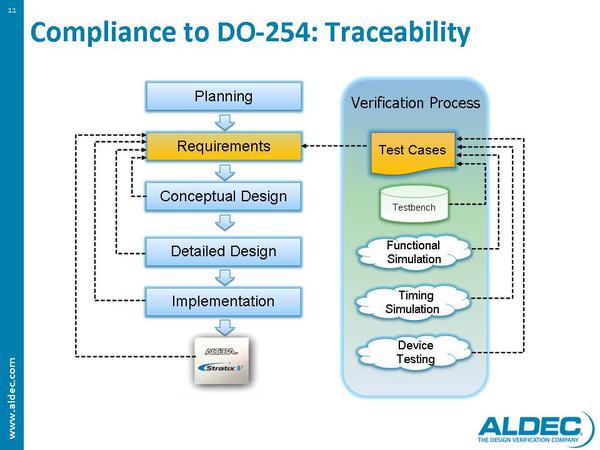

近年、航空宇宙業界、自動車業界をはじめ様々な業界において安全基準の認証規格に関する要求が高まっており、組込みソフトウェアの開発と同じようにハードウェア設計においても、その開発過程、要求の実装経路などを明確にし、管理、ドキュメント化する事が求められるようになってきている。

今回Aldecが発表した「Spec-TRACER」はそのような要求に対応するツールで、ハードウェア設計におけるトレーサビリティ管理を実現。要求仕様をインポートし 、デザインおよびテストに対して各要求がどのように実装されているかをキャプチャ。要求仕様の変更の影響分析や要求カバレッジ分析なども可能で、トレーサビリティレポートを自動生成する事ができる。

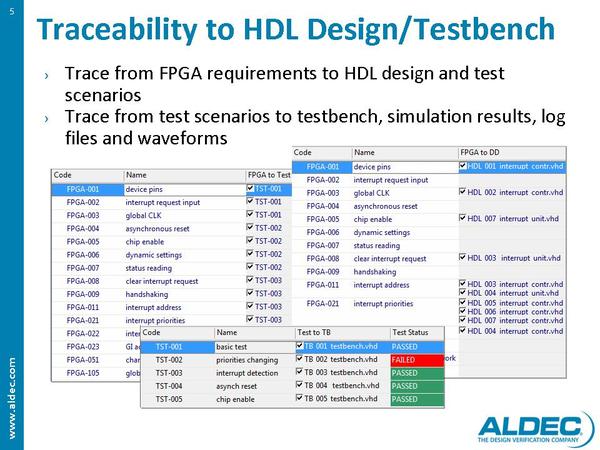

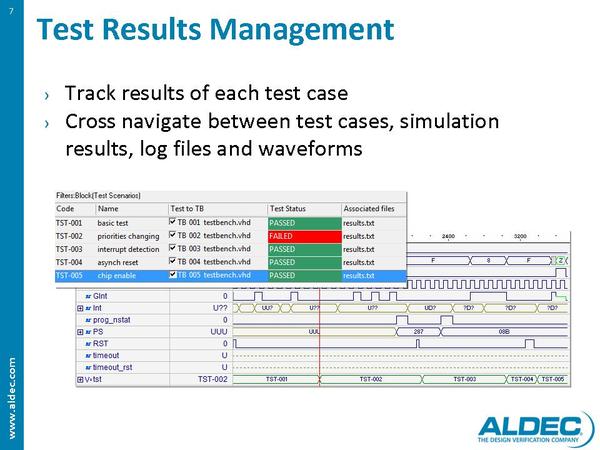

ハードウェア設計においては、設計の要求仕様がどのようにHDLコードやテスト・シナリオに実装されているかを管理・追跡できるほか、テスト・シナリオからテストベンチ、シミュレーション結果へのトレースも可能。それら関係性をナビゲートしてくれる機能もある。

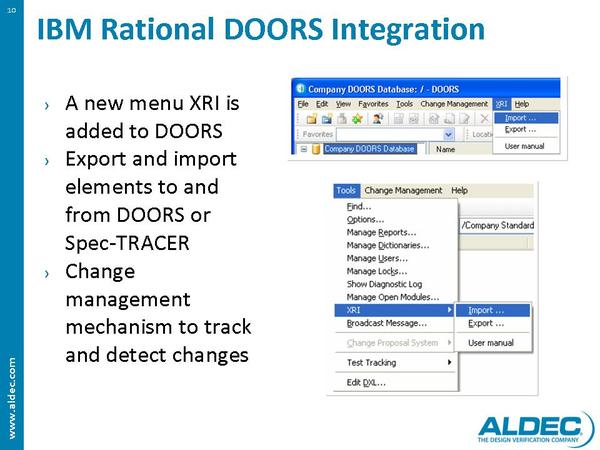

尚、「Spec-TRACER」は、IBMの提供する組込みソフト開発向けの要求管理ツール「Rational DOORS」とのインテグレーションを実現しており、ツール間で相互に要求仕様のインポート/エクスポートが可能。認証規格としては航空宇宙業界の「DO-254」に準拠した要求トレーサビリティをサポートしている。

※画像は全てAldec提供のデータ

= EDA EXPRESS 菰田 浩 =

(2013.05.22

)