Xilinx、設計環境「Vivado」にシステムレベルのIPインテグレーション機能を追加

2013年4月4日、Xilinxは、同社の設計環境「Vivado Design Suite」のバージョンアップを発表した。

発表によると今回のバージョン・アップによる機能向上は大きく2つ。

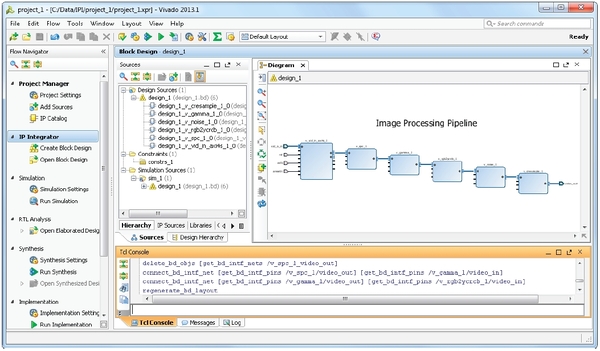

まず、昨年6月の「Vivado」発表時点からロードマップに掲げていた、システムレベルのIPインテグレーション機能「IP Integrator」を実装した。同機能はTCLベースの対話型の環境で、デザインにおけるIPブロックのインテグレーションを容易化するもの。グラフィカルな環境上でARM AXIバスなど主要なインタフェースにIPを自動接続する事が可能なほか、 IPサブシステムの構築、複雑なIPインタフェースを含むシステムのDRC検証、IPインタフェースのトレードオフ、デバッグなど、インタフェース・レベルでのIPベース・システム設計機能を一通り包含しており、新規アルゴリスムやIP、RTL資産などをベースに組み上げたシステムを「Vivado」、「Vivado HLS」、「System Generator」を用いてそのままFPGAに実装する事ができる。

「IP Integrator」によるIPの接続は信号レベルではなく、インタフェース・レベルでの接続で、IPのパラメーターは自動的に設定および伝搬される仕組み。また、「IP Integrator」は、プロセッサ・ベースであるか否かに関わらずデザイン作成が可能で、作成したIPサブシステムを再利用する事も可能となっている。

※画像はIP IntegratorのGUI画面。Xilinx社Web上のブローシャから抜粋。

この「IP Integrator」は、メタデータの記述フォーマットIEEE 1685(IP-XACT)標準の技術を用いた機能で、ユーザーは「IP Packager」と呼ばれる機能を用いて、HDLで記述されたRTL、C/C++/SystemCモデル、MATLAB/Simulinkのアルゴリズム・モデルをパッケージ化し「IP Integrator」で使用する事が可能。それらパッケージ化されたIPは「IP Catalog」と呼ばれるレポジトリ機能で登録・管理することができ、FPGA設計用のデザイン・ライブラリとして共有できる。

今回追加された「IP Integrator」は、高位合成機能「Vivado HLS」と合わせて、より複雑化、大規模化、IPベース化するFPGAデザインの抽象度をシステム・レベルに引き上げるもので、Xilinxは設計生産性を4倍向上と謳うが、設計の効率面だけでなくFPGA設計における社内の資産管理などの面においてもその利用効果は高いと思われる。

今回のバージョンアップのもう一つの目玉は、高位合成機能「Vivado HLS」のライブラリ拡張で、Xilinxは「Vivado HLS」の合成用のライブラリとして新たに浮動小数点演算「math.h」とリアルタイム・ビデオ・プロセッシング機能を追加した。ユーザーはこれらライブラリを用いる事でビデオ・プロセッシング・アプリケーションの開発とそのパフォーマンスを同時に加速できるようになる。

かつてXilinxは、各種アライアンスなどを通じて社外のEDAベンダとの連携により自社FPGAの開発環境を拡充する戦略を展開していたが、その後独自の環境構築強化に方針を変更。結果的にこの判断が「Vivado」の開発に繋がり、SoC/ASIC開発の世界で理想とされる、高い抽象レベルでのIPベースのシステム設計とその実装を実現するに至っている。

= EDA EXPRESS 菰田 浩 =

(2013.04.08

)