Aldecが低コストのVirtex-7搭載ボード「HES-7」でASICプロトタイピング市場に参入

2012年9月17日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、新製品「HES-7」を発表しASICプロトタイピング市場への参入を表明した。

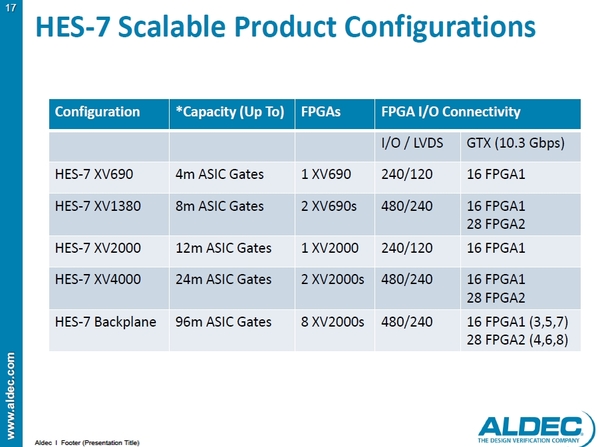

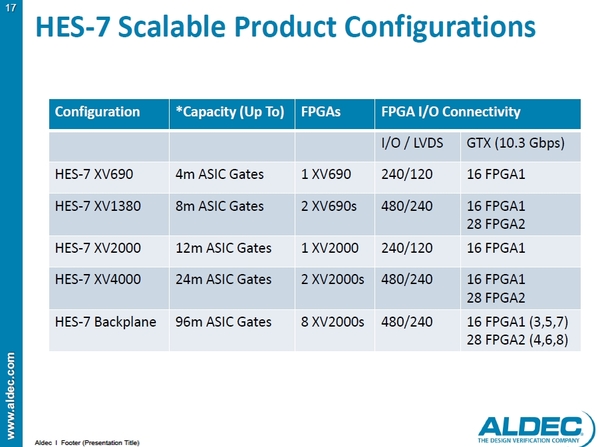

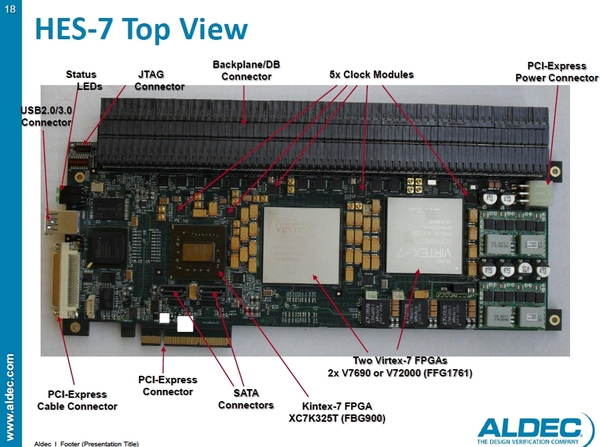

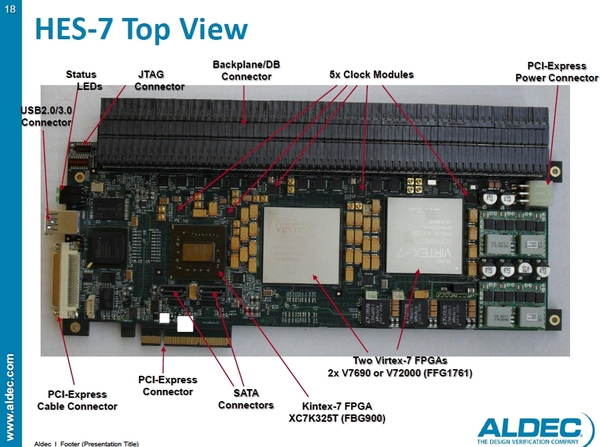

Aldecの新製品「HES-7」は、Xilinxの28nmFPGA「Virtex-7」を搭載するASICプロトタイピング用のFPGAボードで、製品のラインナップは「Virtex-7 690T」を1個または2個搭載するタイプと、Xilinx最大規模の「Virtex-7 2000T」を1個または2個搭載するタイプで計4種類。「Virtex-7 2000T」を2個搭載するタイプは最大400万FPGAロジックセル(実質2400万ASICゲート相当)のデザイン容量を誇り、更に同ボードを4枚繋げて9600万ASICゲートまで対応できる。

※画像はAldecの提供資料

「HES-7」へのデザインのインプリメンテーションは、Xilinxの環境「ISE」または「Vivado」を利用し、特に「HES-7」専用の環境を必要としない。また、デバッグ環境も同様でDesignerはXilinxの「ChipScope」を使ってデザインのデバッグを行う形となる。

AldecのVice PresidentであるDavid Rinehart氏によると、「HES-7」は高価なASICプロトタイピング製品をより低価格かつ身近なものにするというコンセプトで開発された製品で、運用面でもシンプルに顧客のユーザビリティを追求。例えば、「HES-7」のインタフェースとして独自仕様ではない高速バックプレーンコネクタ「Molex」を採用しており、これにより顧客はカスタム・ドーターボード等による拡張が容易に可能。Aldecはそのパフォーマンスと供給体制から「Molex」を採用しており、公開されている「Molex」の仕様は誰でもアクセスできる。

※画像はAldecの提供資料

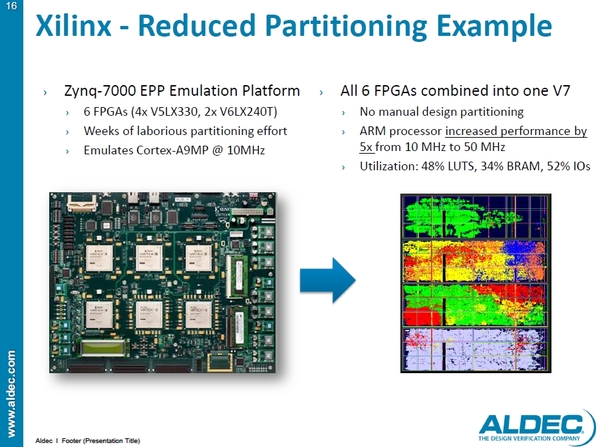

そして何よりもDavid Rinehart氏が強調するのは、「HES-7」を使えばデザインのパーティショニングを無くし、デザインの実装時間短縮とパフォーマンス向上の両方を実現できるという点。現在、市販されている一般的なプロトタイピング・ボードには、通常4?6個の旧世代FPGAが搭載されているが、そこにデザインを実装しようとすると当然ながらデザインの分割作業が必要となる。通常、そのような分割作業は専用ツールで自動処理されるが、それによってパフォーマンスに悪影響を及ぼす事がある。「HES-7」の場合は、大規模FPGAを搭載しているため、デザインを分割することなくダイレクトなインプリメントが可能。複数FPGAを利用する場合は人手作業で分割することになるが、その分割作業は粒度が大きく難易な作業ではないという。

※画像はAldecの提供資料

尚、新製品「HES-7」は既に出荷が開始されており、その価格は最も小さな400万ASIC規模のボードで199万9500円からと市販製品の水準を大きく下回る。また、全ての商品にで1年間の品質保証がつくとの事。David Rinehart氏によると、今後はソフトウェア開発のニーズを意識して各社バーチャル・プラットフォームと「HES-7」の連携に力を入れていくという事だ。

※画像の人物はAldecのDavid Rinehart氏

= EDA EXPRESS 菰田 浩 =

(2012.09.18

)