Synopsysが6種のチップ間接続プロトコル仕様に対応する業界初の28nmマルチギアMIPI M-PHY IPを開発

2012年2月29日、Synopsysは、新しい「DesignWare MIPI M-PHY IP」ソリューションを発表した。

今回Synopsysが発表した「DesignWare MIPI M-PHY IP」は、既存の「DesignWare MIPI M-PHY IP」をベースに開発した製品でMIPI Alliance M-PHY v1.0仕様に準拠。下記6種のチップ間接続プロトコル仕様をサポートしているほか、複数の伝送スピード・ギアを備えている。

・JEDEC Universal Flash Storage(UFS)

・USB SuperSpeed Inter-Chip(SSIC)

・MIPI LLI(Low Latency Interface)

・MIPI DigRF v4(data interface between the RFIC and the BBIC)、

・MIPI CSI-3(camera serial interface) ※今後仕様が確定

・MIPI DSI-2(display serial interface) ※今後仕様が確定

同IPによりモバイル向けICの相互接続手段としてMIPIインタフェースを利用し易くなり、アプリケーションに応じて異なるプロトコル間のインターフェイスを複数の伝送スピードを実現可能となる。

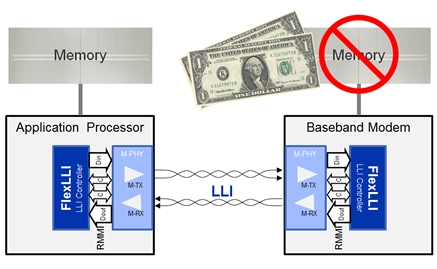

尚、今回のSynopsysの発表と合わせて仏ArterisがMIPI LLIのコントローラIPのリリースを発表しており、同IPとSynopsysの「DesignWare MIPI M-PHY IP」を組み合わせて利用する事で、モバイル端末におけるアプリケーション・プロセッサとモデムのメモリ共有が可能となり、コスト削減や実装面積の削減などのメリットを得られるという。

※画像はArteris社Web掲載の画像

Synopsysのマルチギア対応28nm「DesignWare MIPI M-PHY IP」は、特定顧客向けに2012年Q2から提供を開始する予定。Arterisの「MIPI LLIコントローラIP」は既に出荷が開始されている。

= EDA EXPRESS 菰田 浩 =

(2012.03.02

)