東大竹内研、SSDの寿命を10倍以上向上させるエラー訂正技術を開発 2/22 ISSCCで論文発表

2012年2月20日、JST(科学技術振興寄稿)、東京大学、慶応大学が共同でSSDメモリに関する新技術の開発を発表した。

今回発表された新技術は以下の大きく3つで、東京大学竹内健准教授をリーダーにJSTの研究開発事業として開発された。これら3つの新技術はいずれも半導体分野の国際学会ISSCC 2012で採択され、現在サンフランシスコで開催中の同学会で発表される。

・SSD信頼性向上技術 東京大学 竹内健 准教授

・DRAMモジュールとCPUの無線通信技術 慶應義塾大学 黒田忠宏 教授

・メモリカード向け無線給電技術 慶應義塾大学 石黒仁揮 教授

今回東大竹内研究室が開発したSSD信頼性向上技術は、「EP-LDPC」と呼ぶNANDコントローラーにおけるエラー訂正アルゴリズムで、竹内氏曰く、昨年同氏がISSCC 2011で発表した信頼性向上技術の更に上を行くもの。

SSDはPC、スマートフォン、タブレットから今後はサーバーでの利用が期待されているが、微細化により益々信頼性が損なわれているのが現状で、信頼性を高める手段としてコントローラの技術に期待が集まっている。コントローラが優れていれば、フラッシュでも安価な多ビット品を利用できるようになるため、コスト面でもコントローラ技術の担う役割は大きく、Appleは優れたコントローラ技術を手に入れるためにイスラエルのAnobit社を買収したと言われている。

NANDコントローラーの代表的な技術として、フラッシュの書き換え回数を平滑化するウェアレベリング、複数のメモリを同時に動かすインターリービング、ECC(エラー訂正)があるが、現在世界中でコントローラベンダが取り組んでいるのはLDPC(Low-density-parity-check)を用いたECCで、今回竹内研究室が開発した「EP-LDPC」技術も同分野に分類される。

LDPCは、エラーの判定を1かゼロではなく確率の概念を持ち込み軟判定しており、従来手法であるBCHよりも信頼性は高いが、多数の読み出しが必要で非常に遅い(BCHの約7倍)という難点がある。そこで竹内研究室では、LDPCの信頼性をBCHの速度で実現する新たなアルゴリズム「Error-Prediction-LDPC(EP-LDPC)」を考案した。

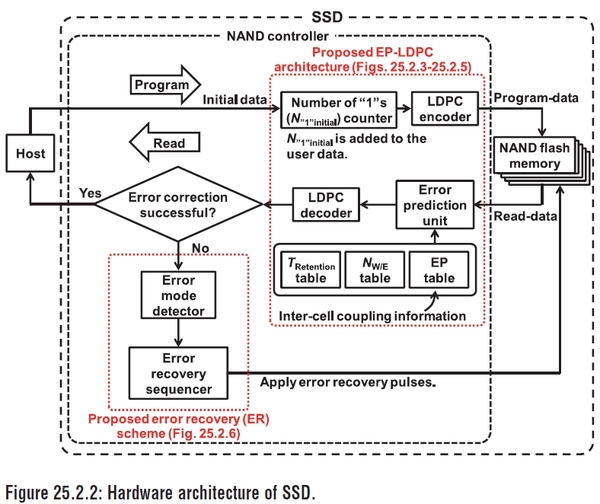

※画像は論文資料より抜粋:上の赤枠がEP-LDPC、下の赤枠はエラー復旧技術

「EP-LDPC」の考え方は、一回の読み込みで電子の抜けによるエラー箇所(しきい値低下)を予測するというもので、予測するという発想そのものがこれまでに無かったもの。

具体的には、1.周りのしきい値、2.書き換え回数、3.データ保持時間の3つの情報からエラー箇所を予測。これら情報はテーブル化し予めフラッシュに書きこんでおき、エラー予測時の計算に使用する。データ保持時間については不揮発性というフラッシュの特性上分からないため、書き換え回数、ビット・エラー・レートとの相関関係に着目し、これら情報から予測する手法を思いついた。

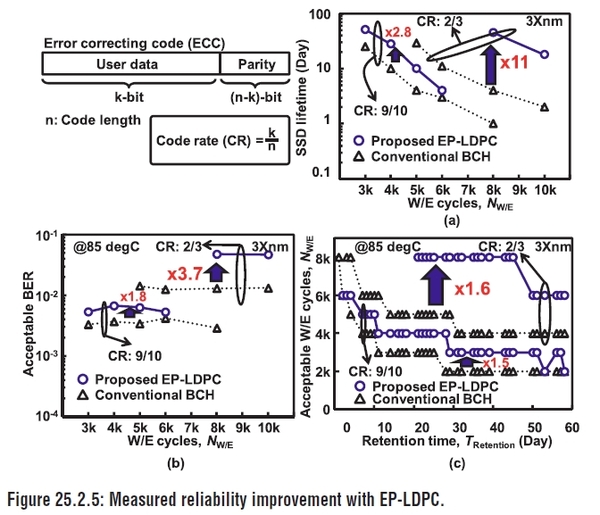

実際に「EP-LDPC」技術を用いてエラー訂正を行ったところ、BCHに対し信頼性を最大11倍向上させることに成功。このケース、違う見方をすると「EP-LDPC」のエラー訂正能力はBCHの3.7倍で、書き換え回数を1.6倍増やせる。すなわち1.6倍SSDを長持ちさせることが可能という事。竹内氏は「コストを60%減らせるのであれば、コントローラが多少高くなっても費用対効果は十分。サーバー等でSSDを利用する上で最適な技術。」としている。

※画像は論文資料抜粋:EP-LDPCの適用効果

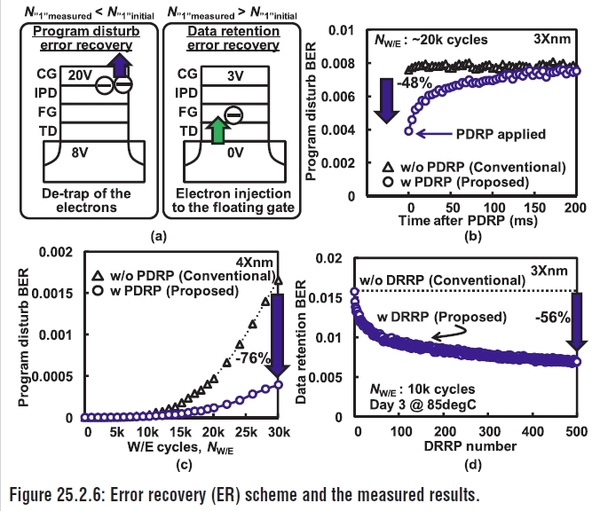

尚、竹内研究室では「EP-LDPC」技術と合わせてもう一つ「エラー復旧技術」も発明。これは研究生が偶然発見した現象を利用したもので、フラッシュ・メモリが本当に壊れてしまった際にそれを復旧するというもの。エラー訂正やむなくメモリが壊れた時に意図的にパルスを加えゲートにストレスを与えると、しきい値が一瞬下がりメモリを復旧できる。本質的にエラーから復旧する訳では無いが、一瞬だけでもメモリを復旧可能な同手法は書き込みエラーにもデータ保持エラーにも有効で、両エラー復旧の際に与えるパルスをそれぞれPDRP/DRRPと命名している。実際に書き込みエラーの場合で最大76%エラー・レートを下げる効果があったということで、同技術もコントローラーで制御可能。フラッシュの専門家が注目しているという。

※画像は論文資料より抜粋:PDRP/DRRPの適用効果

これら竹内研究室の研究成果は、現地時間2月22日にISSCC 2012にて発表される予定。今回JSTの研究開発事業として開発されたその他の技術は以下の通り。

・DRAMモジュールとCPUの無線通信技術 慶應義塾大学 黒田忠宏 教授

ボードにDRAMモジュールを挿す場合、その場所や数によって伝送線路のインピーダンスが変わってしまい、インピーダンスのマッチングを取ることが難しくなる。そこで非接触のワイヤレス通信を用いる事でインピーダンスの調整を行うこと無く高速な通信を実現。DDR3と比較して3倍以上の通信速度の向上を実現した。

・メモリカード向け無線給電技術 慶應義塾大学 石黒仁揮 教授

フラッシュを用いたメモリカードは、書き込みにmsec単位の時間を要する遅いデバイスであるため、ホスト側と合わせるために数十のチップを同時に動かしており、アプリケーションによっては電力の負荷の変動が激しい。そこで負荷の変わるようなアプリケーションに対して変動に追従して送信電力を高速に制御する無線電力転送システムを開発した。

= EDA EXPRESS 菰田 浩 =

(2012.02.21

)