Bluespec User Group Meeting 2012

2012年1月27日、サイバネットシステム社の主催するセミナー「Bluespec User Group Meeting 2012」が開催された。

セミナーは、Bluespec社の提供するSystemVerilogベースの独自言語「Bluespec SystemVerilog(以下、BSV)」とBSVツールセットを用いた設計手法、設計事例を紹介するもので、計5つの講演が行われた。

Bluespec側の講演は、本社マーケティングVPのGeorge Harper氏と、日本代理店であるサイバネットのBluespec担当AE 工野 勝彦氏によって行われ、BSVを用いた設計および検証のメリット、SystemCとBSVの協調設計の手法などが紹介された。

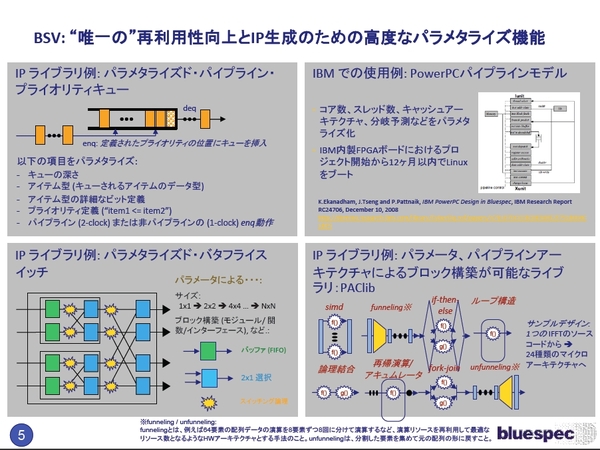

George Harper氏の話のポイントは大きく2つ。一つは高位設計ツールとしてのBSVの強みで、例によってデザインを問わず制御ロジックの合成にも対応可能な点や、BSV資産の再利用性を高めるパラメタライズ機能などが紹介され、BSVの能力を裏付けるエピソードとして、IBMの事例(PowerPCパイプラインモデルの開発)やマサチューセッツ工科大学での教育利用、IEEE MEMOCODEでのデザイン・コンテストにおける実績(直近5年でBSVユーザーが出場した年は4回全て優勝)などが紹介された。

※IBMの事例についてはブログ「Verification Evangelistの戯言」でも紹介されている。

※画像はBluespec提供のデータ

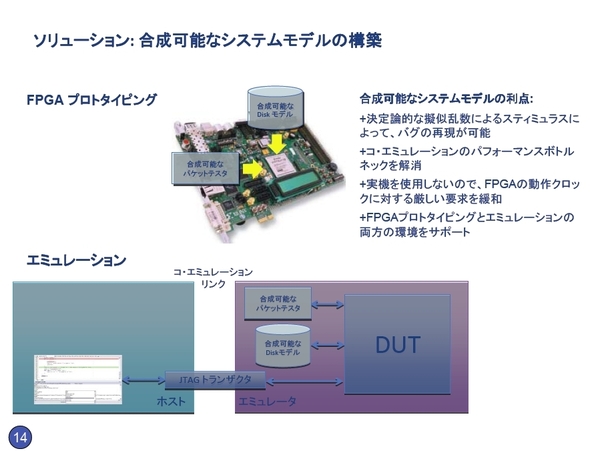

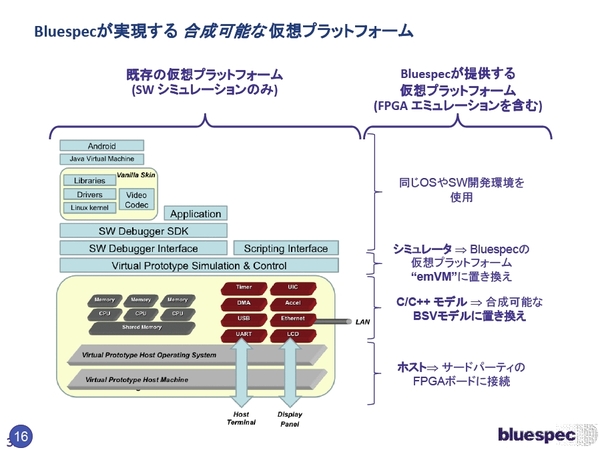

もう一つGeorge Harper氏が強調したのは「合成可能なBSV」という点で、BSVでテストベンチを記述すればSystemVerilogよりも少ない記述量で済み、かつそれらを合成してFPGAプロトタイピングやエミュレーションでも利用出来るという例や、BSVでバーチャル・プラットフォームを作成すれば、そのまま合成してFPGAエミュレーションで使用可能といった例が紹介された。

※画像はBluespec提供のデータ

尚、Bluespecはこれまで同社のツールを導入した顧客として、北米のモバイル半導体大手3社(企業名非公開)、STマイクロエレクトロニクス、パナソニック、富士通、日立製作所などを挙げているが、国内ユーザーとしてはその他にもビッグ・ユーザーが存在している他、Intelも同社のユーザーであるという話だった。

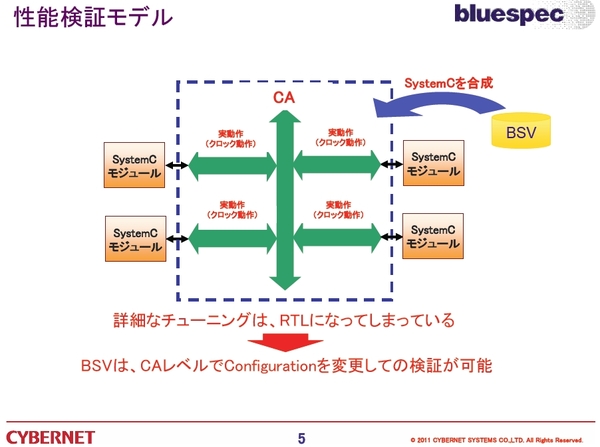

一方の工野氏の話は「SystemCとBSV」の混在利用に関するもので、BSVでもSystemC TLM同等のモデリングが可能とした上で、性能検証にはRTLより抽象度の高いCAレベルでコンフィギュレーションの変更でモデルのチューニングが可能なBSVが便利と解説。(BSVコンパイラはSystemC CAモデルを生成できる)実際にCAレベルのチューニングに着目してBSVを評価しているユーザーもいるという事だった。

※画像はCybernet提供のデータ

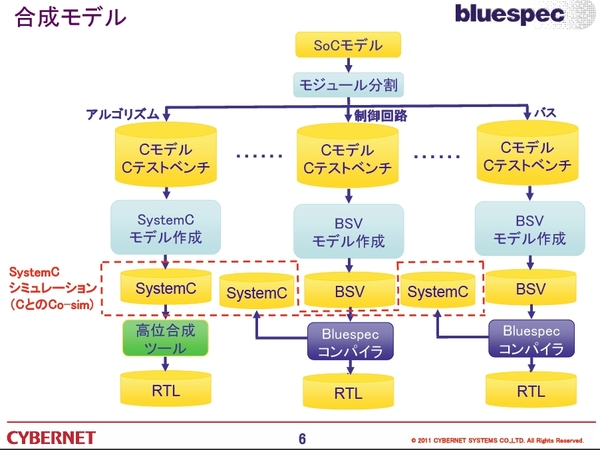

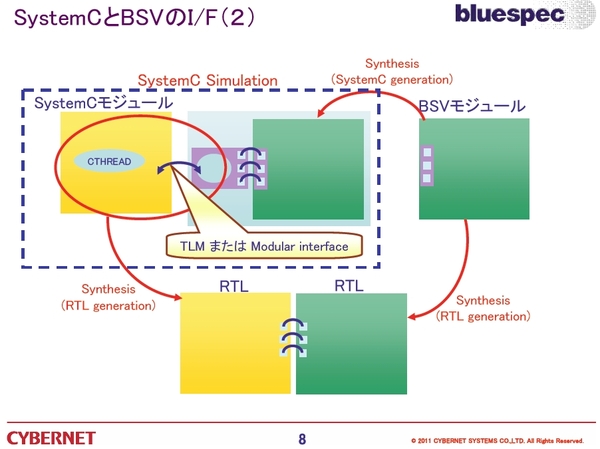

また、回路の合成に関しては、アルゴリズムはSystemCから市販高位合成ツールで合成、制御回路やバスなどはBSV書いてBSVコンパイラで合成という、SystemCとBSVで補完し合う併用方式を提唱。SystemCモデルとBSVモデルのインタフェースは、BSVのラッパ生成機能を使えばSystemCのTLMまたはModular I/Fからピンレベルに変換するラッパーを生成してくれるという。(※ラッパー生成機能は現在開発中とのこと)

※画像はCybernet提供のデータ

続いて事例講演の話。今回は昨年の「Bluespec User Group Meeting 2011」で評価事例を発表した日立製作所 通信ネットワーク事業部 共通設計本部 DA部 主任技師 菊池 光司 氏が「通信ネットワーク事業部でのFPGA論理設計・検証へのBluespec適用事例」と題して講演を行った。

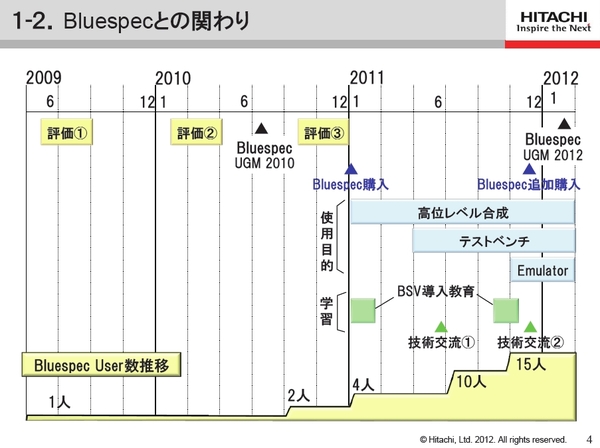

菊池氏によると、同社ではBSVを2009年6月頃から評価開始、2011年1月には正式にBSVを導入し、ユーザーの増加に合わせて2011年12月に追加導入。現在ユーザー数は15名で高位合成、テストベンチ、エミュレーションと大きく3つの用途でBSVを活用している。今回の講演では光通信ネットワーク向けパケット通信装置の設計事例が紹介された。

※画像は日立製作所提供のデータ

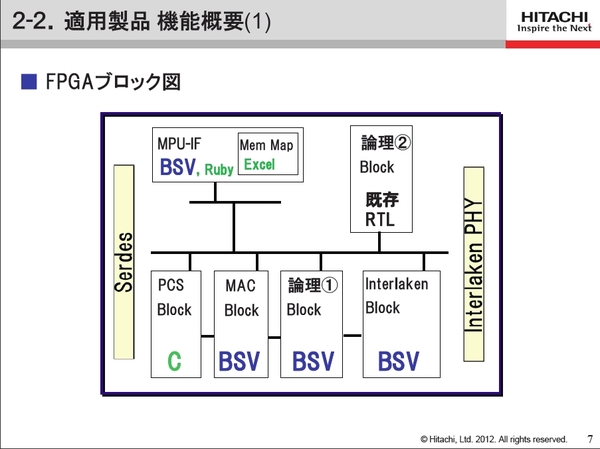

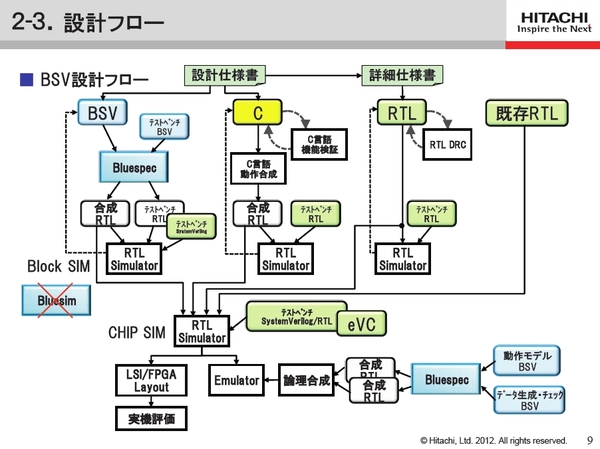

菊池氏の説明によると、パケット通信装置の設計はFPGAをターゲットにBSVとC、既存のRTLを組み合わせて実施。チップ間インタコネクト・プロトコル「InterLaken」をはじめとする幾つかの機能ブロックでBSVを積極的に利用した。スループット1で、3種類のマルチ・クロックを使う「InterLaken」のような回路の設計事例はBSVならではと言える。Cを用いた機能ブロックについては他社の高位合成を利用した。

※画像は日立製作所提供のデータ

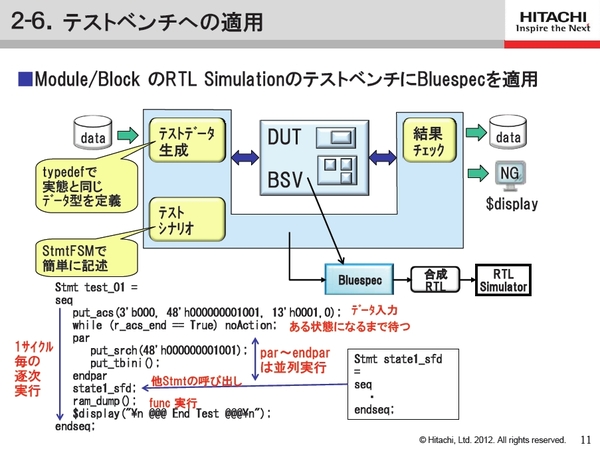

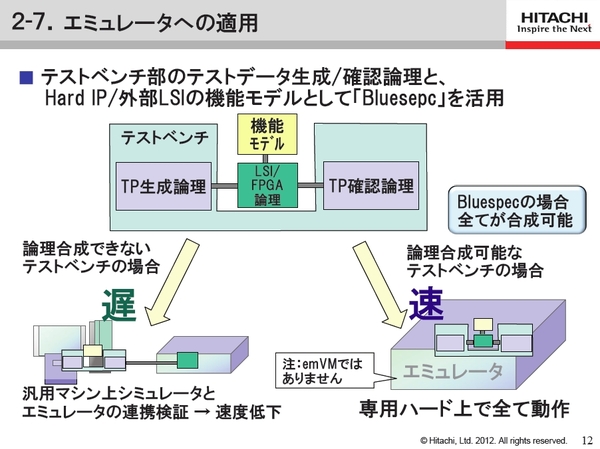

検証については、BSV、C、既存RTLの個々の機能ブロックをRTLでシミュレーションした後にチップ全体のシミュレーションを実施した。モジュールやブロックのRTLシミュレーションではテストベンチの記述にBSVを利用。全体シミュレーションでは、SystemVerilogのテストベンチとeVCを用いたランダムテストを行った。また、全体シミュレーションの後でエミュレーターを使用する際にもBSVを利用。テストベンチと外部の機能モデルをBSVで記述し、それら全てをエミュレーター上に実装する事で高速検証を実現した。

※画像は日立製作所提供のデータ

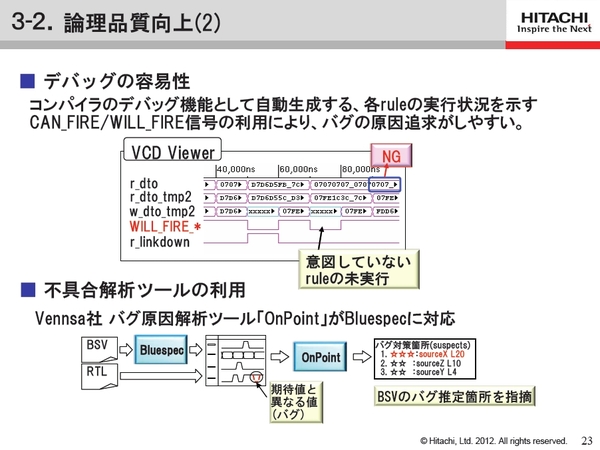

菊池氏はBSVの利点として、「論理記述の効率化」、「論理品質向上」、「再利用性向上」の3点を挙げたが、「論理記述の効率化」の説明で興味深かったのは「リソースを主語にコードを書くか、処理を主語にコードを書くか」というくだりで、BSVは処理を主語にコードを記述するのに適しており、その記述方法であれば仕様をダイレクトにコードに落とす事ができるという事だった。また「論理品質向上」については、BSVの言語体系そのものの良さと合わせてデバッグの容易性を指摘。同社ではBSVコンパイラのデバッグ機能の他に、Vennsa社のバグ原因解析ツール「OnPoint」を導入してBSVのバグ解析に利用しているという。

※画像は日立製作所提供のデータ

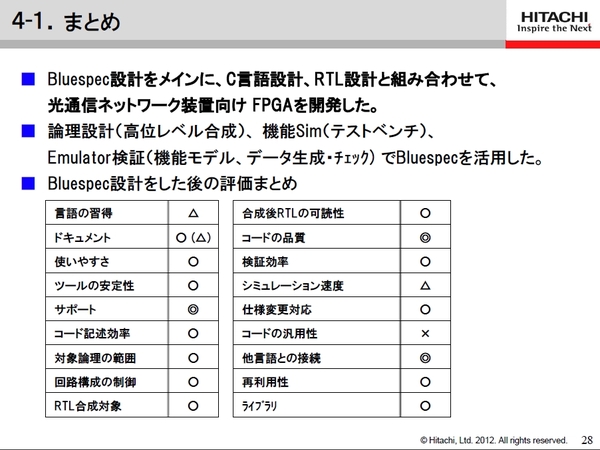

菊池氏は講演の最後にBSVによる設計の評価をまとめたが、ネガティブな評価は言語習得は難しいという点とコードの汎用性が低いという点、あとは専用のBlueSimシミュレーターではRTLの10倍近い速度は見込めないという点だけだった。同社では新規設計ではBSVを使う方向に動いており、今後はグループの枠を超えて系列会社などにも展開していくようだ。

※画像は日立製作所提供のデータ

尚、今回セミナーの最後にサイバネットシステムからサプライズなお知らせがあった。

それはBSVの専用シミュレーター「Bluesim」の無償版の提供で、日本限定で2/1より無償版の「Free Bluesim」の提供が開始される予定。合わせてBSVのサンプル集のPDFドキュメントも無償配布される予定。その詳細は以下の通り。

・機能制限:記述内のオブジェクト数600まで

・期間制限:3ヶ月間(再度申し込み可=おかわり自由)

・商用利用禁止

・技術サポート対象外

※技術サポート付きの通常評価ライセンスは従来通り別途提供

※申し込みURL http://www.cybernet.co.jp/bluespec/download/free.html

= EDA EXPRESS 菰田 浩 =

(2012.02.08

)