【#47DAC】Atrenta、新製品「SpyGlass-Physical」を発表 イケてないRTLを事前修正

第47回DAC(Design Automation Conference)に出展していたアトレンタのブース・レポート。

アトレンタは、DAC2日目の6/15に新製品「SpyGlass-Physical」を発表した。

「SpyGlass-Physical」は、RTLの段階でレイアウト上、問題となりそうな箇所を解析するソリューションで、「いけてない」RTLを事前に修正することで、レイアウト工程からRTLへの手戻り削減を狙うもの。「SpyGlass-Physical」は、従来のSpyGlass製品同様、ルールベースのチェックで問題箇所を指摘するため、重要なのはそのルール作り。アトレンタは日本の半導体ベンダの協力も得て、実例ベースのデータから、レイアウト上問題が発生する可能性の高い「危険なRTL記述」10ケースをルール化したとしている。

「SpyGlass-Physical」は、レイアウト上の問題を完全に取り除く事を目指すツールではないが、実際の開発現場で起こるレイアウト側からRTL設計側への修正依頼を減らし、両者のやり取りを円滑化させる効果も期待できる。

※下の画像はアトレンタ社のブースの様子

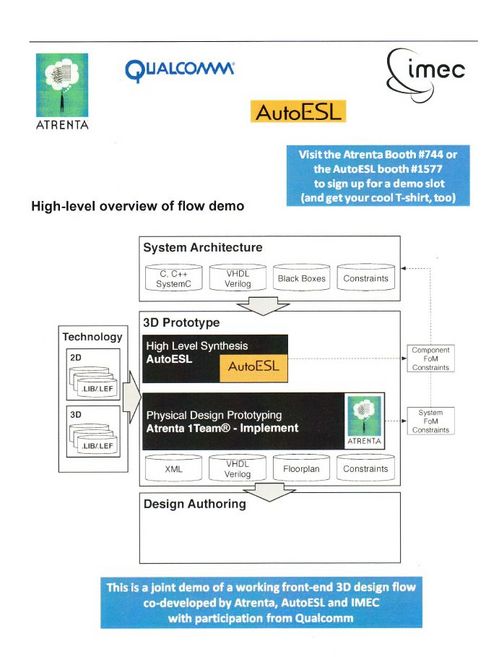

また、今回のアトレンタの展示で興味を惹いたのは、3D-IC設計関連でのAutoESLとのコラボレーション・フロー。ブース内プレゼンで紹介していた同フローは、ベルギーIMECのTSV(スルー・シリコン・ビア)の研究をベースに、Qualcommがユーザーとして参加しているプロジェクトで開発されたもの。TSV技術を効果的に利用するためには、2次元のレイアウトの設計フェーズよりも、より上位の設計フェーズで3次元的な検討が必要というコンセプトがベースとなっており、AtrentaとAutoESLが両社の製品を用いた3D Prototypeフローを構築した。

また、今回のアトレンタの展示で興味を惹いたのは、3D-IC設計関連でのAutoESLとのコラボレーション・フロー。ブース内プレゼンで紹介していた同フローは、ベルギーIMECのTSV(スルー・シリコン・ビア)の研究をベースに、Qualcommがユーザーとして参加しているプロジェクトで開発されたもの。TSV技術を効果的に利用するためには、2次元のレイアウトの設計フェーズよりも、より上位の設計フェーズで3次元的な検討が必要というコンセプトがベースとなっており、AtrentaとAutoESLが両社の製品を用いた3D Prototypeフローを構築した。

フローとしては、AutoESLの高位合成ツールによって様々なアーキテクチャの回路を自動生成し、それら回路のフィジカル・プロトタイプをAtrentaの「1Team-Imprement」で実行。その結果からTSVによるデザインへのインパクト、熱分布、メカニカル・ストレスなどを解析し、何処に、どのようにTSVを使うか? その様々なオプションを探求する。

未だ実験レベルのフローという事だが、上流手法での解析の有効性は確認済みという事で引き続きAtrenta、AutoESL、IMECの3社で研究を進めていくという。

※下の画像はアトレンタ社の資料より 3Dフローの概要

= EDA EXPRESS 菰田 浩 =

(2010.06.24

)