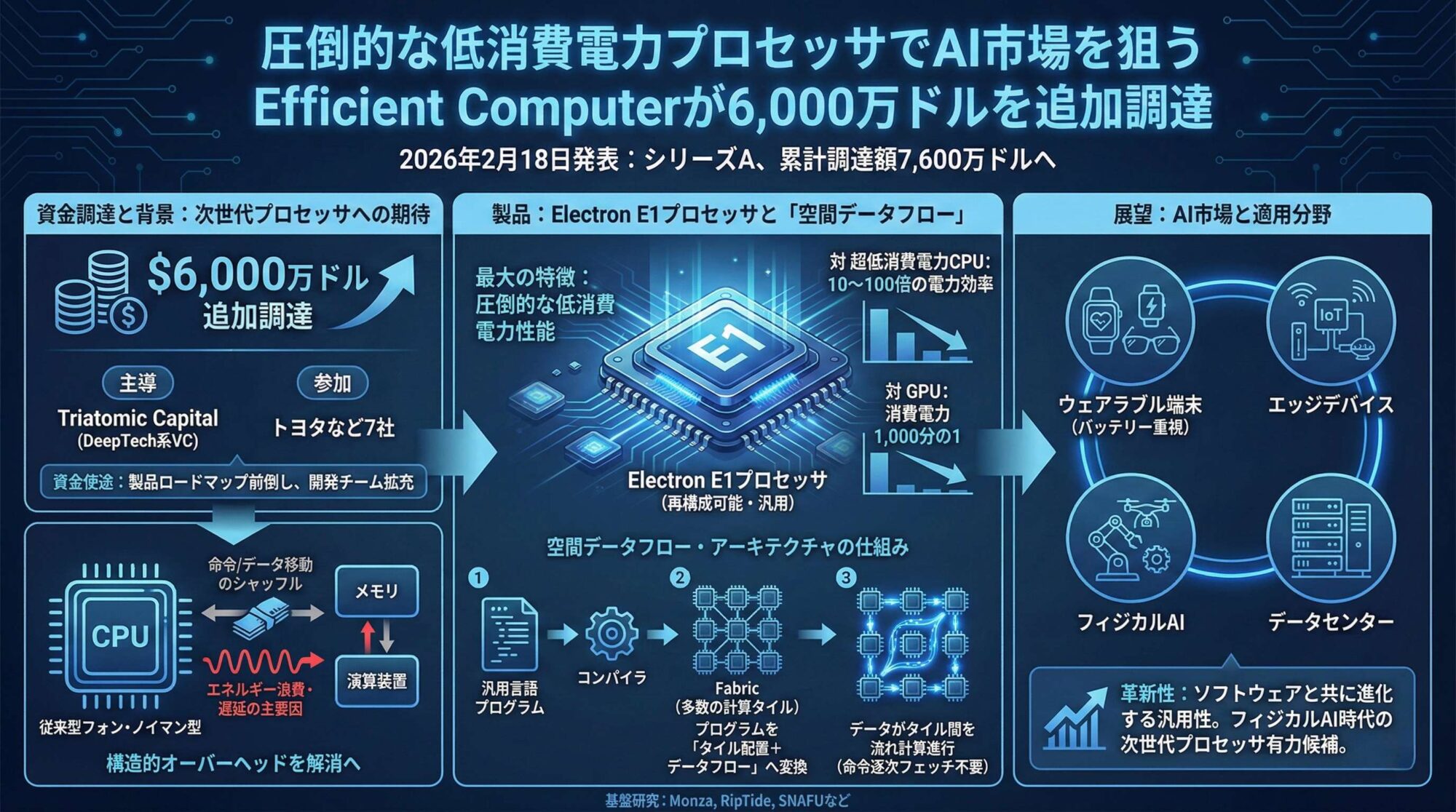

圧倒的な低消費電力プロセッサでAI市場を狙うEfficient Computerが6,000万ドルを追加調達

2026年2月18日、低消費電力の汎用プロセッサを手がける米半導体ベンチャーEfficient Computerは、シリーズAで6,000万ドルを調達したと発表した。

発表によると、今回の資金調達はDeepTech系VCのTriatomic Capitalがリードし、トヨタなど7社が参加した。シード資金を含む累計調達額は7,600万ドルに達する。調達資金は、製品ロードマップの前倒しと、エンジニアリング/開発チームの拡充に充てるとしている。

同社が開発する「Electron E1プロセッサ」は、従来のフォン・ノイマン型とは異なる「空間データフロー(Spatial Dataflow)」の概念を実装した、再構成可能(reconfigurable)な汎用プロセッサだ。最大の特徴は圧倒的な低消費電力性能で、同社は一般的な組み込みタスクにおいて、超低消費電力CPUと比べて10〜100倍の電力効率、GPUと比べて消費電力が1,000分の1になる可能性があると説明している(いずれも同社発表)。

「データのシャッフル」を減らす空間データフロー・アーキテクチャ

Efficient Computerは、従来のCPUやGPUでは計算のたびに命令やデータをサイクルごとに移動させる必要があり、この「データのシャッフル」こそがエネルギーを浪費し、遅延を招く主要因だと指摘する。こうした構造的オーバーヘッドを解消するために考案したのが「空間データフロー・アーキテクチャ」だ。

同アーキテクチャでは、ハードウェアとコンパイラが密に連携し、プログラムの実行プロセスを根本から組み替える。処理の流れ(データフロー)をプロセッサ上に“空間的に配置”して実行することで、従来アーキテクチャに内在する不要なデータ移動やオーバーヘッドの削減を狙う。

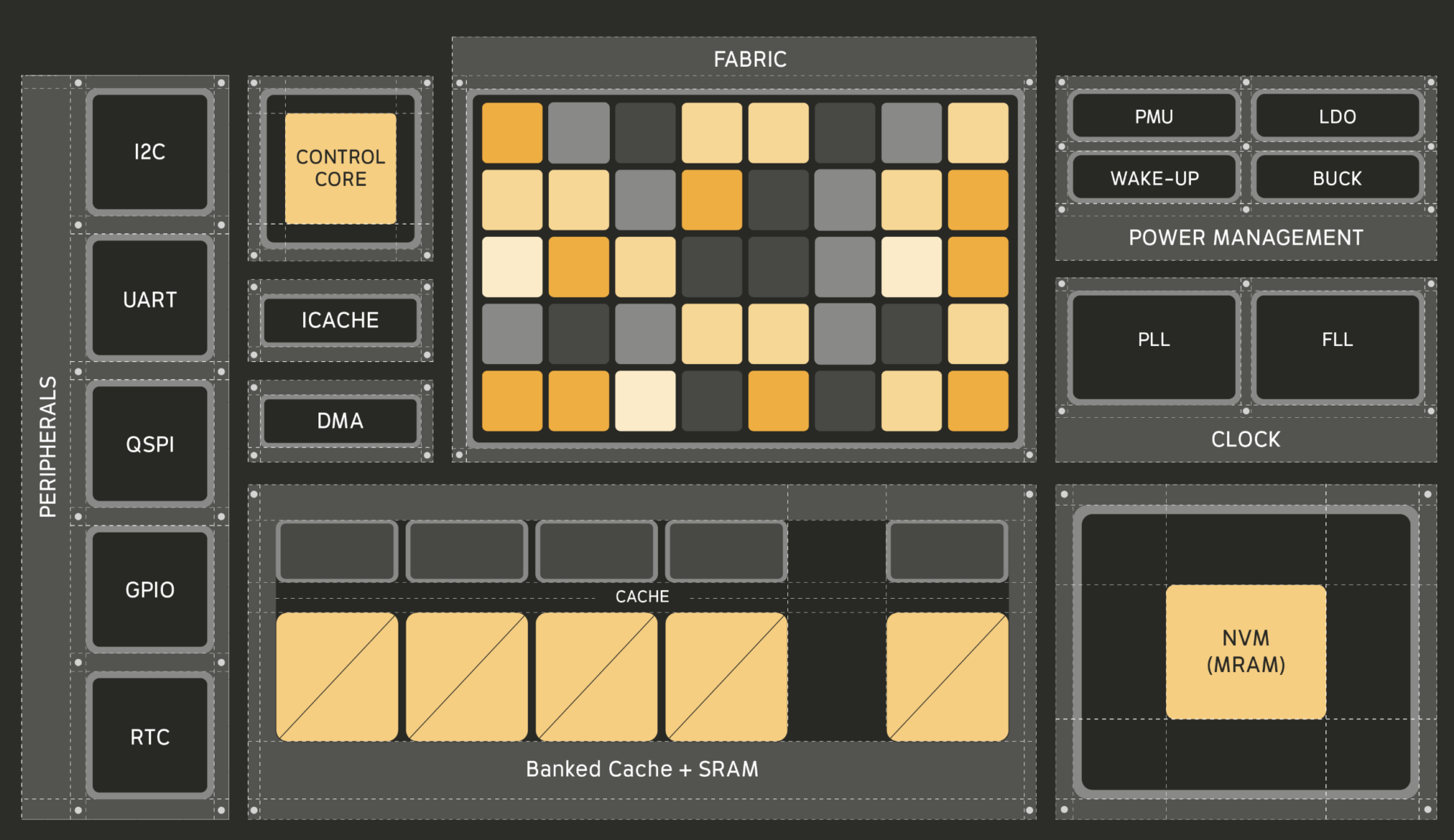

空間データフロー・アーキテクチャを用いたプロセッサの仕組み

・チップ上に「Fabric」と呼ばれる小さな計算タイルを多数配置する

・コンパイラが汎用言語で書かれたプログラムを「タイル配置+タイル間接続(データフロー)」へ変換する

・プログラムのデータの流れそのものを、プロセッサの動作としてマッピング(計算タイルに割り当て)する

・命令を逐次フェッチして実行するのではなく、データがタイル間を流れることで計算を進める

同社によれば、この空間データフロー・アーキテクチャは、Monza、RipTide、SNAFUなど、長年にわたるエネルギー最小化データフロー・システムの研究成果を基盤としており、アカデミックな裏付けがあるという。

ウェアラブルからフィジカルAI、データセンターまでを視野に

Efficient Computerの「Electron E1」は、極めて高い電力効率を備えた汎用プロセッサとして、ウェアラブル端末や各種エッジ・デバイスなど、バッテリー持続時間が重要な領域にとどまらず、フィジカルAIやデータセンターといったAI主導で拡大する新興市場にも適用可能とされる。

Efficient Computerは、ドメイン特化のカスタムSoCとは異なり、ソフトウェアの進化に合わせて機能や最適化を継続的に取り込める“汎用”アーキテクチャである点を同社の技術の革新性として掲げている。多様なユースケースへ適応できると同時に、高いエネルギー効率を提供可能なEfficient Computerの汎用プロセッサは、フィジカルAI時代に向けた次世代プロセッサの有力候補として注目される。

Efficient Computer

= EDA EXPRESS 菰田 浩 =

(2026.02.25

NEW

)