LLMを用いた学習プラットフォームで次世代チップ設計者を育成する

2026年1月20日、ドイツのカイザースラウテルン・ランダウ大学(RPTU)のLukas Krupp氏らの研究グループは、チップ設計教育にLLM(大規模言語モデル)を活用する学習プラットフォームに関する論文を発表した。

論文タイトル: 「From RTL to Prompt Coding: Empowering the Next Generation of Chip Designers through LLMs」。同論文は、2026年5月開催予定のISCAS 2026(International Symposium on Circuits and Systems)に採択されているという。

ここでは同論文の概要を紹介する。

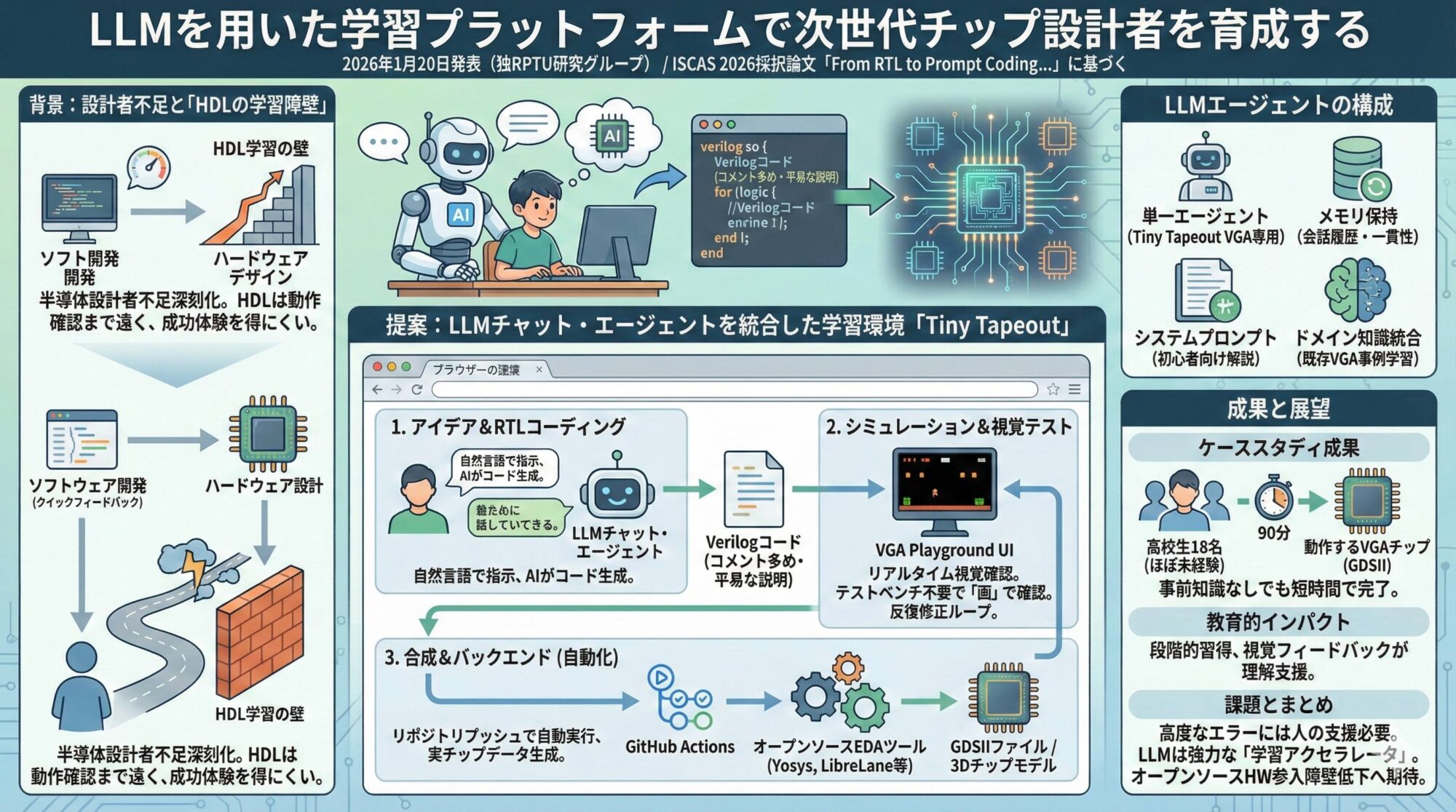

背景:設計者不足と「HDLの学習障壁」

半導体設計者不足が深刻化する中、新たな若年層の設計者が育ちにくい要因の一つとして、ハードウェア記述言語(HDL)の学習難易度の高さが挙げられる。ソフトウェアと比べ、動作確認までの距離が長く、成功体験を得るまでに時間がかかりやすい点が障壁となっている。

提案:LLMチャット・エージェントを統合した学習環境

研究グループは、ソフトウェア開発のように「抽象度が高く、すぐに動かせる」体験をハードウェア設計教育にも取り込むことを狙い、LLMチャット・エージェントを組み込んだ設計教育環境として「Tiny Tapeout」を用いた学習ワークフローを提案する。

Tiny Tapeoutの概要

Tiny Tapeoutは、非専門家でもアイデアをシリコン(実チップ)へ変換するための、ヒューマン・イン・ザ・ループ型の設計フローを提供するブラウザベース環境である。ここにLLMチャット・エージェントを統合することで、フロントエンド(RTL)とバックエンド(合成・P&R)を分断せず、初心者でも自然言語を起点に、テープアウト可能な成果物へ到達しやすい設計体験の実現を目指す。

Tiny Tapeoutを用いたワークフロー(すべてブラウザベース)

1. アイデア開発とRTLコーディング

LLMチャット・エージェントとの対話を通じて、VGAベースのデザイン(レトロゲーム、アニメーションなど)をVerilogコードとして生成する。

2. シミュレーションと視覚テスト

VGA Playground UIを用いて生成コードをリアルタイムにシミュレーションする。OSSのHDLシミュレータVerilatorによるRTLシミュレーションとVGAレンダリングを組み合わせ、テストベンチを書かずに“画”で視覚的に動作確認できる点が特徴。期待した動作と異なる場合は会話に戻って修正し、反復ループを回す。

3. 合成とバックエンド・フロー

GitHub UI経由でVerilogコードをリポジトリへプッシュすると、GitHub Actions上でYosysやLibreLaneなどのオープンソースEDAツールが自動実行され、GDSIIファイルや3Dチップモデルを生成する。

LLMチャット・エージェントの構成

LLMチャット・エージェントは単一エージェント構成とし、対象タスクを「Tiny TapeoutのVGA設計」に絞っている。会話履歴や中間成果物をメモリとして保持し、反復設計でも一貫性を保つ。また、エージェントに守らせるルールを明確に実装したとしており、以下のような点を挙げている。

- システムプロンプト:初心者を前提に平易に説明し、コメント量の多いRTLを出力する

- RTLコーディング命令:Tiny Tapeoutのインターフェース要件(モジュール宣言、信号マッピング等)に準拠したステップ・バイ・ステップのガイダンスを行う

- ドメイン知識の統合:既存のVGAデザイン例と、その視覚的動作の記述をペアとして取り込み、生成精度向上を狙う

ケーススタディ:高校生が90分でGDSII生成

ケーススタディでは、高校生18名(8グループ)が90分で「動作するVGAチップ」のGDSII生成まで到達したと報告されている。チップ設計の事前知識があった参加者は17%、電子工作経験・プログラミング経験は22%程度で、多くはほぼ未経験だったという。

教育的インパクトと課題

学生は、単純な図形表示から開始し、LLMチャット・エージェントとの対話を繰り返すことで、移動、色、インタラクションといった機能を段階的に追加していくプロセスを自然に習得した。シミュレーションによる視覚的フィードバックは、プロンプト修正やコード理解を支援する重要な役割を果たした。

一方で、合成不可能なVerilogコードの生成やチップ面積超過などのエラーも発生し、LLMチャット・エージェントを通じた修正試行が行われたとする。ただし、高度なバックエンド起因のエラーについては指導者の補助が不可欠であり、初心者に成功体験を与える入口として有効である一方、バックエンドの制約理解や設定調整には依然として人の支援が必要、という課題も示唆されている。

まとめ

- 本研究は、LLMがチップ設計教育における強力な「学習アクセラレータ」となり得ることを示した

- 従来は数週間〜数か月を要し得る「設計から物理レイアウトまで」のプロセスを、事前知識のない初心者でも90分で完了できる可能性を提示した

- 今後は、LLMが対応可能なバックエンドエラーの範囲拡大、ならびに大学生・社会人など異なる対象層への適用、学習曲線の定量評価が課題となる

本研究はハードウェア設計者育成の観点に加え、オープンソース・ハードウェアの普及の観点からも興味深い。Tiny Tapeoutのようなオープンソースのハードウェア設計プラットフォームとLLMの生成能力を組み合わせることで、CHIPS Alliance、OpenHW Group、Google&SkyWater、そして国内ではOpenSUSIなどが推進するオープンソース・ハードウェアの参入障壁をさらに下げる可能性も期待できそうだ。

RPTU

= EDA EXPRESS 菰田 浩 =

(2026.02.17

NEW

)