11/14 Quadric/ネクストリーム セミナー・レポート

2025年11月14日、Edge AI向けのプロセッサIPを手がけるQuadricとEDAツールや半導体IP製品のディストリビューター株式会社ネクストリームは、新横浜で共催のセミナー・イベントを開催した。

同セミナー・イベントでは、主催した両社のソリューション紹介のほかに、ユーザーによる導入事例の紹介など計10講演が行われ多数の聴講者を集めた。ここでは興味深かった講演内容をピンポイントで紹介していきたい。

Quadricの会社、技術および製品の紹介

Quadric日本法人 代表取締役社長のJan Goodsell氏によると、同社は直近の四半期決算で黒字化を達成。すでに累計4,300万ドルを資金調達しているが、更に最大5,000万ドル近くの資金調達を計画しており、一気に人員を倍増して市場攻略を進めていく予定とのこと。

Jan Goodsell氏

同社のエッジAI向けプロセッサIP「Chimera」は現在3種類のIPコアがラインナップされており、各コア最大8コアのマルチコア構成が可能。1TOPSから最大864TOPSまで用途に応じてIPコアの構成を選択できる。

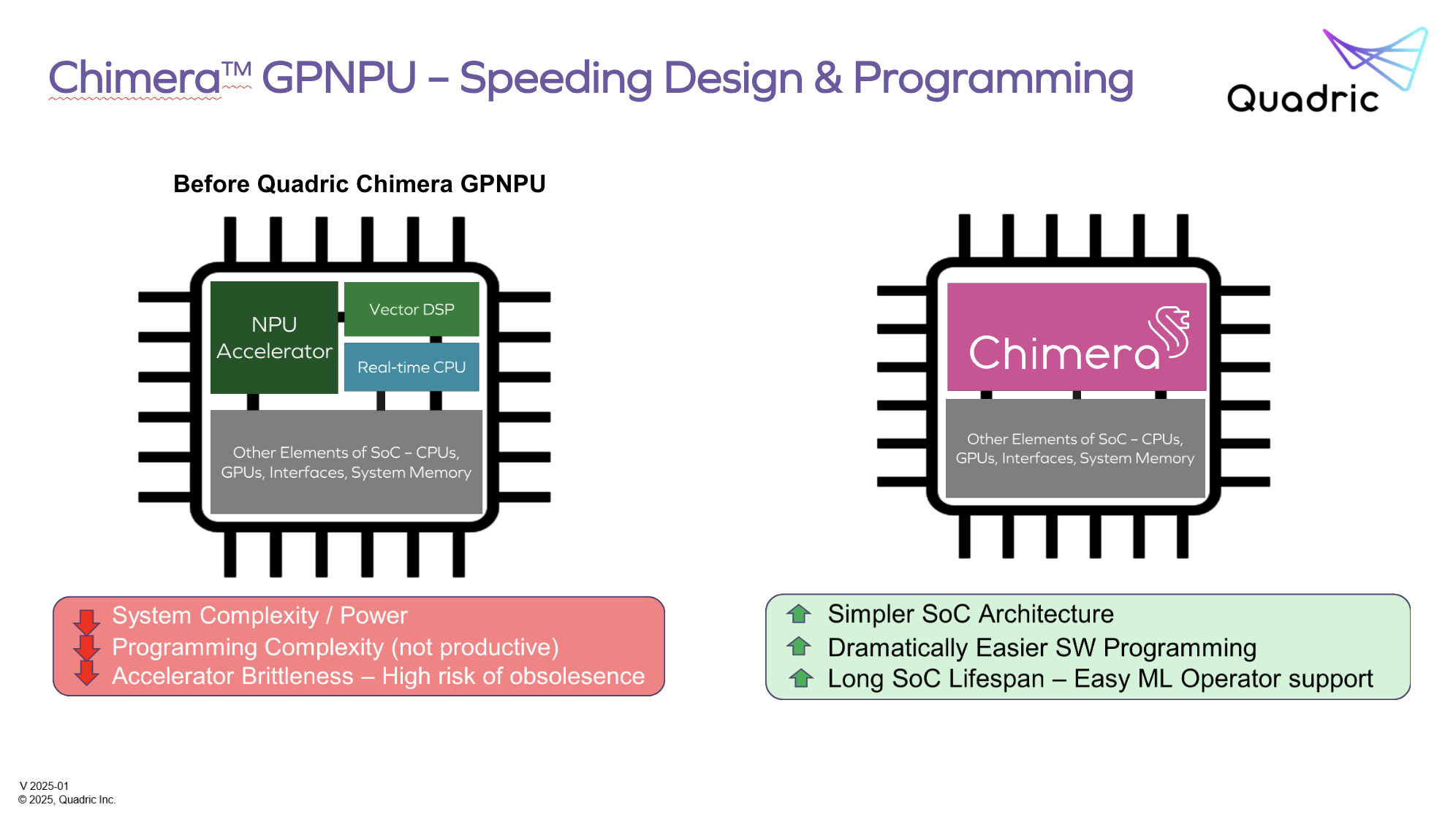

ヘテロジニアス・アーキテクチャの一般的なAIプロセッサと違い、単一のコア、単一のソフトウェア開発環境でAIを実装できるのが「Chimera」の最大の特徴で、ユーザーが実装できる推論用のAIモデルをなんと352種類も用意している。(うち110モデルは今年追加したモデル)同分野のAIプロセッサで用意されているモデルはせいぜい数十種類であることを考えるとQuadricのモデルの多さは抜きん出ているが、これは人海戦術のなせる技ではなく「Chimera」のプログラミングのし易さの現れなのだという。(※Quadricは社員55人と、むしろエンジニアは少ない)

画像はQuadricの発表資料より抜粋

なお、進化の非常に早いAIの世界において、次々と出てくる新たなAIモデルにNPU(ハードウェア)がどう対応していくかは大きな課題の一つとなっているが、そこにずばりはまるのがまさに「Chimera」で、Jan Goodsell氏によると流行りのAI-PCにおいて、新たなAIモデルをキャッチアップするために「Chimera」を活用するPCメーカーも出てきているという話だった。

京セラドキュメントソリューションズの選択、なぜ「Chimera」だったか

Quadricの「Chimera」の採用事例を紹介したのは、京セラドキュメントソリューションズ株式会社、技術本部 ソフトウェア2統括技術部 AIソリューション開発1課の杉原 宏 氏。

杉原 宏 氏

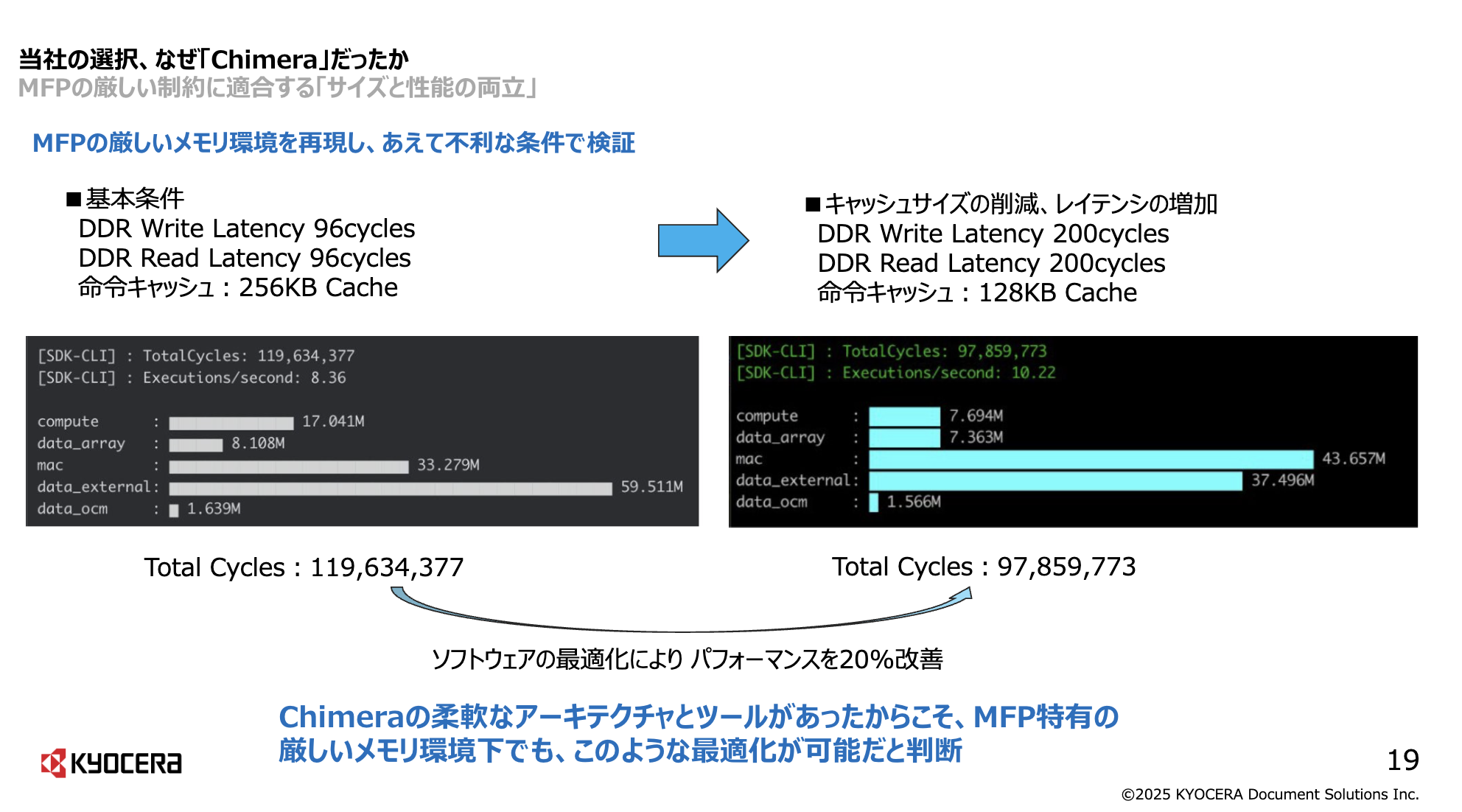

同社では今年5月に次世代SoCへの「Chimera」を発表しているが、杉原氏によるとその決め手となったのは大きく「サイズと性能」、「長寿命アーキテクチャ」、「言語処理能力」の3つ。小面積構成も選択可能で高性能。ソフトウェアの最適化によりパフォーマンスの向上も見込めるという点に加え、新たなAIモデルに対応可能な柔軟性(プログラマブル)と複写機の機能向上に重要なTransformerモデルの性能を挙げた。

画像は杉原氏の発表資料より抜粋

Transformerモデルの性能というのは、「Chimera」に実装するにあたってどこまで最適化できるか?という視点で、Transformerの最適化手法として知られる「KV-caching」の適用を検討したところ、「Chimera」の柔軟なメモリ・アクセスにより、複雑なデータ・フローを効率的に実装可能できると判断したという。

Agnisys社およびAMIQ社のソリューション紹介

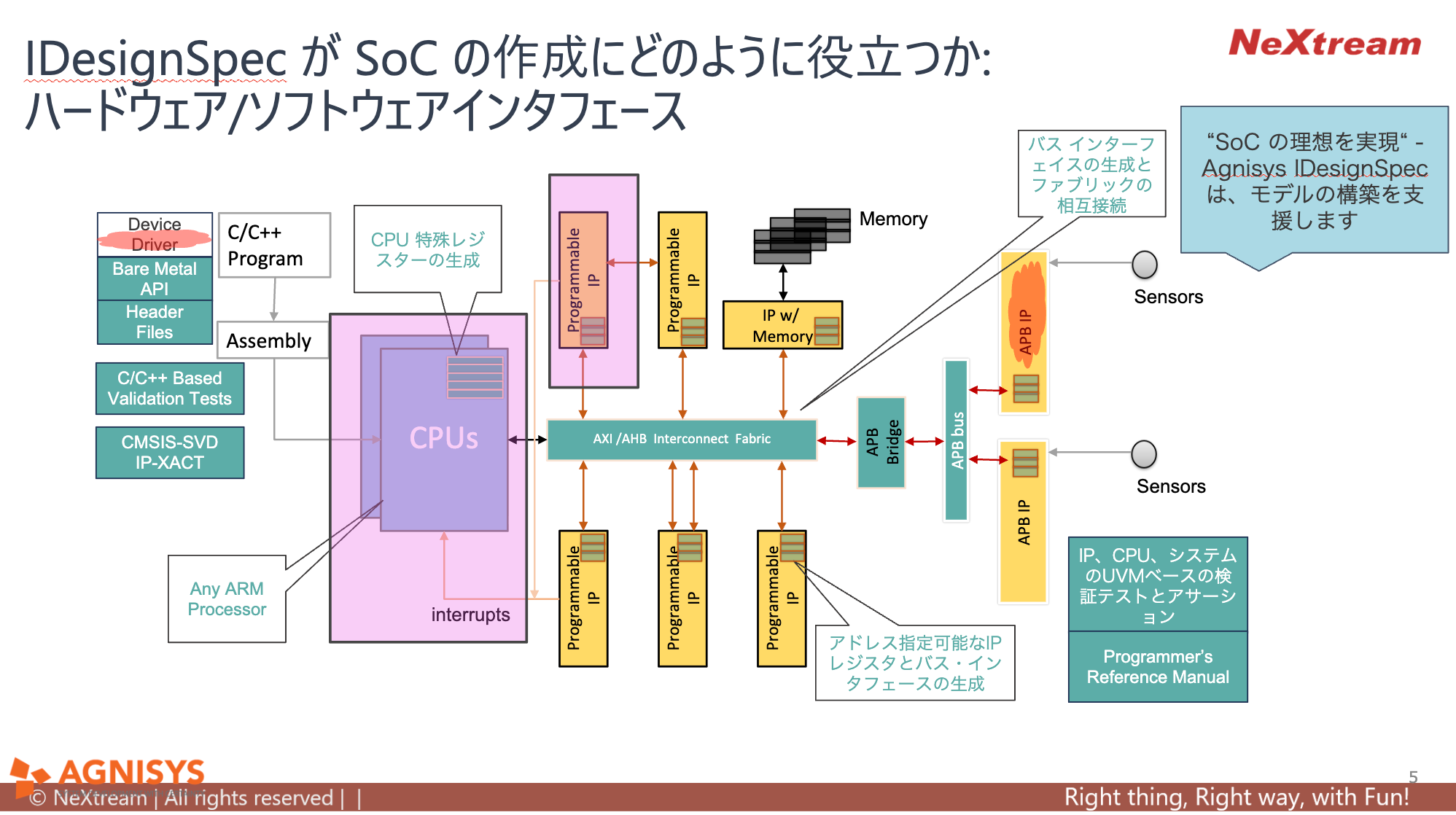

ネクストリーム営業部の中山 みどり氏の説明によると、Agnisys社の「IDesignSpec」はレジスタ/メモリ仕様からHW-SWインタフェース、各種バス・コンポーネント、ファームウェア用のC/C++ヘッダ、SoCのリファレンス・マニュアル用のドキュメントなどを自動生成してくれるということで、製品名通りデザインの「Spec/仕様」に重きを置き、レジスタ/メモリ仕様書を実行可能な「ゴールデンソース」として扱うことをコンセプトとしたツールと言える。

中山 みどり氏

入力はWord, Excel, 各種テキストファイル、SystemRDL, IP-XACT,など、仕様作成に利用されているフォーマットは概ね利用可能。出力は、RTL (Verilog, SystemVerilog, VHDL, SystemC)、C/C++, HTMLなど。出力される各種バス・コンポーネントは事前検証済ですぐに利用可能。また、複数のIPを結線しトップのネットリストを自動生成する機能もある。

画像は中山氏の発表資料より抜粋

仕様が変わったら「ゴールデンソース」を修正し、「IDesignSpec」を使って再度成果物を自動的に再生成という形で運用すれば、仕様変更への追従コストが劇的に減り、レジスタ起因のバグも削減できるというメリットを享受できる。中山氏はハードウェア・ソフトウェア・インタフェース設計にも有効と強調していたが、確かに「IDesignSpec」を利用すればHW-SWのチーム内で仕様に同期した開発が可能となり、既存資産の運用にも役立つことだろう。

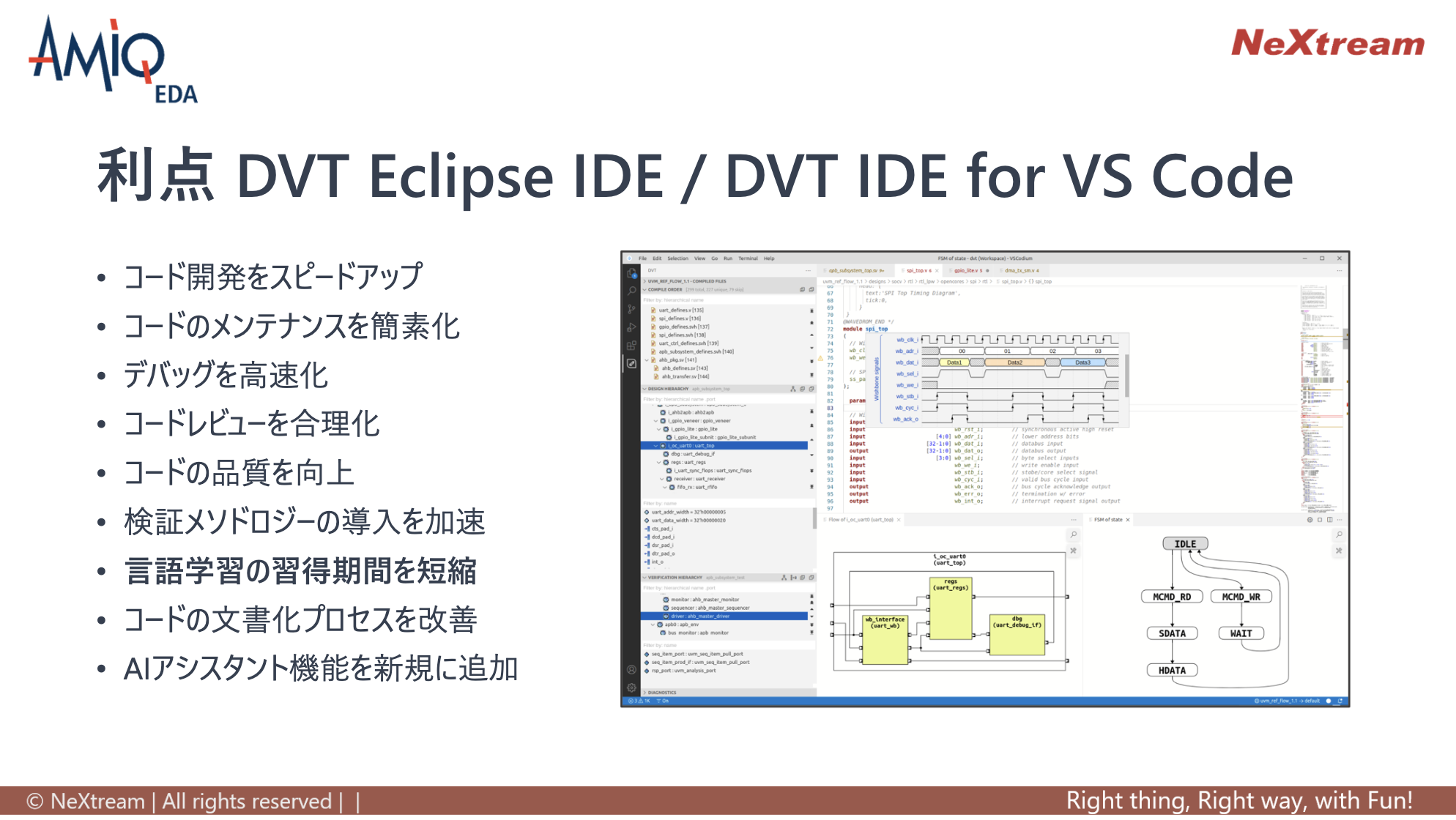

AMIQ EDA社はルーマニアのEDAベンダでネクストリームでは2023年から製品を取り扱っている。主力製品は統合開発環境「DVT IDE」でワールドワイドで200社以上に導入実績があり、独自チップを開発している米国大手企業でも軒並み「DVT IDE」を活用しているという話。中山氏によるとネクストリームでも昨年だけで10社の新規ユーザーを獲得しており、ツール評価を行い導入しなかった会社はないほど好評な製品だという。

「DVT IDE」はRTL設計者がフロントエンド環境として利用する高機能エディタで、「Verissimo」というテストベンチ・チェック機能と「Specador」というドキュメント生成機能がアドオンとして用意されている。

「DVT IDE」のサポート言語はSystem Verilog、Verilog、VHDL、UPF、CPF、e、UVM、Verilog-AMSなど。組み込まれている言語パーサーがバック・グラウンドで実行され、コードを書く側から構文チェックが可能で、ツールのワーニングに従って手早くコードを編集することができるほか、ブロック図やステートマシンなどソースコードから様々な情報を表示することが可能。WaveDromを用いた波形表示もできる。いずれの処理も非常に高速に動作するのも大きな特徴だ。

画像は中山氏の発表資料より抜粋

なお中山氏によると、日本ではドキュメント生成のアドオン機能「Specador」に関するユーザーの関心が高いという話。様々なケースにおいて、ソースコードからドキュメントを生成したいというニーズがあるようだ。

AMIQ DVT IDE を活用した設計開発効率化への取り組みと展望

AMIQの「DVT IDE」の導入事例を紹介してくれたのは、ソニーセミコンダクタソリューションズ株式会社、アナログLSI事業部 SA開発部1課 統括課長の高見 亮 氏。

高見 亮 氏

ソニーではEDAの導入判断は全社的に専門部門が行うが、「DVT IDE」は低価格で資産扱いにならず部署判断で気軽に導入できたと高見氏。高見氏の部署では画像処理LSIの開発と並行してアルゴリズム開発も行っており、SW開発のエッセンスをHW設計にも取り込みたいと考えてた最中に「DVT IDE」VS Codeバージョンの存在を知り、ツールの評価を行なったとの話。

「DVT IDE」の評価を行なった結果その有用性を確認。高見氏は評価のポイントとして下記図の3点を挙げた上で、WaveDrom連携のタイミング・ダイアグラムの生成機能が嬉しい、新人教育にも使えると付け加えた。

画像は高見氏の発表資料より抜粋

なお、「DVT IDE」がAIアシスタントにも対応したことを機に、今後AIを用いたHW設計の試行も進めていく計画と高見氏。過去に行なった汎用LLMを用いたHW設計やGitHub Copilotを用いたSW開発の施行経験を活かして、検証用の周辺回路などを対象にプロンプト入力の指針固めやAI活用ノウハウの蓄積に取り組んでいきたいと語っていた。

Menta社 eFPGAの紹介

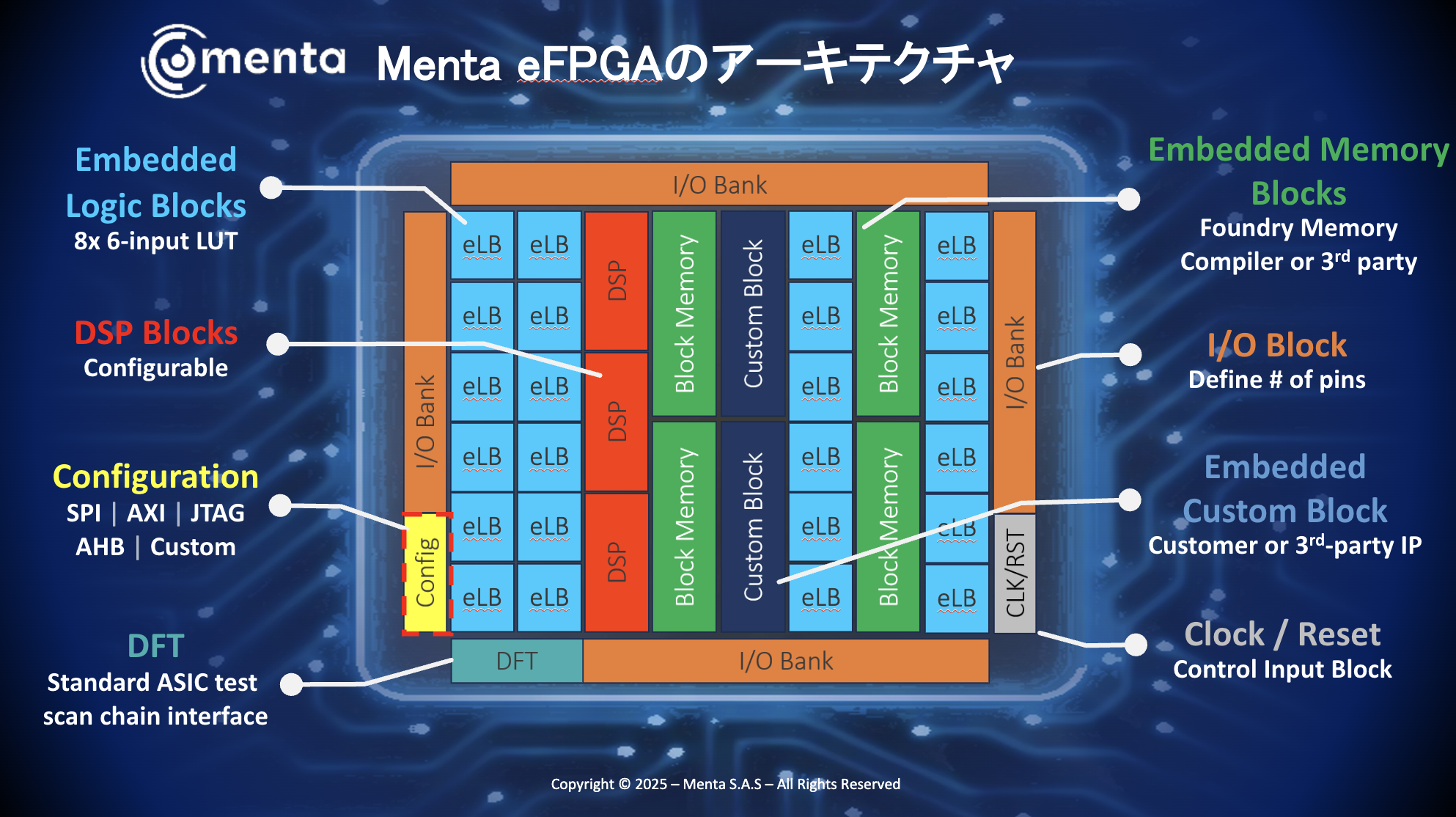

ネクストリームが今年から取り扱いを開始したMenta社はフランスのIPベンダで、ASIC/SoC組み込み型のeFPGAを提供している。ネクストリーム社長の川原 常盛 氏によると、Mentaはヨーロッパを中心に宇宙・航空・防衛分野などで実績があり、日本ではルネサスのほかに先端システム技術研究組合(RaaS)も同社の顧客とのこと。

川原 常盛 氏

MentaのeFPGAは世の中のeFPGA同様、リスピン防止(欠陥対応)、セキュリティ対応、最新規格対応など、作ったチップの更新ニーズに対応するソリューションとして利用されており半導体製品の差別化に貢献しているが、他社製品と大きく異なるのは、MentaのeFPGAはすべて標準セルで構築されているため、あらゆるファウンドリ、プロセスノードに移植可能。RTLのソフトIPとしてわずか2週間で納品されすぐに利用することができる。更に標準スキャン・チェーン・インターフェイスを提供する特許取得済みのDFT機能があり、FPGA部分を含むSoC全体のテストを効率的に行うことが可能。 この機能により、99%を超える高いテストカバレッジを実現できるという。

MentaのeFPGAのアーキテクチャは下記図の通りで、ニーズに応じて様々な構成に変更可能。ユーザーのカスタムブロックをeFPGA内部に置くこともできる。開発環境は専用の「Origami Programmer」が用意されており、RTLを入力してビットストリーム生成までワンストップでカバー。同ツールはeFPGAのユーザーにOEM供給も可能という話だ。

画像は川原氏の発表資料より抜粋

なお川原氏は製品紹介の終わりにeFPGAの潜在的な使い方として、独自のFPGA搭載SoCやプログラマブルPMICなどを紹介。耐量子暗号への対応としてeFPGAを利用するケースも増えているということだった。

ASIC開発環境へのリントチェックツール「BluePearl」導入事例紹介

BluePearlのリントチェック・ツール「Analyze RTL」の導入事例を紹介してくれたのは、株式会社リコー、技術統括部 先端技術研究所 CoE エレキ設計 設計二グループの篠岡 忍 氏。

篠岡 忍 氏

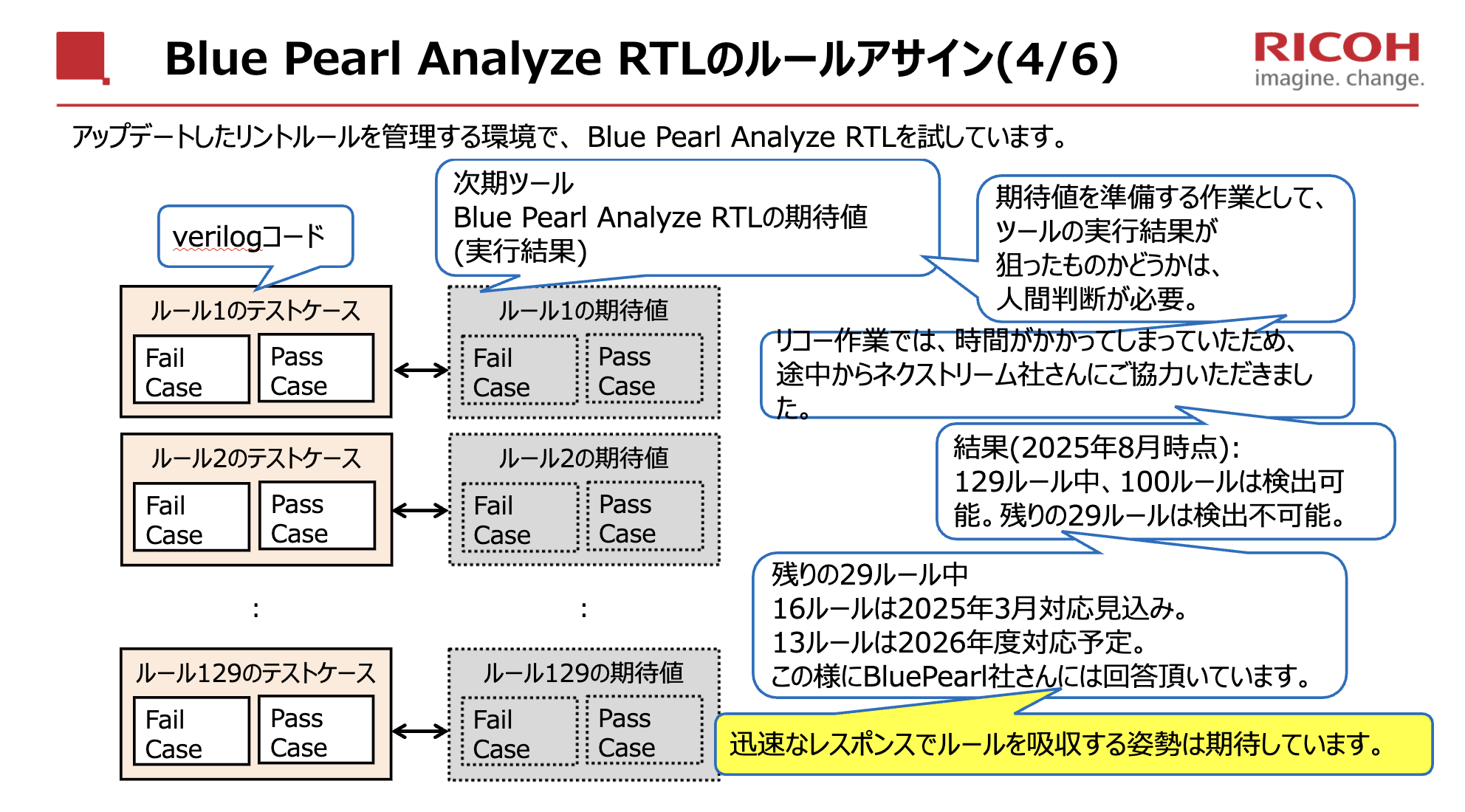

篠岡氏によるとリコーでは使用するツールの選択肢を増やすべく、社内で標準利用しているリントチェック・ツール以外の製品を検討。同等の能力で価格優位性があるなら使いたいと、BluePearl「Analyze RTL」をASIC開発に適用するためのツール評価に着手した。

もともとリコーではRTLの記述ルールを自然言語で管理していたため、「Analyze RTL」の評価の下準備として記述ルールのテストケースをVerilogでコード化。既存のリントチェック・ツールによるテストケース(Verilogコード)の実行結果のログを期待値としてまとめた。同じように「Analyze RTL」の期待値も用意し実行結果を比較したところ、全129ルールのうち100ルールはパスした。

パスしなかったルールについてはBluePearlに対応を依頼。その大半は今年度中に対応される予定とのことで、全てのルール検出が実現したらASIC開発に投入したいと篠岡氏は語った。

画像は篠岡氏の発表資料より抜粋

MachineWare社およびRoofline社のソリューション紹介

MachineWare社とRoofline社はいずれも独アーヘン工科大学を起源とする会社で、ネクストリーム川原氏とアーヘン工科大学の繋がりにより製品の取り扱いを行っている。

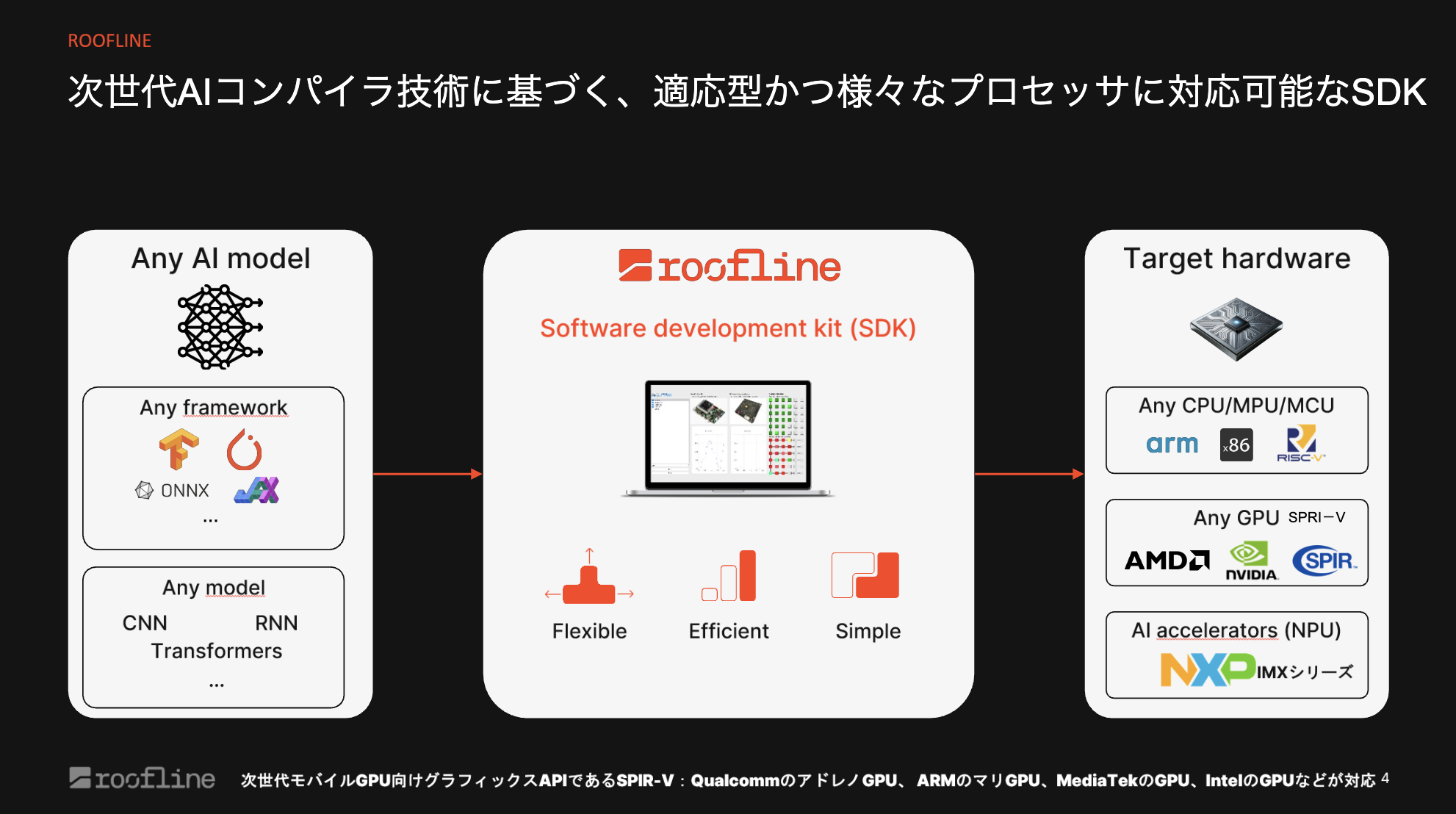

ネクストリームが今年7月から扱い始めたRoofline社のソリューションは、あらゆるAI推論モデルを様々なターゲットに実装できるソフトウェア開発環境で次世代のAIコンパイラ技術をベースとしている。川原氏によるとRooflineはすでに1,500種類のAIモデルを自社のソフトウェア開発環境を使って動かした実績があり、中国のDeepSeekはわずか1日で実装したとのこと。

画像は川原氏の発表資料より抜粋

実装ターゲットとしては様々なCPU, MCU, GPUへの対応を進めているが、中でもあらゆるGPUで実行可能な次世代グラフィックAPIの中間言語「SPIR-V」の対応に注力しているとの話。また、半導体ベンダNXPとはがっつりビジネスをしており、同社のプロセッサ「i.MXシリーズ」を用いたエッジAIの実装環境としてRooflineのソフトウェア開発環境が利用される予定だという。

川原氏はRooflineを使ったAI実装事例を幾つか紹介してくれたが、RooflineはAIモデルを容易に実装できるだけでなく、最適なパフォーマンスを自動または手動で実現できるのが大きな特長。ビジネスモデルとしては、エッジAIシステムの開発者向けにソフトウェア開発環境を販売する形態と、エッジ向けハードウェアIP(NPU)ベンダにソフトウェア開発環境を販売する形態(NXPのパターン)、2つのモデルがあるということだ。

各社製品に関する詳細は、ネクストリームにお問い合わせください。

株式会社ネクストリーム

クアドリック株式会社

= EDA EXPRESS 菰田 浩 =

(2025.11.19

)