AIベースのレイアウト設計でCMOSイメージセンサーのメモリ配置を最適化、キヤノンによるテープアウト事例

2024年7月10日、日本ケイデンスは品川で「デジタル設計ソリューションセミナー」を開催した。

Cadenceは新たな試みとして、特定テーマに絞った様々なセミナーを単発で開催しているが、「デジタル設計ソリューションセミナー」もそのうちの一つ。

ここでは同セミナー行われた講演の一つ、「Cerebrusを用いたCMOSイメージセンサーにおけるメモリ配置最適化」について紹介する。

同講演の講演者は、キヤノン株式会社 デバイス開発本部 デバイス開発統括部門 半導体デバイス第二開発センター 半導体デバイス製品第三設計部 佐々木 誠仁 氏。

実は佐々木氏の講演は、昨年もCadenceのユーザー・カンファレンス「CadenceLIVE Japan 2023」で聴講し、レポートしている。

※CadenceLIVE Japan 2023参加レポート(2)、ルネサス、キヤノンによるAIツール活用設計の事例

※講演者佐々木氏

昨年の講演の続編となる今回の佐々木氏の講演は、AIベースの設計最適化機能「Cerebrus」によるフロアプラン最適化の事例。これまで評価止まりだったフロアプランへの「Cerebrus」適用を試みた。

佐々木氏の担当するCMOSイメージセンサーの設計は、配線リソースが少なく、メモリマクロの配置が非常に困難で工数を要する。そのためどうしても保守的なレイアウトになりがちなため、「Cerebrus」の導入によるメモリ配置の最適化と効率化を考えた。

■Floorplan Optimizationの適用

今回キヤノンが実設計に適用したのは、「Cerebrus」の「Floorplan Optimization」という機能。この機能はCadenceの配置配線ツール「Innovus」の自動配置機能「Mixecd Placer」を通して実行する機能で、これまで人手で行っていたメモリマクロセルの配置を自動化してくれるもの。設計対象によっては100以上のメモリマクロセルを配置する必要があるため、同機能の活用はキヤノンの課題克服に直結する。

「Floorplan Optimization」の探索はスタンダードセルの初期配置結果で評価されるため、スタンダードセルの配置リスト(タイミング、消費電力、エリア、配線混雑)、電源の配線リストも考慮したメモリマクロセルの最適な配置を探索することが可能。ユーザーが定義した探索対象からシナリオが自動生成され「Innovus」が実行されると、その実行結果からのフィードバックをもとに更に次々とシナリオを自動生成できるため、この繰り返しにより最適なレイアウト結果を探索できるようになる。

佐々木氏によると、キヤノンでは「Floorplan Optimization」を試行した結果から、Cadenceの協力を得てメモリマクロ間の配置スペースをMachine Learningの探索対象として定義。それにより「Innovus」による最終的な配線によるPPAの品質を高めた。なお「Floorplan Optimization」によるメモリ配置の探索結果の中で最もPPAの改善度が高いシナリオが、「Innovus」による最終配線の結果としても最もPPAが良かったとのこと。「Floorplan Optimization」の探索結果は実レイアウトにおいても信頼性が高いことがうかがえる。

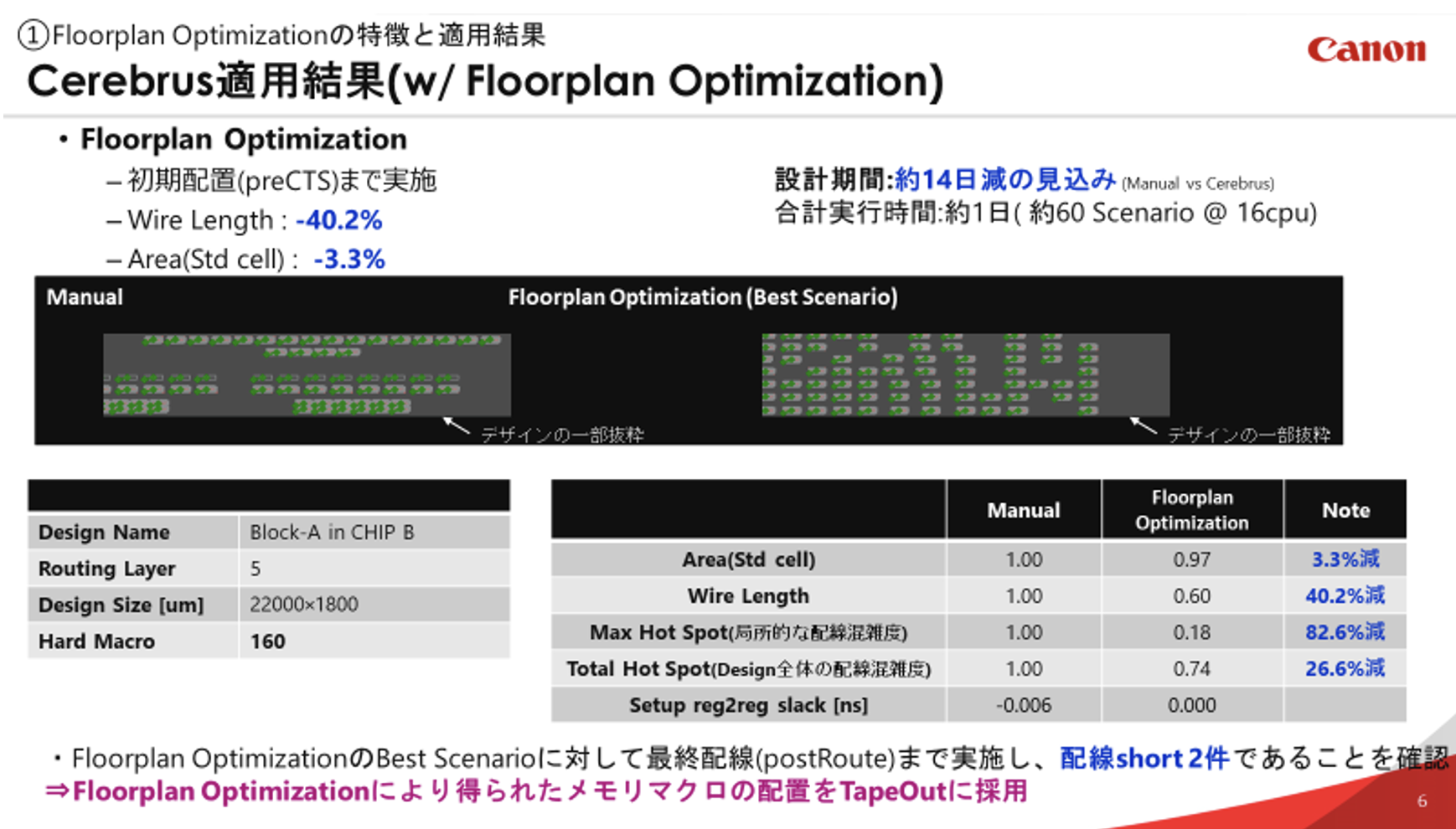

実際に「Floorplan Optimization」を使ったレイアウト結果は以下の画像の通り。

2つのデザインに「Floorplan Optimization」を適用したところ、いずれの結果も人手によるレイアウトよりもエリアが3%程度、配線長が20%以上減った。片方のデザインは全体的な配線混雑度が4倍以上に増えたが、最終的な「Innovus」による配線の結果、配線ショートはなかった。タイミングに関する問題もなく結果に満足し、自動生成したレイアウトをテープアウトに採用した。

当然ながら工数の面では「Floorplan Optimization」により大幅な工数削減に成功した。特に高アスペクト比で難易度の高いデザインに関しては、人手設計と比較して工数を14日削減、人でやると30日かかる作業を半減できた。

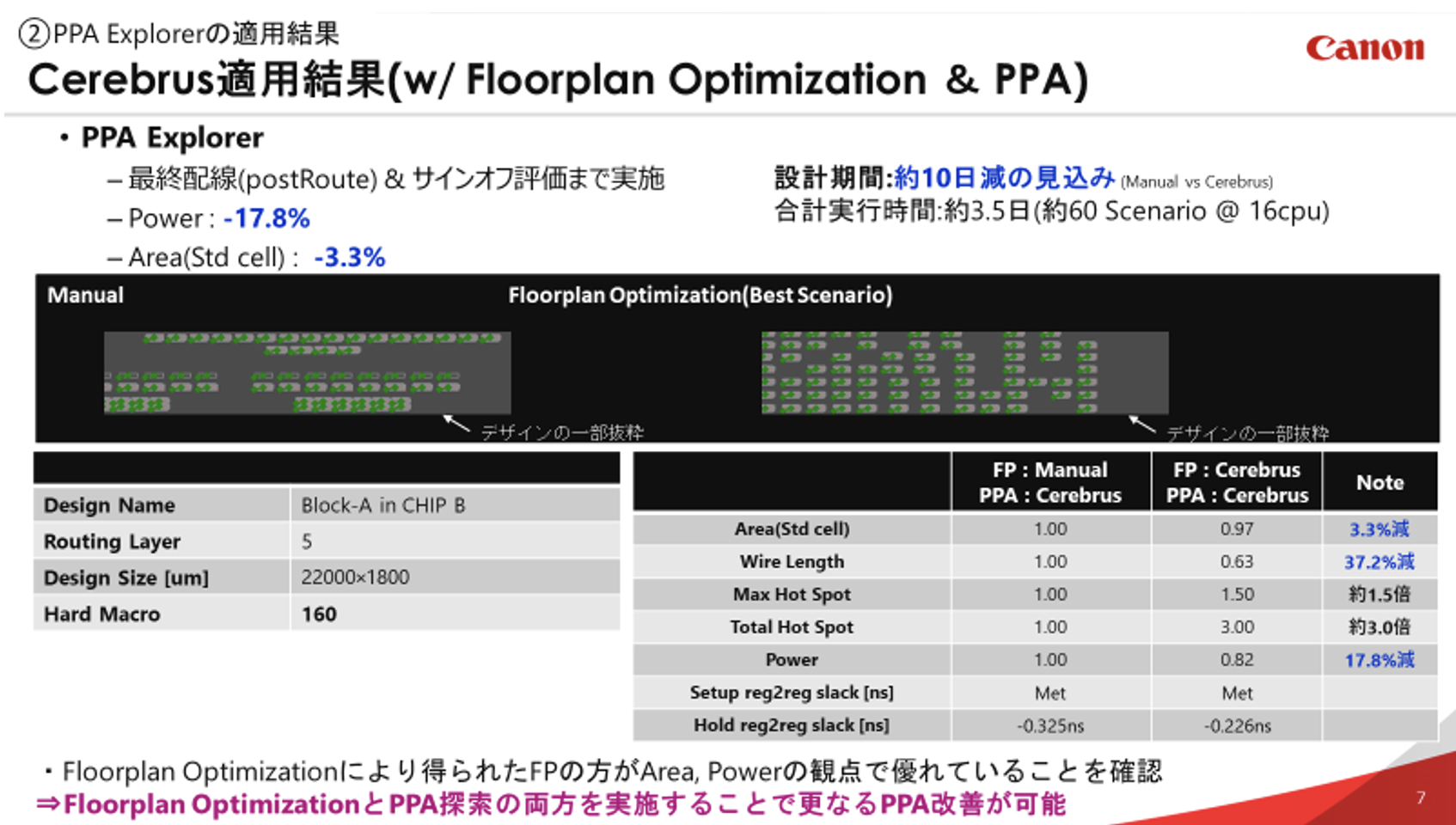

更に「Floorplan Optimization」で得られたフロアプランに初期配置以降のPPA探索機能「PPA Explorer」を適用したところ、人手設計よりもエリアを約3%、消費電力を約18%削減することに成功(パワーサインオフツールVoltusの結果)。PPA探索に関しても10日程度の工数削減効果があった。着目したのはエリア、配線長ともに人手設計よりも良く「Floorplan Optimization」の結果を維持できている点。佐々木氏は「Floorplan Optimization」と「PPA Explorer」を両方使うことで更なるPPA改善が可能になるとした。

※画像は全てCadence提供のデータ

これらの結果から佐々木氏は「Floorplan Optimization」と「PPA Explorer」によって、メモリマクロの配置に関する下記全ての課題に対応できたとまとめた。

・プロセステクノロジ毎に最適なレイアウト結果を導く

・難易度が高いメモリマクロの配置

・メモリマクロの配置工数の削減

・回路規模、電力を抑えた最適なレイアウト結果を短期間で得る

なお佐々木氏は「Floorplan Optimization」の良い点として以下のような点も指摘していた。

・設計時間の短縮と合わせて、ベストシナリオが一目でわかる

・人で行えなかった探索パラメータを自動で探求できる

・従来フローより楽にメモリマクロセルの配置が行える。しかも設計フローへの組み込みが容易。

・メモリマクロセル配置を無理なく攻められる

■Model Replay機能について

佐々木氏は講演の最後に「Cerebrus」の「Model Replay機能」についても紹介。同機能は「Cerebrus」の探索結果から得られた設計パラメータを「Innovus」など各ツールに与える機能で、過去の実行結果をデザインに反映できるため、クリーンなRTLを用いたレイアウト設計においてPPA探索の再実行などが不要となりTAT短縮に役立つ。キヤノンでは実際に同機能を試行し、「PPA Explorer」の再実行を行うことなく過去のPPA探索結果が再現可能であることを確認しているということだ。

■まとめ

キヤノンは今回の「Floorplan Optimization」の適用により、レイアウトフロー全体に対する「Cerebrus」の適用を完了。各レイアウト工程でその適用効果を確認できたことから、今後は他のツールにおいても「Cerebrus」の適用を検討していく予定だという。

= EDA EXPRESS 菰田 浩 =

(2024.08.06

)