Cadenceが同社初となるNetwork-on-Chip (NoC)の設計IPを発表

Cadenceが同社初となるNetwork-on-Chip (NoC)の設計IPを発表

2024年6月25日、Cadenceは設計IPの新製品「Janus ™ Network-on-Chip (NoC) 」を発表した。

発表によると「Janus NoC」は、GUIベースのツールで高度に構成可能な高性能NoC IPで、大規模SoCのサブシステムからマルチチップ・システムのネットワーク設計まで対応可能。配線数の削減、複雑さの低減、動作の高速化など、ネットワーク設計における課題に対処し、迅速かつ低リスクなPPA目標の達成を実現する。

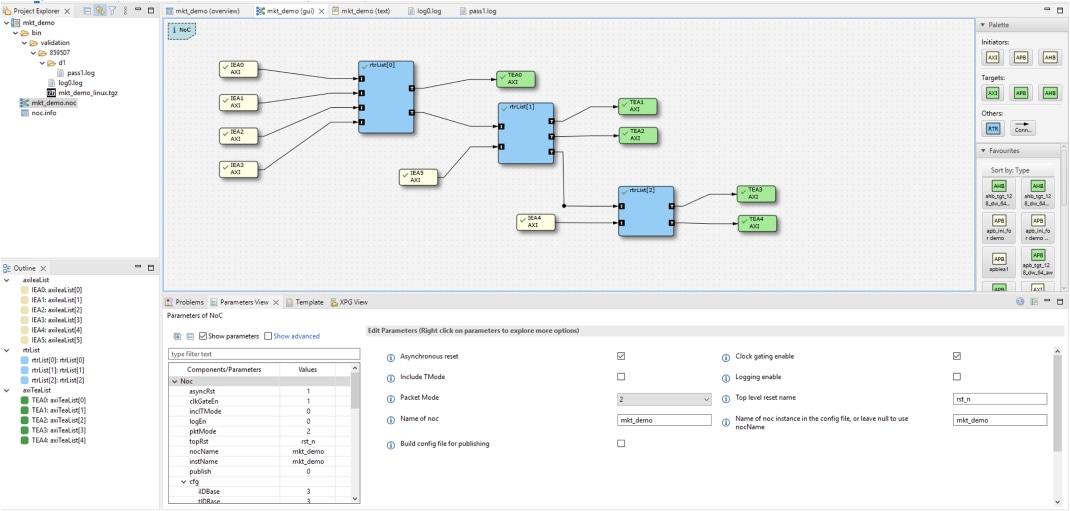

「Janus NoC」の設計ツールはCadenceのプロセッサIP「Tensilica」の設計ツールをベースとしており、GUIベースの操作からテキストファイル、RTL、機能検証用SystemCモデル、合成スクリプト、テストベンチを生成可能。帯域幅、レイテンシ、クロック・ドメイン・クロッシング、クロック・ゲーティング、バッファサイズ、パイプライン・ステージなど、ユーザーによる高度な設定が可能となっている。

※画像はNoC設計ツールのGUI、CadenceのWeb上の掲載データ

設計したNoCは、Cadenceのシミュレーション/エミュレーション・ツールを使用してPPAメトリックを検証することが可能。この早期のアーキテクチャ探索により、ニーズを満たす最適なNoC設計が現実のものとなり、製品の市場投入時間を短縮できる。

なお「Janus NoC」を用いて作ったサブシステムは容易に再利用することが可能。また「Janus NoC」はAXI4やAHBなどの業界標準インターフェースを備えたあらゆるIPと互換性があるということだ。

NoC IPと言えば古くはFacebookに買収されたSonicsの製品、近年ではArterisの製品が有名だが、大手EDAベンダによる独自のNoC IPはこれまで有りそうで無かった。システムのパフォーマンスに大きな影響を及ぼすコンポーネントだけに、CadenceのNoCがどの程度のBenefitをもたらすのか非常に興味深い。

= EDA EXPRESS 菰田 浩 =

(2024.06.27

)