性能、コード密度、電力効率を全て100倍に引き上げる英RED Semiconductorの高性能プロセッサ「VISC」

2024年4月2日、英半導体ベンチャーRED Semiconductorは、RISC-Vの機能を拡張する独自のISA「VISC ISA」とRISC-VベースのプロセッサIP「VISC」を発表した。

RED Semiconductorは、2021年に英国半導体業界の著名な人物らが創業した半導体ベンチャーで、CEOのJames Lewis氏はOxford Semiconductor、Reduxなどのベンチャー企業を設立して成功を収めている。

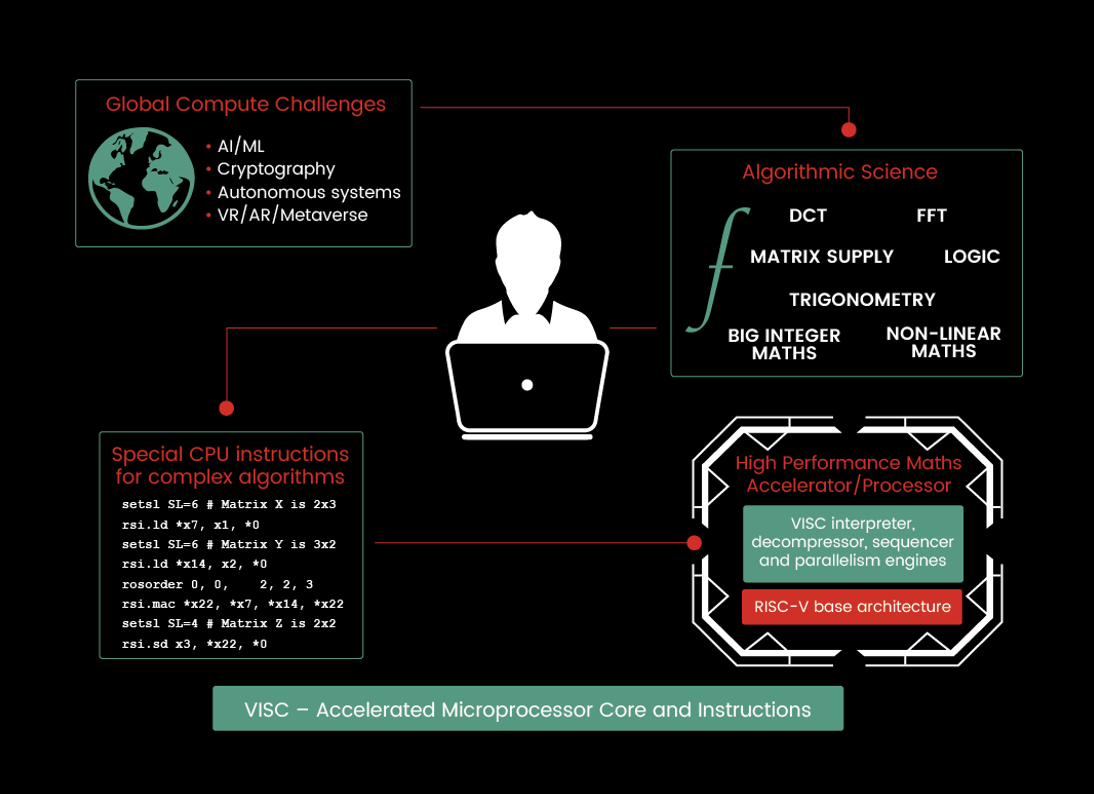

RED Semiconductorが目指すのは、マイクロ・プロセッサの大幅なパフォーマンス向上で「VISC (Versatile Intrinsic Structured Computing) 」と呼ぶプロセッサ・アーキテクチャでそれを実現しようとしている。

「VISC」はオープンソースのハードウェア・プロジェクト「Libre-SOC」から生まれた技術で、RED Semiconductorは同技術をもとに独自の圧縮およびシーケンス技術を使用して数学的アルゴリズムを並列実行可能な形に最適化し、ベクトル化された命令セットを使用して再構成可能なハードウェア・エンジンを備えるRISC-Vベースのプロセッサ・コア「VICS」で並列実行を行う。アルゴリズムの個々の要素を順番に実行するのではなく、ルーチン全体を総合的に並列実行することにより「VISC」は消費電力を削減しながら、既存のプロセッサよりもはるかに優れたパフォーマンスを実現できるという。

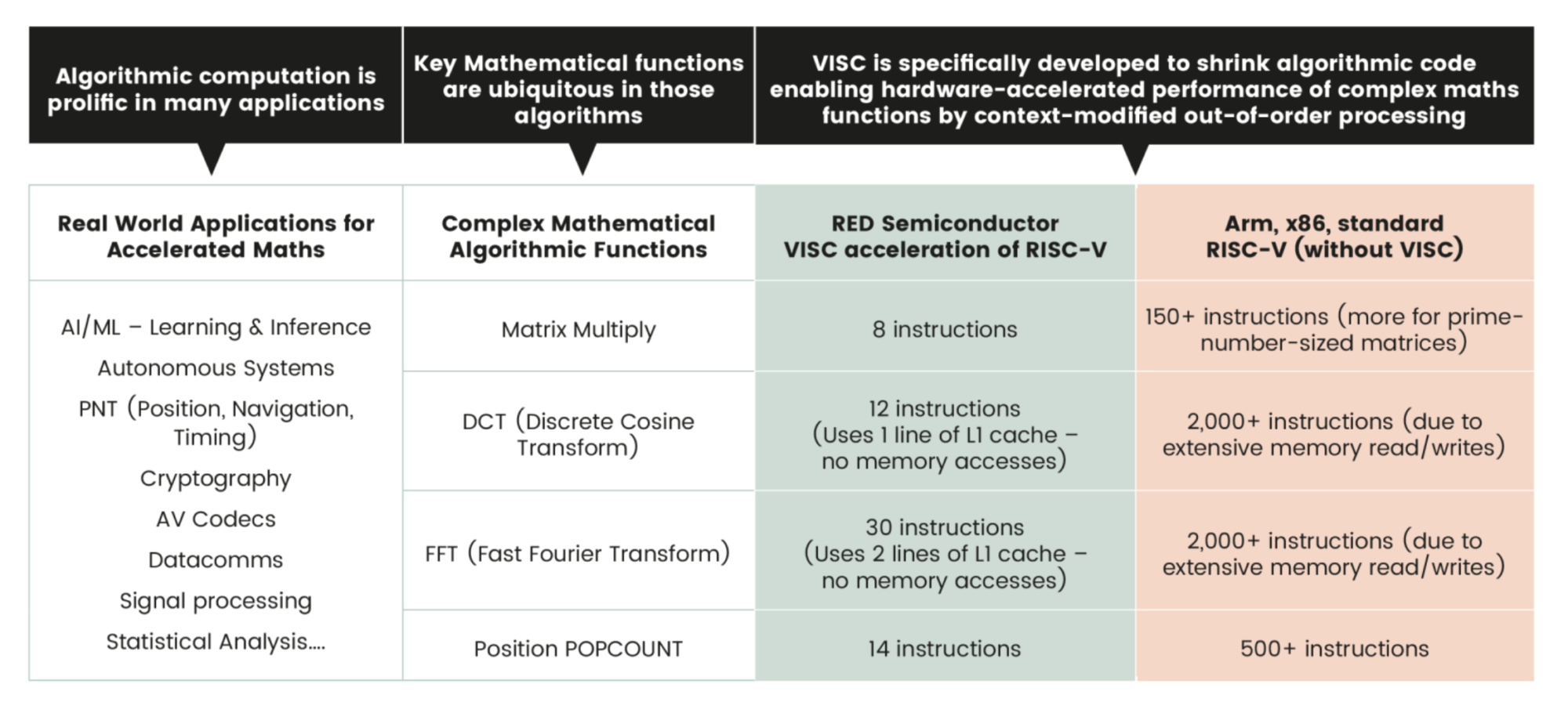

RED Semiconductorによると「VISC ISA」はRISC-Vと互換性があり、標準のRISC-V命令セット、RISC-Vベクトル拡張はすべてベクトル化され、単一のレジスタ・バンクを使用して効率的に実行可能。また「VISC ISA」は非常にコード密度が高く、RISC-V, x86, ArmなどのISAで必要となるコードサイズのほんの一部で複雑なアルゴリズムを記述することができる。例えば主流のISAでは行列乗算に100以上の命令が必要となるが「VISC ISA」ではわずか3命令で記述可能。2,000以上の命令が必要なDCTやFFTもわずか数十命令で済むという。

今回発表されたプロセッサIP「VISC」は、汎用マイクロ・プロセッサの多用途性と専用ハードウェア・アクセラレータのパフォーマンス、両方の利点を提供するソリューションで、計算中のメモリアクセスを排除してセキュリティを強化できるという大きなメリットも兼ね備えている。AI計算をより効率的かつ低消費電力で実行でき、セキュリティ面の利点もあることから、RED SemiconductorはエッジAIを「VISC」の大きなターゲットの一つとしてとらえているが、「VISC」は1コアから1,000コア以上まで拡張できるため、エッジAIに限らずHPCアプリケーションにも対応することも可能だとしている。

なお今回発表された「VISC」はRISC-Vベースで実装されているが、「VISC」は基本的にISAに依存していないため、RED Semiconductorは将来的に「VISC」を他の命令セット・アーキテクチャに適用する可能性があるとしている。

RED Semiconductorは、現在「VISC」の生産に向けた資金として250万ポンド(約5億円)の調達を計画中とのこと。

= EDA EXPRESS 菰田 浩 =

(2024.04.11

)